Welcome to **E-XFL.COM**

**Understanding Embedded - CPLDs (Complex Programmable Logic Devices)**

Embedded - CPLDs, or Complex Programmable Logic Devices, are highly versatile digital logic devices used in electronic systems. These programmable components are designed to perform complex logical operations and can be customized for specific applications. Unlike fixed-function ICs, CPLDs offer the flexibility to reprogram their configuration, making them an ideal choice for various embedded systems. They consist of a set of logic gates and programmable interconnects, allowing designers to implement complex logic circuits without needing custom hardware.

#### **Applications of Embedded - CPLDs**

| Details                         |                                                           |

|---------------------------------|-----------------------------------------------------------|

| Product Status                  | Active                                                    |

| Programmable Type               | In System Programmable                                    |

| Delay Time tpd(1) Max           | 9 ns                                                      |

| Voltage Supply - Internal       | 1.71V ~ 1.89V                                             |

| Number of Logic Elements/Blocks | 570                                                       |

| Number of Macrocells            | 440                                                       |

| Number of Gates                 | -                                                         |

| Number of I/O                   | 160                                                       |

| Operating Temperature           | 0°C ~ 85°C (TJ)                                           |

| Mounting Type                   | Surface Mount                                             |

| Package / Case                  | 256-TFBGA                                                 |

| Supplier Device Package         | 256-MBGA (11x11)                                          |

| Purchase URL                    | https://www.e-xfl.com/product-detail/intel/epm570zm256c7n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

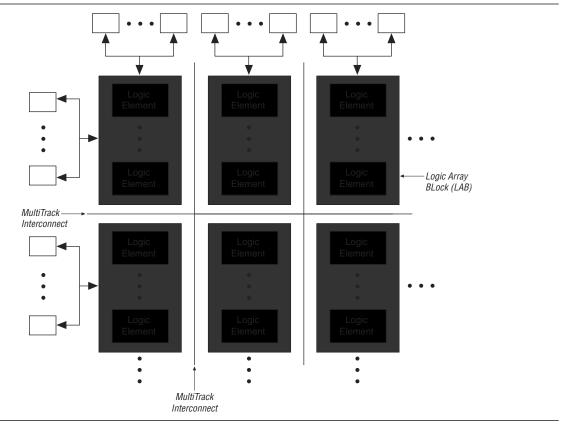

Figure 2–1 shows a functional block diagram of the MAX II device.

Figure 2–1. MAX II Device Block Diagram

Each MAX II device contains a flash memory block within its floorplan. On the EPM240 device, this block is located on the left side of the device. On the EPM570, EPM1270, and EPM2210 devices, the flash memory block is located on the bottom-left area of the device. The majority of this flash memory storage is partitioned as the dedicated configuration flash memory (CFM) block. The CFM block provides the non-volatile storage for all of the SRAM configuration information. The CFM automatically downloads and configures the logic and I/O at power-up, providing instant-on operation.

For more information about configuration upon power-up, refer to the *Hot Socketing* and *Power-On Reset in MAX II Devices* chapter in the *MAX II Device Handbook*.

A portion of the flash memory within the MAX II device is partitioned into a small block for user data. This user flash memory (UFM) block provides 8,192 bits of general-purpose user storage. The UFM provides programmable port connections to the logic array for reading and writing. There are three LAB rows adjacent to this block, with column numbers varying by device.

Table 2–1 shows the number of LAB rows and columns in each device, as well as the number of LAB rows and columns adjacent to the flash memory area in the EPM570, EPM1270, and EPM2210 devices. The long LAB rows are full LAB rows that extend from one side of row I/O blocks to the other. The short LAB rows are adjacent to the UFM block; their length is shown as width in LAB columns.

# **Logic Array Blocks**

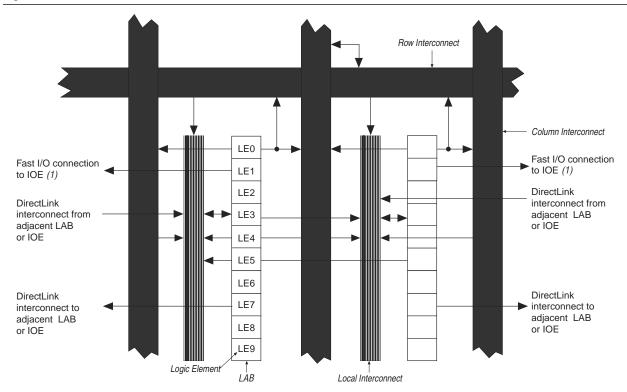

Each LAB consists of 10 LEs, LE carry chains, LAB control signals, a local interconnect, a look-up table (LUT) chain, and register chain connection lines. There are 26 possible unique inputs into an LAB, with an additional 10 local feedback input lines fed by LE outputs in the same LAB. The local interconnect transfers signals between LEs in the same LAB. LUT chain connections transfer the output of one LE's LUT to the adjacent LE for fast sequential LUT connections within the same LAB. Register chain connections transfer the output of one LE's register to the adjacent LE's register within an LAB. The Quartus® II software places associated logic within an LAB or adjacent LABs, allowing the use of local, LUT chain, and register chain connections for performance and area efficiency. Figure 2–3 shows the MAX II LAB.

Figure 2–3. MAX II LAB Structure

#### Note to Figure 2-3:

(1) Only from LABs adjacent to IOEs.

#### LAB Interconnects

The LAB local interconnect can drive LEs within the same LAB. The LAB local interconnect is driven by column and row interconnects and LE outputs within the same LAB. Neighboring LABs, from the left and right, can also drive an LAB's local interconnect through the DirectLink connection. The DirectLink connection feature minimizes the use of row and column interconnects, providing higher performance and flexibility. Each LE can drive 30 other LEs through fast local and DirectLink interconnects. Figure 2–4 shows the DirectLink connection.

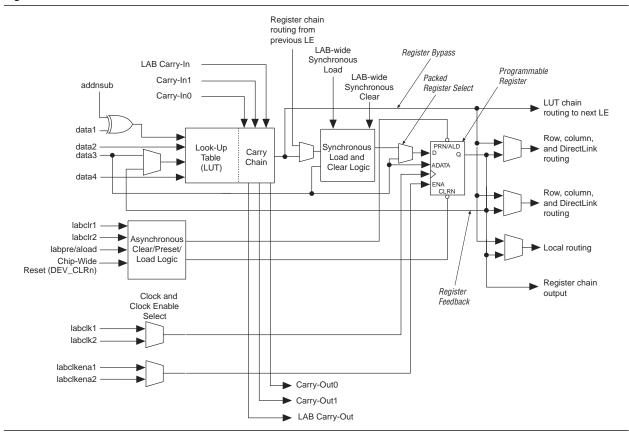

Figure 2-6. MAX II LE

Each LE's programmable register can be configured for D, T, JK, or SR operation. Each register has data, true asynchronous load data, clock, clock enable, clear, and asynchronous load/preset inputs. Global signals, general-purpose I/O pins, or any LE can drive the register's clock and clear control signals. Either general-purpose I/O pins or LEs can drive the clock enable, preset, asynchronous load, and asynchronous data. The asynchronous load data input comes from the data3 input of the LE. For combinational functions, the LUT output bypasses the register and drives directly to the LE outputs.

Each LE has three outputs that drive the local, row, and column routing resources. The LUT or register output can drive these three outputs independently. Two LE outputs drive column or row and DirectLink routing connections and one drives local interconnect resources. This allows the LUT to drive one output while the register drives another output. This register packing feature improves device utilization because the device can use the register and the LUT for unrelated functions. Another special packing mode allows the register output to feed back into the LUT of the same LE so that the register is packed with its own fan-out LUT. This provides another mechanism for improved fitting. The LE can also drive out registered and unregistered versions of the LUT output.

The Quartus II software automatically creates carry chain logic during design processing, or you can create it manually during design entry. Parameterized functions such as LPM functions automatically take advantage of carry chains for the appropriate functions. The Quartus II software creates carry chains longer than 10 LEs by linking adjacent LABs within the same row together automatically. A carry chain can extend horizontally up to one full LAB row, but does not extend between LAB rows

#### **Clear and Preset Logic Control**

LAB-wide signals control the logic for the register's clear and preset signals. The LE directly supports an asynchronous clear and preset function. The register preset is achieved through the asynchronous load of a logic high. MAX II devices support simultaneous preset/asynchronous load and clear signals. An asynchronous clear signal takes precedence if both signals are asserted simultaneously. Each LAB supports up to two clears and one preset signal.

In addition to the clear and preset ports, MAX II devices provide a chip-wide reset pin (DEV\_CLRn) that resets all registers in the device. An option set before compilation in the Quartus II software controls this pin. This chip-wide reset overrides all other control signals and uses its own dedicated routing resources (that is, it does not use any of the four global resources). Driving this signal low before or during power-up prevents user mode from releasing clears within the design. This allows you to control when clear is released on a device that has just been powered-up. If not set for its chip-wide reset function, the DEV\_CLRn pin is a regular I/O pin.

By default, all registers in MAX II devices are set to power-up low. However, this power-up state can be set to high on individual registers during design entry using the Quartus II software.

## **MultiTrack Interconnect**

In the MAX II architecture, connections between LEs, the UFM, and device I/O pins are provided by the MultiTrack interconnect structure. The MultiTrack interconnect consists of continuous, performance-optimized routing lines used for inter- and intradesign block connectivity. The Quartus II Compiler automatically places critical design paths on faster interconnects to improve design performance.

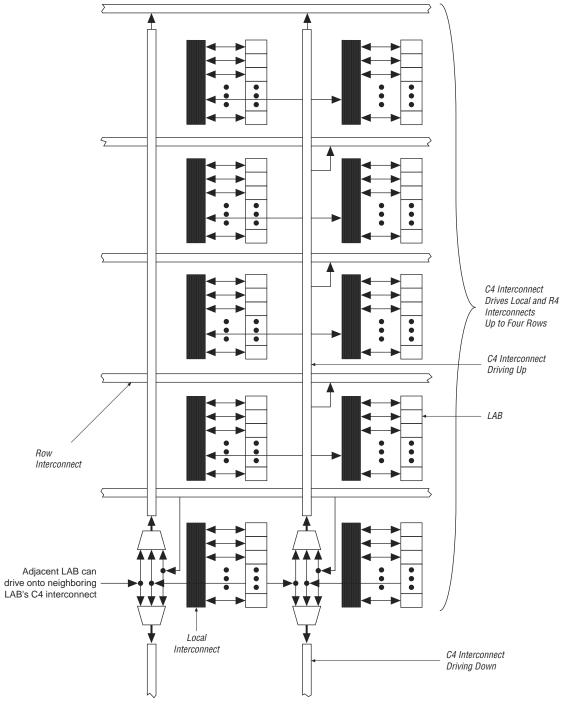

The MultiTrack interconnect consists of row and column interconnects that span fixed distances. A routing structure with fixed length resources for all devices allows predictable and short delays between logic levels instead of large delays associated with global or long routing lines. Dedicated row interconnects route signals to and from LABs within the same row. These row resources include:

- DirectLink interconnects between LABs

- R4 interconnects traversing four LABs to the right or left

The DirectLink interconnect allows an LAB to drive into the local interconnect of its left and right neighbors. The DirectLink interconnect provides fast communication between adjacent LABs and/or blocks without using row interconnect resources.

Figure 2–12. C4 Interconnect Connections (Note 1)

### Note to Figure 2–12:

(1) Each C4 interconnect can drive either up or down four rows.

## I/O Structure

IOEs support many features, including:

- LVTTL and LVCMOS I/O standards

- 3.3-V, 32-bit, 66-MHz PCI compliance

- Joint Test Action Group (JTAG) boundary-scan test (BST) support

- Programmable drive strength control

- Weak pull-up resistors during power-up and in system programming

- Slew-rate control

- Tri-state buffers with individual output enable control

- Bus-hold circuitry

- Programmable pull-up resistors in user mode

- Unique output enable per pin

- Open-drain outputs

- Schmitt trigger inputs

- Fast I/O connection

- Programmable input delay

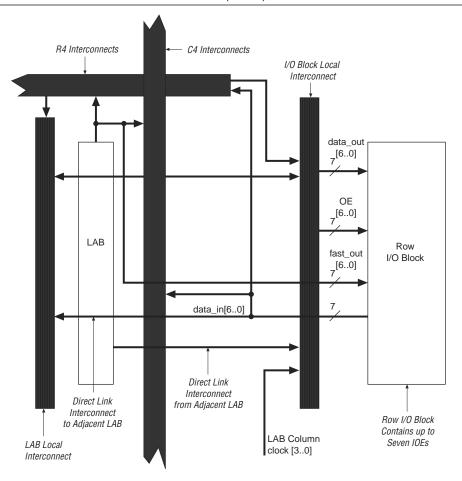

MAX II device IOEs contain a bidirectional I/O buffer. Figure 2–19 shows the MAX II IOE structure. Registers from adjacent LABs can drive to or be driven from the IOE's bidirectional I/O buffers. The Quartus II software automatically attempts to place registers in the adjacent LAB with fast I/O connection to achieve the fastest possible clock-to-output and registered output enable timing. For input registers, the Quartus II software automatically routes the register to guarantee zero hold time. You can set timing assignments in the Quartus II software to achieve desired I/O timing.

### **Fast I/O Connection**

A dedicated fast I/O connection from the adjacent LAB to the IOEs within an I/O block provides faster output delays for clock-to-output and  $t_{PD}$  propagation delays. This connection exists for data output signals, not output enable signals or input signals. Figure 2–20, Figure 2–21, and Figure 2–22 illustrate the fast I/O connection.

Figure 2–20 shows how a row I/O block connects to the logic array.

Figure 2–20. Row I/O Block Connection to the Interconnect (Note 1)

#### Note to Figure 2-20:

(1) Each of the seven IOEs in the row I/O block can have one  $\mathtt{data\_out}$  or  $\mathtt{fast\_out}$  output, one  $\mathtt{OE}$  output, and one  $\mathtt{data\_in}$  input.

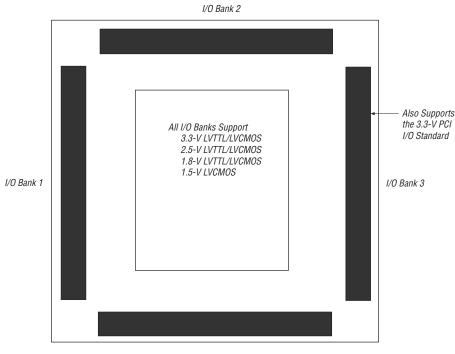

Figure 2-23. MAX II I/O Banks for EPM1270 and EPM2210 (Note 1), (2)

I/O Bank 4

#### Notes to Figure 2-23:

- (1) Figure 2-23 is a top view of the silicon die.

- (2) Figure 2-23 is a graphical representation only. Refer to the pin list and the Quartus II software for exact pin locations.

Each I/O bank has dedicated  $V_{\rm CCIO}$  pins that determine the voltage standard support in that bank. A single device can support 1.5-V, 1.8-V, 2.5-V, and 3.3-V interfaces; each individual bank can support a different standard. Each I/O bank can support multiple standards with the same  $V_{\rm CCIO}$  for input and output pins. For example, when  $V_{\rm CCIO}$  is 3.3 V, Bank 3 can support LVTTL, LVCMOS, and 3.3-V PCI.  $V_{\rm CCIO}$  powers both the input and output buffers in MAX II devices.

The JTAG pins for MAX II devices are dedicated pins that cannot be used as regular I/O pins. The pins TMS, TDI, TDO, and TCK support all the I/O standards shown in Table 2–4 on page 2–27 except for PCI. These pins reside in Bank 1 for all MAX II devices and their I/O standard support is controlled by the  $V_{\text{CCIO}}$  setting for Bank 1.

#### **PCI Compliance**

The MAX II EPM1270 and EPM2210 devices are compliant with PCI applications as well as all 3.3-V electrical specifications in the *PCI Local Bus Specification Revision 2.2*. These devices are also large enough to support PCI intellectual property (IP) cores. Table 2–5 shows the MAX II device speed grades that meet the PCI timing specifications.

### **Bus Hold**

Each MAX II device I/O pin provides an optional bus-hold feature. The bus-hold circuitry can hold the signal on an I/O pin at its last-driven state. Since the bus-hold feature holds the last-driven state of the pin until the next input signal is present, an external pull-up or pull-down resistor is not necessary to hold a signal level when the bus is tri-stated.

The bus-hold circuitry also pulls undriven pins away from the input threshold voltage where noise can cause unintended high-frequency switching. The designer can select this feature individually for each I/O pin. The bus-hold output will drive no higher than  $V_{\text{CCIO}}$  to prevent overdriving signals. If the bus-hold feature is enabled, the device cannot use the programmable pull-up option.

The bus-hold circuitry uses a resistor to pull the signal level to the last driven state. The *DC and Switching Characteristics* chapter in the *MAX II Device Handbook* gives the specific sustaining current for each  $V_{\text{CCIO}}$  voltage level driven through this resistor and overdrive current used to identify the next-driven input level.

The bus-hold circuitry is only active after the device has fully initialized. The bus-hold circuit captures the value on the pin present at the moment user mode is entered.

## **Programmable Pull-Up Resistor**

Each MAX II device I/O pin provides an optional programmable pull-up resistor during user mode. If the designer enables this feature for an I/O pin, the pull-up resistor holds the output to the  $V_{\text{CCIO}}$  level of the output pin's bank.

The programmable pull-up resistor feature should not be used at the same time as the bus-hold feature on a given I/O pin.

## **Programmable Input Delay**

The MAX II IOE includes a programmable input delay that is activated to ensure zero hold times. A path where a pin directly drives a register, with minimal routing between the two, may require the delay to ensure zero hold time. However, a path where a pin drives a register through long routing or through combinational logic may not require the delay to achieve a zero hold time. The Quartus II software uses this delay to ensure zero hold times when needed.

### MultiVolt I/O Interface

The MAX II architecture supports the MultiVolt I/O interface feature, which allows MAX II devices in all packages to interface with systems of different supply voltages. The devices have one set of VCC pins for internal operation ( $V_{\text{CCINT}}$ ), and up to four sets for input buffers and I/O output driver buffers ( $V_{\text{CCIO}}$ ), depending on the number of I/O banks available in the devices where each set of VCC pins powers one I/O bank. The EPM240 and EPM570 devices have two I/O banks respectively while the EPM1270 and EPM2210 devices have four I/O banks respectively.

MII51003-1.6

## Introduction

This chapter discusses how to use the IEEE Standard 1149.1 Boundary-Scan Test (BST) circuitry in MAX II devices and includes the following sections:

- "IEEE Std. 1149.1 (JTAG) Boundary-Scan Support" on page 3–1

- "In System Programmability" on page 3–4

# IEEE Std. 1149.1 (JTAG) Boundary-Scan Support

All MAX® II devices provide Joint Test Action Group (JTAG) boundary-scan test (BST) circuitry that complies with the IEEE Std. 1149.1-2001 specification. JTAG boundary-scan testing can only be performed at any time after  $V_{\text{CCINT}}$  and all  $V_{\text{CCIO}}$  banks have been fully powered and a  $t_{\text{CONFIG}}$  amount of time has passed. MAX II devices can also use the JTAG port for in-system programming together with either the Quartus® II software or hardware using Programming Object Files (.pof), JamTM Standard Test and Programming Language (STAPL) Files (.jam), or Jam Byte-Code Files (.jbc).

The JTAG pins support 1.5-V, 1.8-V, 2.5-V, or 3.3-V I/O standards. The supported voltage level and standard are determined by the  $V_{\rm CCIO}$  of the bank where it resides. The dedicated JTAG pins reside in Bank 1 of all MAX II devices.

MAX II devices support the JTAG instructions shown in Table 3–1.

**Table 3–1.** MAX II JTAG Instructions (Part 1 of 2)

| JTAG Instruction | Instruction Code | Description                                                                                                                                                                                                                                       |

|------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SAMPLE/PRELOAD   | 00 0000 0101     | Allows a snapshot of signals at the device pins to be captured and examined during normal device operation, and permits an initial data pattern to be output at the device pins.                                                                  |

| EXTEST (1)       | 00 0000 1111     | Allows the external circuitry and board-level interconnects to be tested by forcing a test pattern at the output pins and capturing test results at the input pins.                                                                               |

| BYPASS           | 11 1111 1111     | Places the 1-bit bypass register between the TDI and TDO pins, which allows the BST data to pass synchronously through selected devices to adjacent devices during normal device operation.                                                       |

| USERCODE         | 00 0000 0111     | Selects the 32-bit USERCODE register and places it between the TDI and TDO pins, allowing the USERCODE to be serially shifted out of TDO. This register defaults to all 1's if not specified in the Quartus II software.                          |

| IDCODE           | 00 0000 0110     | Selects the IDCODE register and places it between TDI and TDO, allowing the IDCODE to be serially shifted out of TDO.                                                                                                                             |

| HIGHZ (1)        | 00 0000 1011     | Places the 1-bit bypass register between the TDI and TDO pins, which allows the boundary scan test data to pass synchronously through selected devices to adjacent devices during normal device operation, while tri-stating all of the I/O pins. |

## I/O Pins Remain Tri-Stated during Power-Up

A device that does not support hot-socketing may interrupt system operation or cause contention by driving out before or during power-up. In a hot socketing situation, the MAX II device's output buffers are turned off during system power-up. MAX II devices do not drive out until the device attains proper operating conditions and is fully configured. Refer to "Power-On Reset Circuitry" on page 4–5 for information about turn-on voltages.

## Signal Pins Do Not Drive the $V_{cco}$ or $V_{ccint}$ Power Supplies

MAX II devices do not have a current path from I/O pins or GCLK[3..0] pins to the  $V_{\text{CCIO}}$  or  $V_{\text{CCINT}}$  pins before or during power-up. A MAX II device may be inserted into (or removed from) a system board that was powered up without damaging or interfering with system-board operation. When hot socketing, MAX II devices may have a minimal effect on the signal integrity of the backplane.

## **AC and DC Specifications**

You can power up or power down the  $V_{\text{CCIO}}$  and  $V_{\text{CCINT}}$  pins in any sequence. During hot socketing, the I/O pin capacitance is less than 8 pF. MAX II devices meet the following hot socketing specifications:

- The hot socketing DC specification is:  $|I_{IOPIN}| < 300 \,\mu\text{A}$ .

- The hot socketing AC specification is:  $|I_{IOPIN}|$  < 8 mA for 10 ns or less.

MAX II devices are immune to latch-up when hot socketing. If the TCK JTAG input pin is driven high during hot socketing, the current on that pin might exceed the specifications above.

$I_{\text{IOPIN}}$  is the current at any user I/O pin on the device. The AC specification applies when the device is being powered up or powered down. This specification takes into account the pin capacitance but not board trace and external loading capacitance. Additional capacitance for trace, connector, and loading must be taken into consideration separately. The peak current duration due to power-up transients is 10 ns or less.

The DC specification applies when all  $V_{\text{CC}}$  supplies to the device are stable in the powered-up or powered-down conditions.

## **Hot Socketing Feature Implementation in MAX II Devices**

The hot socketing feature turns off (tri-states) the output buffer during the power-up event (either  $V_{\text{CCINT}}$  or  $V_{\text{CCIO}}$  supplies) or power-down event. The hot-socket circuit generates an internal HOTSCKT signal when either  $V_{\text{CCINT}}$  or  $V_{\text{CCIO}}$  is below the threshold voltage during power-up or power-down. The HOTSCKT signal cuts off the output buffer to make sure that no DC current (except for weak pull-up leaking) leaks through the pin. When  $V_{\text{CC}}$  ramps up very slowly during power-up,  $V_{\text{CC}}$  may still be relatively low even after the power-on reset (POR) signal is released and device configuration is complete.

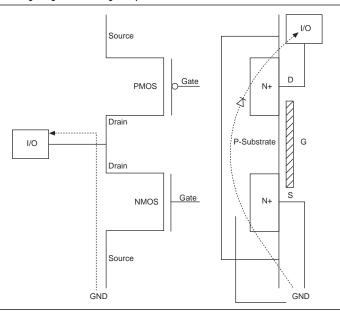

When the I/O pin receives a negative ESD zap at the pin that is less than -0.7 V (0.7 V is the voltage drop across a diode), the intrinsic

P-Substrate/N+ drain diode is forward biased. Therefore, the discharge ESD current path is from GND to the I/O pin, as shown in Figure 4–4.

Figure 4-4. ESD Protection During Negative Voltage Zap

## **Power-On Reset Circuitry**

MAX II devices have POR circuits to monitor  $V_{\text{CCINT}}$  and  $V_{\text{CCIO}}$  voltage levels during power-up. The POR circuit monitors these voltages, triggering download from the non-volatile configuration flash memory (CFM) block to the SRAM logic, maintaining tri-state of the I/O pins (with weak pull-up resistors enabled) before and during this process. When the MAX II device enters user mode, the POR circuit releases the I/O pins to user functionality. The POR circuit of the MAX II (except MAX IIZ) device continues to monitor the  $V_{\text{CCINT}}$  voltage level to detect a brown-out condition. The POR circuit of the MAX IIZ device does not monitor the  $V_{\text{CCINT}}$  voltage level after the device enters into user mode. More details are provided in the following sub-sections.

MII51005-2.5

## Introduction

System designers must consider the recommended DC and switching conditions discussed in this chapter to maintain the highest possible performance and reliability of the MAX® II devices. This chapter contains the following sections:

- "Operating Conditions" on page 5–1

- "Power Consumption" on page 5–8

- "Timing Model and Specifications" on page 5–8

## **Operating Conditions**

Table 5–1 through Table 5–12 provide information about absolute maximum ratings, recommended operating conditions, DC electrical characteristics, and other specifications for MAX II devices.

## **Absolute Maximum Ratings**

Table 5–1 shows the absolute maximum ratings for the MAX II device family.

**Table 5–1.** MAX II Device Absolute Maximum Ratings (Note 1), (2)

| Parameter                      | Conditions                                                                                                                                  | Minimum                                                                                                                                                                                                                                     | Maximum                                                                                                                                                                                                                                                            | Unit                                                                                                                                                                                                                                                                                  |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Internal supply voltage (3)    | With respect to ground                                                                                                                      | -0.5                                                                                                                                                                                                                                        | 4.6                                                                                                                                                                                                                                                                | V                                                                                                                                                                                                                                                                                     |

| I/O supply voltage             | _                                                                                                                                           | -0.5                                                                                                                                                                                                                                        | 4.6                                                                                                                                                                                                                                                                | V                                                                                                                                                                                                                                                                                     |

| DC input voltage               | _                                                                                                                                           | -0.5                                                                                                                                                                                                                                        | 4.6                                                                                                                                                                                                                                                                | V                                                                                                                                                                                                                                                                                     |

| DC output current, per pin (4) | _                                                                                                                                           | -25                                                                                                                                                                                                                                         | 25                                                                                                                                                                                                                                                                 | mA                                                                                                                                                                                                                                                                                    |

| Storage temperature            | No bias                                                                                                                                     | -65                                                                                                                                                                                                                                         | 150                                                                                                                                                                                                                                                                | °C                                                                                                                                                                                                                                                                                    |

| Ambient temperature            | Under bias (5)                                                                                                                              | -65                                                                                                                                                                                                                                         | 135                                                                                                                                                                                                                                                                | °C                                                                                                                                                                                                                                                                                    |

| Junction temperature           | TQFP and BGA packages under bias                                                                                                            | _                                                                                                                                                                                                                                           | 135                                                                                                                                                                                                                                                                | °C                                                                                                                                                                                                                                                                                    |

|                                | Internal supply voltage (3)  I/O supply voltage  DC input voltage  DC output current, per pin (4)  Storage temperature  Ambient temperature | Internal supply voltage (3) With respect to ground  I/O supply voltage —  DC input voltage —  DC output current, per pin (4) —  Storage temperature No bias  Ambient temperature Under bias (5)  Junction temperature TQFP and BGA packages | Internal supply voltage (3) With respect to ground -0.5  I/O supply voltage -0.5  DC input voltage -0.5  DC output current, per pin (4) -25  Storage temperature No bias -65  Ambient temperature Under bias (5) -65  Junction temperature TQFP and BGA packages - | Internal supply voltage (3) With respect to ground -0.5 4.6  I/O supply voltage0.5 4.6  DC input voltage0.5 4.6  DC output current, per pin (4)25 25  Storage temperature No bias -65 150  Ambient temperature Under bias (5) -65 135  Junction temperature TQFP and BGA packages 135 |

#### Notes to Table 5-1:

- (1) Refer to the Operating Requirements for Altera Devices Data Sheet.

- (2) Conditions beyond those listed in Table 5–1 may cause permanent damage to a device. Additionally, device operation at the absolute maximum ratings for extended periods of time may have adverse affects on the device.

- (3) Maximum V<sub>CCINT</sub> for MAX II devices is 4.6 V. For MAX IIG and MAX IIZ devices, it is 2.4 V.

- (4) Refer to AN 286: Implementing LED Drivers in MAX & MAX II Devices for more information about the maximum source and sink current for MAX II devices.

- (5) Refer to Table 5-2 for information about "under bias" conditions.

**Table 5–6.** 3.3-V LVCMOS Specifications (Part 2 of 2)

| Symbol          | Parameter                 | Conditions                                      | Minimum                 | Maximum | Unit |

|-----------------|---------------------------|-------------------------------------------------|-------------------------|---------|------|

| V <sub>OH</sub> | High-level output voltage | $V_{ccio} = 3.0$ , $IOH = -0.1 \text{ mA } (1)$ | V <sub>ccio</sub> - 0.2 | _       | V    |

| V <sub>oL</sub> | Low-level output voltage  | $V_{ccio} = 3.0,$ $IOL = 0.1 \text{ mA } (1)$   | _                       | 0.2     | V    |

Table 5-7. 2.5-V I/O Specifications

| Symbol            | Parameter                 | Conditions        | Minimum | Maximum | Unit |

|-------------------|---------------------------|-------------------|---------|---------|------|

| V <sub>CCIO</sub> | I/O supply voltage        | _                 | 2.375   | 2.625   | V    |

| V <sub>IH</sub>   | High-level input voltage  | _                 | 1.7     | 4.0     | V    |

| V <sub>IL</sub>   | Low-level input voltage   | _                 | -0.5    | 0.7     | V    |

| V <sub>OH</sub>   | High-level output voltage | IOH = -0.1 mA (1) | 2.1     | _       | V    |

|                   |                           | IOH = -1 mA (1)   | 2.0     | _       | V    |

|                   |                           | IOH = -2 mA (1)   | 1.7     | _       | V    |

| Vol               | Low-level output voltage  | IOL = 0.1 mA (1)  |         | 0.2     | V    |

|                   |                           | IOL = 1 mA (1)    | _       | 0.4     | V    |

|                   |                           | IOL = 2 mA (1)    |         | 0.7     | V    |

Table 5-8. 1.8-V I/O Specifications

| Symbol            | Parameter                 | Conditions      | Minimum                  | Maximum                  | Unit |

|-------------------|---------------------------|-----------------|--------------------------|--------------------------|------|

| V <sub>CCIO</sub> | I/O supply voltage        | _               | 1.71                     | 1.89                     | V    |

| V <sub>IH</sub>   | High-level input voltage  | _               | 0.65 × V <sub>cc10</sub> | 2.25 (2)                 | V    |

| V <sub>IL</sub>   | Low-level input voltage   | _               | -0.3                     | 0.35 × V <sub>ccio</sub> | ٧    |

| V <sub>OH</sub>   | High-level output voltage | IOH = -2 mA (1) | V <sub>ccio</sub> - 0.45 | _                        | ٧    |

| V <sub>oL</sub>   | Low-level output voltage  | IOL = 2 mA (1)  | _                        | 0.45                     | V    |

Table 5-9. 1.5-V I/O Specifications

| Symbol            | Parameter                 | Conditions      | Minimum                  | Maximum                     | Unit |

|-------------------|---------------------------|-----------------|--------------------------|-----------------------------|------|

| V <sub>ccio</sub> | I/O supply voltage        | _               | 1.425                    | 1.575                       | V    |

| V <sub>IH</sub>   | High-level input voltage  | _               | 0.65 × V <sub>ccio</sub> | V <sub>ccio</sub> + 0.3 (2) | ٧    |

| V <sub>IL</sub>   | Low-level input voltage   | _               | -0.3                     | 0.35 × V <sub>ccio</sub>    | V    |

| V <sub>OH</sub>   | High-level output voltage | IOH = -2 mA (1) | 0.75 × V <sub>ccio</sub> | _                           | V    |

| VoL               | Low-level output voltage  | IOL = 2 mA (1)  | _                        | 0.25 × V <sub>ccio</sub>    | V    |

#### Notes to Table 5-5 through Table 5-9:

- (1) This specification is supported across all the programmable drive strength settings available for this I/O standard, as shown in the MAX II Architecture chapter (I/O Structure section) in the MAX II Device Handbook.

- (2) This maximum  $V_{IH}$  reflects the JEDEC specification. The MAX II input buffer can tolerate a  $V_{IH}$  maximum of 4.0, as specified by the  $V_{II}$  parameter in Table 5–2.

Table 5-21. UFM Block Internal Timing Microparameters (Part 2 of 3)

|                   |                                                                                                |                          | M   | IAX II / | MAX II      | G           |     | MAX IIZ |             |     |             |     |             |      |

|-------------------|------------------------------------------------------------------------------------------------|--------------------------|-----|----------|-------------|-------------|-----|---------|-------------|-----|-------------|-----|-------------|------|

|                   |                                                                                                | −3 S <sub>l</sub><br>Gra |     |          | peed<br>ade | −5 S<br>Gra |     |         | peed<br>ade |     | peed<br>ade |     | peed<br>ade |      |

| Symbol            | Parameter                                                                                      | Min                      | Max | Min      | Max         | Min         | Max | Min     | Max         | Min | Max         | Min | Max         | Unit |

| $t_{	exttt{DDS}}$ | Data register data in setup to data register clock                                             | 20                       | _   | 20       | _           | 20          | _   | 20      | _           | 20  | _           | 20  | _           | ns   |

| t <sub>DDH</sub>  | Data register data in<br>hold from data<br>register clock                                      | 20                       | _   | 20       | _           | 20          | _   | 20      | _           | 20  | _           | 20  | _           | ns   |

| t <sub>DP</sub>   | Program signal to data clock hold time                                                         | 0                        | _   | 0        | _           | 0           | _   | 0       | _           | 0   | _           | 0   | _           | ns   |

| t <sub>PB</sub>   | Maximum delay<br>between program<br>rising edge to UFM<br>busy signal rising<br>edge           |                          | 960 | _        | 960         |             | 960 | _       | 960         | _   | 960         | _   | 960         | ns   |

| t <sub>BP</sub>   | Minimum delay<br>allowed from UFM<br>busy signal going low<br>to program signal<br>going low   | 20                       | _   | 20       | _           | 20          | _   | 20      | _           | 20  | _           | 20  | _           | ns   |

| t <sub>PPMX</sub> | Maximum length of busy pulse during a program                                                  |                          | 100 | _        | 100         | _           | 100 | _       | 100         | _   | 100         | _   | 100         | μs   |

| t <sub>AE</sub>   | Minimum erase signal<br>to address clock hold<br>time                                          | 0                        | _   | 0        | _           | 0           | _   | 0       | _           | 0   | _           | 0   | _           | ns   |

| t <sub>EB</sub>   | Maximum delay<br>between the erase<br>rising edge to the<br>UFM busy signal<br>rising edge     |                          | 960 | _        | 960         |             | 960 | _       | 960         | _   | 960         | _   | 960         | ns   |

| t <sub>BE</sub>   | Minimum delay<br>allowed from the UFM<br>busy signal going low<br>to erase signal going<br>low | 20                       | _   | 20       | _           | 20          | _   | 20      | _           | 20  | _           | 20  | _           | ns   |

| t <sub>EPMX</sub> | Maximum length of busy pulse during an erase                                                   | _                        | 500 | _        | 500         | _           | 500 | _       | 500         | _   | 500         | _   | 500         | ms   |

| t <sub>DCO</sub>  | Delay from data<br>register clock to data<br>register output                                   | _                        | 5   | _        | 5           | _           | 5   | _       | 5           | _   | 5           | _   | 5           | ns   |

## **External Timing Parameters**

External timing parameters are specified by device density and speed grade. All external I/O timing parameters shown are for the 3.3-V LVTTL I/O standard with the maximum drive strength and fast slew rate. For external I/O timing using standards other than LVTTL or for different drive strengths, use the I/O standard input and output delay adders in Table 5–27 through Table 5–31.

For more information about each external timing parameters symbol, refer to the *Understanding Timing in MAX II Devices* chapter in the *MAX II Device Handbook*.

Table 5–23 shows the external I/O timing parameters for EPM240 devices.

**Table 5–23.** EPM240 Global Clock External I/O Timing Parameters (Part 1 of 2)

|                  |                                                                          |           |                   | ı        | MAX II | MAX II       | G   |              |     |              | MA  | X IIZ        |     |              |      |

|------------------|--------------------------------------------------------------------------|-----------|-------------------|----------|--------|--------------|-----|--------------|-----|--------------|-----|--------------|-----|--------------|------|

|                  |                                                                          |           | -3 Speed<br>Grade |          |        | Speed<br>ade |     | Speed<br>ade |     | Speed<br>ade |     | Speed<br>ade |     | Speed<br>ade | Ī    |

| Symbol           | Parameter                                                                | Condition | Min               | Max      | Min    | Max          | Min | Max          | Min | Max          | Min | Max          | Min | Max          | Unit |

| t <sub>PD1</sub> | Worst case<br>pin-to-pin<br>delay<br>through 1<br>look-up table<br>(LUT) | 10 pF     | _                 | 4.7      | _      | 6.1          | _   | 7.5          | _   | 7.9          | _   | 12.0         | _   | 14.0         | ns   |

| t <sub>PD2</sub> | Best case<br>pin-to-pin<br>delay<br>through<br>1 LUT                     | 10 pF     |                   | 3.7      | _      | 4.8          | _   | 5.9          | _   | 5.8          | _   | 7.8          | _   | 8.5          | ns   |

| t <sub>SU</sub>  | Global clock<br>setup time                                               | _         | 1.7               | _        | 2.2    | _            | 2.7 | _            | 2.4 | _            | 4.1 | _            | 4.6 | _            | ns   |

| t <sub>H</sub>   | Global clock<br>hold time                                                | _         | 0                 |          | 0      | _            | 0   | _            | 0   | _            | 0   | _            | 0   | _            | ns   |

| t <sub>co</sub>  | Global clock<br>to output<br>delay                                       | 10 pF     | 2.0               | 4.3      | 2.0    | 5.6          | 2.0 | 6.9          | 2.0 | 6.6          | 2.0 | 8.1          | 2.0 | 8.6          | ns   |

| t <sub>CH</sub>  | Global clock<br>high time                                                | _         | 166               | _        | 216    | _            | 266 | _            | 253 | _            | 335 | _            | 339 | _            | ps   |

| t <sub>CL</sub>  | Global clock<br>low time                                                 | _         | 166               | _        | 216    | _            | 266 | _            | 253 | _            | 335 | _            | 339 | _            | ps   |

| t <sub>CNT</sub> | Minimum<br>global clock<br>period for<br>16-bit<br>counter               | _         | 3.3               | <u>—</u> | 4.0    |              | 5.0 |              | 5.4 |              | 8.1 |              | 8.4 |              | ns   |

**Table 5–23.** EPM240 Global Clock External I/O Timing Parameters (Part 2 of 2)

|                  |                                                               |           | MAX II / MAX IIG  |           |                   |       |                   |       | MAX IIZ           |       |                   |       |                   |       |      |

|------------------|---------------------------------------------------------------|-----------|-------------------|-----------|-------------------|-------|-------------------|-------|-------------------|-------|-------------------|-------|-------------------|-------|------|

|                  |                                                               |           | -3 Speed<br>Grade |           | -4 Speed<br>Grade |       | –5 Speed<br>Grade |       | –6 Speed<br>Grade |       | -7 Speed<br>Grade |       | –8 Speed<br>Grade |       |      |

| Symbol           | Parameter                                                     | Condition | Min               | Max       | Min               | Max   | Min               | Max   | Min               | Max   | Min               | Max   | Min               | Max   | Unit |

| f <sub>CNT</sub> | Maximum<br>global clock<br>frequency for<br>16-bit<br>counter | _         | _                 | 304.0 (1) | _                 | 247.5 | _                 | 201.1 | _                 | 184.1 | _                 | 123.5 | _                 | 118.3 | MHz  |

#### Note to Table 5-23:

Table 5–24 shows the external I/O timing parameters for EPM570 devices.

**Table 5–24.** EPM570 Global Clock External I/O Timing Parameters (Part 1 of 2)

|                  |                                                                      |           |                | N   | ΛΑΧ II | / MAX I | IG  |             | MAX IIZ           |     |                   |      |                   |      |      |

|------------------|----------------------------------------------------------------------|-----------|----------------|-----|--------|---------|-----|-------------|-------------------|-----|-------------------|------|-------------------|------|------|

|                  |                                                                      |           | -3 Spo<br>Grad |     |        |         |     | peed<br>ade | -6 Speed<br>Grade |     | -7 Speed<br>Grade |      | -8 Speed<br>Grade |      |      |

| Symbol           | Parameter                                                            | Condition | Min            | Max | Min    | Max     | Min | Max         | Min               | Max | Min               | Max  | Min               | Max  | Unit |

| t <sub>PD1</sub> | Worst case pin-<br>to-pin delay<br>through 1 look-<br>up table (LUT) | 10 pF     | _              | 5.4 | _      | 7.0     | _   | 8.7         | _                 | 9.5 | _                 | 15.1 | _                 | 17.7 | ns   |

| t <sub>PD2</sub> | Best case pin-<br>to-pin delay<br>through 1 LUT                      | 10 pF     | _              | 3.7 | _      | 4.8     | _   | 5.9         | _                 | 5.7 | _                 | 7.7  | _                 | 8.5  | ns   |

| t <sub>su</sub>  | Global clock<br>setup time                                           | _         | 1.2            | _   | 1.5    | _       | 1.9 | _           | 2.2               | _   | 3.9               | _    | 4.4               | _    | ns   |

| t <sub>H</sub>   | Global clock<br>hold time                                            | _         | 0              | _   | 0      | _       | 0   | _           | 0                 | _   | 0                 | _    | 0                 | _    | ns   |

| t <sub>co</sub>  | Global clock to output delay                                         | 10 pF     | 2.0            | 4.5 | 2.0    | 5.8     | 2.0 | 7.1         | 2.0               | 6.7 | 2.0               | 8.2  | 2.0               | 8.7  | ns   |

| t <sub>cH</sub>  | Global clock<br>high time                                            | _         | 166            | _   | 216    | _       | 266 | _           | 253               | _   | 335               | _    | 339               | _    | ps   |

| t <sub>CL</sub>  | Global clock<br>low time                                             | _         | 166            | _   | 216    | _       | 266 | _           | 253               | _   | 335               | _    | 339               | _    | ps   |

| t <sub>cnt</sub> | Minimum<br>global clock<br>period for<br>16-bit counter              | _         | 3.3            |     | 4.0    | _       | 5.0 | _           | 5.4               | _   | 8.1               | _    | 8.4               | _    | ns   |

<sup>(1)</sup> The maximum frequency is limited by the I/O standard on the clock input pin. The 16-bit counter critical delay performs faster than this global clock input pin maximum frequency.

**Table 5–29.** External Timing Output Delay and  $t_{\mbox{\tiny OD}}$  Adders for Fast Slew Rate

|               |       |                                  | M     | AX II / | MAX IIG           | ì   |       |             |     | MA          | X IIZ |             |     |      |

|---------------|-------|----------------------------------|-------|---------|-------------------|-----|-------|-------------|-----|-------------|-------|-------------|-----|------|

|               |       | -3 Speed -4 Speed<br>Grade Grade |       | •       | –5 Speed<br>Grade |     |       | peed<br>ade |     | peed<br>ade |       | peed<br>ade |     |      |

| I/O Standa    | ırd   | Min                              | Max   | Min     | Max               | Min | Max   | Min         | Max | Min         | Max   | Min         | Max | Unit |

| 3.3-V LVTTL   | 16 mA | _                                | 0     | _       | 0                 | _   | 0     | _           | 0   | _           | 0     | _           | 0   | ps   |

|               | 8 mA  | _                                | 65    | _       | 84                | _   | 104   | _           | -6  | _           | -2    | _           | -3  | ps   |

| 3.3-V LVCMOS  | 8 mA  |                                  | 0     | _       | 0                 | _   | 0     | _           | 0   | _           | 0     | _           | 0   | ps   |

|               | 4 mA  | _                                | 65    | _       | 84                | _   | 104   | _           | -6  | _           | -2    | _           | -3  | ps   |

| 2.5-V LVTTL / | 14 mA | _                                | 122   | _       | 158               | _   | 195   | _           | -63 | _           | -71   | _           | -88 | ps   |

| LVCMOS        | 7 mA  |                                  | 193   | _       | 251               | _   | 309   | _           | 10  | _           | -1    | _           | 1   | ps   |

| 1.8-V LVTTL / | 6 mA  | _                                | 568   | _       | 738               | _   | 909   | _           | 128 | _           | 118   | _           | 118 | ps   |

| LVCMOS        | 3 mA  | _                                | 654   | _       | 850               | _   | 1,046 | _           | 352 | _           | 327   | _           | 332 | ps   |

| 1.5-V LVCMOS  | 4 mA  | _                                | 1,059 | _       | 1,376             | _   | 1,694 | _           | 421 | _           | 400   | _           | 400 | ps   |

|               | 2 mA  | _                                | 1,167 | _       | 1,517             | _   | 1,867 | _           | 757 | _           | 743   | _           | 743 | ps   |

| 3.3-V PCI     | 20 mA | _                                | 3     | _       | 4                 | _   | 5     | _           | -6  | _           | -2    | _           | -3  | ps   |

**Table 5–30.** External Timing Output Delay and  $t_{\tiny OD}$  Adders for Slow Slew Rate

|                         |       | MAX II / MAX IIG  |        |                   |        |                   | MAX IIZ |                   |        |                   |        |                   |        |      |

|-------------------------|-------|-------------------|--------|-------------------|--------|-------------------|---------|-------------------|--------|-------------------|--------|-------------------|--------|------|

|                         |       | -3 Speed<br>Grade |        | -4 Speed<br>Grade |        | –5 Speed<br>Grade |         | –6 Speed<br>Grade |        | –7 Speed<br>Grade |        | –8 Speed<br>Grade |        |      |

| I/O Standard            |       | Min               | Max    | Min               | Max    | Min               | Max     | Min               | Max    | Min               | Max    | Min               | Max    | Unit |

| 3.3-V LVTTL             | 16 mA | _                 | 7,064  | _                 | 6,745  | _                 | 6,426   | _                 | 5,966  | _                 | 5,992  | _                 | 6,118  | ps   |

|                         | 8 mA  | _                 | 7,946  | _                 | 7,627  | _                 | 7,308   | _                 | 6,541  | _                 | 6,570  | _                 | 6,720  | ps   |

| 3.3-V LVCMOS            | 8 mA  | _                 | 7,064  | _                 | 6,745  | _                 | 6,426   | _                 | 5,966  | _                 | 5,992  | _                 | 6,118  | ps   |

|                         | 4 mA  | _                 | 7,946  | _                 | 7,627  | _                 | 7,308   | _                 | 6,541  | _                 | 6,570  | _                 | 6,720  | ps   |

| 2.5-V LVTTL /<br>LVCMOS | 14 mA | _                 | 10,434 | _                 | 10,115 | _                 | 9,796   | _                 | 9,141  | _                 | 9,154  | _                 | 9,297  | ps   |

|                         | 7 mA  | _                 | 11,548 | _                 | 11,229 | _                 | 10,910  | _                 | 9,861  | _                 | 9,874  | _                 | 10,037 | ps   |

| 1.8-V LVTTL /<br>LVCMOS | 6 mA  | _                 | 22,927 | _                 | 22,608 | _                 | 22,289  | _                 | 21,811 | _                 | 21,854 | _                 | 21,857 | ps   |

|                         | 3 mA  | _                 | 24,731 | _                 | 24,412 | _                 | 24,093  | _                 | 23,081 | _                 | 23,034 | _                 | 23,107 | ps   |

| 1.5-V LVCMOS            | 4 mA  | _                 | 38,723 | _                 | 38,404 | _                 | 38,085  | _                 | 39,121 | _                 | 39,124 | _                 | 39,124 | ps   |

|                         | 2 mA  | _                 | 41,330 | _                 | 41,011 | _                 | 40,692  | _                 | 40,631 | _                 | 40,634 | _                 | 40,634 | ps   |

| 3.3-V PCI               | 20 mA | _                 | 261    | _                 | 339    | _                 | 418     | _                 | 6,644  | _                 | 6,627  | _                 | 6,914  | ps   |

**Table 5–34.** MAX II JTAG Timing Parameters (Part 2 of 2)

| Symbol                   | Parameter                                      | Min | Max | Unit |

|--------------------------|------------------------------------------------|-----|-----|------|

| t <sub>JPSU</sub>        | JTAG port setup time (2)                       | 8   | _   | ns   |

| t <sub>JPH</sub>         | JTAG port hold time                            | 10  | _   | ns   |

| t <sub>JPCO</sub>        | JTAG port clock to output (2)                  | _   | 15  | ns   |

| <b>t</b> <sub>JPZX</sub> | JTAG port high impedance to valid output (2)   | _   | 15  | ns   |

| t <sub>JPXZ</sub>        | JTAG port valid output to high impedance (2)   | _   | 15  | ns   |

| t <sub>JSSU</sub>        | Capture register setup time                    | 8   | _   | ns   |

| t <sub>эsн</sub>         | Capture register hold time                     | 10  | _   | ns   |

| t <sub>Jsco</sub>        | Update register clock to output                | _   | 25  | ns   |

| t <sub>JSZX</sub>        | Update register high impedance to valid output |     | 25  | ns   |

| t <sub>JSXZ</sub>        | Update register valid output to high impedance | _   | 25  | ns   |

#### Notes to Table 5-34:

- (1) Minimum clock period specified for 10 pF load on the TDO pin. Larger loads on TDO will degrade the maximum TCK frequency.

- (2) This specification is shown for 3.3-V LVTTL/LVCMOS and 2.5-V LVTTL/LVCMOS operation of the JTAG pins. For 1.8-V LVTTL/LVCMOS and 1.5-V LVCMOS, the t<sub>JPSU</sub> minimum is 6 ns and t<sub>JPCO</sub>, t<sub>JPZX</sub>, and t<sub>JPXZ</sub> are maximum values at 35 ns.

## **Referenced Documents**

This chapter references the following documents:

- I/O Structure section in the MAX II Architecture chapter in the MAX II Device Handbook

- Hot Socketing and Power-On Reset in MAX II Devices chapter in the MAX II Device Handbook

- Operating Requirements for Altera Devices Data Sheet

- PowerPlay Power Analysis chapter in volume 3 of the Quartus II Handbook

- Understanding and Evaluating Power in MAX II Devices chapter in the MAX II Device Handbook

- *Understanding Timing in MAX II Devices* chapter in the *MAX II Device Handbook*

- Using MAX II Devices in Multi-Voltage Systems chapter in the MAX II Device Handbook

## **Referenced Documents**

This chapter references the following document:

■ Package Information chapter in the MAX II Device Handbook

# **Document Revision History**

Table 6–1 shows the revision history for this chapter.

Table 6-1. Document Revision History

| Date and Revision             | Changes Made                                                                        | Summary of Changes                         |

|-------------------------------|-------------------------------------------------------------------------------------|--------------------------------------------|

| August 2009,<br>version 1.6   | ■ Updated Figure 6–1.                                                               | Added information for speed grade –8       |

| October 2008,<br>version 1.5  | ■ Updated New Document Format.                                                      | _                                          |

| December 2007,<br>version 1.4 | <ul><li>Added "Referenced Documents" section.</li><li>Updated Figure 6–1.</li></ul> | Updated document with MAX IIZ information. |

| December 2006,<br>version 1.3 | Added document revision history.                                                    | _                                          |

| October 2006,<br>version 1.2  | ■ Updated Figure 6-1.                                                               | _                                          |

| June 2005,<br>version 1.1     | Removed Dual Marking section.                                                       | _                                          |