Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | ARM® Cortex®-M0                                                             |

| Core Size                  | 32-Bit Single-Core                                                          |

| Speed                      | 24MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, Microwire, SmartCard, SPI, SSP, UART/USART  |

| Peripherals                | Brown-out Detect/Reset, CapSense, LCD, LVD, POR, PWM, WDT                   |

| Number of I/O              | 36                                                                          |

| Program Memory Size        | 32KB (32K x 8)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 4K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 5.5V                                                                |

| Data Converters            | A/D 8x12b SAR; D/A 2xIDAC                                                   |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-LQFP                                                                     |

| Supplier Device Package    | 44-TQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c4125axi-483t |

# **Contents**

| Functional Definition        | 5  |

|------------------------------|----|

| CPU and Memory Subsystem     | 5  |

| System Resources             | 5  |

| Analog Blocks                | 6  |

| Fixed Function Digital       | 7  |

| GPIO                         | 7  |

| Special Function Peripherals | 8  |

| Pinouts                      | 9  |

| Power                        | 15 |

| Unregulated External Supply  | 15 |

| Regulated External Supply    | 16 |

| Development Support          | 17 |

| Documentation                | 17 |

| Online                       | 17 |

| Tools                        | 17 |

| Electrical Specifications    | 18 |

| Absolute Maximum Ratings     | 18 |

| Davica Laval Specifications  |    |

| Analog Peripherals                      | 22 |

|-----------------------------------------|----|

| Digital Peripherals                     | 26 |

| Memory                                  | 29 |

|                                         | 29 |

| Ordering Information                    | 32 |

| Part Numbering Conventions              | 33 |

| Packaging                               | 34 |

| Acronyms                                | 38 |

| Document Conventions                    | 40 |

| Units of Measure                        | 40 |

| Revision History                        | 41 |

| Sales, Solutions, and Legal Information | 42 |

| Worldwide Sales and Design Support      | 42 |

| Products                                |    |

| PSoC® Solutions                         |    |

| Cypress Developer Community             |    |

| Technical Support                       |    |

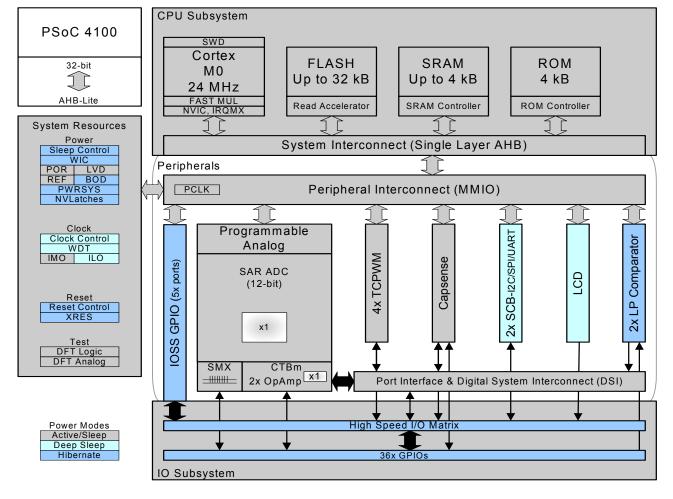

Figure 2. Block Diagram

The PSoC 4100 devices include extensive support for programming, testing, debugging, and tracing both hardware and firmware.

The ARM Serial\_Wire Debug (SWD) interface supports all programming and debug features of the device.

Complete debug-on-chip functionality enables full device debugging in the final system using the standard production device. It does not require special interfaces, debugging pods, simulators, or emulators. Only the standard programming connections are required to fully support debug.

The PSoC Creator Integrated Development Environment (IDE) provides fully integrated programming and debug support for the PSoC 4100 devices. The SWD interface is fully compatible with industry standard third party tools. With the ability to disable debug features, with very robust flash protection, and by allowing customer-proprietary functionality to be implemented in on-chip programmable blocks, the PSoC 4100 family provides a level of

security not possible with multi-chip application solutions or with microcontrollers.

The debug circuits are enabled by default and can only be disabled in firmware. If not enabled, the only way to re-enable them is to erase the entire device, clear flash protection, and reprogram the device with new firmware that enables debugging.

Additionally, all device interfaces can be permanently disabled (device security) for applications concerned about phishing attacks due to a maliciously reprogrammed device or attempts to defeat security by starting and interrupting flash programming sequences. Because all programming, debug, and test interfaces are disabled when maximum device security is enabled, PSoC 4100 with device security enabled may not be returned for failure analysis. This is a trade-off the PSoC 4100 allows the customer to make.

#### IMO Clock Source

The IMO is the primary source of internal clocking in the PSoC 4100. It is trimmed during testing to achieve the specified accuracy. Trim values are stored in nonvolatile latches (NVL). Additional trim settings from flash can be used to compensate for changes. The IMO default frequency is 24 MHz and it can be adjusted between 3 MHz to 24 MHz in steps of 1 MHz. The IMO tolerance with Cypress-provided calibration settings is ±2%.

#### ILO Clock Source

The ILO is a very low power oscillator, which is primarily used to generate clocks for peripheral operation in Deep Sleep mode. ILO-driven counters can be calibrated to the IMO to improve accuracy. Cypress provides a software component, which does the calibration.

#### Watchdog Timer

A watchdog timer is implemented in the clock block running from the ILO; this allows watchdog operation during Deep Sleep and generates a watchdog reset if not serviced before the timeout occurs. The watchdog reset is recorded in the Reset Cause register.

#### Reset

PSoC 4100 can be reset from a variety of sources including a software reset. Reset events are asynchronous and guarantee reversion to a known state. The reset cause is recorded in a register, which is sticky through reset and allows software to determine the cause of the reset. An XRES pin is reserved for external reset to avoid complications with configuration and multiple pin functions during power-on or reconfiguration. The XRES pin has an internal pull-up resistor that is always enabled.

#### Voltage Reference

The PSoC 4100 reference system generates all internally required references. A 1% voltage reference spec is provided for the 12-bit ADC. To allow better signal to noise ratios (SNR) and better absolute accuracy, it is possible to bypass the internal reference using a GPIO pin or to use an external reference for the SAR.

#### **Analog Blocks**

#### 12-bit SAR ADC

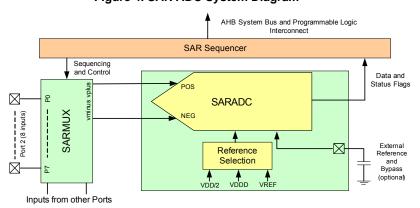

The 12-bit 806 ksps SAR ADC can operate at a maximum clock rate of 14.5 MHz and requires a minimum of 18 clocks at that frequency to do a 12-bit conversion.

The block functionality is augmented for the user by adding a reference buffer to it (trimmable to  $\pm 1\%$ ) and by providing the choice (for the PSoC 4100 case) of three internal voltage references:  $V_{DD},\,V_{DD}/2,\,$  and  $V_{REF}$  (nominally 1.024 V) as well as an external reference through a GPIO pin. The sample-and-hold (S/H) aperture is programmable allowing the gain bandwidth requirements of the amplifier driving the SAR inputs, which determine its settling time, to be relaxed if required. System performance will be 65 dB for true 12-bit precision providing appropriate references are used and system noise levels permit. To improve performance in noisy conditions, it is possible to provide an external bypass (through a fixed pin location) for the internal reference amplifier.

The SAR is connected to a fixed set of pins through an 8-input sequencer. The sequencer cycles through selected channels autonomously (sequencer scan) and does so with zero switching overhead (that is, aggregate sampling bandwidth is equal to 806 ksps whether it is for a single channel or distributed over several channels). The sequencer switching is effected through a state machine or through firmware driven switching. A feature provided by the sequencer is buffering of each channel to reduce CPU interrupt service requirements. To accommodate signals with varying source impedance and frequency, it is possible to have different sample times programmable for each channel. Also, signal range specification through a pair of range registers (low and high range values) is implemented with a corresponding out-of-range interrupt if the digitized value exceeds the programmed range; this allows fast detection of out-of-range values without the necessity of having to wait for a sequencer scan to be completed and the CPU to read the values and check for out-of-range values in software.

The SAR is able to digitize the output of the on-board temperature sensor for calibration and other temperature-dependent functions. The SAR is not available in Deep Sleep and Hibernate modes as it requires a high-speed clock (up to 18 MHz). The SAR operating range is 1.71 V to 5.5 V.

Figure 4. SAR ADC System Diagram

#### Two Opamps (CTBm Block)

PSoC 4100 has two opamps with Comparator modes which allow most common analog functions to be performed on-chip eliminating external components; PGAs, voltage buffers, filters, trans-impedance amplifiers, and other functions can be realized with external passives saving power, cost, and space. The on-chip opamps are designed with enough bandwidth to drive the S/H circuit of the ADC without requiring external buffering.

#### Temperature Sensor

PSoC 4100 has one on-chip temperature sensor This consists of a diode, which is biased by a current source that can be disabled to save power. The temperature sensor is connected to the ADC, which digitizes the reading and produces a temperature value using Cypress supplied software that includes calibration and linearization.

#### Low-power Comparators

PSoC 4100 has a pair of low-power comparators, which can also operate in the Deep Sleep and Hibernate modes. This allows the analog system blocks to be disabled while retaining the ability to monitor external voltage levels during low-power modes. The comparator outputs are normally synchronized to avoid metastability unless operating in an asynchronous power mode (Hibernate) where the system wake-up circuit is activated by a comparator switch event.

#### **Fixed Function Digital**

#### Timer/Counter/PWM Block (TCPWM)

The TCPWM block consists of four 16-bit counters with user-programmable period length. There is a Capture register to record the count value at the time of an event (which may be an I/O event), a period register which is used to either stop or auto-reload the counter when its count is equal to the period register, and compare registers to generate compare value signals which are used as PWM duty cycle outputs. The block also provides true and complementary outputs with programmable offset between them to allow use as deadband programmable complementary PWM outputs. It also has a Kill input to force outputs to a predetermined state; for example, this is used in motor drive systems when an overcurrent state is indicated and the PWMs driving the FETs need to be shut off immediately with no time for software intervention.

#### Serial Communication Blocks (SCB)

The PSoC 4100 has two SCBs, which can each implement an  $I^2$ C, UART, or SPI interface.

**I<sup>2</sup>C Mode**: The hardware I<sup>2</sup>C block implements a full multi-master and slave interface (it is capable of multimaster arbitration). This block is capable of operating at speeds of up to 1 Mbps (Fast Mode Plus) and has flexible buffering options to reduce interrupt overhead and latency for the CPU. The FIFO mode is available in all channels and is very useful in the absence of DMA.

The I<sup>2</sup>C peripheral is compatible with the I<sup>2</sup>C Standard-mode, Fast-mode, and Fast-Mode Plus devices as defined in the NXP I<sup>2</sup>C-bus specification and user manual (UM10204). The I<sup>2</sup>C bus I/O is implemented with GPIO in open-drain modes. The I<sup>2</sup>C bus uses open-drain drivers for clock and data with pull-up resistors on the bus for clock and data connected to all nodes. The required Rise and Fall times for different I<sup>2</sup>C speeds are guaranteed by using appropriate pull-up resistor values depending on VDD, Bus Capacitance, and resistor tolerance. For detailed information on how to calculate the optimum pull-up resistor value for your design, refer to the UM10204 I2C bus specification and user manual (the latest revision is available at www.nxp.com).

PSoC 4100 is not completely compliant with the I<sup>2</sup>C spec in the following respects:

- GPIO cells are not overvoltage-tolerant and, therefore, cannot be hot-swapped or powered up independently of the rest of the I<sup>2</sup>C system.

- Fast-mode Plus has an I<sub>OL</sub> specification of 20 mA at a V<sub>OL</sub> of 0.4 V. The GPIO cells can sink a maximum of 8-mA I<sub>OL</sub> with a V<sub>OL</sub> maximum of 0.6 V.

- Fast-mode and Fast-mode Plus specify minimum Fall times, which are not met with the GPIO cell; Slow strong mode can help meet this spec depending on the Bus Load.

- When the SCB is an I<sup>2</sup>C master, it interposes an IDLE state between NACK and Repeated Start; the I<sup>2</sup>C spec defines Bus free as following a Stop condition so other Active Masters do not intervene but a Master that has just become activated may start an Arbitration cycle.

- When the SCB is in I<sup>2</sup>C slave mode, and Address Match on External Clock is enabled (EC\_AM = 1) along with operation in the internally clocked mode (EC\_OP = 0), then its I<sup>2</sup>C address must be even.

**UART Mode**: This is a full-feature UART operating at up to 1 Mbps. It supports automotive single-wire interface (LIN), infrared interface (IrDA), and SmartCard (ISO7816) protocols, all of which are minor variants of the basic UART protocol. In addition, it supports the 9-bit multiprocessor mode that allows addressing of peripherals connected over common RX and TX lines. Common UART functions such as parity error, break detect, and frame error are supported. An 8-deep FIFO allows much greater CPU service latencies to be tolerated.

**SPI Mode**: The SPI mode supports full Motorola SPI, TI SSP (essentially adds a start pulse used to synchronize SPI Codecs), and National Microwire (half-duplex form of SPI). The SPI block can use the FIFO.

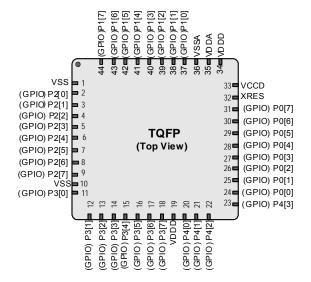

# **Pinouts**

The following is the pin-list for PSoC 4100 (44-TQFP, 40-QFN, 28-SSOP, and 48-TQFP). Port 2 comprises of the high-speed Analog inputs for the SAR Mux. P1.7 is the optional external input and bypass for the SAR reference. Ports 3 and 4 contain the Digital Communication channels. All pins support CSD CapSense and analog mux bus connections.

| 44  | 4-TQFP | 40  | -QFN | 28-SSOP |      | 48  | 3-TQFP |               | Alte        | ernate Functions f | or Pins         |                    | Dia Description                              |

|-----|--------|-----|------|---------|------|-----|--------|---------------|-------------|--------------------|-----------------|--------------------|----------------------------------------------|

| Pin | Name   | Pin | Name | Pin     | Name | Pin | Name   | Analog        | Alt 1       | Alt 2              | Alt 3           | Alt 4              | - Pin Description                            |

| 1   | VSS    | -   | -    | -       | -    | -   | -      | -             | _           | -                  | -               | _                  | Ground                                       |

| 2   | P2.0   | 1   | P2.0 | -       | -    | 2   | P2.0   | sarmux.0      | -           | -                  | -               | _                  | Port 2 Pin 0: gpio, lcd, csd, sarmux         |

| 3   | P2.1   | 2   | P2.1 | -       | -    | 3   | P2.1   | sarmux.1      | -           | -                  | -               | _                  | Port 2 Pin 1: gpio, lcd, csd, sarmux         |

| 4   | P2.2   | 3   | P2.2 | 5       | P2.2 | 4   | P2.2   | sarmux.2      | -           | -                  | -               | _                  | Port 2 Pin 2: gpio, lcd, csd, sarmux         |

| 5   | P2.3   | 4   | P2.3 | 6       | P2.3 | 5   | P2.3   | sarmux.3      | -           | -                  | -               | ı                  | Port 2 Pin 3: gpio, lcd, csd, sarmux         |

| 6   | P2.4   | 5   | P2.4 | 7       | P2.4 | 6   | P2.4   | sarmux.4      | tcpwm0_p[1] | _                  | _               | _                  | Port 2 Pin 4: gpio, lcd, csd, sarmux, pwm    |

| 7   | P2.5   | 6   | P2.5 | 8       | P2.5 | 7   | P2.5   | sarmux.5      | tcpwm0_n[1] | -                  | -               | _                  | Port 2 Pin 5: gpio, lcd, csd, sarmux, pwm    |

| 8   | P2.6   | 7   | P2.6 | 9       | P2.6 | 8   | P2.6   | sarmux.6      | tcpwm1_p[1] | _                  | -               | ı                  | Port 2 Pin 6: gpio, lcd, csd, sarmux, pwm    |

| 9   | P2.7   | 8   | P2.7 | 10      | P2.7 | 9   | P2.7   | sarmux.7      | tcpwm1_n[1] | -                  | -               | _                  | Port 2 Pin 7: gpio, lcd, csd, sarmux, pwm    |

| 10  | VSS    | 9   | VSS  | -       | -    | -   | -      | -             | -           | -                  | -               | _                  | Ground                                       |

| -   | -      | 1   | -    | -       | -    | 10  | NC     | -             | -           | -                  | -               | -                  | No Connect                                   |

| -   | _      | -   | -    | -       | -    | 11  | NC     | -             | -           | -                  | -               | _                  | No Connect                                   |

| 11  | P3.0   | 10  | P3.0 | 11      | P3.0 | 12  | P3.0   | -             | tcpwm0_p[0] | scb1_uart_rx[0]    | scb1_i2c_scl[0] | scb1_spi_mosi[0]   | Port 3 Pin 0: gpio, lcd, csd, pwm, scb1      |

| 12  | P3.1   | 11  | P3.1 | 12      | P3.1 | 13  | P3.1   | -             | tcpwm0_n[0] | scb1_uart_tx[0]    | scb1_i2c_sda[0] | scb1_spi_miso[0]   | Port 3 Pin 1: gpio, lcd, csd, pwm, scb1      |

| 13  | P3.2   | 12  | P3.2 | 13      | P3.2 | 14  | P3.2   | -             | tcpwm1_p[0] | _                  | swd_io[0]       | scb1_spi_clk[0]    | Port 3 Pin 2: gpio, lcd, csd, pwm, scb1, swd |

| -   | _      | -   | -    | -       | -    | 15  | VSSD   | -             | -           | -                  | -               | _                  | Ground                                       |

| 14  | P3.3   | 13  | P3.3 | 14      | P3.3 | 16  | P3.3   | -             | tcpwm1_n[0] | _                  | swd_clk[0]      | scb1_spi_ssel_0[0] | Port 3 Pin 3: gpio, lcd, csd, pwm, scb1, swd |

| 15  | P3.4   | 14  | P3.4 | -       | -    | 17  | P3.4   | -             | tcpwm2_p[0] | -                  | -               | scb1_spi_ssel_1    | Port 3 Pin 4: gpio, lcd, csd, pwm, scb1      |

| 16  | P3.5   | 15  | P3.5 | -       | -    | 18  | P3.5   | -             | tcpwm2_n[0] | -                  | -               | scb1_spi_ssel_2    | Port 3 Pin 5: gpio, lcd, csd, pwm, scb1      |

| 17  | P3.6   | 16  | P3.6 | -       | -    | 19  | P3.6   | -             | tcpwm3_p[0] | _                  | swd_io[1]       | scb1_spi_ssel_3    | Port 3 Pin 6: gpio, lcd, csd, pwm, scb1, swd |

| 18  | P3.7   | 17  | P3.7 | -       | -    | 20  | P3.7   | -             | tcpwm3_n[0] | -                  | swd_clk[1]      | _                  | Port 3 Pin 7: gpio, lcd, csd, pwm, swd       |

| 19  | VDDD   | -   | -    | -       | -    | 21  | VDDD   | -             | -           | -                  | -               | _                  | Digital Supply, 1.8 - 5.5V                   |

| 20  | P4.0   | 18  | P4.0 | 15      | P4.0 | 22  | P4.0   | -             | -           | scb0_uart_rx       | scb0_i2c_scl    | scb0_spi_mosi      | Port 4 Pin 0: gpio, lcd, csd, scb0           |

| 21  | P4.1   | 19  | P4.1 | 16      | P4.1 | 23  | P4.1   | -             | -           | scb0_uart_tx       | scb0_i2c_sda    | scb0_spi_miso      | Port 4 Pin 1: gpio, lcd, csd, scb0           |

| 22  | P4.2   | 20  | P4.2 | 17      | P4.2 | 24  | P4.2   | csd_c_mod     | _           | -                  | -               | scb0_spi_clk       | Port 4 Pin 2: gpio, lcd, csd, scb0           |

| 23  | P4.3   | 21  | P4.3 | 18      | P4.3 | 25  | P4.3   | csd_c_sh_tank | -           | -                  | -               | scb0_spi_ssel_0    | Port 4 Pin 3: gpio, lcd, csd, scb0           |

| _   | _      | _   | -    | -       | -    | 26  | NC     | _             | -           | _                  | -               | -                  | No Connect                                   |

| _   |        | _   | -    | -       | -    | 27  | NC     | _             | -           | _                  | -               | -                  | No Connect                                   |

Document Number: 001-87220 Rev. \*H

(GPIO) P1.6 (GPIO) P1.5 (GPIO) P1.4 (GPIO) P1.3 (GPIO) P1.1 (GPIO) P1.0 (GPIO) P1.2 (GPIO) (G (GPIO)P1.7/VREF 1 XRES (GPIO) P2.0 2 35 GPIO) P0.7 (GPIO) P2.1 34 GPIO) P0.6 (GPIO) P2.2 33 GPIO) P0.5 (GPIO) P2.3 32 GPIO) P0.4 **48 TQFP** (GPIO) P2.4 (GPIO) P0.3 **Top View** (GPIO) P2.5 30 GPIO) P0.2 29 GPIO) P0.1 (GPIO) P2.6 (GPIO) P2.7 28 GPIO) P0.0 NC NC NC NC 25 GPIO) P4.3 (GPIO) P3.0 12 (GPIO) P4.0 (GPIO) P4.1 (GPIO) P3.2 (GPIO) P3.3 (GPIO) P3.4 (GPIO) P3.5 (GPIO) P3.6 (GPIO) P3.7 (GPIO) P4.2 (GPIO) P3.1

Figure 5. 48-Pin TQFP Pinout

Figure 6. 44-pin TQFP Part Pinout

Table 2. DC Specifications (continued)

| Spec ID#  | Parameter                                                                | Description                                        | Min | Тур | Max  | Units | Details/<br>Conditions         |  |  |  |  |  |

|-----------|--------------------------------------------------------------------------|----------------------------------------------------|-----|-----|------|-------|--------------------------------|--|--|--|--|--|

| Deep Slee | p Mode, V <sub>DD</sub> =                                                |                                                    |     |     |      |       |                                |  |  |  |  |  |

| SID34     | IDD29                                                                    | I <sup>2</sup> C wakeup and WDT on                 | 1   | 1.5 | 15   | μA    | Typ at 25 °C<br>Max at 85 °C   |  |  |  |  |  |

| Deep Slee | Deep Sleep Mode, V <sub>DD</sub> = 1.71 V to 1.89 V (Regulator bypassed) |                                                    |     |     |      |       |                                |  |  |  |  |  |

| SID37     | IDD32                                                                    | I <sup>2</sup> C wakeup and WDT on.                | -   | 1.7 | -    | μA    | T = 25 °C                      |  |  |  |  |  |

| SID38     | IDD33                                                                    | I <sup>2</sup> C wakeup and WDT on                 | -   | _   | 60   | μΑ    | T = 85 °C                      |  |  |  |  |  |

| Deep Slee | p Mode, +105 °                                                           | C                                                  |     |     |      |       |                                |  |  |  |  |  |

| SID33Q    | IDD28Q                                                                   | I <sup>2</sup> C wakeup and WDT on. Regulator Off. | _   | _   | 135  | μA    | V <sub>DD</sub> = 1.71 to 1.89 |  |  |  |  |  |

| SID34Q    | IDD29Q                                                                   | I <sup>2</sup> C wakeup and WDT on.                | -   | _   | 180  | μΑ    | $V_{DD}$ = 1.8 to 3.6          |  |  |  |  |  |

| SID35Q    | IDD30Q                                                                   | I <sup>2</sup> C wakeup and WDT on.                | -   | _   | 140  | μΑ    | V <sub>DD</sub> = 3.6 to 5.5   |  |  |  |  |  |

| Hibernate | Mode, V <sub>DD</sub> = 1                                                | .8 V to 3.6 V (Regulator on)                       |     |     |      |       |                                |  |  |  |  |  |

| SID40     | IDD35                                                                    | GPIO and Reset active                              | _   | 150 | _    | nA    | T = 25 °C                      |  |  |  |  |  |

| SID41     | IDD36                                                                    | GPIO and Reset active                              | -   | _   | 1000 | nA    | T = 85 °C                      |  |  |  |  |  |

| Hibernate | Mode, V <sub>DD</sub> = 3                                                | .6 V to 5.5 V                                      |     | •   |      | •     |                                |  |  |  |  |  |

| SID43     | IDD38                                                                    | GPIO and Reset active                              | _   | 150 | _    | nA    | T = 25 °C                      |  |  |  |  |  |

| Hibernate | Mode, V <sub>DD</sub> = 1                                                | .71 V to 1.89 V (Regulator bypassed)               |     | •   |      | •     |                                |  |  |  |  |  |

| SID46     | IDD41                                                                    | GPIO and Reset active                              | -   | 150 | -    | nA    | T = 25 °C                      |  |  |  |  |  |

| SID47     | IDD42                                                                    | GPIO and Reset active                              | _   | _   | 1000 | nA    | T = 85 °C                      |  |  |  |  |  |

| Hibernate | Mode, +105 °C                                                            |                                                    |     |     |      |       |                                |  |  |  |  |  |

| SID42Q    | IDD37Q                                                                   | Regulator Off                                      | -   | _   | 19.4 | μA    | $V_{DD}$ = 1.71 to 1.89        |  |  |  |  |  |

| SID43Q    | IDD38Q                                                                   |                                                    | _   | _   | 17   | μA    | $V_{DD}$ = 1.8 to 3.6          |  |  |  |  |  |

| SID44Q    | IDD39Q                                                                   |                                                    | _   | _   | 16   | μA    | $V_{DD} = 3.6 \text{ to } 5.5$ |  |  |  |  |  |

| Stop Mode | 9                                                                        |                                                    |     |     |      |       |                                |  |  |  |  |  |

| SID304    | IDD43A                                                                   | Stop Mode current; V <sub>DD</sub> = 3.3 V         | _   | 20  | 80   | nA    | Typ at 25 °C<br>Max at 85 °C   |  |  |  |  |  |

| Stop Mode | e, +105 °C                                                               |                                                    |     |     |      |       |                                |  |  |  |  |  |

| SID304Q   | IDD43AQ                                                                  | Stop Mode current; V <sub>DD</sub> = 3.6 V         | _   | _   | 5645 | nA    |                                |  |  |  |  |  |

| XRES curi | ent                                                                      | -                                                  |     | •   |      | •     | •                              |  |  |  |  |  |

| SID307    | IDD_XR                                                                   | Supply current while XRES asserted                 | _   | 2   | 5    | mA    |                                |  |  |  |  |  |

Table 3. AC Specifications

| Spec ID# | Parameter               | Description                          | Min | Тур | Max | Units | Details/<br>Conditions                        |

|----------|-------------------------|--------------------------------------|-----|-----|-----|-------|-----------------------------------------------|

| SID48    | F <sub>CPU</sub>        | CPU frequency                        | DC  | _   | 24  | MHz   | $1.71 \leq V_{DD} \leq 5.5$                   |

| SID49    | T <sub>SLEEP</sub>      | Wakeup from sleep mode               | _   | 0   | _   | μs    | Guaranteed by characterization                |

| SID50    | T <sub>DEEPSLEEP</sub>  | Wakeup from Deep Sleep mode          | _   | _   | 25  | μs    | 24-MHz IMO.<br>Guaranteed by characterization |

| SID51    | T <sub>HIBERNATE</sub>  | Wakeup from Hibernate and Stop modes | -   | _   | 2   | ms    | Guaranteed by characterization                |

| SID52    | T <sub>RESETWIDTH</sub> | External reset pulse width           | 1   | _   | -   | μs    | Guaranteed by characterization                |

Document Number: 001-87220 Rev. \*H Page 19 of 43

**GPIO**

# Table 4. GPIO DC Specifications

| Spec ID# | Parameter                      | Description                                              | Min                        | Тур | Max                       | Units | Details/<br>Conditions                                         |

|----------|--------------------------------|----------------------------------------------------------|----------------------------|-----|---------------------------|-------|----------------------------------------------------------------|

| SID57    | V <sub>IH</sub> <sup>[2]</sup> | Input voltage high threshold                             | 0.7 ×<br>V <sub>DDD</sub>  | _   | -                         | V     | CMOS Input                                                     |

| SID58    | V <sub>IL</sub>                | Input voltage low threshold                              | _                          | _   | 0.3 ×<br>V <sub>DDD</sub> | V     | CMOS Input                                                     |

| SID241   | V <sub>IH</sub> <sup>[2]</sup> | LVTTL input, V <sub>DDD</sub> < 2.7 V                    | 0.7×<br>V <sub>DDD</sub>   | _   | -                         | V     |                                                                |

| SID242   | V <sub>IL</sub>                | LVTTL input, V <sub>DDD</sub> < 2.7 V                    | _                          | _   | 0.3 ×<br>V <sub>DDD</sub> | V     |                                                                |

| SID243   | V <sub>IH</sub> <sup>[2]</sup> | LVTTL input, V <sub>DDD</sub> ≥ 2.7 V                    | 2.0                        | _   |                           | V     |                                                                |

| SID244   | V <sub>IL</sub>                | LVTTL input, V <sub>DDD</sub> ≥ 2.7 V                    | _                          | _   | 8.0                       | V     |                                                                |

| SID59    | V <sub>OH</sub>                | Output voltage high level                                | V <sub>DDD</sub><br>-0.6   | _   | -                         | V     | I <sub>OH</sub> = 4 mA at<br>3-V V <sub>DDD</sub>              |

| SID60    | V <sub>OH</sub>                | Output voltage high level                                | V <sub>DDD</sub><br>-0.5   | _   | -                         | V     | I <sub>OH</sub> = 1 mA at<br>1.8-V V <sub>DDD</sub>            |

| SID61    | V <sub>OL</sub>                | Output voltage low level                                 | _                          | _   | 0.6                       | V     | $I_{OL}$ = 4 mA at<br>1.8-V $V_{DDD}$                          |

| SID62    | V <sub>OL</sub>                | Output voltage low level                                 | _                          | _   | 0.6                       | V     | $I_{OL} = 8 \text{ mA at } 3-V$<br>$V_{DDD}$                   |

| SID62A   | V <sub>OL</sub>                | Output voltage low level                                 | -                          | -   | 0.4                       | V     | $I_{OL} = 3 \text{ mA at } 3-V$<br>$V_{DDD}$                   |

| SID63    | R <sub>PULLUP</sub>            | Pull-up resistor                                         | 3.5                        | 5.6 | 8.5                       | kΩ    |                                                                |

| SID64    | R <sub>PULLDOWN</sub>          | Pull-down resistor                                       | 3.5                        | 5.6 | 8.5                       | kΩ    |                                                                |

| SID65    | I <sub>IL</sub>                | Input leakage current (absolute value)                   | -                          | -   | 2                         | nA    | 25 °C, V <sub>DDD</sub> = 3.0-V                                |

| SID65A   | I <sub>IL_CTBM</sub>           | Input leakage current (absolute value) for CTBM pins     | _                          | _   | 4                         | nA    |                                                                |

| SID66    | C <sub>IN</sub>                | Input capacitance                                        | _                          | _   | 7                         | pF    |                                                                |

| SID67    | V <sub>HYSTTL</sub>            | Input hysteresis LVTTL                                   | 25                         | 40  | -                         | mV    | V <sub>DDD</sub> ≥ 2.7 V.<br>Guaranteed by<br>characterization |

| SID68    | V <sub>HYSCMOS</sub>           | Input hysteresis CMOS                                    | 0.05 ×<br>V <sub>DDD</sub> | _   | _                         | mV    | Guaranteed by characterization                                 |

| SID69    | I <sub>DIODE</sub>             | Current through protection diode to V <sub>DD</sub> /Vss | _                          | _   | 100                       | μΑ    | Guaranteed by characterization                                 |

| SID69A   | I <sub>TOT_GPIO</sub>          | Maximum Total Source or Sink Chip Current                | _                          | _   | 200                       | mA    | Guaranteed by characterization                                 |

Note 2.  $V_{IH}$  must not exceed  $V_{DDD}$  + 0.2 V.

Document Number: 001-87220 Rev. \*H

Table 5. GPIO AC Specifications (Guaranteed by Characterization)

| Spec ID# | Parameter            | Description                                                                    | Min | Тур | Max  | Units | Details/<br>Conditions                     |

|----------|----------------------|--------------------------------------------------------------------------------|-----|-----|------|-------|--------------------------------------------|

| SID70    | T <sub>RISEF</sub>   | Rise time in fast strong mode                                                  | 2   | -   | 12   | ns    | 3.3-V V <sub>DDD</sub> ,<br>Cload = 25 pF  |

| SID71    | T <sub>FALLF</sub>   | Fall time in fast strong mode                                                  | 2   | _   | 12   | ns    | 3.3-V V <sub>DDD</sub> ,<br>Cload = 25 pF  |

| SID72    | T <sub>RISES</sub>   | Rise time in slow strong mode                                                  | 10  | _   | 60   | ns    | 3.3-V V <sub>DDD</sub> ,<br>Cload = 25 pF  |

| SID73    | T <sub>FALLS</sub>   | Fall time in slow strong mode                                                  | 10  | _   | 60   | ns    | 3.3-V V <sub>DDD</sub> ,<br>Cload = 25 pF  |

| SID74    | F <sub>GPIOUT1</sub> | GPIO Fout;3.3 V $\leq$ V <sub>DDD</sub> $\leq$ 5.5 V. Fast strong mode.        | -   | -   | 24   | MHz   | 90/10%, 25-pF<br>load, 60/40 duty<br>cycle |

| SID75    | F <sub>GPIOUT2</sub> | GPIO Fout;1.7 $V \le V_{DDD} \le 3.3 \text{ V. Fast strong mode.}$             | -   | -   | 16.7 | MHz   | 90/10%, 25-pF<br>load, 60/40 duty<br>cycle |

| SID76    | F <sub>GPIOUT3</sub> | GPIO Fout;3.3 V $\leq$ V <sub>DDD</sub> $\leq$ 5.5 V. Slow strong mode.        | -   | -   | 7    | MHz   | 90/10%, 25-pF<br>load, 60/40 duty<br>cycle |

| SID245   | F <sub>GPIOUT4</sub> | GPIO Fout; 1.7 V $\leq$ V <sub>DDD</sub> $\leq$ 3.3 V. Slow strong mode.       | -   | -   | 3.5  | MHz   | 90/10%, 25-pF<br>load, 60/40 duty<br>cycle |

| SID246   | F <sub>GPIOIN</sub>  | GPIO input operating frequency;<br>1.71 V $\leq$ V <sub>DDD</sub> $\leq$ 5.5 V | -   | _   | 24   | MHz   | 90/10% V <sub>IO</sub>                     |

# XRES

# Table 6. XRES DC Specifications

| Spec ID# | Parameter            | Description                                          | Min                       | Тур | Max                       | Units | Details/<br>Conditions         |

|----------|----------------------|------------------------------------------------------|---------------------------|-----|---------------------------|-------|--------------------------------|

| SID77    | V <sub>IH</sub>      | Input voltage high threshold                         | 0.7 ×<br>V <sub>DDD</sub> | -   | _                         | V     | CMOS Input                     |

| SID78    | V <sub>IL</sub>      | Input voltage low threshold                          | _                         | 1   | 0.3 ×<br>V <sub>DDD</sub> | V     | CMOS Input                     |

| SID79    | R <sub>PULLUP</sub>  | Pull-up resistor                                     | 3.5                       | 5.6 | 8.5                       | kΩ    |                                |

| SID80    | C <sub>IN</sub>      | Input capacitance                                    | _                         | 3   | _                         | pF    |                                |

| SID81    | V <sub>HYSXRES</sub> | Input voltage hysteresis                             | _                         | 100 | _                         | mV    | Guaranteed by characterization |

| SID82    | I <sub>DIODE</sub>   | Current through protection diode to $V_{DDD}/V_{SS}$ | _                         | -   | 100                       | μA    | Guaranteed by characterization |

# Table 7. XRES AC Specifications

| Spec ID# | Parameter               | Description       | Min | Тур | Max | Units | Details/<br>Conditions         |

|----------|-------------------------|-------------------|-----|-----|-----|-------|--------------------------------|

| SID83    | T <sub>RESETWIDTH</sub> | Reset pulse width | 1   | 1   | 1   | μs    | Guaranteed by characterization |

Document Number: 001-87220 Rev. \*H Page 21 of 43

# **Analog Peripherals**

Opamp

**Table 8. Opamp Specifications (Guaranteed by Characterization)**

| Spec ID# | Parameter                | Description                                    | Min   | Тур  | Max                    | Units   | Details/<br>Conditions                    |

|----------|--------------------------|------------------------------------------------|-------|------|------------------------|---------|-------------------------------------------|

|          | I <sub>DD</sub>          | Opamp block current. No load.                  | _     | -    | -                      | _       |                                           |

| SID269   | I <sub>DD_HI</sub>       | Power = high                                   | _     | 1100 | 1850                   | μΑ      |                                           |

| SID270   | I <sub>DD_MED</sub>      | Power = medium                                 | _     | 550  | 950                    | μA      |                                           |

| SID271   | I <sub>DD_LOW</sub>      | Power = low                                    | _     | 150  | 350                    | μA      |                                           |

|          | GBW                      | Load = 20 pF, 0.1 mA. V <sub>DDA</sub> = 2.7 V | _     | _    | _                      | _       |                                           |

| SID272   | GBW_HI                   | Power = high                                   | 6     | _    | _                      | MHz     |                                           |

| SID273   | GBW_MED                  | Power = medium                                 | 4     | _    | _                      | MHz     |                                           |

| SID274   | GBW_LO                   | Power = low                                    | _     | 1    | _                      | MHz     |                                           |

|          | I <sub>OUT_MAX</sub>     | V <sub>DDA</sub> ≥ 2.7 V, 500 mV from rail     | _     | _    | _                      | _       |                                           |

| SID275   | I <sub>OUT_MAX_HI</sub>  | Power = high                                   | 10    | _    | _                      | mA      |                                           |

| SID276   | I <sub>OUT_MAX_MID</sub> | Power = medium                                 | 10    | _    | _                      | mA      |                                           |

| SID277   | I <sub>OUT_MAX_LO</sub>  | Power = low                                    | _     | 5    | _                      | mA      |                                           |

|          | I <sub>OUT</sub>         | V <sub>DDA</sub> = 1.71 V, 500 mV from rail    | _     | _    | _                      | _       |                                           |

| SID278   | I <sub>OUT_MAX_HI</sub>  | Power = high                                   | 4     | _    | _                      | mA      |                                           |

| SID279   | I <sub>OUT MAX MID</sub> | Power = medium                                 | 4     | _    | _                      | mA      |                                           |

| SID280   | I <sub>OUT_MAX_LO</sub>  | Power = low                                    | _     | 2    | _                      | mA      |                                           |

| SID281   | V <sub>IN</sub>          | Charge pump on, V <sub>DDA</sub> ≥ 2.7 V       | -0.05 | _    | V <sub>DDA</sub> – 0.2 | V       |                                           |

| SID282   | V <sub>CM</sub>          | Charge pump on, V <sub>DDA</sub> ≥ 2.7 V       | -0.05 | _    | $V_{DDA} - 0.2$        | V       |                                           |

|          | V <sub>OUT</sub>         | $V_{DDA} \ge 2.7 \text{ V}$                    | _     | _    | _                      |         |                                           |

| SID283   | V <sub>OUT_1</sub>       | Power = high, Iload=10 mA                      | 0.5   | _    | V <sub>DDA</sub> – 0.5 | V       |                                           |

| SID284   | V <sub>OUT_2</sub>       | Power = high, Iload=1 mA                       | 0.2   | _    | V <sub>DDA</sub> – 0.2 | V       |                                           |

| SID285   | V <sub>OUT_3</sub>       | Power = medium, Iload=1 mA                     | 0.2   | _    | $V_{DDA} - 0.2$        | V       |                                           |

| SID286   | V <sub>OUT_4</sub>       | Power = low, Iload=0.1 mA                      | 0.2   | _    | V <sub>DDA</sub> – 0.2 | V       |                                           |

| SID288   | V <sub>OS_TR</sub>       | Offset voltage, trimmed                        | 1     | ±0.5 | 1                      | mV      | High mode                                 |

| SID288A  | V <sub>OS_TR</sub>       | Offset voltage, trimmed                        | _     | ±1   | _                      | mV      | Medium mode                               |

| SID288B  | V <sub>OS_TR</sub>       | Offset voltage, trimmed                        | _     | ±2   | _                      | mV      | Low mode                                  |

| SID290   | V <sub>OS_DR_TR</sub>    | Offset voltage drift, trimmed                  | -10   | ±3   | 10                     | μV/°C   | High mode.<br>T <sub>A</sub> ≤ 85 °C      |

| SID290Q  | VOS_DR_TR                | Offset voltage drift, trimmed                  | 15    | ±3   | 15                     | μV/°C   | High mode. $T_A \le 105 ^{\circ}\text{C}$ |

| SID290A  | V <sub>OS_DR_TR</sub>    | Offset voltage drift, trimmed                  | _     | ±10  | -                      | μV/°C   | Medium mode                               |

| SID290B  | V <sub>OS_DR_TR</sub>    | Offset voltage drift, trimmed                  | _     | ±10  | -                      | μV/°C   | Low mode                                  |

| SID291   | CMRR                     | DC                                             | 70    | 80   | _                      | dB      | V <sub>DDD</sub> = 3.6 V                  |

| SID292   | PSRR                     | At 1 kHz, 100-mV ripple                        | 70    | 85   | _                      | dB      | V <sub>DDD</sub> = 3.6 V                  |

|          | Noise                    |                                                | _     | _    | _                      | _       |                                           |

| SID293   | V <sub>N1</sub>          | Input referred, 1 Hz - 1GHz, power = high      | _     | 94   | _                      | μVrms   |                                           |

| SID294   | V <sub>N2</sub>          | Input referred, 1 kHz, power = high            | _     | 72   | _                      | nV/rtHz |                                           |

| SID295   | V <sub>N3</sub>          | Input referred, 10kHz, power = high            | _     | 28   | _                      | nV/rtHz |                                           |

| SID296   | V <sub>N4</sub>          | Input referred, 100kHz, power = high           | _     | 15   | _                      | nV/rtHz |                                           |

Document Number: 001-87220 Rev. \*H Page 22 of 43

#### Memory

#### Table 26. Flash DC Specifications

| Spec ID | Parameter | Description               | Min  | Тур | Max | Units | Details/Conditions |

|---------|-----------|---------------------------|------|-----|-----|-------|--------------------|

| SID173  | $V_{PE}$  | Erase and program voltage | 1.71 | 1   | 5.5 | V     |                    |

#### Table 27. Flash AC Specifications

| Spec ID | Parameter                              | Description                                                                                              | Min   | Тур | Max | Units   | Details/Conditions             |

|---------|----------------------------------------|----------------------------------------------------------------------------------------------------------|-------|-----|-----|---------|--------------------------------|

| SID174  | T <sub>ROWWRITE</sub> <sup>[3]</sup>   | Row (block) write time (erase and program)                                                               | _     | _   | 20  | ms      | Row (block) = 128 bytes        |

| SID175  | T <sub>ROWERASE</sub> <sup>[3]</sup>   | Row erase time                                                                                           | _     | _   | 13  | ms      |                                |

| SID176  | T <sub>ROWPROGRAM</sub> <sup>[3]</sup> | Row program time after erase                                                                             | 1     | 1   | 7   | ms      |                                |

| SID178  | T <sub>BULKERASE</sub> <sup>[3]</sup>  | Bulk erase time (32 KB)                                                                                  | 1     | 1   | 35  | ms      |                                |

| SID180  | T <sub>DEVPROG</sub> <sup>[3]</sup>    | Total device program time                                                                                | 1     | 1   | 7   | seconds | Guaranteed by characterization |

| SID181  | F <sub>END</sub>                       | Flash endurance                                                                                          | 100 K | -   | -   | cycles  | Guaranteed by characterization |

| SID182  | F <sub>RET</sub>                       | Flash retention. T <sub>A</sub> ≤ 55 °C, 100 K<br>P/E cycles                                             | 20    | _   | _   | years   | Guaranteed by characterization |

| SID182A |                                        | Flash retention. $T_A \le 85$ °C, 10 K P/E cycles                                                        | 10    | _   | _   | years   | Guaranteed by characterization |

| SID182B | F <sub>RETQ</sub>                      | Flash retention. $T_A \le 105 ^{\circ}C$ , 10 K P/E cycles, $\le$ three years at TA $\ge$ 85 $^{\circ}C$ | 10    | _   | 20  | years   | Guaranteed by characterization |

# **System Resources**

Power-on-Reset (POR) with Brown Out

# Table 28. Imprecise Power On Reset (IPOR)

| Spec ID | Parameter             | Description          | Min  | Тур | Max  | Units | Details/Conditions             |

|---------|-----------------------|----------------------|------|-----|------|-------|--------------------------------|

| SID185  | V <sub>RISEIPOR</sub> | Rising trip voltage  | 0.80 | _   | 1.45 | V     | Guaranteed by characterization |

| SID186  | V <sub>FALLIPOR</sub> | Falling trip voltage | 0.75 | _   | 1.4  | V     | Guaranteed by characterization |

| SID187  | V <sub>IPORHYST</sub> | Hysteresis           | 15   | _   | 200  | mV    | Guaranteed by characterization |

# Table 29. Precise Power On Reset (POR)

| Spec ID | Parameter              | Description                                | Min  | Тур | Max | Units  | Details/Conditions                                                                       |

|---------|------------------------|--------------------------------------------|------|-----|-----|--------|------------------------------------------------------------------------------------------|

| SID190  | V <sub>FALLPPOR</sub>  | BOD trip voltage in active and sleep modes | 1.64 | _   | _   |        | Full functionality between 1.71 V and BOD trip voltage is guaranteed by characterization |

| SID192  | V <sub>FALLDPSLP</sub> | BOD trip voltage in Deep Sleep             | 1.4  | _   | _   | V      | Guaranteed by characterization                                                           |

| BID55   | Svdd                   | Maximum power supply ramp rate             | _    | _   | 67  | kV/sec |                                                                                          |

Document Number: 001-87220 Rev. \*H Page 29 of 43

Note

3. It can take as much as 20 milliseconds to write to Flash. During this time the device should not be Reset, or Flash operations will be interrupted and cannot be relied on to have completed. Reset sources include the XRES pin, software resets, CPU lockup states and privilege violations, improper power supply levels, and watchdogs. Make certain that these are not inadvertently activated.

#### Internal Main Oscillator

# Table 33. IMO DC Specifications (Guaranteed by Design)

| Spec ID | Parameter         | Description                     | Min | Тур | Max  | Units | Details/Conditions |

|---------|-------------------|---------------------------------|-----|-----|------|-------|--------------------|

| SID218  | I <sub>IMO1</sub> | IMO operating current at 48 MHz | _   | _   | 1000 | μΑ    |                    |

| SID219  | I <sub>IMO2</sub> | IMO operating current at 24 MHz | _   | _   | 325  | μΑ    |                    |

| SID220  | I <sub>IMO3</sub> | IMO operating current at 12 MHz | _   | _   | 225  | μΑ    |                    |

| SID221  | I <sub>IMO4</sub> | IMO operating current at 6 MHz  | _   | _   | 180  | μΑ    |                    |

| SID222  | I <sub>IMO5</sub> | IMO operating current at 3 MHz  | _   | _   | 150  | μA    |                    |

# Table 34. IMO AC Specifications

| Spec ID | Parameter               | Description                          | Min | Тур | Max | Units | Details/Conditions                                             |

|---------|-------------------------|--------------------------------------|-----|-----|-----|-------|----------------------------------------------------------------|

| SID223  | F <sub>IMOTOL1</sub>    | Frequency variation from 3 to 48 MHz | -   | _   | ±2  | %     | ±3% if T <sub>A</sub> > 85 °C and<br>IMO frequency <<br>24 MHz |

| SID226  | T <sub>STARTIMO</sub>   | IMO startup time                     | _   | _   | 12  | μs    |                                                                |

| SID227  | T <sub>JITRMSIMO1</sub> | RMS Jitter at 3 MHz                  | _   | 156 | _   | ps    |                                                                |

| SID228  | T <sub>JITRMSIMO2</sub> | RMS Jitter at 24 MHz                 | _   | 145 | _   | ps    |                                                                |

| SID229  | T <sub>JITRMSIMO3</sub> | RMS Jitter at 48 MHz                 | 1   | 139 | _   | ps    |                                                                |

# Internal Low-Speed Oscillator

# Table 35. ILO DC Specifications (Guaranteed by Design)

| Spec ID | Parameter            | Description                     | Min | Тур | Max  | Units | Details/Conditions             |

|---------|----------------------|---------------------------------|-----|-----|------|-------|--------------------------------|

| SID231  | I <sub>ILO1</sub>    | ILO operating current at 32 kHz | _   | 0.3 | 1.05 | •     | Guaranteed by Characterization |

| SID233  | I <sub>ILOLEAK</sub> | ILO leakage current             | -   | 2   | 15   | nA    | Guaranteed by<br>Design        |

# Table 36. ILO AC Specifications

| Spec ID | Parameter              | Description              | Min | Тур | Max | Units | Details/Conditions                                    |

|---------|------------------------|--------------------------|-----|-----|-----|-------|-------------------------------------------------------|

| SID234  | T <sub>STARTILO1</sub> | ILO startup time         | -   | 1   | 2   |       | Guaranteed by characterization                        |

| SID236  | T <sub>ILODUTY</sub>   | ILO duty cycle           | 40  | 50  | 60  |       | Guaranteed by characterization                        |

| SID237  | F <sub>ILOTRIM1</sub>  | 32 kHz trimmed frequency | 15  | 32  | 50  | kHz   | Max ILO frequency is 70 kHz if T <sub>A</sub> > 85 °C |

# **Table 37. External Clock Specifications**

| Spec ID | Parameter  | Description                               | Min | Min Typ Max |    | Units | Details/Conditions             |

|---------|------------|-------------------------------------------|-----|-------------|----|-------|--------------------------------|

| SID305  | ExtClkFreq | External Clock input Frequency            | 0   | _           | 24 |       | Guaranteed by characterization |

| SID306  | ExtClkDuty | Duty cycle; Measured at V <sub>DD/2</sub> | 45  | _           | 55 |       | Guaranteed by characterization |

Document Number: 001-87220 Rev. \*H Page 31 of 43

# **Ordering Information**

The PSoC 4100 part numbers and features are listed in the following table.

Table 39. PSoC 4100 Family Ordering Information

|        |                    | or uei              | Features   |           |     |               |          |                  |                |                |              |            |      | Package |          |          |             |           |

|--------|--------------------|---------------------|------------|-----------|-----|---------------|----------|------------------|----------------|----------------|--------------|------------|------|---------|----------|----------|-------------|-----------|

|        |                    |                     |            |           |     |               | 1 60     | ı                | <b>.</b>       |                |              |            |      |         |          | ıcka     | <del></del> |           |

| Family | MPN                | Max CPU Speed (MHz) | Flash (KB) | SRAM (KB) | NDB | Op-amp (CTBm) | CapSense | Direct LCD Drive | 12-bit SAR ADC | LP Comparators | TCPWM Blocks | SCB Blocks | GPIO | 28-SSOP | 35-WLCSP | 40-QFN   | 44-TQFP     | 48-TQFP   |

|        | CY8C4124PVI-432    | 24                  | 16         | 4         | -   | 1             | -        | -                | 806 ksps       | 2              | 4            | 2          | 24   | 1       |          |          |             |           |

|        | CY8C4124PVI-442    | 24                  | 16         | 4         | -   | 1             | V        | √                | 806 ksps       | 2              | 4            | 2          | 24   | 1       |          |          |             |           |

|        | CY8C4124PVQ-432    | 24                  | 16         | 4         | -   | 1             | -        | -                | 806 ksps       | 2              | 4            | 2          | 24   | V       |          |          |             |           |

|        | CY8C4124PVQ-442    | 24                  | 16         | 4         | -   | 1             | V        | V                | 806 ksps       | 2              | 4            | 2          | 24   | V       |          |          |             |           |

|        | CY8C4124FNI-443    | 24                  | 16         | 4         | -   | 2             | V        | V                | 806 ksps       | 2              | 4            | 2          | 31   |         | V        |          |             |           |

|        | CY8C4124LQI-443    | 24                  | 16         | 4         | -   | 2             | V        | V                | 806 ksps       | 2              | 4            | 2          | 34   |         |          | V        |             |           |

|        | CY8C4124AXI-443    | 24                  | 16         | 4         | -   | 2             | <b>V</b> | 1                | 806 ksps       | 2              | 4            | 2          | 36   |         |          |          | 1           |           |

|        | CY8C4124LQQ-443    | 24                  | 16         | 4         | -   | 2             | <b>V</b> | 1                | 806 ksps       | 2              | 4            | 2          | 34   |         |          | 1        |             |           |

|        | CY8C4124AXQ-443    | 24                  | 16         | 4         | -   | 2             | V        | 1                | 806 ksps       | 2              | 4            | 2          | 36   |         |          |          | 1           |           |

|        | CY8C4124AZI-443    | 24                  | 16         | 4         | -   | 2             | V        | √                | 806 ksps       | 2              | 4            | 2          | 36   |         |          |          |             | $\sqrt{}$ |

| 4100   | CY8C4125AXI-473    | 24                  | 32         | 4         | -   | 2             | -        | -                | 806 ksps       | 2              | 4            | 2          | 36   |         |          |          | V           |           |

| 4      | CY8C4125AXQ-473    | 24                  | 32         | 4         | -   | 2             | -        | -                | 806 ksps       | 2              | 4            | 2          | 36   |         |          |          | <b>V</b>    |           |

|        | CY8C4125AZI-473    | 24                  | 32         | 4         | -   | 2             | -        | -                | 806 ksps       | 2              | 4            | 2          | 36   |         |          |          |             | √         |

|        | CY8C4125PVI-482    | 24                  | 32         | 4         | -   | 1             | V        | V                | 806 ksps       | 2              | 4            | 2          | 24   | V       |          |          |             |           |

|        | CY8C4125PVQ-482    | 24                  | 32         | 4         | -   | 1             | V        | V                | 806 ksps       | 2              | 4            | 2          | 24   | V       |          |          |             |           |

|        | CY8C4125FNI-483(T) | 24                  | 32         | 4         | -   | 2             | V        | V                | 806 ksps       | 2              | 4            | 2          | 31   |         | V        |          |             |           |

|        | CY8C4125LQI-483    | 24                  | 32         | 4         | -   | 2             | V        | √                | 806 ksps       | 2              | 4            | 2          | 34   |         |          | 1        |             |           |

|        | CY8C4125AXI-483    | 24                  | 32         | 4         | -   | 2             | <b>V</b> | <b>V</b>         | 806 ksps       | 2              | 4            | 2          | 36   |         |          |          | 1           |           |

|        | CY8C4125LQQ-483    | 24                  | 32         | 4         | -   | 2             | V        | V                | 806 ksps       | 2              | 4            | 2          | 34   |         |          | <b>V</b> |             |           |

|        | CY8C4125AXQ-483    | 24                  | 32         | 4         | -   | 2             | V        | V                | 806 ksps       | 2              | 4            | 2          | 36   |         |          |          | <b>V</b>    |           |

|        | CY8C4125AZI-483    | 24                  | 32         | 4         | -   | 2             | √        | V                | 806 ksps       | 2              | 4            | 2          | 36   |         |          |          |             | V         |

Document Number: 001-87220 Rev. \*H Page 33 of 43

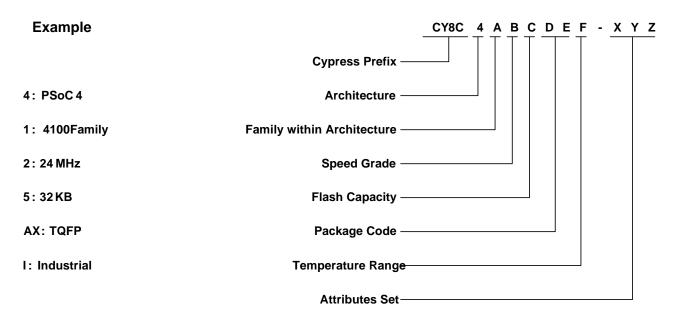

# **Part Numbering Conventions**

PSoC 4 devices follow the part numbering convention described in the following table. All fields are single-character alphanumeric (0, 1, 2, ..., 9, A,B, ..., Z) unless stated otherwise.

The part numbers are of the form CY8C4ABCDEF-XYZ where the fields are defined as follows.

The Field Values are listed in the following table.

| Field | Description                | Values  | Meaning                                |

|-------|----------------------------|---------|----------------------------------------|

| CY8C  | Cypress Prefix             |         |                                        |

| 4     | Architecture               | 4       | PSoC 4                                 |

| Α     | Family within architecture | 1       | 4100 Family                            |

|       | army within architecture   | 2       | 4200 Family                            |

| В     | CPU Speed                  | 2       | 24 MHz                                 |

|       | Ci o speed                 | 4       | 48 MHz                                 |

| С     | Flash Capacity             | 4       | 16 KB                                  |

|       | Trasti Capacity            | 5       | 32 KB                                  |

|       |                            | AX, AZ  | TQFP                                   |

| DE    | Package Code               | LQ      | QFN                                    |

|       | l ackage code              | PV      | SSOP                                   |

|       |                            | FN      | WLCSP                                  |

| F     | Temperature Range          | I       | Industrial                             |

| '     | Temperature realige        | Q       | Extended Industrial                    |

| XYZ   | Attributes Code            | 000-999 | Code of feature set in specific family |

Document Number: 001-87220 Rev. \*H Page 34 of 43

# **Packaging**

**Table 40. Package Characteristics**

| Parameter      | Description                             | Conditions | Min | Тур   | Max | Units   |

|----------------|-----------------------------------------|------------|-----|-------|-----|---------|

| T <sub>A</sub> | Operating ambient temperature           |            | -40 | 25.00 | 105 | °C      |

| T <sub>J</sub> | Operating junction temperature          |            | -40 | -     | 125 | °C      |

| $T_{JA}$       | Package θ <sub>JA</sub> (28-pin SSOP)   |            | _   | 66.58 | -   | °C/Watt |

| $T_{JA}$       | Package θ <sub>JA</sub> (35-ball WLCSP) |            | _   | 28.00 | _   | °C/Watt |

| $T_{JA}$       | Package θ <sub>JA</sub> (40-pin QFN)    |            | _   | 15.34 | _   | °C/Watt |

| $T_{JA}$       | Package θ <sub>JA</sub> (44-pin TQFP)   |            | _   | 57.16 | -   | °C/Watt |

| $T_{JA}$       | Package θ <sub>JA</sub> (48-pin TQFP)   |            | _   | 67.30 | _   | °C/Watt |

| $T_JC$         | Package θ <sub>JC</sub> (28-pin SSOP)   |            | _   | 26.28 | -   | °C/Watt |

| $T_{JC}$       | Package $\theta_{JC}$ (35-ball WLCSP)   |            | _   | 00.40 | _   | °C/Watt |

| $T_{JC}$       | Package θ <sub>JC</sub> (40-pin QFN)    |            | _   | 2.50  | _   | °C/Watt |

| $T_{JC}$       | Package θ <sub>JC</sub> (44-pin TQFP)   |            | _   | 17.47 | _   | °C/Watt |

| $T_{JC}$       | Package θ <sub>JC</sub> (48-pin TQFP)   |            | _   | 27.60 | _   | °C/Watt |

Table 41. Solder Reflow Peak Temperature

| Package       | Maximum Peak<br>Temperature | Maximum Time at Peak Temperature |

|---------------|-----------------------------|----------------------------------|

| 28-pin SSOP   | 260 °C                      | 30 seconds                       |

| 35-ball WLCSP | 260 °C                      | 30 seconds                       |

| 40-pin QFN    | 260 °C                      | 30 seconds                       |

| 44-pin TQFP   | 260 °C                      | 30 seconds                       |

| 48-pin TQFP   | 260 °C                      | 30 seconds                       |

Table 42. Package Moisture Sensitivity Level (MSL), IPC/JEDEC J-STD-2

| Package       | MSL   |

|---------------|-------|

| 28-pin SSOP   | MSL 3 |

| 35-ball WLCSP | MSL 3 |

| 40-pin QFN    | MSL 3 |

| 44-pin TQFP   | MSL 3 |

| 48-pin TQFP   | MSL 3 |

PSoC 4 CAB Libraries with Schematics Symbols and PCB Footprints are on the Cypress web site at http://www.cypress.com/cad-resources/psoc-4-cad-libraries?source=search&cat=technical\_documents.

Document Number: 001-87220 Rev. \*H Page 35 of 43

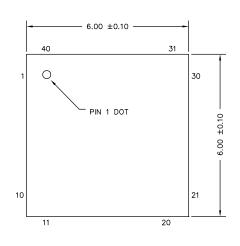

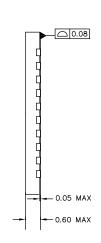

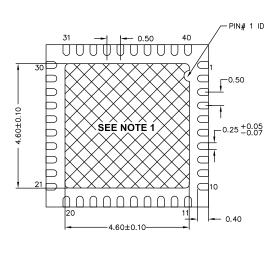

Figure 17. 40-pin QFN Package Outline

TOP VIEW SIDE VIEW BOTTOM VIEW

#### NOTES:

- 2. REFERENCE JEDEC # MO-248

- 3. PACKAGE WEIGHT: 68 ±2 mg

- 4. ALL DIMENSIONS ARE IN MILLIMETERS

001-80659 \*A

The center pad on the QFN package should be connected to ground (VSS) for best mechanical, thermal, and electrical performance. If not connected to ground, it should be electrically floating and not connected to any other signal.

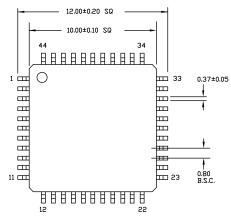

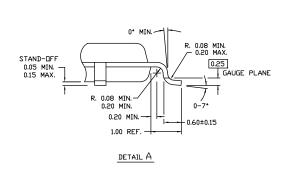

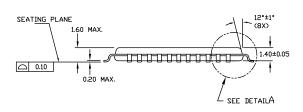

Figure 18. 44-pin TQFP Package Outline

NDTE:

- 1. JEDEC STD REF MS-026

- 2. BODY LENGTH DIMENSION DOES NOT INCLUDE MOLD PROTRUSION/END FLASH

MOLD PROTRUSION/END FLASH SHALL NOT EXCEED 0.0098 in (0.25 mm) PER SIDE

BODY LENGTH DIMENSIONS ARE MAX PLASTIC BODY SIZE INCLUDING MOLD MISMATCH

- 3. DIMENSIONS IN MILLIMETERS

51-85064 \*G

9.00±0.25 SQ -7.00±0.10 SQ DIMENSIONS ARE IN MILLIMETERS 0.20±0.05 0° MIN. R. 0.08 MIN. — 0.20 MAX. STAND-OFF 0.05 MIN. 0.15 MAX. GAUGE PLANE \_ \_ 0.50 TYP. R. 0.08 MIN. 0-7 13 0.20 MIN. 0.60±0.15 12°±1° SEATING PLANE 1.00 REF. 1.60 MAX. DETAILA 1.40±0.05 O.10 0.20 MAX. 51-85135 \*C SEE DETAILA

Figure 19. 48-Pin TQFP Package Outline

Table 43. Acronyms Used in this Document (continued)

| Acronym           | Description                                                  |  |  |

|-------------------|--------------------------------------------------------------|--|--|

| PC                | program counter                                              |  |  |

| PCB               | printed circuit board                                        |  |  |

| PGA               | programmable gain amplifier                                  |  |  |

| PHUB              | peripheral hub                                               |  |  |

| PHY               | physical layer                                               |  |  |

| PICU              | port interrupt control unit                                  |  |  |

| PLA               | programmable logic array                                     |  |  |

| PLD               | programmable logic device, see also PAL                      |  |  |

| PLL               | phase-locked loop                                            |  |  |

| PMDD              | package material declaration data sheet                      |  |  |

| POR               | power-on reset                                               |  |  |

| PRES              | precise power-on reset                                       |  |  |

| PRS               | pseudo random sequence                                       |  |  |

| PS                | port read data register                                      |  |  |

| PSoC <sup>®</sup> | Programmable System-on-Chip™                                 |  |  |

| PSRR              | power supply rejection ratio                                 |  |  |

| PWM               | pulse-width modulator                                        |  |  |

| RAM               | random-access memory                                         |  |  |

| RISC              | reduced-instruction-set computing                            |  |  |

| RMS               | root-mean-square                                             |  |  |

| RTC               | real-time clock                                              |  |  |

| RTL               | register transfer language                                   |  |  |

| RTR               | remote transmission request                                  |  |  |

| RX                | receive                                                      |  |  |

| SAR               | successive approximation register                            |  |  |

| SC/CT             | switched capacitor/continuous time                           |  |  |

| SCL               | I <sup>2</sup> C serial clock                                |  |  |

| SDA               | I <sup>2</sup> C serial data                                 |  |  |

| S/H               | sample and hold                                              |  |  |

| SINAD             | signal to noise and distortion ratio                         |  |  |

| SIO               | special input/output, GPIO with advanced features. See GPIO. |  |  |

| SOC               | start of conversion                                          |  |  |

| SOF               | start of frame                                               |  |  |

| SPI               | Serial Peripheral Interface, a communications protocol       |  |  |

| SR                | slew rate                                                    |  |  |

| SRAM              | static random access memory                                  |  |  |

| SRES              | software reset                                               |  |  |

| SWD               | serial wire debug, a test protocol                           |  |  |

Table 43. Acronyms Used in this Document (continued)

| Acronym | Description                                                            |  |  |  |

|---------|------------------------------------------------------------------------|--|--|--|

| SWV     | single-wire viewer                                                     |  |  |  |

| TD      | transaction descriptor, see also DMA                                   |  |  |  |

| THD     | total harmonic distortion                                              |  |  |  |

| TIA     | transimpedance amplifier                                               |  |  |  |

| TRM     | technical reference manual                                             |  |  |  |

| TTL     | transistor-transistor logic                                            |  |  |  |

| TX      | transmit                                                               |  |  |  |

| UART    | Universal Asynchronous Transmitter Receiver, a communications protocol |  |  |  |

| UDB     | universal digital block                                                |  |  |  |

| USB     | Universal Serial Bus                                                   |  |  |  |

| USBIO   | USB input/output, PSoC pins used to connect to a USB port              |  |  |  |

| VDAC    | voltage DAC, see also DAC, IDAC                                        |  |  |  |

| WDT     | watchdog timer                                                         |  |  |  |

| WOL     | write once latch, see also NVL                                         |  |  |  |

| WRES    | watchdog timer reset                                                   |  |  |  |

| XRES    | external reset I/O pin                                                 |  |  |  |

| XTAL    | crystal                                                                |  |  |  |

Document Number: 001-87220 Rev. \*H Page 40 of 43

# **Document Conventions**

# **Units of Measure**

# Table 44. Units of Measure

|        | Table 44. Units of Measure |  |  |  |  |  |

|--------|----------------------------|--|--|--|--|--|

| Symbol | Unit of Measure            |  |  |  |  |  |

| °C     | degrees Celsius            |  |  |  |  |  |

| dB     | decibel                    |  |  |  |  |  |

| fF     | femto farad                |  |  |  |  |  |

| Hz     | hertz                      |  |  |  |  |  |

| KB     | 1024 bytes                 |  |  |  |  |  |

| kbps   | kilobits per second        |  |  |  |  |  |

| Khr    | kilohour                   |  |  |  |  |  |

| kHz    | kilohertz                  |  |  |  |  |  |

| kΩ     | kilo ohm                   |  |  |  |  |  |

| ksps   | kilosamples per second     |  |  |  |  |  |

| LSB    | least significant bit      |  |  |  |  |  |

| Mbps   | megabits per second        |  |  |  |  |  |

| MHz    | megahertz                  |  |  |  |  |  |

| ΜΩ     | mega-ohm                   |  |  |  |  |  |

| Msps   | megasamples per second     |  |  |  |  |  |

| μΑ     | microampere                |  |  |  |  |  |

| μF     | microfarad                 |  |  |  |  |  |

| μH     | microhenry                 |  |  |  |  |  |

| μs     | microsecond                |  |  |  |  |  |

| μV     | microvolt                  |  |  |  |  |  |

| μW     | microwatt                  |  |  |  |  |  |

| mA     | milliampere                |  |  |  |  |  |

| ms     | millisecond                |  |  |  |  |  |

| mV     | millivolt                  |  |  |  |  |  |

| nA     | nanoampere                 |  |  |  |  |  |

| ns     | nanosecond                 |  |  |  |  |  |

| nV     | nanovolt                   |  |  |  |  |  |

| Ω      | ohm                        |  |  |  |  |  |

| pF     | picofarad                  |  |  |  |  |  |

| ppm    | parts per million          |  |  |  |  |  |

| ps     | picosecond                 |  |  |  |  |  |

| s      | second                     |  |  |  |  |  |

| sps    | samples per second         |  |  |  |  |  |

| sqrtHz | square root of hertz       |  |  |  |  |  |