Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                     |

| Core Processor             | M8C                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 12MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                            |

| Peripherals                | POR, PWM, WDT                                                                |

| Number of I/O              | 24                                                                           |

| Program Memory Size        | 32KB (32K x 8)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 2K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.25V                                                                   |

| Data Converters            | A/D 12x14b; D/A 4x9b                                                         |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                               |

| Supplier Device Package    | 28-SSOP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c29466-12pvxet |

|                            |                                                                              |

### Contents

| PSoC Functional Overview          | 3  |

|-----------------------------------|----|

| The Digital System                | 3  |

| The Analog System                 |    |

| Additional System Resources       |    |

| PSoC Device Characteristics       |    |

| Getting Started                   |    |

| Application Notes                 |    |

| Development Kits                  | 6  |

| Training                          |    |

| CYPros Consultants                |    |

| Solutions Library                 | 6  |

| Technical Support                 | 6  |

| Development Tools                 | 7  |

| PSoC Designer Software Subsystems | 7  |

| Designing with PSoC Designer      |    |

| Select User Modules               | 7  |

| Configure User Modules            | 8  |

| Organize and Connect              | 8  |

| Generate, Verify, and Debug       | 8  |

| Pinouts                           | 9  |

| 28-pin Part Pinout                | 9  |

| 48-pin Part Pinout                | 10 |

| Registers                         | 11 |

| Register Conventions              | 11 |

| Register Mapping Tables           | 11 |

| Electrical Specifications         | 14 |

| Absolute Maximum Ratings          | 15 |

|     | •                                       |    |

|-----|-----------------------------------------|----|

|     | Operating Temperature                   |    |

|     | DC Electrical Characteristics           | 16 |

|     | AC Electrical Characteristics           | 22 |

| Pac | kaging Information                      |    |

|     | Thermal Impedances                      | 30 |

|     | Capacitance on Crystal Pins             | 30 |

|     | Solder Reflow Specifications            | 30 |

| Deν | relopment Tool Selection                |    |

|     | Software                                |    |

|     | Development Kits                        |    |

|     | Evaluation Tools                        | 31 |

|     | Device Programmers                      | 31 |

|     | Accessories (Emulation and Programming) | 32 |

| Ord | lering Information                      | 32 |

|     | Ordering Code Definitions               | 32 |

| Ref | erence Information                      |    |

|     | Acronyms Used                           | 33 |

|     | Units of Measure                        | 33 |

|     | Numeric Naming                          | 33 |

| Dod | cument History Page                     |    |

|     | es, Solutions, and Legal Information    |    |

|     | Worldwide Sales and Design Support      | 35 |

|     | Products                                | 35 |

|     | PSoC® Solutions                         | 35 |

|     | Cypress Developer Community             | 35 |

|     | Technical Support                       |    |

|     |                                         |    |

### **Development Tools**

PSoC Designer™ is the revolutionary integrated design environment (IDE) that you can use to customize PSoC to meet your specific application requirements. PSoC Designer software accelerates system design and time to market. Develop your applications using a library of precharacterized analog and digital peripherals (called user modules) in a drag-and-drop design environment. Then, customize your design by leveraging the dynamically generated application programming interface (API) libraries of code. Finally, debug and test your designs with the integrated debug environment, including in-circuit emulation and standard software debug features. PSoC Designer includes:

- Application editor graphical user interface (GUI) for device and user module configuration and dynamic reconfiguration

- Extensive user module catalog

- Integrated source-code editor (C and assembly)

- Free C compiler with no size restrictions or time limits

- Built-in debugger

- In-circuit emulation

- Built-in support for communication interfaces:

- ☐ Hardware and software I<sup>2</sup>C slaves and masters

- □ Full-speed USB 2.0

- □ Up to four full-duplex universal asynchronous receiver/transmitters (UARTs), SPI master and slave, and wireless

PSoC Designer supports the entire library of PSoC 1 devices and runs on Windows XP, Windows Vista, and Windows 7.

### **PSoC Designer Software Subsystems**

### Design Entry

In the chip-level view, choose a base device to work with. Then select different onboard analog and digital components that use the PSoC blocks, which are called user modules. Examples of user modules are ADCs, DACs, amplifiers, and filters. Configure the user modules for your chosen application and connect them to each other and to the proper pins. Then generate your project. This prepopulates your project with APIs and libraries that you can use to program your application.

The tool also supports easy development of multiple configurations and dynamic reconfiguration. Dynamic reconfiguration makes it possible to change configurations at run time. In essence, this allows you to use more than 100 percent of PSoC's resources for an application.

### Code Generation Tools

The code generation tools work seamlessly within the PSoC Designer interface and have been tested with a full range of debugging tools. You can develop your design in C, assembly, or a combination of the two.

**Assemblers**. The assemblers allow you to merge assembly code seamlessly with C code. Link libraries automatically use absolute addressing or are compiled in relative mode, and are linked with other software modules to get absolute addressing.

**C Language Compilers**. C language compilers are available that support the PSoC family of devices. The products allow you to create complete C programs for the PSoC family devices. The optimizing C compilers provide all of the features of C, tailored to the PSoC architecture. They come complete with embedded libraries providing port and bus operations, standard keypad and display support, and extended math functionality.

#### Debugger

PSoC Designer has a debug environment that provides hardware in-circuit emulation, allowing you to test the program in a physical system while providing an internal view of the PSoC device. Debugger commands allow you to read and program and read and write data memory, and read and write I/O registers. You can read and write CPU registers, set and clear breakpoints, and provide program run, halt, and step control. The debugger also allows you to create a trace buffer of registers and memory locations of interest.

#### Online Help System

The online help system displays online, context-sensitive help. Designed for procedural and quick reference, each functional subsystem has its own context-sensitive help. This system also provides tutorials and links to FAQs and an online support Forum to aid the designer.

#### In-Circuit Emulator

A low-cost, high-functionality in-circuit emulator (ICE) is available for development support. This hardware can program single devices.

The emulator consists of a base unit that connects to the PC using a USB port. The base unit is universal and operates with all PSoC devices. Emulation pods for each device family are available separately. The emulation pod takes the place of the PSoC device in the target board and performs full-speed (24 MHz) operation.

### **Designing with PSoC Designer**

The development process for the PSoC device differs from that of a traditional fixed function microprocessor. The configurable analog and digital hardware blocks give the PSoC architecture a unique flexibility that pays dividends in managing specification change during development and by lowering inventory costs. These configurable resources, called PSoC Blocks, have the ability to implement a wide variety of user-selectable functions. The PSoC development process is summarized in four steps:

- 1. Select User Modules.

- 2. Configure User Modules.

- 3. Organize and Connect.

- 4. Generate, Verify, and Debug.

#### **Select User Modules**

PSoC Designer provides a library of prebuilt, pretested hardware peripheral components called "user modules." User modules make selecting and implementing peripheral devices, both analog and digital, simple.

### **Pinouts**

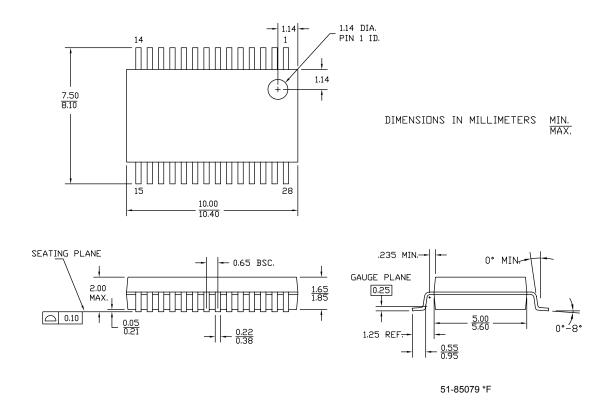

The automotive CY8C29x66 PSoC device is available in a variety of packages which are listed and illustrated in the following tables. Every port pin (labeled with a "P") is capable of Digital I/O. However, Vss, Vdd, and XRES are not capable of Digital I/O.

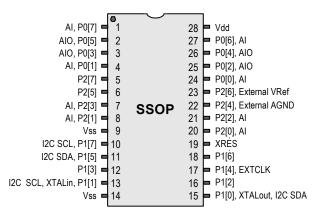

### 28-pin Part Pinout

Table 2. 28-Pin Part Pinout (SSOP)

| Pin | Ту      | pe     | Pin   | December 1                                                                                |  |  |  |  |

|-----|---------|--------|-------|-------------------------------------------------------------------------------------------|--|--|--|--|

| No. | Digital | Analog | Name  | Description                                                                               |  |  |  |  |

| 1   | I/O     |        | P0[7] | Analog column mux input.                                                                  |  |  |  |  |

| 2   | I/O     | I/O    | P0[5] | Analog column mux input and column output.                                                |  |  |  |  |

| 3   | I/O     | I/O    | P0[3] | Analog column mux input and column output.                                                |  |  |  |  |

| 4   | I/O     | ı      | P0[1] | Analog column mux input.                                                                  |  |  |  |  |

| 5   | I/O     |        | P2[7] |                                                                                           |  |  |  |  |

| 6   | I/O     |        | P2[5] |                                                                                           |  |  |  |  |

| 7   | I/O     | ı      | P2[3] | Direct switched capacitor block input.                                                    |  |  |  |  |

| 8   | I/O     | ı      | P2[1] | Direct switched capacitor block input.                                                    |  |  |  |  |

| 9   | Pov     | wer    | Vss   | Ground connection.                                                                        |  |  |  |  |

| 10  | I/O     |        | P1[7] | I <sup>2</sup> C Serial Clock (SCL).                                                      |  |  |  |  |

| 11  | I/O     |        | P1[5] | I <sup>2</sup> C Serial Data (SDA).                                                       |  |  |  |  |

| 12  | I/O     |        | P1[3] |                                                                                           |  |  |  |  |

| 13  | I/O     |        | P1[1] | Crystal Input (XTALin), I <sup>2</sup> C Serial Clock (SCL), ISSP-SCLK <sup>[5]</sup> .   |  |  |  |  |

| 14  | Pov     | wer    | Vss   | Ground connection.                                                                        |  |  |  |  |

| 15  | I/O     |        | P1[0] | Crystal Output (XTALout), I <sup>2</sup> C Serial Data (SDA), ISSP-SDATA <sup>[5]</sup> . |  |  |  |  |

| 16  | I/O     |        | P1[2] |                                                                                           |  |  |  |  |

| 17  | I/O     |        | P1[4] | Optional External Clock Input (EXTCLK).                                                   |  |  |  |  |

| 18  | I/O     |        | P1[6] |                                                                                           |  |  |  |  |

| 19  | Int     | out    | XRES  | Active high external reset with internal pull down.                                       |  |  |  |  |

| 20  | I/O     |        | P2[0] | Direct switched capacitor block input.                                                    |  |  |  |  |

| 21  | I/O     | ı      | P2[2] | Direct switched capacitor block input.                                                    |  |  |  |  |

| 22  | I/O     |        | P2[4] | External Analog Ground (AGND).                                                            |  |  |  |  |

| 23  | I/O     |        | P2[6] | External Voltage Reference (VRef).                                                        |  |  |  |  |

| 24  | I/O     | ı      | P0[0] | Analog column mux input.                                                                  |  |  |  |  |

| 25  | I/O     | I/O    | P0[2] | Analog column mux input and column output.                                                |  |  |  |  |

| 26  | I/O     | I/O    | P0[4] | Analog column mux input and column output.                                                |  |  |  |  |

| 27  | I/O     | ı      | P0[6] | Analog column mux input.                                                                  |  |  |  |  |

| 28  | Pov     | wer    | Vdd   | Supply voltage.                                                                           |  |  |  |  |

Figure 3. CY8C29466 28-pin PSoC Device

**LEGEND**: A = Analog, I = Input, and O = Output.

#### Note

<sup>5.</sup> These are the ISSP pins, which are not High Z when coming out of POR (Power On Reset). See the PSoC Technical Reference Manual for details.

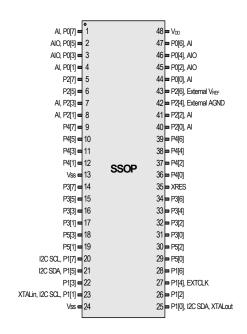

### 48-pin Part Pinout

Table 3. 48-pin Part Pinout (SSOP)

|            |         |              |                 | - /                                                                                     |  |  |  |  |  |  |

|------------|---------|--------------|-----------------|-----------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Pin<br>No. | Digital | pe<br>Analog | Pin<br>Name     | Description                                                                             |  |  |  |  |  |  |

| 1          | I/O     | Allalog      | P0[7]           | Analog column mux input                                                                 |  |  |  |  |  |  |

| 2          | I/O     | I/O          | P0[5]           | Analog column mux input and column output                                               |  |  |  |  |  |  |

| 3          | I/O     | I/O          | P0[3]           | Analog column mux input and column output                                               |  |  |  |  |  |  |

| 4          | I/O     | 1            | P0[1]           | Analog column mux input                                                                 |  |  |  |  |  |  |

| 5          | 1/0     | '            | P2[7]           | 7 thatog column max input                                                               |  |  |  |  |  |  |

| 6          | I/O     |              | P2[5]           |                                                                                         |  |  |  |  |  |  |

| 7          | 1/0     | 1            | P2[3]           | Direct switched capacitor block input                                                   |  |  |  |  |  |  |

| 8          | 1/0     | i            | P2[1]           | Direct switched capacitor block input                                                   |  |  |  |  |  |  |

| 9          | I/O     | '            | P4[7]           | Direct switched capacitor block input                                                   |  |  |  |  |  |  |

| 10         | 1/0     |              | P4[5]           |                                                                                         |  |  |  |  |  |  |

| 11         | 1/0     |              | P4[3]           |                                                                                         |  |  |  |  |  |  |

| 12         | 1/0     |              | P4[1]           |                                                                                         |  |  |  |  |  |  |

| 13         |         | wer          |                 | Ground connection                                                                       |  |  |  |  |  |  |

| 14         |         | WCI          | V <sub>SS</sub> | Ground Connection                                                                       |  |  |  |  |  |  |

|            | 1/0     |              | P3[7]           |                                                                                         |  |  |  |  |  |  |

| 15         | I/O     |              | P3[5]           |                                                                                         |  |  |  |  |  |  |

| 16         | I/O     |              | P3[3]           |                                                                                         |  |  |  |  |  |  |

| 17         | I/O     |              | P3[1]           |                                                                                         |  |  |  |  |  |  |

| 18         | I/O     |              | P5[3]           |                                                                                         |  |  |  |  |  |  |

| 19         | I/O     |              | P5[1]           |                                                                                         |  |  |  |  |  |  |

| 20         | I/O     |              | P1[7]           | I <sup>2</sup> C serial clock (SCL)                                                     |  |  |  |  |  |  |

| 21         | I/O     |              | P1[5]           | I <sup>2</sup> C serial data (SDA)                                                      |  |  |  |  |  |  |

| 22         | I/O     |              | P1[3]           |                                                                                         |  |  |  |  |  |  |

| 23         | I/O     |              | P1[1]           | Crystal input (XTALin), I <sup>2</sup> C serial clock (SCL), ISSP-SCLK <sup>[6]</sup>   |  |  |  |  |  |  |

| 24         | Pov     | wer          | $V_{SS}$        | Ground connection                                                                       |  |  |  |  |  |  |

| 25         | I/O     |              | P1[0]           | Crystal output (XTALout), I <sup>2</sup> C Serial Data (SDA), ISSP-SDATA <sup>[6]</sup> |  |  |  |  |  |  |

| 26         | I/O     |              | P1[2]           |                                                                                         |  |  |  |  |  |  |

| 27         | I/O     |              | P1[4]           | Optional external clock (EXTCLK) input                                                  |  |  |  |  |  |  |

| 28         | I/O     |              | P1[6]           |                                                                                         |  |  |  |  |  |  |

| 29         | I/O     |              | P5[0]           |                                                                                         |  |  |  |  |  |  |

| 30         | I/O     |              | P5[2]           |                                                                                         |  |  |  |  |  |  |

| 31         | I/O     |              | P3[0]           |                                                                                         |  |  |  |  |  |  |

| 32         | I/O     |              | P3[2]           |                                                                                         |  |  |  |  |  |  |

| 33         | I/O     |              | P3[4]           |                                                                                         |  |  |  |  |  |  |

| 34         | I/O     |              | P3[6]           |                                                                                         |  |  |  |  |  |  |

| 35         | Int     | out          | XRES            | Active high external reset with internal pull-down                                      |  |  |  |  |  |  |

| 36         | I/O     |              | P4[0]           |                                                                                         |  |  |  |  |  |  |

| 37         | I/O     |              | P4[2]           |                                                                                         |  |  |  |  |  |  |

| 38         | I/O     |              | P4[4]           |                                                                                         |  |  |  |  |  |  |

| 39         | I/O     |              | P4[6]           |                                                                                         |  |  |  |  |  |  |

| 40         | I/O     | 1            | P2[0]           | Direct switched capacitor block input                                                   |  |  |  |  |  |  |

| 41         | I/O     | i            | P2[2]           | Direct switched capacitor block input                                                   |  |  |  |  |  |  |

| 42         | I/O     |              | P2[4]           | External analog ground (AGND)                                                           |  |  |  |  |  |  |

| 43         | I/O     |              | P2[6]           | External voltage reference (V <sub>RFF</sub> )                                          |  |  |  |  |  |  |

| 44         | I/O     | ı            | P0[0]           | Analog column mux input                                                                 |  |  |  |  |  |  |

| 45         | I/O     | I/O          | P0[2]           | Analog column mux input and column output                                               |  |  |  |  |  |  |

|            |         |              | P0[2]           |                                                                                         |  |  |  |  |  |  |

| 46         | 1/0     | I/O          |                 | Analog column mux input and column output                                               |  |  |  |  |  |  |

| 47         | I/O     |              | P0[6]           | Analog column mux input                                                                 |  |  |  |  |  |  |

| 48         | P0\     | wer          | $V_{DD}$        | Supply voltage                                                                          |  |  |  |  |  |  |

**LEGEND**: A = Analog, I = Input, and O = Output.

Figure 4. CY8C29666 48-pin PSoC Device

### Note

<sup>6.</sup> These are the ISSP pins, which are not high Z when coming out of POR. See the PSoC Technical Reference Manual for details.

### Registers

### **Register Conventions**

This section lists the the registers of the automotive CY8C29x66 PSoC device. For detailed register information, reference the PSoC Technical Reference Manual.

The register conventions specific to this section are listed in the following table.

Table 4. Abbreviations

| Convention | Description                  |

|------------|------------------------------|

| R          | Read register or bit(s)      |

| W          | Write register or bit(s)     |

| L          | Logical register or bit(s)   |

| С          | Clearable register or bit(s) |

| #          | Access is bit specific       |

### **Register Mapping Tables**

The PSoC device has a total register address space of 512 bytes. The register space is referred to as I/O space and is divided into two banks. The XIO bit in the Flag register (CPU\_F) determines which bank the user is currently in. When the XIO bit is set the user is in Bank 1.

**Note** In the following register mapping tables, blank fields are Reserved and should not be accessed.

Table 5. Register Map Bank 0 Table: User Space

| Name     | Addr (0, Hex) | Access   | Name           | Addr (0,Hex) | Access | Name                 | Addr (0,Hex) | Access | Name     | Addr (0,Hex) | Access |

|----------|---------------|----------|----------------|--------------|--------|----------------------|--------------|--------|----------|--------------|--------|

| PRT0DR   | 00            | RW       | DBB20DR0       | 40           | #      | ASC10CR0             | 80           | RW     | RDI2RI   | C0           | RW     |

| PRT0IE   | 01            | RW       | DBB20DR1       | 41           | W      | ASC10CR1             | 81           | RW     | RDI2SYN  | C1           | RW     |

| PRT0GS   | 02            | RW       | DBB20DR2       | 42           | RW     | ASC10CR2             | 82           | RW     | RDI2IS   | C2           | RW     |

| PRT0DM2  | 03            | RW       | DBB20CR0       | 43           | #      | ASC10CR3             | 83           | RW     | RDI2LT0  | C3           | RW     |

| PRT1DR   | 03            | RW       | DBB20CR0       | 44           | #      | ASD11CR0             | 84           | RW     | RDI2LT1  | C4           | RW     |

| PRT1IE   |               |          |                |              |        |                      |              |        |          |              |        |

|          | 05            | RW       | DBB21DR1       | 45           | W      | ASD11CR1             | 85           | RW     | RDI2RO0  | C5           | RW     |

| PRT1GS   | 06            | RW       | DBB21DR2       | 46           | RW     | ASD11CR2             | 86           | RW     | RDI2RO1  | C6           | RW     |

| PRT1DM2  | 07            | RW       | DBB21CR0       | 47           | #      | ASD11CR3             | 87           | RW     |          | C7           |        |

| PRT2DR   | 80            | RW       | DCB22DR0       | 48           | #      | ASC12CR0             | 88           | RW     | RDI3RI   | C8           | RW     |

| PRT2IE   | 09            | RW       | DCB22DR1       | 49           | W      | ASC12CR1             | 89           | RW     | RDI3SYN  | C9           | RW     |

| PRT2GS   | 0A            | RW       | DCB22DR2       | 4A           | RW     | ASC12CR2             | 8A           | RW     | RDI3IS   | CA           | RW     |

| PRT2DM2  | 0B            | RW       | DCB22CR0       | 4B           | #      | ASC12CR3             | 8B           | RW     | RDI3LT0  | CB           | RW     |

| PRT3DR   | 0C            | RW       | DCB23DR0       | 4C           | #      | ASD13CR0             | 8C           | RW     | RDI3LT1  | CC           | RW     |

| PRT3IE   | 0D            | RW       | DCB23DR1       | 4D           | W      | ASD13CR1             | 8D           | RW     | RDI3RO0  | CD           | RW     |

| PRT3GS   | 0E            | RW       | DCB23DR2       | 4E           | RW     | ASD13CR2             | 8E           | RW     | RDI3RO1  | CE           | RW     |

| PRT3DM2  | 0F            | RW       | DCB23CR0       | 4F           | #      | ASD13CR3             | 8F           | RW     |          | CF           |        |

| PRT4DR   | 10            | RW       | DBB30DR0       | 50           | #      | ASD20CR0             | 90           | RW     | CUR PP   | D0           | RW     |

| PRT4IE   | 11            | RW       | DBB30DR1       | 51           | W      | ASD20CR1             | 91           | RW     | STK PP   | D1           | RW     |

| PRT4GS   | 12            | RW       | DBB30DR2       | 52           | RW     | ASD20CR2             | 92           | RW     | 011(_11  | D2           |        |

| PRT4DM2  | 13            | RW       | DBB30DR2       | 53           | #      | ASD20CR2<br>ASD20CR3 | 93           | RW     | IDX PP   | D3           | RW     |

| PRT5DR   | 13            | RW       | DBB30CR0       | 54           | #      | ASC21CR0             | 93           | RW     | MVR PP   | D3           | RW     |

|          |               |          |                |              |        |                      |              |        |          |              |        |

| PRT5IE   | 15            | RW       | DBB31DR1       | 55           | W      | ASC21CR1             | 95           | RW     | MVW_PP   | D5           | RW     |

| PRT5GS   | 16            | RW       | DBB31DR2       | 56           | RW     | ASC21CR2             | 96           | RW     | I2C_CFG  | D6           | RW     |

| PRT5DM2  | 17            | RW       | DBB31CR0       | 57           | #      | ASC21CR3             | 97           | RW     | I2C_SCR  | D7           | #      |

|          | 18            |          | DCB32DR0       | 58           | #      | ASD22CR0             | 98           | RW     | I2C_DR   | D8           | RW     |

|          | 19            |          | DCB32DR1       | 59           | W      | ASD22CR1             | 99           | RW     | I2C_MSCR | D9           | #      |

|          | 1A            |          | DCB32DR2       | 5A           | RW     | ASD22CR2             | 9A           | RW     | INT_CLR0 | DA           | RW     |

|          | 1B            |          | DCB32CR0       | 5B           | #      | ASD22CR3             | 9B           | RW     | INT_CLR1 | DB           | RW     |

|          | 1C            |          | DCB33DR0       | 5C           | #      | ASC23CR0             | 9C           | RW     | INT_CLR2 | DC           | RW     |

|          | 1D            |          | DCB33DR1       | 5D           | W      | ASC23CR1             | 9D           | RW     | INT_CLR3 | DD           | RW     |

|          | 1E            |          | DCB33DR2       | 5E           | RW     | ASC23CR2             | 9E           | RW     | INT MSK3 | DE           | RW     |

|          | 1F            |          | DCB33CR0       | 5F           | #      | ASC23CR3             | 9F           | RW     | INT MSK2 | DF           | RW     |

| DBB00DR0 | 20            | #        | AMX IN         | 60           | RW     |                      | A0           |        | INT MSK0 | E0           | RW     |

| DBB00DR1 | 21            | W        | 7 11127 (_11.1 | 61           |        |                      | A1           |        | INT MSK1 | E1           | RW     |

| DBB00DR2 | 22            | RW       |                | 62           |        |                      | A2           |        | INT VC   | E2           | RC     |

| DBB00CR0 | 23            | #        | ARF CR         | 63           | RW     |                      | A3           |        | RES WDT  | E3           | W      |

| DBB00CR0 | 24            | #        | CMP CR0        | 64           | #      |                      | A4           |        | DEC DH   | E4           | RC     |

|          |               |          |                |              | #      |                      |              |        | DEC_DH   |              |        |

| DBB01DR1 | 25            | W        | ASY_CR         | 65           |        |                      | A5           |        | _        | E5           | RC     |

| DBB01DR2 | 26            | RW       | CMP_CR1        | 66           | RW     |                      | A6           |        | DEC_CR0  | E6           | RW     |

| DBB01CR0 | 27            | #        |                | 67           |        |                      | A7           |        | DEC_CR1  | E7           | RW     |

| DCB02DR0 | 28            | #        |                | 68           |        | MUL1_X               | A8           | W      | MUL0_X   | E8           | W      |

| DCB02DR1 | 29            | W        |                | 69           |        | MUL1_Y               | A9           | W      | MUL0_Y   | E9           | W      |

| DCB02DR2 | 2A            | RW       |                | 6A           |        | MUL1_DH              | AA           | R      | MUL0_DH  | EA           | R      |

| DCB02CR0 | 2B            | #        |                | 6B           |        | MUL1_DL              | AB           | R      | MUL0_DL  | EB           | R      |

| DCB03DR0 | 2C            | #        | TMP_DR0        | 6C           | RW     | ACC1_DR1             | AC           | RW     | ACC0_DR1 | EC           | RW     |

| DCB03DR1 | 2D            | W        | TMP_DR1        | 6D           | RW     | ACC1_DR0             | AD           | RW     | ACC0_DR0 | ED           | RW     |

| DCB03DR2 | 2E            | RW       | TMP_DR2        | 6E           | RW     | ACC1_DR3             | AE           | RW     | ACC0_DR3 | EE           | RW     |

| DCB03CR0 | 2F            | #        | TMP_DR3        | 6F           | RW     | ACC1_DR2             | AF           | RW     | ACC0_DR2 | EF           | RW     |

| DBB10DR0 | 30            | #        | ACB00CR3       | 70           | RW     | RDI0RI               | В0           | RW     |          | F0           |        |

| DBB10DR1 | 31            | W        | ACB00CR0       | 71           | RW     | RDI0SYN              | B1           | RW     |          | F1           |        |

| DBB10DR2 | 32            | RW       | ACB00CR1       | 72           | RW     | RDI0IS               | B2           | RW     |          | F2           |        |

| DBB10CR0 | 33            | #        | ACB00CR2       | 73           | RW     | RDI0LT0              | B3           | RW     |          | F3           |        |

| DBB11DR0 | 34            | #        | ACB01CR3       | 74           | RW     | RDI0LT1              | B4           | RW     |          | F4           |        |

| DBB11DR0 | 35            | W W      | ACB01CR3       | 75           | RW     | RDI0RO0              | B5           | RW     |          | F5           |        |

|          |               |          |                |              |        |                      |              |        |          |              |        |

| DBB11DR2 | 36            | RW       | ACB01CR1       | 76           | RW     | RDI0RO1              | B6           | RW     | CDU F    | F6           | r.     |

| DBB11CR0 | 37            | #        | ACB01CR2       | 77           | RW     | DDI4B;               | B7           | D) * / | CPU_F    | F7           | RL     |

| DCB12DR0 | 38            | #        | ACB02CR3       | 78           | RW     | RDI1RI               | B8           | RW     |          | F8           |        |

| DCB12DR1 | 39            | W        | ACB02CR0       | 79           | RW     | RDI1SYN              | B9           | RW     |          | F9           |        |

| DCB12DR2 | 3A            | RW       | ACB02CR1       | 7A           | RW     | RDI1IS               | BA           | RW     |          | FA           |        |

| DCB12CR0 | 3B            | #        | ACB02CR2       | 7B           | RW     | RDI1LT0              | BB           | RW     |          | FB           |        |

| DCB13DR0 | 3C            | #        | ACB03CR3       | 7C           | RW     | RDI1LT1              | BC           | RW     |          | FC           |        |

| DCB13DR1 | 3D            | W        | ACB03CR0       | 7D           | RW     | RDI1RO0              | BD           | RW     |          | FD           |        |

| DCB13DR2 | 3E            | RW       | ACB03CR1       | 7E           | RW     | RDI1RO1              | BE           | RW     | CPU SCR1 | FE           | #      |

| DCB13CR0 | 3F            | #        | ACB03CR2       | 7F           | RW     |                      | BF           |        | CPU SCR0 | FF           | #      |

|          | <u> </u>      | <u> </u> |                |              |        | •                    | <u> </u>     |        |          | <u> </u>     | •      |

Blank fields are Reserved and should not be accessed.

# Access is bit specific.

Table 6. Register Map Bank 1 Table: Configuration Space

| Name               | Addr (1,Hex) | Access | Name               | Addr (1,Hex) | Access | Name                 | Addr (1,Hex) | Access | Name      | Addr (1,Hex) | Access |

|--------------------|--------------|--------|--------------------|--------------|--------|----------------------|--------------|--------|-----------|--------------|--------|

| PRT0DM0            | 00           | RW     | DBB20FN            | 40           | RW     | ASC10CR0             | 80           | RW     | RDI2RI    | C0           | RW     |

| PRT0DM1            | 01           | RW     | DBB20IN            | 41           | RW     | ASC10CR1             | 81           | RW     | RDI2SYN   | C1           | RW     |

| PRT0IC0            | 02           | RW     | DBB20OU            | 42           | RW     | ASC10CR2             | 82           | RW     | RDI2IS    | C2           | RW     |

| PRT0IC1            | 03           | RW     |                    | 43           |        | ASC10CR3             | 83           | RW     | RDI2LT0   | C3           | RW     |

| PRT1DM0            | 04           | RW     | DBB21FN            | 44           | RW     | ASD11CR0             | 84           | RW     | RDI2LT1   | C4           | RW     |

| PRT1DM1            | 05           | RW     | DBB21IN            | 45           | RW     | ASD11CR1             | 85           | RW     | RDI2RO0   | C5           | RW     |

| PRT1IC0            | 06           | RW     | DBB210U            | 46           | RW     | ASD11CR2             | 86           | RW     | RDI2RO1   | C6           | RW     |

| PRT1IC1            | 07           | RW     | DBB2100            | 47           | IXVV   | ASD11CR2<br>ASD11CR3 | 87           | RW     | RDIZROT   | C7           | IXVV   |

| PRT2DM0            | 08           | RW     | DCB22FN            | 48           | RW     | ASC12CR0             | 88           | RW     | RDI3RI    | C8           | RW     |

|                    |              |        |                    |              |        | ASC12CR0<br>ASC12CR1 |              |        | RDI3SYN   |              |        |

| PRT2DM1            | 09           | RW     | DCB22IN<br>DCB22OU | 49           | RW     |                      | 89           | RW     | RDI3IS    | C9           | RW     |

| PRT2IC0            | 0A           | RW     | DCB2200            | 4A           | RW     | ASC12CR2             | 8A           | RW     |           | CA           | RW     |

| PRT2IC1            | 0B           | RW     | BOBOSELL           | 4B           | D) 47  | ASC12CR3             | 8B           | RW     | RDI3LT0   | СВ           | RW     |

| PRT3DM0            | 0C           | RW     | DCB23FN            | 4C           | RW     | ASD13CR0             | 8C           | RW     | RDI3LT1   | CC           | RW     |

| PRT3DM1            | 0D           | RW     | DCB23IN            | 4D           | RW     | ASD13CR1             | 8D           | RW     | RDI3RO0   | CD           | RW     |

| PRT3IC0            | 0E           | RW     | DCB23OU            | 4E           | RW     | ASD13CR2             | 8E           | RW     | RDI3RO1   | CE           | RW     |

| PRT3IC1            | 0F           | RW     |                    | 4F           |        | ASD13CR3             | 8F           | RW     |           | CF           |        |

| PRT4DM0            | 10           | RW     | DBB30FN            | 50           | RW     | ASD20CR0             | 90           | RW     | GDI_O_IN  | D0           | RW     |

| PRT4DM1            | 11           | RW     | DBB30IN            | 51           | RW     | ASD20CR1             | 91           | RW     | GDI_E_IN  | D1           | RW     |

| PRT4IC0            | 12           | RW     | DBB30OU            | 52           | RW     | ASD20CR2             | 92           | RW     | GDI_O_OU  | D2           | RW     |

| PRT4IC1            | 13           | RW     |                    | 53           |        | ASD20CR3             | 93           | RW     | GDI E OU  | D3           | RW     |

| PRT5DM0            | 14           | RW     | DBB31FN            | 54           | RW     | ASC21CR0             | 94           | RW     |           | D4           |        |

| PRT5DM1            | 15           | RW     | DBB31IN            | 55           | RW     | ASC21CR1             | 95           | RW     |           | D5           |        |

| PRT5IC0            | 16           | RW     | DBB31OU            | 56           | RW     | ASC21CR2             | 96           | RW     |           | D6           |        |

| PRT5IC1            | 17           | RW     | BBB0100            | 57           | 1 (1 ) | ASC21CR3             | 97           | RW     |           | D7           |        |

| 11(13)()1          | 18           | 1744   | DCB32FN            | 58           | RW     | ASD22CR0             | 98           | RW     |           | D8           |        |

|                    | 19           |        | DCB32IN            | 59           | RW     | ASD22CR0<br>ASD22CR1 | 99           | RW     |           | D9           |        |

|                    | 19<br>1A     |        | DCB32IN<br>DCB32OU | 59<br>5A     |        | ASD22CR1             | 99<br>9A     | RW     |           | DA           |        |

|                    |              |        | DCB3200            |              | RW     |                      |              |        |           |              |        |

|                    | 1B           |        | D.O.D.O.E.L.       | 5B           | 5147   | ASD22CR3             | 9B           | RW     |           | DB           |        |

|                    | 1C           |        | DCB33FN            | 5C           | RW     | ASC23CR0             | 9C           | RW     |           | DC           |        |

|                    | 1D           |        | DCB33IN            | 5D           | RW     | ASC23CR1             | 9D           | RW     | OSC_GO_EN | DD           | RW     |

|                    | 1E           |        | DCB33OU            | 5E           | RW     | ASC23CR2             | 9E           | RW     | OSC_CR4   | DE           | RW     |

|                    | 1F           |        |                    | 5F           |        | ASC23CR3             | 9F           | RW     | OSC_CR3   | DF           | RW     |

| DBB00FN            | 20           | RW     | CLK_CR0            | 60           | RW     |                      | A0           |        | OSC_CR0   | E0           | RW     |

| DBB00IN            | 21           | RW     | CLK_CR1            | 61           | RW     |                      | A1           |        | OSC_CR1   | E1           | RW     |

| DBB00OU            | 22           | RW     | ABF_CR0            | 62           | RW     |                      | A2           |        | OSC_CR2   | E2           | RW     |

|                    | 23           |        | AMD_CR0            | 63           | RW     |                      | A3           |        | VLT_CR    | E3           | RW     |

| DBB01FN            | 24           | RW     |                    | 64           |        |                      | A4           |        | VLT_CMP   | E4           | R      |

| DBB01IN            | 25           | RW     |                    | 65           |        |                      | A5           |        |           | E5           |        |

| DBB01OU            | 26           | RW     | AMD_CR1            | 66           | RW     |                      | A6           |        |           | E6           |        |

|                    | 27           |        | ALT CR0            | 67           | RW     |                      | A7           |        |           | E7           |        |

| DCB02FN            | 28           | RW     | ALT CR1            | 68           | RW     |                      | A8           |        | IMO TR    | E8           | W      |

| DCB02IN            | 29           | RW     | CLK CR2            | 69           | RW     |                      | A9           |        | ILO TR    | E9           | W      |

| DCB02OU            | 2A           | RW     |                    | 6A           |        |                      | AA           |        | BDG_TR    | EA           | RW     |

|                    | 2B           |        |                    | 6B           |        |                      | AB           |        | ECO_TR    | EB           | W      |

| DCB03FN            | 2C           | RW     | TMP DR0            | 6C           | RW     |                      | AC           |        |           | EC           |        |

| DCB03IN            | 2D           | RW     | TMP_DR1            | 6D           | RW     |                      | AD           |        |           | ED           |        |

| DCB03IN            | 2E           | RW     | TMP_DR1            | 6E           | RW     | <b>-</b>             | AE           |        |           | EE           |        |

| PCB0300            | 2F           | LVVV   |                    | 6F           | RW     | -                    | AF           |        |           | EF           |        |

| DDD40EN            | 30           | DVA    | TMP_DR3            |              |        | DDIODI               |              | DIA    |           | F0           |        |

| DBB10FN            |              | RW     | ACBOOCR3           | 70           | RW     | RDI0RI               | B0           | RW     |           |              |        |

| DBB10IN            | 31           | RW     | ACB00CR0           | 71           | RW     | RDI0SYN              | B1           | RW     |           | F1           |        |

| DBB10OU            | 32           | RW     | ACB00CR1           | 72           | RW     | RDI0IS               | B2           | RW     |           | F2           |        |

|                    | 33           |        | ACB00CR2           | 73           | RW     | RDI0LT0              | B3           | RW     |           | F3           |        |

| DBB11FN            | 34           | RW     | ACB01CR3           | 74           | RW     | RDI0LT1              | B4           | RW     |           | F4           |        |

| DBB11IN            | 35           | RW     | ACB01CR0           | 75           | RW     | RDI0RO0              | B5           | RW     |           | F5           |        |

| DBB11OU            | 36           | RW     | ACB01CR1           | 76           | RW     | RDI0RO1              | B6           | RW     |           | F6           |        |

|                    | 37           |        | ACB01CR2           | 77           | RW     |                      | B7           |        | CPU_F     | F7           | RL     |

| DCB12FN            | 38           | RW     | ACB02CR3           | 78           | RW     | RDI1RI               | B8           | RW     |           | F8           |        |

| DCB12IN            | 39           | RW     | ACB02CR0           | 79           | RW     | RDI1SYN              | В9           | RW     |           | F9           |        |

| DCB12OU            | 3A           | RW     | ACB02CR1           | 7A           | RW     | RDI1IS               | BA           | RW     | FLS PR1   | FA           | RW     |

|                    | 3B           |        | ACB02CR2           | 7B           | RW     | RDI1LT0              | BB           | RW     | _         | FB           |        |

| DCB13FN            | 3C           | RW     | ACB03CR3           | 7C           | RW     | RDI1LT1              | BC           | RW     |           | FC           |        |

| DCB13IN            | 3D           | RW     | ACB03CR0           | 7D           | RW     | RDI1RO0              | BD           | RW     |           | FD           |        |

| DCB13IN<br>DCB13OU | 3E           | RW     | ACB03CR0           | 7E           | RW     | RDI1RO1              | BE           | RW     | CPU SCR1  | FE           | #      |

| 2001300            | 3F           | 1744   | ACB03CR1           | 7E<br>7F     | RW     | RUINOI               | BF           | 1744   | CPU_SCR1  | FF           | #      |

|                    | 3F           |        | AUDUSUKZ           | / F          | L/AA   |                      | DF.          |        | OFU_SCRU  | FF           | #      |

Blank fields are Reserved and should not be accessed.

# Access is bit specific.

## **Electrical Specifications**

This section presents the DC and AC electrical specifications of the automotive CY8C29x66 PSoC device. For the most up to date electrical specifications, confirm that you have the most recent data sheet by visiting <a href="http://www.cypress.com">http://www.cypress.com</a>.

Specifications are valid for –40  $^{\circ}C \leq T_{A} \leq$  125  $^{\circ}C$  and  $T_{J} \leq$  135  $^{\circ}C,$  except where noted.

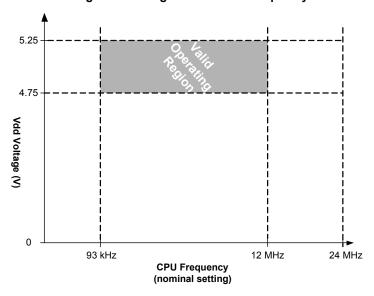

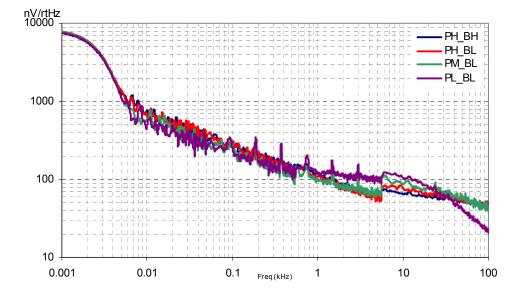

Figure 5. Voltage versus CPU Frequency

### **Absolute Maximum Ratings**

Exceeding maximum ratings may shorten the useful life of the device. User guidelines are not tested.

**Table 7. Absolute Maximum Ratings**

| Symbol                | Description                            | Min                     | Тур | Max                     | Units | Notes                                                                                                                                                                                                                                    |

|-----------------------|----------------------------------------|-------------------------|-----|-------------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T <sub>STG</sub>      | Storage Temperature                    | <b>-</b> 55             | +25 | +125                    | °C    | Higher storage temperatures reduce data retention time. Recommended storage temperature is +25 °C ± 25 °C. Storage temperatures above 65 °C degrade reliability. Maximum combined storage and operational time at +125 °C is 7000 hours. |

| T <sub>BAKETEMP</sub> | Bake Temperature                       | _                       | 125 | See<br>package<br>label | °C    |                                                                                                                                                                                                                                          |

| T <sub>BAKETIME</sub> | Bake Time                              | See<br>package<br>label | _   | 72                      | Hours |                                                                                                                                                                                                                                          |

| T <sub>A</sub>        | Ambient Temperature with Power Applied | -40                     | -   | +125                    | °C    |                                                                                                                                                                                                                                          |

| Vdd                   | Supply Voltage on Vdd Relative to Vss  | -0.5                    | -   | +6.0                    | V     |                                                                                                                                                                                                                                          |

| V <sub>IO</sub>       | DC Input Voltage                       | Vss - 0.5               | _   | Vdd + 0.5               | V     |                                                                                                                                                                                                                                          |

| $V_{IOZ}$             | DC Voltage Applied to Tri-state        | Vss - 0.5               | -   | Vdd + 0.5               | V     |                                                                                                                                                                                                                                          |

| I <sub>MIO</sub>      | Maximum Current into any Port Pin      | -25                     | -   | +25                     | mA    |                                                                                                                                                                                                                                          |

| ESD                   | Electro Static Discharge Voltage       | 2000                    | -   | -                       | V     | Human Body Model ESD.                                                                                                                                                                                                                    |

| LU                    | Latch up Current                       | _                       | _   | 200                     | mA    |                                                                                                                                                                                                                                          |

### **Operating Temperature**

**Table 8. Operating Temperature**

| Symbol         | Description          | Min             | Тур | Max  | Units | Notes                                                                                                                                                                            |

|----------------|----------------------|-----------------|-----|------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T <sub>A</sub> | Ambient Temperature  | -40             | _   | +125 | °C    |                                                                                                                                                                                  |

| Т              | Junction Temperature | <del>-4</del> 0 | 1   | +135 | °C    | The temperature rise from ambient to junction is package specific. See Thermal Impedances on page 30. The user must limit the power consumption to comply with this requirement. |

### **DC Electrical Characteristics**

DC Chip-Level Specifications

The following table lists guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and  $-40~^{\circ}\text{C} \le T_{A} \le 125~^{\circ}\text{C}$ . Typical parameters apply to 5 V at 25  $^{\circ}\text{C}$  and are for design guidance only.

Table 9. DC Chip-Level Specifications

| Symbol              | Description                                                                                                    | Min  | Тур | Max  | Units | Notes                                                                                                                                                         |

|---------------------|----------------------------------------------------------------------------------------------------------------|------|-----|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Vdd                 | Supply Voltage                                                                                                 | 4.75 | -   | 5.25 | V     |                                                                                                                                                               |

| I <sub>DD</sub>     | Supply Current                                                                                                 | -    | 8   | 15   | mA    | Conditions are $-40$ °C $\leq$ T <sub>A</sub> $\leq$ 125 °C, CPU=3 MHz, 48 MHz disabled. VC1 = 1.5 MHz, VC2 = 93.75 kHz, VC3 = 0.366 kHz. Analog power = off. |

| I <sub>SB</sub>     | Sleep (Mode) Current with POR, LVD, Sleep Timer, and WDT. <sup>[7]</sup>                                       | -    | 6   | 16   | μА    | Conditions are with internal low speed oscillator active, $-40~^{\circ}C \le T_{A} \le 55~^{\circ}C$ . Analog power = off.                                    |

| I <sub>SBH</sub>    | Sleep (Mode) Current with POR, LVD, Sleep Timer, and WDT at high temperature <sup>[7]</sup>                    | _    | 6   | 100  | μА    | Conditions are with internal low speed oscillator active, 55 °C < $T_A \le 125$ °C. Analog power = off.                                                       |

| I <sub>SBXTL</sub>  | Sleep (Mode) Current with POR, LVD, Sleep Timer, WDT, and external crystal. <sup>[7]</sup>                     | -    | 8   | 18   | μА    | Conditions are with properly loaded, 1 $\mu$ W max, 32.768 kHz crystal. –40 °C $\leq$ T <sub>A</sub> $\leq$ 55 °C. Analog power = off.                        |

| I <sub>SBXTLH</sub> | Sleep (Mode) Current with POR, LVD, Sleep Timer, WDT, and external crystal at high temperature. <sup>[7]</sup> | -    | 8   | 100  | μА    | Conditions are with properly loaded, 1 $\mu$ W max, 32.768 kHz crystal. 55 °C < $T_A \le$ 125 °C. Analog power = off.                                         |

| V <sub>REF</sub>    | Reference Voltage (Bandgap)                                                                                    | 1.25 | 1.3 | 1.35 | V     |                                                                                                                                                               |

Document Number: 38-12026 Rev. \*N Page 16 of 35

Note

Standby current includes all functions (POR, LVD, WDT, Sleep Timer) needed for reliable system operation. This must be compared with devices that have similar functions enabled.

### DC General Purpose I/O Specifications

The following table lists guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and  $-40~^{\circ}\text{C} \le T_{A} \le 125~^{\circ}\text{C}$ . Typical parameters apply to 5 V at 25  $^{\circ}\text{C}$  and are for design guidance only.

Table 10. DC GPIO Specifications

| Symbol           | Description                       | Min | Тур | Max  | Units | Notes                                                                                                                                                                                                                                  |

|------------------|-----------------------------------|-----|-----|------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R <sub>PU</sub>  | Pull up Resistor                  | 4   | 5.6 | 8    | kΩ    |                                                                                                                                                                                                                                        |

| R <sub>PD</sub>  | Pull down Resistor                | 4   | 5.6 | 8    | kΩ    |                                                                                                                                                                                                                                        |

| V <sub>OH</sub>  | High Output Level                 | 3.5 | -   | _    | V     | I <sub>OH</sub> = 10 mA, Vdd = 4.75 to 5.25 V<br>(maximum 40 mA on even port pins<br>(for example, P0[2], P1[4]),<br>maximum 40 mA on odd port pins<br>(for example, P0[3], P1[5])). 80 mA<br>maximum combined I <sub>OH</sub> budget. |

| V <sub>OL</sub>  | Low Output Level                  | _   | _   | 0.75 | V     | I <sub>OL</sub> = 25 mA, Vdd = 4.75 to 5.25 V (maximum 100 mA on even port pins (for example, P0[2], P1[4]), maximum 100 mA on odd port pins (for example, P0[3], P1[5])). 150 mA maximum combined I <sub>OL</sub> budget.             |

| I <sub>OH</sub>  | High Level Source Current         | 10  | _   | _    | mA    | $V_{OH} \ge Vdd-1.0 \text{ V}$ , see the limitations of the total current in the note for $V_{OH}$                                                                                                                                     |

| I <sub>OL</sub>  | Low Level Sink Current            | 25  | _   | _    | mA    | $V_{OL} \le 0.75$ V, see the limitations of the total current in the note for $V_{OL}$                                                                                                                                                 |

| $V_{IL}$         | Input Low Level                   | _   | _   | 0.8  | V     |                                                                                                                                                                                                                                        |

| V <sub>IH</sub>  | Input High Level                  | 2.1 | _   |      | V     |                                                                                                                                                                                                                                        |

| $V_{H}$          | Input Hysterisis                  | _   | 60  | _    | mV    |                                                                                                                                                                                                                                        |

| I <sub>IL</sub>  | Input Leakage (Absolute Value)    | _   | 1   | _    | nA    | Gross tested to 1 μA.                                                                                                                                                                                                                  |

| C <sub>IN</sub>  | Capacitive Load on Pins as Input  | _   | 3.5 | 10   | pF    | Package and pin dependent.<br>Temp = 25 °C.                                                                                                                                                                                            |

| C <sub>OUT</sub> | Capacitive Load on Pins as Output | -   | 3.5 | 10   | pF    | Package and pin dependent.<br>Temp = 25 °C.                                                                                                                                                                                            |

### DC Low Power Comparator Specifications

The following tables list guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and  $-40 \,^{\circ}\text{C} \le T_{A} \le 125 \,^{\circ}\text{C}$ . Typical parameters apply to 5 V at  $25 \,^{\circ}\text{C}$  and are for design guidance only.

Table 12. DC Low Power Comparator Specifications

| Symbol              | Description                                        | Min | Тур | Max     | Units | Notes |

|---------------------|----------------------------------------------------|-----|-----|---------|-------|-------|

| V <sub>REFLPC</sub> | Low power comparator (LPC) reference voltage range | 0.2 | _   | Vdd – 1 | V     |       |

| I <sub>SLPC</sub>   | LPC supply current                                 | _   | 10  | 40      | μΑ    |       |

| V <sub>OSLPC</sub>  | LPC voltage offset                                 | _   | 2.5 | 30      | mV    |       |

### DC Analog Output Buffer Specifications

The following tables list guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and  $-40~^{\circ}\text{C} \le T_{A} \le 125~^{\circ}\text{C}$ . Typical parameters apply to 5 V at 25  $^{\circ}\text{C}$  and are for design guidance only.

Table 13. DC Analog Output Buffer Specifications

| Symbol               | Description                                                           | Min                | Тур        | Max                | Units    | Notes |

|----------------------|-----------------------------------------------------------------------|--------------------|------------|--------------------|----------|-------|

| V <sub>OSOB</sub>    | Input Offset Voltage (Absolute Value)                                 | _                  | 3          | 18                 | mV       |       |

| TCV <sub>OSOB</sub>  | Input Offset Voltage Drift                                            | _                  | +6         | _                  | μV/°C    |       |

| V <sub>CMOB</sub>    | Common-Mode Input Voltage Range                                       | 0.5                | -          | Vdd – 1.0          | V        |       |

| R <sub>OUTOB</sub>   | Output Resistance                                                     | _                  | 1          | _                  | W        |       |

| V <sub>OHIGHOB</sub> | High Output Voltage Swing (Load = $32\Omega$ to Vdd/2)                | 0.5 x Vdd +<br>1.1 | -          | _                  | V        |       |

| V <sub>OLOWOB</sub>  | Low Output Voltage Swing (Load = $32\Omega$ to Vdd/2)                 | _                  | _          | 0.5 x Vdd –<br>1.3 | V        |       |

| I <sub>SOB</sub>     | Supply Current Including Bias Cell (No Load) Power = Low Power = High |                    | 1.1<br>2.6 | 5.1<br>8.8         | mA<br>mA |       |

| PSRR <sub>OB</sub>   | Supply Voltage Rejection Ratio                                        | _                  | 64         | -                  | dB       |       |

Document Number: 38-12026 Rev. \*N Page 19 of 35

### DC Analog Reference Specifications

The following tables list guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and  $-40 \,^{\circ}\text{C} \le T_A \le 125 \,^{\circ}\text{C}$ . Typical parameters apply to  $5 \,^{\circ}\text{V}$  at  $25 \,^{\circ}\text{C}$  and are for design guidance only.

The guaranteed specifications for RefHI and RefLO are measured through the analog continuous time PSoC blocks. The power levels for RefHI and RefLO refer to the analog reference control register. AGND is measured at P2[4] in AGND bypass mode. Each analog continuous time PSoC block adds a maximum of 10 mV additional offset error to guaranteed AGND specifications from the local AGND buffer. Reference control power can be set to medium or high unless otherwise noted.

**Note** Avoid using P2[4] for digital signaling when using an analog resource that depends on the Analog Reference. Some coupling of the digital signal may appear on the AGND.

Table 14. DC Analog Reference Specifications

| Symbol   | Description                                                            | Min                 | Тур           | Max                 | Units |

|----------|------------------------------------------------------------------------|---------------------|---------------|---------------------|-------|

| $V_{BG}$ | Bandgap Voltage Reference                                              | 1.25                | 1.30          | 1.35                | V     |

| _        | $AGND = Vdd/2^{[8]}$                                                   | Vdd/2 - 0.02        | Vdd/2         | Vdd/2 + 0.02        | V     |

| _        | AGND = 2 x BandGap <sup>[8]</sup>                                      | 2.4                 | 2.6           | 2.8                 | V     |

| _        | AGND = P2[4] (P2[4] = Vdd/2) <sup>[8]</sup>                            | P2[4] - 0.02        | P2[4]         | P2[4] + 0.02        | V     |

| _        | AGND = BandGap <sup>[8]</sup>                                          | 1.23                | 1.3           | 1.37                | V     |

| _        | AGND = 1.6 x BandGap <sup>[8]</sup>                                    | 1.98                | 2.08          | 2.14                | V     |

| _        | AGND Column to Column Variation (AGND=Vdd/2) <sup>[8]</sup>            | 0.035               | 0.000         | 0.035               | V     |

| _        | RefHi = Vdd/2 + BandGap <sup>[9]</sup>                                 | Vdd/2 + 1.15        | Vdd/2 + 1.30  | Vdd/2 + 1.45        | V     |

| _        | RefHi = 3 x BandGap <sup>[9]</sup>                                     | 3.65                | 3.9           | 4.15                | V     |

| _        | RefHi = 2 x BandGap + P2[6] (P2[6] = 1.3 V)[9]                         | P2[6] + 2.4         | P2[6] + 2.6   | P2[6] + 2.8         | V     |

| _        | RefHi = P2[4] + BandGap (P2[4] = Vdd/2) <sup>[9]</sup>                 | P2[4] + 1.24        | P2[4] + 1.30  | P2[4] + 1.36        | V     |

| _        | RefHi = P2[4] + P2[6] (P2[4] = Vdd/2, P2[6] = 1.3 V) <sup>[9]</sup>    | P2[4] + P2[6] – 0.1 | P2[4] + P2[6] | P2[4] + P2[6] + 0.1 | V     |

| _        | RefHi = 2 x BandGap <sup>[9]</sup>                                     | 2.4                 | 2.6           | 2.8                 | V     |

| _        | RefHi = 3.2 x BandGap <sup>[9]</sup>                                   | 3.9                 | 4.16          | 4.42                | V     |

| _        | RefLo = Vdd/2 - BandGap <sup>[9]</sup>                                 | Vdd/2 - 1.45        | Vdd/2 - 1.3   | Vdd/2 - 1.15        | V     |

| _        | RefLo = BandGap <sup>[9]</sup>                                         | 1.15                | 1.30          | 1.45                | V     |

| _        | RefLo = $2 \times BandGap - P2[6] (P2[6] = 1.3 \text{ V})^{[9]}$       | 2.4 – P2[6]         | 2.6 - P2[6]   | 2.8 – P2[6]         | V     |

| _        | RefLo = P2[4] - BandGap (P2[4] = Vdd/2) <sup>[9]</sup>                 | P2[4] - 1.45        | P2[4] – 1.3   | P2[4] – 1.15        | V     |

| -        | RefLo = P2[4] - P2[6] (P2[4] = Vdd/2,<br>P2[6] = 1.3 V) <sup>[9]</sup> | P2[4] – P2[6] – 0.1 | P2[4] – P2[6] | P2[4] – P2[6] + 0.1 | V     |

### DC Analog PSoC Block Specifications

The following table lists guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and  $-40 \,^{\circ}\text{C} \leq T_A \leq 125 \,^{\circ}\text{C}$ . Typical parameters apply to  $5 \,^{\circ}\text{V}$  at  $25 \,^{\circ}\text{C}$  and are for design guidance only.

Table 15. DC Analog PSoC Block Specifications

| S | ymbol | Description                           | Min | Тур   | Max | Units | Notes |

|---|-------|---------------------------------------|-----|-------|-----|-------|-------|

| R | СТ    | Resistor Unit Value (Continuous Time) | _   | 12.24 | _   | kΩ    |       |

| C | SC    | Capacitor Unit Value (Switch Cap)     | _   | 80    | _   | fF    |       |

#### Notes

- 8. This specification is only valid when CT Block Power = High. AGND tolerance includes the offsets of the local buffer in the PSoC block.

- 9. This specification is only valid when Ref Control Power = High.

### DC POR and LVD Specifications

The following table lists guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and -40 °C  $\leq T_A \leq 125$  °C. Typical parameters apply to 5 V at 25 °C and are for design guidance only.

Table 16. DC POR and LVD Specifications

| Symbol                                 | Description                                                | Min           | Тур           | Max           | Units  | Notes                                                                                                       |

|----------------------------------------|------------------------------------------------------------|---------------|---------------|---------------|--------|-------------------------------------------------------------------------------------------------------------|

| V <sub>PPOR2</sub>                     | Vdd Value for PPOR Trip<br>PORLEV[1:0] = 10b               | _             | 4.55          | 4.70          | V      | Vdd must be greater than or equal to 2.5 V during startup, reset from the XRES pin, or reset from watchdog. |

| V <sub>LVD6</sub><br>V <sub>LVD7</sub> | Vdd Value for LVD Trip<br>VM[2:0] = 110b<br>VM[2:0] = 111b | 4.62<br>4.710 | 4.73<br>4.814 | 4.83<br>4.950 | V<br>V |                                                                                                             |

### DC Programming Specifications

The following table lists guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and –40 °C ≤ T<sub>A</sub> ≤ 125 °C. Typical parameters apply to 5 V at 25 °C and are for design guidance only.

**Table 17. DC Programming Specifications**

| Symbol                | Description                                                                                 | Min    | Тур | Max     | Units | Notes                                |

|-----------------------|---------------------------------------------------------------------------------------------|--------|-----|---------|-------|--------------------------------------|

| I <sub>DDP</sub>      | Supply Current During Programming or Verify                                                 | _      | 15  | 30      | mA    |                                      |

| V <sub>ILP</sub>      | Input Low Voltage During Programming or Verify                                              | _      | -   | 0.8     | V     |                                      |

| V <sub>IHP</sub>      | Input High Voltage During Programming or Verify                                             |        | -   | _       | V     |                                      |

| I <sub>ILP</sub>      | Input Current when Applying V <sub>ILP</sub> to P1[0] or P1[1] During Programming or Verify |        | _   | 0.2     | mA    | Driving internal pull down resistor. |

| I <sub>IHP</sub>      | Input Current when Applying V <sub>IHP</sub> to P1[0] or P1[1] During Programming or Verify | _      | _   | – 1.5 n |       | Driving internal pull down resistor. |

| V <sub>OLV</sub>      | Output Low Voltage During Programming or Verify                                             | _      | _   | 0.75    | V     |                                      |

| V <sub>OHV</sub>      | Output High Voltage During Programming or Verify                                            | 3.5    | _   | Vdd     | V     |                                      |

| Flash <sub>ENPB</sub> | Flash Endurance (per block) <sup>[10]</sup>                                                 | 100    | _   | -       | _     | Erase/write cycles per block.        |