Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                |

| Core Processor             | AVR                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 4MHz                                                                    |

| Connectivity               | SPI, UART/USART                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 32                                                                      |

| Program Memory Size        | 8KB (4K x 16)                                                           |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 512 x 8                                                                 |

| RAM Size                   | 512 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 6V                                                               |

| Data Converters            | -                                                                       |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | 0°C ~ 70°C                                                              |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 44-LCC (J-Lead)                                                         |

| Supplier Device Package    | 44-PLCC (16.6x16.6)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at90s8515-4jc |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|       | current if the pull-up resistors are activated. The Port D pins are tri-stated when a reset condition becomes active, even if the clock is not active.                                                                                                               |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | Port D also serves the functions of various special features of the AT90S8515 as listed on page 73.                                                                                                                                                                  |

| RESET | Reset input. A low level on this pin for more than 50 ns will generate a reset, even if the clock is not running. Shorter pulses are not guaranteed to generate a reset.                                                                                             |

| XTAL1 | Input to the inverting oscillator amplifier and input to the internal clock operating circuit.                                                                                                                                                                       |

| XTAL2 | Output from the inverting oscillator amplifier.                                                                                                                                                                                                                      |

| ICP   | ICP is the input pin for the Timer/Counter1 Input Capture function.                                                                                                                                                                                                  |

| OC1B  | OC1B is the output pin for the Timer/Counter1 Output CompareB function.                                                                                                                                                                                              |

| ALE   | ALE is the Address Latch Enable used when the External Memory is enabled. The ALE strobe is used to latch the low-order address (8 bits) into an address latch during the first access cycle, and the AD0 - 7 pins are used for data during the second access cycle. |

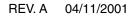

### **Crystal Oscillator**

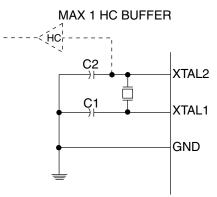

XTAL1 and XTAL2 are input and output, respectively, of an inverting amplifier that can be configured for use as an on-chip oscillator, as shown in Figure 2. Either a quartz crystal or a ceramic resonator may be used. To drive the device from an external clock source, XTAL2 should be left unconnected while XTAL1 is driven as shown in Figure 3.

Figure 2. Oscillator Connections

- Note: When using the MCU oscillator as a clock for an external device, an HC buffer should be connected as indicated in the figure.

- Figure 3. External Clock Drive Configuration

AT90S8515

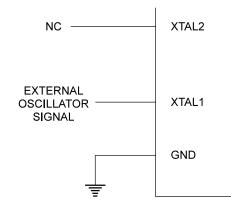

Figure 5. Memory Maps

## General-purpose Register File

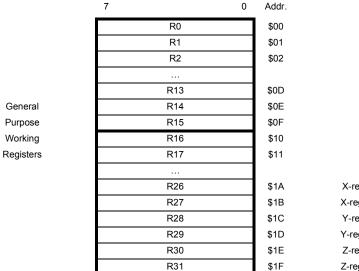

Figure 6 shows the structure of the 32 general-purpose working registers in the CPU.

#### Figure 6. AVR CPU General-purpose Working Registers

X-register low byte X-register high byte Y-register low byte Y-register high byte Z-register low byte Z-register high byte

All the register operating instructions in the instruction set have direct and single-cycle access to all registers. The only exception are the five constant arithmetic and logic instructions SBCI, SUBI, CPI, ANDI and ORI between a constant and a register and the LDI instruction for load immediate constant data. These instructions apply to the second half of the registers in the register file (R16..R31). The general SBC, SUB, CP, AND and OR and all other operations between two registers or on a single register apply to the entire register file.

As shown in Figure 6, each register is also assigned a data memory address, mapping them directly into the first 32 locations of the user Data Space. Although not being physically implemented as SRAM locations, this memory organization provides great flexibility in access of the registers, as the X-, Y- and Z-registers can be set to index any register in the file.

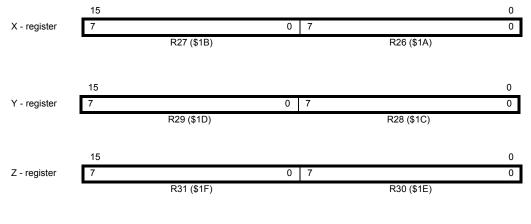

The registers R26..R31 have some added functions to their general-purpose usage. These registers are address pointers for indirect addressing of the Data Space. The three indirect address registers X, Y, and Z are defined as:

Figure 7. X-, Y-, and Z-registers

AT90S8515

X-register, Y-register and

**Z-register**

10

| Address Hex | Name | Function                                      |  |

|-------------|------|-----------------------------------------------|--|

| \$11 (\$31) | DDRD | Data Direction Register, Port D               |  |

| \$10 (\$30) | PIND | Input Pins, Port D                            |  |

| \$0F (\$2F) | SPDR | SPI I/O Data Register                         |  |

| \$0E (\$2E) | SPSR | SPI Status Register                           |  |

| \$0D (\$2D) | SPCR | SPI Control Register                          |  |

| \$0C (\$2C) | UDR  | UART I/O Data Register                        |  |

| \$0B (\$2B) | USR  | UART Status Register                          |  |

| \$0A (\$2A) | UCR  | UART Control Register                         |  |

| \$09 (\$29) | UBRR | UART Baud Rate Register                       |  |

| \$08 (\$28) | ACSR | Analog Comparator Control and Status Register |  |

| Table 1. AT90S8515 I/O Space (Continu |

|---------------------------------------|

|---------------------------------------|

Note: Reserved and unused locations are not shown in the table.

All AT90S8515 I/Os and peripherals are placed in the I/O space. The I/O locations are accessed by the IN and OUT instructions transferring data between the 32 general-purpose working registers and the I/O space. I/O registers within the address range \$00 - \$1F are directly bit-accessible using the SBI and CBI instructions. In these registers, the value of single bits can be checked by using the SBIS and SBIC instructions. Refer to the instruction set section for more details. When using the I/O-specific commands IN and OUT, the I/O addresses \$00 - \$3F must be used. When addressing I/O registers as SRAM, \$20 must be added to this address. All I/O register addresses throughout this document are shown with the SRAM address in parentheses.

For compatibility with future devices, reserved bits should be written to zero if accessed. Reserved I/O memory addresses should never be written.

Some of the status flags are cleared by writing a logical "1" to them. Note that the CBI and SBI instructions will operate on all bits in the I/O register, writing a "1" back into any flag read as set, thus clearing the flag. The CBI and SBI instructions work with registers \$00 to \$1F only.

The I/O and peripherals control registers are explained in the following sections.

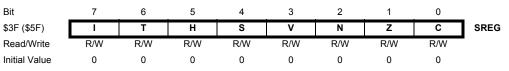

#### Status Register – SREG

The AVR status register (SREG) at I/O space location \$3F (\$5F) is defined as:

#### • Bit 7 – I: Global Interrupt Enable

The global interrupt enable bit must be set (one) for the interrupts to be enabled. The individual interrupt enable control is then performed in separate control registers. If the global interrupt enable bit is cleared (zero), none of the interrupts are enabled independent of the individual interrupt enable settings. The I-bit is cleared by hardware after an interrupt has occurred and is set by the RETI instruction to enable subsequent interrupts.

#### • Bit 6 – T: Bit Copy Storage

The bit copy instructions BLD (Bit LoaD) and BST (Bit STore) use the T-bit as source and destination for the operated bit. A bit from a register in the register file can be copied

# AIMEL

# Reset and Interrupt Handling

The AT90S8515 provides 12 different interrupt sources. These interrupts and the separate reset vector each have a separate program vector in the program memory space. All interrupts are assigned individual enable bits that must be set (one) together with the I-bit in the Status Register in order to enable the interrupt.

The lowest addresses in the program memory space are automatically defined as the Reset and Interrupt vectors. The complete list of vectors is shown in Table 2. The list also determines the priority levels of the different interrupts. The lower the address, the higher the priority level. RESET has the highest priority, and next is INTO (the External Interrupt Request 0), etc.

| Vector No. | Program<br>Address | Source       | Interrupt Definition                                 |

|------------|--------------------|--------------|------------------------------------------------------|

| 1          | \$000              | RESET        | External Reset, Power-on Reset and<br>Watchdog Reset |

| 2          | \$001              | INT0         | External Interrupt Request 0                         |

| 3          | \$002              | INT1         | External Interrupt Request 1                         |

| 4          | \$003              | TIMER1 CAPT  | Timer/Counter1 Capture Event                         |

| 5          | \$004              | TIMER1 COMPA | Timer/Counter1 Compare Match A                       |

| 6          | \$005              | TIMER1 COMPB | Timer/Counter1 Compare Match B                       |

| 7          | \$006              | TIMER1 OVF   | Timer/Counter1 Overflow                              |

| 8          | \$007              | TIMER0, OVF  | Timer/Counter0 Overflow                              |

| 9          | \$008              | SPI, STC     | Serial Transfer Complete                             |

| 10         | \$009              | UART, RX     | UART, Rx Complete                                    |

| 11         | \$00A              | UART, UDRE   | UART Data Register Empty                             |

| 12         | \$00B              | UART, TX     | UART, Tx Complete                                    |

| 13         | \$00C              | ANA_COMP     | Analog Comparator                                    |

The most typical and general program setup for the Reset and Interrupt vector addresses are:

| an 00000 ai | 0.     |         |                  |     |                               |

|-------------|--------|---------|------------------|-----|-------------------------------|

| Address     | Labels | Code    | C                | Com | ments                         |

| \$000       |        | rjmp    | RESET            | ;   | Reset Handler                 |

| \$001       |        | rjmp    | EXT_INT0         | ;   | IRQ0 Handler                  |

| \$002       |        | rjmp    | EXT_INT1         | ;   | IRQ1 Handler                  |

| \$003       |        | rjmp    | TIM1_CAPT        | ;   | Timer1 Capture Handler        |

| \$004       |        | rjmp    | TIM1_COMPA       | ;   | Timer1 CompareA Handler       |

| \$005       |        | rjmp    | TIM1_COMPB       | ;   | Timer1 CompareB Handler       |

| \$006       |        | rjmp    | TIM1_OVF         |     | ; Timer1 Overflow Handler     |

| \$007       |        | rjmp    | TIM0_OVF         | ;   | Timer0 Overflow Handler       |

| \$008       |        | rjmp    | SPI_STC          | ;   | SPI Transfer Complete Handler |

| \$009       |        | rjmp    | UART_RXC         | ;   | UART RX Complete Handler      |

| \$00a       |        | rjmp    | UART_DRE         | ;   | UDR Empty Handler             |

| \$00b       |        | rjmp    | UART_TXC         | ;   | UART TX Complete Handler      |

| \$00c       |        | rjmp    | ANA_COMP         | ;   | Analog Comparator Handler     |

| ;           |        |         |                  |     |                               |

| \$00d       | MAIN:  | ldi r10 | 5, high (RAMEND) | );  | Main program start            |

| \$00e       |        | out SPH | H,r16            |     |                               |

|             |        |         |                  |     |                               |

The user can select the start-up time according to typical oscillator start-up. The number of WDT oscillator cycles used for each time-out is shown in Table 4. The frequency of the Watchdog Oscillator is voltage-dependent as shown in "Typical Characteristics" on page 95.

| Table 4. | Number of Watchdog Oscillator Cycles |  |

|----------|--------------------------------------|--|

|----------|--------------------------------------|--|

| FSTRT        | Time-out at V <sub>CC</sub> = 5V | Number of WDT Cycles |

|--------------|----------------------------------|----------------------|

| Programmed   | 0.28 ms                          | 256                  |

| Unprogrammed | 16.0 ms                          | 16K                  |

#### **Power-on Reset**

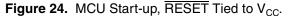

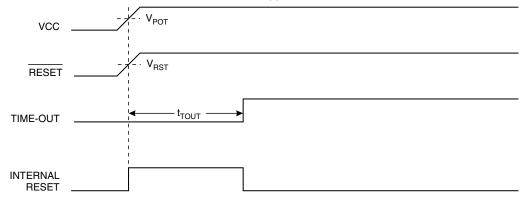

A Power-on Reset (POR) circuit ensures that the device is reset from power-on. As shown in Figure 23, an internal timer clocked from the Watchdog Timer oscillator prevents the MCU from starting until after a certain period after  $V_{CC}$  has reached the Power-on Threshold Voltage ( $V_{POT}$ ), regardless of the  $V_{CC}$  rise time (see Figure 24). The FSTRT Fuse bit in the Flash can be programmed to give a shorter start-up time if a certamic resonator or any other fast-start oscillator is used to clock the MCU.

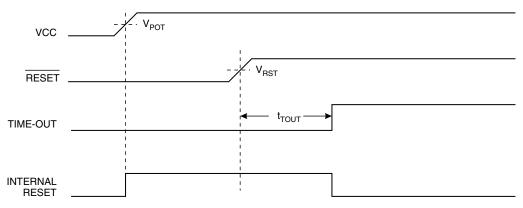

If the built-in start-up delay is sufficient,  $\overline{\text{RESET}}$  can be connected to V<sub>CC</sub> directly or via an external pull-up resistor. By holding the pin low for a period after V<sub>CC</sub> has been applied, the Power-on Reset period can be extended. Refer to Figure 25 for a timing example of this.

#### Figure 25. MCU Start-up, RESET Controlled Externally

#### • Bit 6 – INTF0: External Interrupt Flag0

When an edge on the INT0 pin triggers an interrupt request, the corresponding interrupt flag, INTF0, becomes set (one). If the I-bit in SREG and the corresponding interrupt enable bit, INT0 in GIMSK are set (one), the MCU will jump to the interrupt vector. The flag is cleared when the interrupt routine is executed. Alternatively, the flag is cleared by writing a logical "1" to it. This flag is always cleared when INT0 is configured as level interrupt.

#### Bits 5..0 – Res: Reserved Bits

These bits are reserved bits in the AT90S8515 and always read as zero.

#### Timer/Counter Interrupt Mask Register – TIMSK

| Bit           | 7     | 6      | 5      | 4 | 3      | 2 | 1     | 0 |       |

|---------------|-------|--------|--------|---|--------|---|-------|---|-------|

| \$39 (\$59)   | TOIE1 | OCIE1A | OCIE1B | - | TICIE1 | - | TOIE0 | - | TIMSK |

| Read/Write    | R/W   | R/W    | R/W    | R | R/W    | R | R/W   | R | -     |

| Initial Value | 0     | 0      | 0      | 0 | 0      | 0 | 0     | 0 |       |

#### Bit 7 – TOIE1: Timer/Counter1 Overflow Interrupt Enable

When the TOIE1 bit is set (one) and the I-bit in the Status Register is set (one), the Timer/Counter1 Overflow interrupt is enabled. The corresponding interrupt (at vector \$006) is executed if an overflow in Timer/Counter1 occurs, i.e., when the TOV1 bit is set in the Timer/Counter Interrupt Flag Register (TIFR).

#### • Bit 6 – OCE1A: Timer/Counter1 Output CompareA Match Interrupt Enable

When the OCIE1A bit is set (one) and the I-bit in the Status Register is set (one), the Timer/Counter1 CompareA Match interrupt is enabled. The corresponding interrupt (at vector \$004) is executed if a CompareA match in Timer/Counter1 occurs, i.e., when the OCF1A bit is set in the Timer/Counter Interrupt Flag Register (TIFR).

#### • Bit 5 – OCIE1B: Timer/Counter1 Output CompareB Match Interrupt Enable

When the OCIE1B bit is set (one) and the I-bit in the Status Register is set (one), the Timer/Counter1 CompareB Match interrupt is enabled. The corresponding interrupt (at vector \$005) is executed if a CompareB match in Timer/Counter1 occurs, i.e., when the OCF1B bit is set in the Timer/Counter Interrupt Flag Register (TIFR).

#### • Bit 4 – Res: Reserved Bit

This bit is a reserved bit in the AT90S8515 and always reads zero.

#### • Bit 3 – TICIE1: Timer/Counter1 Input Capture Interrupt Enable

When the TICIE1 bit is set (one) and the I-bit in the Status Register is set (one), the Timer/Counter1 Input Capture Event interrupt is enabled. The corresponding interrupt (at vector \$003) is executed if a capture-triggering event occurs on pin 31, ICP, i.e., when the ICF1 bit is set in the Timer/Counter Interrupt Flag Register (TIFR).

#### • Bit 2 - Res: Reserved Bit

This bit is a reserved bit in the AT90S8515 and always reads zero.

#### • Bit 1 – TOIE0: Timer/Counter0 Overflow Interrupt Enable

When the TOIE0 bit is set (one) and the I-bit in the Status Register is set (one), the Timer/Counter0 Overflow interrupt is enabled. The corresponding interrupt (at vector \$007) is executed if an overflow in Timer/Counter0 occurs, i.e., when the TOV0 bit is set in the Timer/Counter Interrupt Flag Register (TIFR).

#### • Bit 0 – Res: Reserved Bit

This bit is a reserved bit in the AT90S8515 and always reads zero.

#### • Bit 2 – EEMWE: EEPROM Master Write Enable

The EEMWE bit determines whether setting EEWE to one causes the EEPROM to be written. When EEMWE is set (one), setting EEWE will write data to the EEPROM at the selected address. If EEMWE is zero, setting EEWE will have no effect. When EEMWE has been set (one) by software, hardware clears the bit to zero after four clock cycles. See the description of the EEWE bit for a EEPROM write procedure.

#### • Bit 1 – EEWE: EEPROM Write Enable

The EEPROM Write Enable signal (EEWE) is the write strobe to the EEPROM. When address and data are correctly set up, the EEWE bit must be set to write the value into the EEPROM. The EEMWE bit must be set when the logical "1" is written to EEWE, otherwise no EEPROM write takes place. The following procedure should be followed when writing the EEPROM (the order of steps 2 and 3 is unessential):

- 1. Wait until EEWE becomes zero.

- 2. Write new EEPROM address to EEARL and EEARH (optional).

- 3. Write new EEPROM data to EEDR (optional).

- 4. Write a logical "1" to the EEMWE bit in EECR (to be able to write a logical "1" to the EEMWE bit, the EEWE bit must be written to zero in the same cycle).

- 5. Within four clock cycles after setting EEMWE, write a logical "1" to EEWE.

When the write access time (typically 2.5 ms at  $V_{CC} = 5V$  or 4 ms at  $V_{CC} = 2.7V$ ) has elapsed, the EEWE bit is cleared (zero) by hardware. The user software can poll this bit and wait for a zero before writing the next byte. When EEWE has been set, the CPU is halted for two cycles before the next instruction is executed.

**Caution**: An interrupt between step 4 and step 5 will make the write cycle fail, since the EEPROM Master Write Enable will time-out. If an interrupt routine accessing the EEPROM is interrupting another EEPROM access, the EEAR or EEDR registers will be modified, causing the interrupted EEPROM access to fail. It is recommended to have the global interrupt flag cleared during the four last steps to avoid these problems.

#### • Bit 0 – EERE: EEPROM Read Enable

The EEPROM Read Enable signal EERE is the read strobe to the EEPROM. When the correct address is set up in the EEAR register, the EERE bit must be set. When the EERE bit is cleared (zero) by hardware, requested data is found in the EEDR register. The EEPROM read access takes one instruction and there is no need to poll the EERE bit. When EERE has been set, the CPU is halted for four cycles before the next instruction is executed.

The user should poll the EEWE bit before starting the read operation. If a write operation is in progress when new data or address is written to the EEPROM I/O registers, the write operation will be interrupted and the result is undefined.

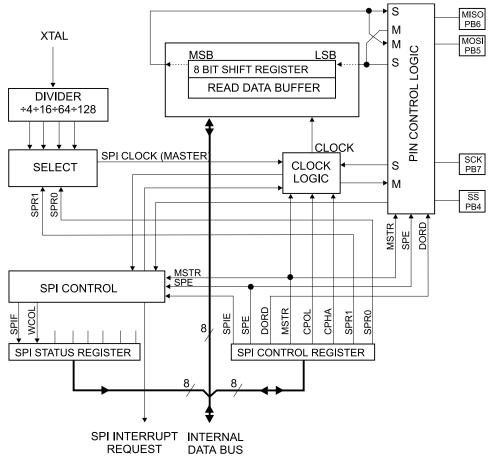

# Serial Peripheral Interface – SPI

The Serial Peripheral Interface (SPI) allows high-speed synchronous data transfer between the AT90S8515 and peripheral devices or between several AVR devices. The AT90S8515 SPI features include the following:

- Full-duplex, 3-wire Synchronous Data Transfer

- Master or Slave Operation

- LSB First or MSB First Data Transfer

- Four Programmable Bit Rates

- End-of-Transmission Interrupt Flag

- Write Collision Flag Protection

- Wake-up from Idle Mode (Slave Mode Only)

Figure 34. SPI Block Diagram

The interconnection between master and slave CPUs with SPI is shown in Figure 35. The PB7(SCK) pin is the clock output in the Master Mode and is the clock input in the Slave Mode. Writing to the SPI Data Register of the master CPU starts the SPI clock generator and the data written shifts out of the PB5(MOSI) pin and into the PB5(MOSI) pin of the slave CPU. After shifting one byte, the SPI clock generator stops, setting the end-of-transmission flag (SPIF). If the SPI interrupt enable bit (SPIE) in the SPCR register is set, an interrupt is requested. The Slave Select input, PB4(SS), is set low to select an individual slave SPI device. The two shift registers in the master and the slave can be considered as one distributed 16-bit circular shift register. This is shown in Figure 35. When data is shifted from the master to the slave, data is also shifted in the opposite direction, simultaneously. This means that during one shift cycle, data in the master and the slave are interchanged.

#### • Bit 5 – DORD: Data Order

When the DORD bit is set (one), the LSB of the data word is transmitted first.

When the DORD bit is cleared (zero), the MSB of the data word is transmitted first.

#### • Bit 4 – MSTR: Master/Slave Select

This bit selects Master SPI Mode when set (one), and Slave SPI Mode when cleared (zero). If  $\overline{SS}$  is configured as an input and is driven low while MSTR is set, MSTR will be cleared and SPIF in SPSR will become set. The user will then have to set MSTR to reenable SPI Master Mode.

#### Bit 3 – CPOL: Clock Polarity

When this bit is set (one), SCK is high when idle. When CPOL is cleared (zero), SCK is low when idle. Refer to Figure 36 and Figure 37 for additional information.

• Bit 2 – CPHA: Clock Phase

Refer to Figure 36 or Figure 37 for the functionality of this bit.

#### • Bits 1, 0 – SPR1, SPR0: SPI Clock Rate Select 1 and 0

These two bits control the SCK rate of the device configured as a master. SPR1 and SPR0 have no effect on the slave. The relationship between SCK and the oscillator clock frequency  $f_{cl}$  is shown in Table 16.

| Table 16. Relationship between SCK and the Oscillator Freque | ency |

|--------------------------------------------------------------|------|

|--------------------------------------------------------------|------|

| SPR1 | SPR0 | SCK Frequency       |

|------|------|---------------------|

| 0    | 0    | f <sub>cl</sub> /4  |

| 0    | 1    | f <sub>cl</sub> /16 |

| 1    | 0    | f <sub>cl</sub> /64 |

| 1    | 1    | f <sub>c</sub> /128 |

#### SPI Status Register – SPSR

| Bit           | 7    | 6    | 5 | 4 | 3 | 2 | 1 | 0 |      |

|---------------|------|------|---|---|---|---|---|---|------|

| \$0E (\$2E)   | SPIF | WCOL | - | - | - | - | - | - | SPSR |

| Read/Write    | R    | R    | R | R | R | R | R | R |      |

| Initial Value | 0    | 0    | 0 | 0 | 0 | 0 | 0 | 0 |      |

#### Bit 7 – SPIF: SPI Interrupt Flag

When a serial transfer is complete, the SPIF bit is set (one) and an interrupt is generated if SPIE in SPCR is set (one) and global interrupts are enabled. If SS is an input and is driven low when the SPI is in Master Mode, this will also set the SPIF flag. SPIF is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, the SPIF bit is cleared by first reading the SPI Status Register when SPIF is set (one), then by accessing the SPI Data Register (SPDR).

#### Bit 6 – WCOL: Write Collision Flag

The WCOL bit is set if the SPI Data Register (SPDR) is written during a data transfer. The WCOL bit (and the SPIF bit) are cleared (zero) by first reading the SPI Status Register when WCOL is set (one), and then by accessing the SPI Data Register.

#### Bits 5..0 – Res: Reserved Bits

These bits are reserved bits in the AT90S8515 and will always read as zero.

The SPI interface on the AT90S8515 is also used for program memory and EEPROM downloading or uploading. See page 86 for serial programming and verification.

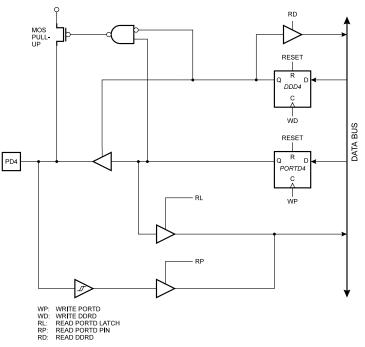

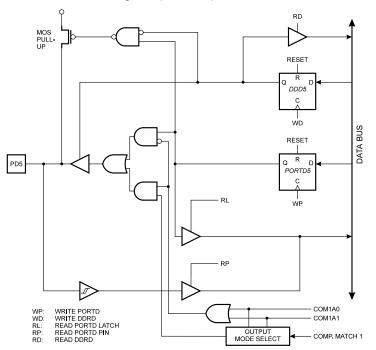

Figure 57. Port D Schematic Diagram (Pin PD5)

the self-timed write operation in the serial programming mode. During programming, the supply voltage must be in accordance with Table 26.

**Table 26.** Supply Voltage during Programming

| Part      | Serial Programming | Parallel Programming |  |  |

|-----------|--------------------|----------------------|--|--|

| AT90S8515 | 2.7 - 6.0V         | 4.5 - 5.5V           |  |  |

**Parallel Programming** This section describes how to parallel program and verify Flash program memory, EEPROM data memory, Lock bits and Fuse bits in the AT90S8515.

Signal Names In this section, some pins of the AT908515 are referenced by signal names describing their function during parallel programming. See Figure 60 and Table 27. Pins not described in Table 27 are referenced by pin names.

The XA1/XA0 pins determine the action executed when the XTAL1 pin is given a positive pulse. The bit coding are shown in Table 28.

When pulsing  $\overline{WR}$  or  $\overline{OE}$ , the command loaded determines the action executed. The command is a byte where the different bits are assigned functions as shown in Table 29.

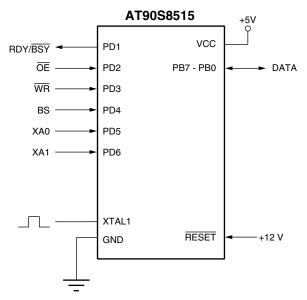

Figure 60. Parallel Programming

### Serial Downloading

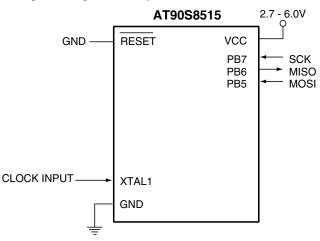

Both the program and data memory arrays can be programmed using the SPI bus while RESET is pulled to GND. The serial interface consists of pins SCK, MOSI (input) and MISO (output). See Figure 64. After RESET is set low, the Programming Enable instruction needs to be executed first before program/erase instructions can be executed.

Figure 64. Serial Programming and Verify

For the EEPROM, an auto-erase cycle is provided within the self-timed Write instruction and there is no need to first execute the Chip Erase instruction. The Chip Erase instruction turns the content of every memory location in both the program and EEPROM arrays into \$FF.

The program and EEPROM memory arrays have separate address spaces: \$0000 to \$0FFF (AT90S8515) for program memory and \$0000 to \$01FF (AT90S8515) for EEPROM memory.

Either an external clock is supplied at pin XTAL1 or a crystal needs to be connected across pins XTAL1 and XTAL2. The minimum low and high periods for the serial clock (SCK) input are defined as follows:

Low: > 2 XTAL1 clock cycles

High: > 2 XTAL1 clock cycles

When writing serial data to the AT90S8515, data is clocked on the rising edge of SCK.

When reading data from the AT90S8515, data is clocked on the falling edge of SCK. See Figure 65, Figure 66 and Table 33 on page 89 for timing details.

To program and verify the AT90S8515 in the Serial Programming Mode, the following sequence is recommended (see 4-byte instruction formats in Table 32):

1. Power-up sequence:

Apply power between V<sub>CC</sub> and GND while  $\overrightarrow{\text{RESET}}$  and SCK are set to "0". If a crystal is not connected across pins XTAL1 and XTAL2, apply a clock signal to the XTAL1 pin. In some systems, the programmer cannot guarantee that SCK is held low during power-up. In this case,  $\overrightarrow{\text{RESET}}$  must be given a positive pulse of at least two XTAL1 cycles duration after SCK has been set to "0".

- 2. Wait for at least 20 ms and enable serial programming by sending the Programming Enable serial instruction to the MOSI (PB5) pin.

- 3. The serial programming instructions will not work if the communication is out of synchronization. When in sync, the second byte (\$53) will echo back when issu-

Serial Programming Algorithm

# AT90S8515

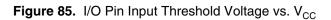

- Notes: 1. "Max" means the highest value where the pin is guaranteed to be read as low.

- 2. "Min" means the lowest value where the pin is guaranteed to be read as high.

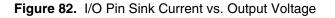

- Although each I/O port can sink more than the test conditions (20 mA at V<sub>CC</sub> = 5V, 10 mA at V<sub>CC</sub> = 3V) under steady state conditions (non-transient), the following must be observed:

- 1] The sum of all  $\mathrm{I}_{\mathrm{OL}},$  for all ports, should not exceed 200 mA.

- 2] The sum of all  $\rm I_{OL},$  for ports B0 B7, D0 D7 and XTAL2, should not exceed 100 mA.

- 3] The sum of all I<sub>OL</sub>, for ports A0 A7, ALE, OC1B and C0 C7 should not exceed 100 mA.

If  $I_{OL}$  exceeds the test condition,  $V_{OL}$  may exceed the related specification. Pins are not guaranteed to sink current greater than the listed test condition.

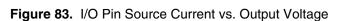

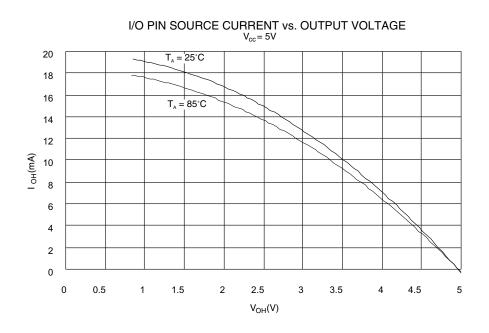

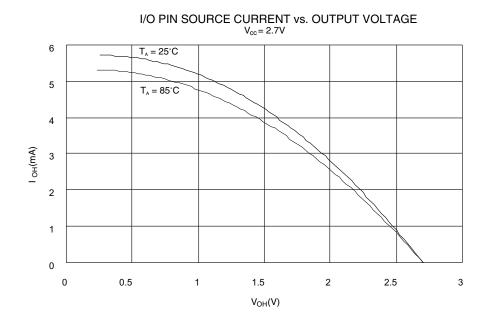

- Although each I/O port can source more than the test conditions (3 mA at V<sub>CC</sub> = 5V, 1.5 mA at V<sub>CC</sub> = 3V) under steady state conditions (non-transient), the following must be observed:

- 1] The sum of all  $I_{OH}$ , for all ports, should not exceed 200 mA.

- 2] The sum of all  $\rm I_{OH},$  for ports B0 B7, D0 D7 and XTAL2, should not exceed 100 mA.

3] The sum of all  $I_{OH}$ , for ports A0 - A7, ALE, OC1B and C0 - C7 should not exceed 100 mA.

If  $I_{OH}$  exceeds the test condition,  $V_{OH}$  may exceed the related specification. Pins are not guaranteed to source current greater than the listed test condition.

5. Minimum  $V_{CC}$  for power-down is 2V.

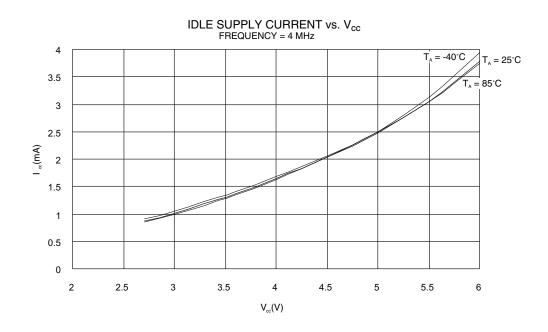

Figure 72. Idle Supply Current vs. V<sub>CC</sub>

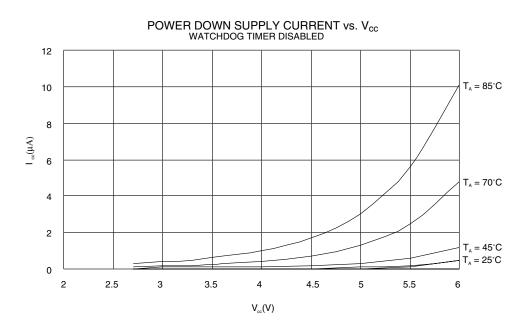

Figure 73. Power-down Supply Current vs. V<sub>CC</sub>

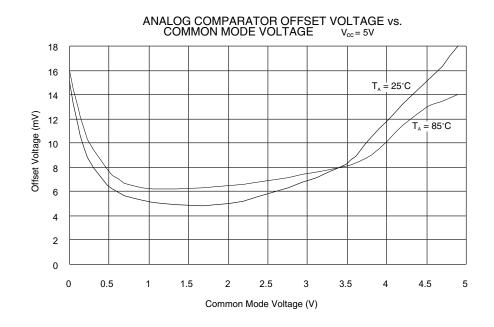

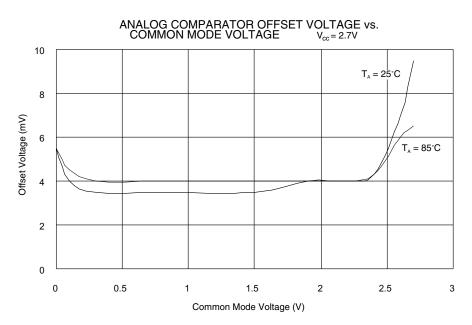

Analog Comparator offset voltage is measured as absolute offset.

Figure 76. Analog Comparator Offset Voltage vs. Common Mode Voltage

Figure 84. I/O Pin Source Current vs. Output Voltage

44J

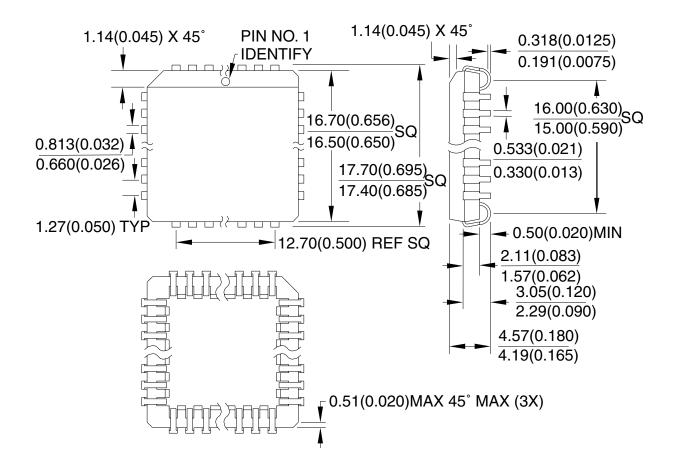

44J, 44-lead, Plastic J-leaded Chip Carrier (PLCC) Dimensions in Milimeters and (Inches)\* JEDEC STANDARD MS-018 AC

\*Controlling dimensions: Inches