Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

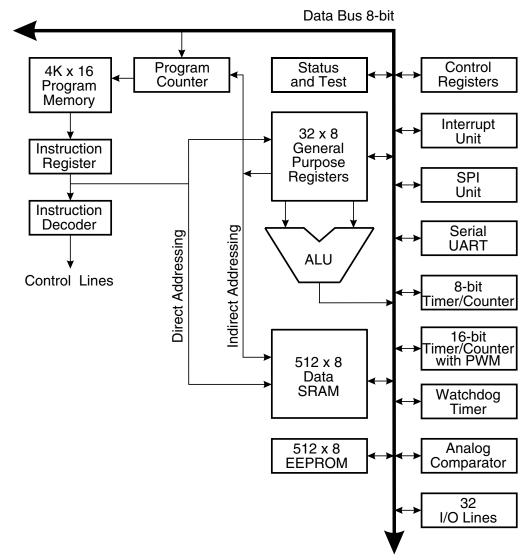

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                 |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | AVR                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 4MHz                                                                     |

| Connectivity               | SPI, UART/USART                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 32                                                                       |

| Program Memory Size        | 8KB (4K x 16)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 512 x 8                                                                  |

| RAM Size                   | 512 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 6V                                                                |

| Data Converters            | -                                                                        |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C                                                             |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 44-TQFP                                                                  |

| Supplier Device Package    | 44-TQFP (10x10)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at90s8515a-4ai |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

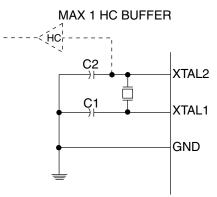

# **Crystal Oscillator**

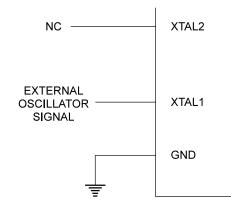

XTAL1 and XTAL2 are input and output, respectively, of an inverting amplifier that can be configured for use as an on-chip oscillator, as shown in Figure 2. Either a quartz crystal or a ceramic resonator may be used. To drive the device from an external clock source, XTAL2 should be left unconnected while XTAL1 is driven as shown in Figure 3.

Figure 2. Oscillator Connections

- Note: When using the MCU oscillator as a clock for an external device, an HC buffer should be connected as indicated in the figure.

- Figure 3. External Clock Drive Configuration

A flexible interrupt module has its control registers in the I/O space with an additional global interrupt enable bit in the status register. All the different interrupts have a separate interrupt vector in the interrupt vector table at the beginning of the program memory. The different interrupts have priority in accordance with their interrupt vector position. The lower the interrupt vector address, the higher the priority.

8

# AT90S8515

d

31

|                                        | two additional clock cycles is used per byte. This has the following effect: Data transfer instructions take two extra clock cycles, whereas interrupt, subroutine calls and returns will need four clock cycles more than specified in the instruction set manual.                                                                                                                                                                    |

|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                        | The five different addressing modes for the data memory cover: Direct, Indirect with Displacement, Indirect, Indirect with Pre-decrement and Indirect with Post-increment. In the register file, registers R26 to R31 feature the indirect addressing pointer registers.                                                                                                                                                               |

|                                        | The direct addressing reaches the entire data space.                                                                                                                                                                                                                                                                                                                                                                                   |

|                                        | The Indirect with Displacement mode features 63 address locations reached from the base address given by the Y- or Z-register.                                                                                                                                                                                                                                                                                                         |

|                                        | When using register indirect addressing modes with automatic pre-decrement and post-<br>increment, the address registers X, Y and Z are decremented and incremented.                                                                                                                                                                                                                                                                   |

|                                        | The 32 general-purpose working registers, 64 I/O registers, the 512 bytes of internal data SRAM, and the 64K bytes of optional external data SRAM in the AT90S8515 are all accessible through all these addressing modes.                                                                                                                                                                                                              |

|                                        | See the next section for a detailed description of the different addressing modes.                                                                                                                                                                                                                                                                                                                                                     |

| Program and Data<br>Addressing Modes   | The AT90S8515 AVR RISC microcontroller supports powerful and efficient addressing modes for access to the program memory (Flash) and data memory (SRAM, Register file and I/O memory). This section describes the different addressing modes supported by the AVR architecture. In the figures, OP means the operation code part of the instruction word. To simplify, not all figures show the exact location of the addressing bits. |

| Register Direct, Single<br>Register RD | Figure 9. Direct Single Register Addressing                                                                                                                                                                                                                                                                                                                                                                                            |

|                                        | 15 4 0<br>OP d                                                                                                                                                                                                                                                                                                                                                                                                                         |

The operand is contained in register d (Rd).

The X-, Y-, or the Z-register is decremented before the operation. Operand address is the decremented contents of the X-, Y-, or the Z-register.

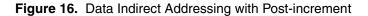

Data Indirect with Postincrement

The X-, Y-, or the Z-register is incremented after the operation. Operand address is the content of the X-, Y-, or the Z-register prior to incrementing.

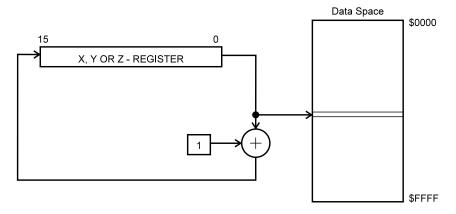

#### Constant Addressing Using F the LPM Instruction

Figure 17. Code Memory Constant Addressing

Constant byte address is specified by the Z-register contents. The 15 MSBs select word address (0 - 4K), the LSB selects low byte if cleared (LSB = 0) or high byte if set (LSB = 1).

# • Bit 6 – INTF0: External Interrupt Flag0

When an edge on the INT0 pin triggers an interrupt request, the corresponding interrupt flag, INTF0, becomes set (one). If the I-bit in SREG and the corresponding interrupt enable bit, INT0 in GIMSK are set (one), the MCU will jump to the interrupt vector. The flag is cleared when the interrupt routine is executed. Alternatively, the flag is cleared by writing a logical "1" to it. This flag is always cleared when INT0 is configured as level interrupt.

# Bits 5..0 – Res: Reserved Bits

These bits are reserved bits in the AT90S8515 and always read as zero.

#### Timer/Counter Interrupt Mask Register – TIMSK

| Bit           | 7     | 6      | 5      | 4 | 3      | 2 | 1     | 0 |       |

|---------------|-------|--------|--------|---|--------|---|-------|---|-------|

| \$39 (\$59)   | TOIE1 | OCIE1A | OCIE1B | - | TICIE1 | - | TOIE0 | - | TIMSK |

| Read/Write    | R/W   | R/W    | R/W    | R | R/W    | R | R/W   | R | -     |

| Initial Value | 0     | 0      | 0      | 0 | 0      | 0 | 0     | 0 |       |

# Bit 7 – TOIE1: Timer/Counter1 Overflow Interrupt Enable

When the TOIE1 bit is set (one) and the I-bit in the Status Register is set (one), the Timer/Counter1 Overflow interrupt is enabled. The corresponding interrupt (at vector \$006) is executed if an overflow in Timer/Counter1 occurs, i.e., when the TOV1 bit is set in the Timer/Counter Interrupt Flag Register (TIFR).

# • Bit 6 – OCE1A: Timer/Counter1 Output CompareA Match Interrupt Enable

When the OCIE1A bit is set (one) and the I-bit in the Status Register is set (one), the Timer/Counter1 CompareA Match interrupt is enabled. The corresponding interrupt (at vector \$004) is executed if a CompareA match in Timer/Counter1 occurs, i.e., when the OCF1A bit is set in the Timer/Counter Interrupt Flag Register (TIFR).

# • Bit 5 – OCIE1B: Timer/Counter1 Output CompareB Match Interrupt Enable

When the OCIE1B bit is set (one) and the I-bit in the Status Register is set (one), the Timer/Counter1 CompareB Match interrupt is enabled. The corresponding interrupt (at vector \$005) is executed if a CompareB match in Timer/Counter1 occurs, i.e., when the OCF1B bit is set in the Timer/Counter Interrupt Flag Register (TIFR).

# • Bit 4 – Res: Reserved Bit

This bit is a reserved bit in the AT90S8515 and always reads zero.

# • Bit 3 – TICIE1: Timer/Counter1 Input Capture Interrupt Enable

When the TICIE1 bit is set (one) and the I-bit in the Status Register is set (one), the Timer/Counter1 Input Capture Event interrupt is enabled. The corresponding interrupt (at vector \$003) is executed if a capture-triggering event occurs on pin 31, ICP, i.e., when the ICF1 bit is set in the Timer/Counter Interrupt Flag Register (TIFR).

# • Bit 2 - Res: Reserved Bit

This bit is a reserved bit in the AT90S8515 and always reads zero.

# • Bit 1 – TOIE0: Timer/Counter0 Overflow Interrupt Enable

When the TOIE0 bit is set (one) and the I-bit in the Status Register is set (one), the Timer/Counter0 Overflow interrupt is enabled. The corresponding interrupt (at vector \$007) is executed if an overflow in Timer/Counter0 occurs, i.e., when the TOV0 bit is set in the Timer/Counter Interrupt Flag Register (TIFR).

# • Bit 0 – Res: Reserved Bit

This bit is a reserved bit in the AT90S8515 and always reads zero.

# Timer/Counter Interrupt Flag Register – TIFR

| Bit           | 7    | 6     | 5     | 4 | 3    | 2 | 1    | 0 | _    |

|---------------|------|-------|-------|---|------|---|------|---|------|

| \$38 (\$58)   | TOV1 | OCF1A | OCIFB | - | ICF1 | - | TOV0 | - | TIFR |

| Read/Write    | R/W  | R/W   | R/W   | R | R/W  | R | R/W  | R | -    |

| Initial Value | 0    | 0     | 0     | 0 | 0    | 0 | 0    | 0 |      |

# • Bit 7 – TOV1: Timer/Counter1 Overflow Flag

The TOV1 is set (one) when an overflow occurs in Timer/Counter1. TOV1 is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, TOV1 is cleared by writing a logical "1" to the flag. When the I-bit in SREG, TOIE1 (Timer/Counter1 Overflow Interrupt Enable) and TOV1 are set (one), the Timer/Counter1 Overflow interrupt is executed. In PWM mode, this bit is set when Timer/Counter1 changes counting direction at \$0000.

# • Bit 6 – OCF1A: Output Compare Flag 1A

The OCF1A bit is set (one) when compare match occurs between the Timer/Counter1 and the data in OCR1A (Output Compare Register 1A). OCF1A is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, OCF1A is cleared by writing a logical "1" to the flag. When the I-bit in SREG, OCIE1A (Timer/Counter1 Compare Match InterruptA Enable) and the OCF1A are set (one), the Timer/Counter1 CompareA Match interrupt is executed.

# • Bit 5 – OCF1B: Output Compare Flag 1B

The OCF1B bit is set (one) when compare match occurs between the Timer/Counter1 and the data in OCR1B (Output Compare Register 1B). OCF1B is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, OCF1B is cleared by writing a logical "1" to the flag. When the I-bit in SREG, OCIE1B (Timer/Counter1 Compare Match InterruptB Enable) and the OCF1B are set (one), the Timer/Counter1 CompareB Match interrupt is executed.

# • Bit 4 - Res: Reserved Bit

This bit is a reserved bit in the AT90S8515 and always reads zero.

# • Bit 3 – ICF1: Input Capture Flag 1

The ICF1 bit is set (one) to flag an input capture event, indicating that the Timer/Counter1 value has been transferred to the input capture register (ICR1). ICF1 is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, ICF1 is cleared by writing a logical "1" to the flag. When the SREG I-bit, TICIE1 (Timer/Counter1 Input Capture Interrupt Enable) and ICF1 are set (one), the Timer/Counter1 Capture interrupt is executed.

# • Bit 2 - Res: Reserved Bit

This bit is a reserved bit in the AT90S8515 and always reads zero.

# • Bit 1 – TOV: Timer/Counter0 Overflow Flag

The bit TOV0 is set (one) when an overflow occurs in Timer/Counter0. TOV0 is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, TOV0 is cleared by writing a logical "1" to the flag. When the SREG I-bit, TOIE0 (Timer/Counter0 Overflow Interrupt Enable) and TOV0 are set (one), the Timer/Counter0 Overflow interrupt is executed.

# • Bit 0 – Res: Reserved Bit

This bit is a reserved bit in the AT90S8515 and always reads zero.

# <u>AÎMEL</u>

The Stop condition provides a Timer Enable/Disable function. The CK down divided modes are scaled directly from the CK oscillator clock. If the external pin modes are used for Timer/Counter0, transitions on PB0/(T0) will clock the counter even if the pin is configured as an output. This feature can give the user software control of the counting.

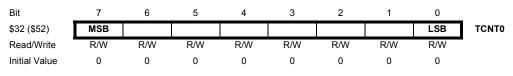

# Timer Counter0 – TCNT0

The Timer/Counter0 is realized as an up-counter with read and write access. If the Timer/Counter0 is written and a clock source is present, the Timer/Counter0 continues counting in the clock cycle following the write operation.

# 16-bit Timer/Counter1

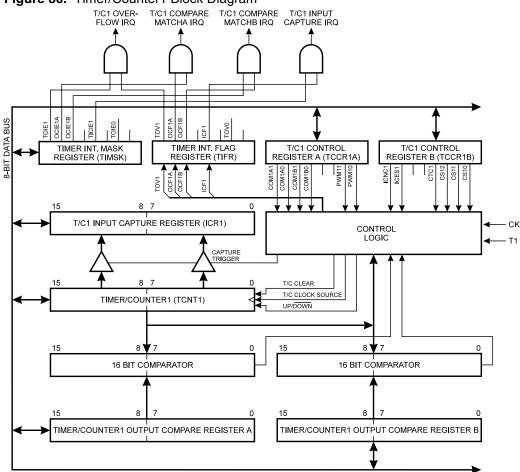

Figure 30 shows the block diagram for Timer/Counter1.

#### Figure 30. Timer/Counter1 Block Diagram

The 16-bit Timer/Counter1 can select clock source from CK, prescaled CK or an external pin. In addition, it can be stopped as described in the specification for the Timer/Counter1 Control Registers (TCCR1A and TCCR1B). The different status flags (overflow, compare match and capture event) are found in the Timer/Counter Interrupt Flag Register (TIFR). Control signals are found in the Timer/Counter1 Control Registers

# Timer/Counter1 Control Register A – TCCR1A

| Bit           | 7      | 6      | 5      | 4      | 3 | 2 | 1     | 0     |        |

|---------------|--------|--------|--------|--------|---|---|-------|-------|--------|

| \$2F (\$4F)   | COM1A1 | COM1A0 | COM1B1 | COM1B0 | - | - | PWM11 | PWM10 | TCCR1A |

| Read/Write    | R/W    | R/W    | R/W    | R/W    | R | R | R/W   | R/W   |        |

| Initial Value | 0      | 0      | 0      | 0      | 0 | 0 | 0     | 0     |        |

# • Bits 7, 6 - COM1A1, COM1A0: Compare Output Mode1A, Bits 1 and 0

The COM1A1 and COM1A0 control bits determine any output pin action following a compare match in Timer/Counter1. Any output pin actions affect pin OC1A (Output CompareA pin 1). This is an alternative function to an I/O port and the corresponding direction control bit must be set (one) to control the output pin. The control configuration is shown in Table 8.

# • Bits 5, 4 – COM1B1, COM1B0: Compare Output Mode1B, Bits 1 and 0

The COM1B1 and COM1B0 control bits determine any output pin action following a compare match in Timer/Counter1. Any output pin actions affect pin OC1B (Output CompareB). The control configuration is given in Table 8.

| Table 8. | Compare 1 | Mode Select |

|----------|-----------|-------------|

|----------|-----------|-------------|

| COM1X1 | COM1X0 | Description                                      |

|--------|--------|--------------------------------------------------|

| 0      | 0      | Timer/Counter1 disconnected from output pin OC1X |

| 0      | 1      | Toggle the OC1X output line.                     |

| 1      | 0      | Clear the OC1X output line (to zero).            |

| 1      | 1      | Set the OC1X output line (to one).               |

Note: X = A or B

In PWM mode, these bits have a different function. Refer to Table 12 on page 40 for a detailed description.

# • Bits 3..2 - Res: Reserved Bits

These bits are reserved bits in the AT90S8515 and always read zero.

# • Bits 1..0 – PWM11, PWM10: Pulse Width Modulator Select Bits 1 and 0

These bits select PWM operation of Timer/Counter1 as specified in Table 9. This mode is described on page 40.

Table 9.

PWM Mode Select

| PWM11 | PWM10 | Description                                 |

|-------|-------|---------------------------------------------|

| 0     | 0     | PWM operation of Timer/Counter1 is disabled |

| 0     | 1     | Timer/Counter1 is an 8-bit PWM              |

| 1     | 0     | Timer/Counter1 is a 9-bit PWM               |

| 1     | 1     | Timer/Counter1 is a 10-bit PWM              |

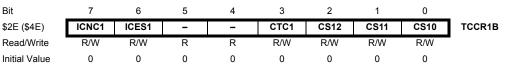

# Timer/Counter1 Control Register B – TCCR1B

# • Bit 7 – ICNC1: Input Capture1 Noise Canceler (4 CKs)

When the ICNC1 bit is cleared (zero), the input capture trigger noise canceler function is disabled. The input capture is triggered at the first rising/falling edge sampled on the ICP (input capture pin) as specified. When the ICNC1 bit is set (one), four successive samples are measured on the ICP, and all samples must be high/low according to the input capture trigger specification in the ICES1 bit. The actual sampling frequency is XTAL clock frequency.

# • Bit 6 – ICES1: Input Capture1 Edge Select

While the ICES1 bit is cleared (zero), the Timer/Counter1 contents are transferred to the Input Capture Register (ICR1) on the falling edge of the input capture pin (ICP). While the ICES1 bit is set (one), the Timer/Counter1 contents are transferred to the ICR1 on the rising edge of the ICP.

# • Bits 5, 4 - Res: Reserved Bits

These bits are reserved bits in the AT90S8515 and always read zero.

# • Bit 3 – CTC1: Clear Timer/Counter1 on Compare Match

When the CTC1 control bit is set (one), the Timer/Counter1 is reset to \$0000 in the clock cycle after a compareA match. If the CTC1 control bit is cleared, Timer/Counter1 continues counting and is unaffected by a compare match. Since the compare match is detected in the CPU clock cycle following the match, this function will behave differently when a prescaling higher than 1 is used for the timer. When a prescaling of 1 is used, and the compareA register is set to C, the timer will count as follows if CTC1 is set:

... | C-2 | C-1 | C | 0 | 1 | ...

When the prescaler is set to divide by 8, the timer will count like this:

In PWM mode, this bit has no effect.

# • Bits 2, 1, 0 - CS12, CS11, CS10: Clock Select1, Bits 2, 1 and 0

The Clock Select1 bits 2, 1 and 0 define the prescaling source of Timer/Counter1.

| CS12 | CS11 | CS10 | Description                          |

|------|------|------|--------------------------------------|

| 0    | 0    | 0    | Stop, the Timer/Counter1 is stopped. |

| 0    | 0    | 1    | СК                                   |

| 0    | 1    | 0    | CK/8                                 |

| 0    | 1    | 1    | CK/64                                |

| 1    | 0    | 0    | CK/256                               |

| 1    | 0    | 1    | CK/1024                              |

| 1    | 1    | 0    | External Pin T1, falling edge        |

| 1    | 1    | 1    | External Pin T1, rising edge         |

Table 10.

Clock 1 Prescale Select

- 1. In the same operation, write a logical "1" to WDTOE and WDE. A logical "1" must be written to WDE even though it is set to one before the disable operation starts.

- 2. Within the next four clock cycles, write a logical "0" to WDE. This disables the Watchdog.

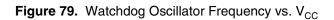

- Bits 2..0 WDP2, WDP1, WDP0: Watchdog Timer Prescaler 2, 1 and 0

The WDP2, WDP1 and WDP0 bits determine the Watchdog Timer prescaling when the Watchdog Timer is enabled. The different prescaling values and their corresponding Time-out periods are shown in Table 14.

| WDP2 | WDP1 | WDP0 | Number of WDT<br>Oscillator Cycles | Typical Time-out<br>at V <sub>CC</sub> = 3.0V | Typical Time-out<br>at V <sub>CC</sub> = 5.0V |

|------|------|------|------------------------------------|-----------------------------------------------|-----------------------------------------------|

| 0    | 0    | 0    | 16K cycles                         | 47.0 ms                                       | 15.0 ms                                       |

| 0    | 0    | 1    | 32K cycles                         | 94.0 ms                                       | 30.0 ms                                       |

| 0    | 1    | 0    | 64K cycles                         | 0.19 s                                        | 60.0 ms                                       |

| 0    | 1    | 1    | 128K cycles                        | 0.38 s                                        | 0.12 s                                        |

| 1    | 0    | 0    | 256K cycles                        | 0.75 s                                        | 0.24 s                                        |

| 1    | 0    | 1    | 512K cycles                        | 1.5 s                                         | 0.49 s                                        |

| 1    | 1    | 0    | 1,024K cycles                      | 3.0 s                                         | 0.97 s                                        |

| 1    | 1    | 1    | 2,048K cycles                      | 6.0 s                                         | 1.9 s                                         |

| Table 14. | Watchdog | Timer Pre | scale Select |

|-----------|----------|-----------|--------------|

|-----------|----------|-----------|--------------|

Note: The frequency of the Watchdog oscillator is voltage-dependent as shown in the Electrical Characteristics section.

The WDR (Watchdog Reset) instruction should always be executed before the Watchdog Timer is enabled. This ensures that the reset period will be in accordance with the Watchdog Timer prescale settings. If the Watchdog Timer is enabled without reset, the Watchdog Timer may not start to count from zero.

To avoid unintentional MCU reset, the Watchdog Timer should be disabled or reset before changing the Watchdog Timer Prescale Select.

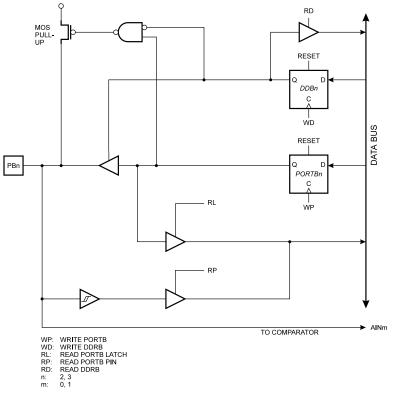

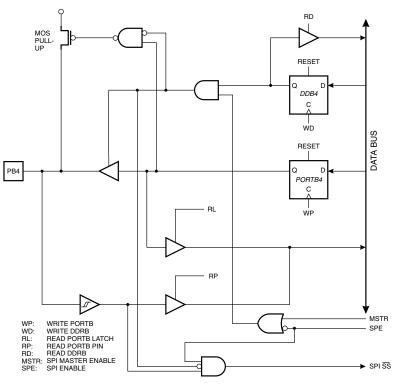

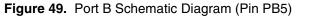

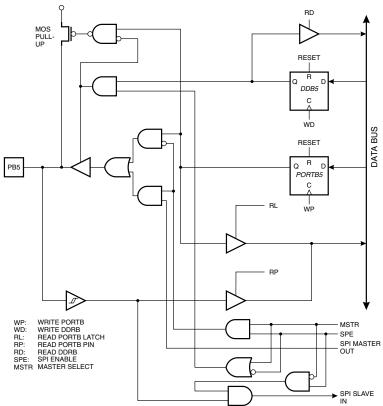

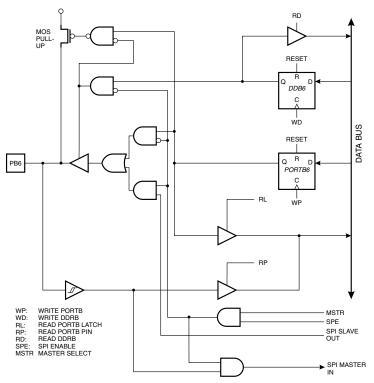

Port B is an 8-bit bi-directional I/O port.

Three I/O memory address locations are allocated for the Port B, one each for the Data Register – PORTB, \$18(\$38), Data Direction Register – DDRB, \$17(\$37) and the Port B Input Pins – PINB, \$16(\$36). The Port B Input Pins address is read-only, while the Data Register and the Data Direction Register are read/write.

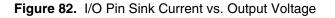

All port pins have individually selectable pull-up resistors. The Port B output buffers can sink 20 mA and thus drive LED displays directly. When pins PB0 to PB7 are used as inputs and are externally pulled low, they will source current if the internal pull-up resistors are activated.

The Port B pins with alternate functions are shown in Table 20.

| Port Pin | Alternate Functions                         |

|----------|---------------------------------------------|

| PB0      | T0 (Timer/Counter 0 External Counter Input) |

| PB1      | T1 (Timer/Counter 1 External Counter Input) |

| PB2      | AIN0 (Analog Comparator positive input)     |

| PB3      | AIN1 (Analog Comparator negative input)     |

| PB4      | SS (SPI Slave Select Input)                 |

| PB5      | MOSI (SPI Bus Master Output/Slave Input)    |

| PB6      | MISO (SPI Bus Master Input/Slave Output)    |

| PB7      | SCK (SPI Bus Serial Clock)                  |

Table 20.

Port B Pin Alternate Functions

When the pins are used for the alternate function, the DDRB and PORTB registers have to be set according to the alternate function description.

#### Port B Data Register – PORTB

|                                | Bit           | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |       |

|--------------------------------|---------------|--------|--------|--------|--------|--------|--------|--------|--------|-------|

|                                | \$18 (\$38)   | PORTB7 | PORTB6 | PORTB5 | PORTB4 | PORTB3 | PORTB2 | PORTB1 | PORTB0 | PORTB |

|                                | Read/Write    | R/W    |       |

|                                | Initial Value | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |       |

| Port B Data Direction Register |               |        |        |        |        |        |        |        |        |       |

| – DDRB                         | Bit           | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |       |

|                                | \$17 (\$37)   | DDB7   | DDB6   | DDB5   | DDB4   | DDB3   | DDB2   | DDB1   | DDB0   | DDRB  |

|                                | Read/Write    | R/W    |       |

|                                | Initial Value | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |       |

| Port B Input Pins Address –    |               |        |        |        |        |        |        |        |        |       |

| PINB                           | Bit           | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |       |

|                                | \$16 (\$36)   | PINB7  | PINB6  | PINB5  | PINB4  | PINB3  | PINB2  | PINB1  | PINB0  | PINB  |

|                                | Read/Write    | R      | R      | R      | R      | R      | R      | R      | R      |       |

|                                | Initial Value | N/A    |       |

The Port B Input Pins address (PINB) is not a register; this address enables access to the physical value on each Port B pin. When reading PORTB, the Port B Data Latch is read and when reading PINB, the logical values present on the pins are read.

Figure 47. Port B Schematic Diagram (Pins PB2 and PB3)

Figure 48. Port B Schematic Diagram (Pin PB4)

# AT90S8515

#### Port D Data Register – PORTD

|                                | Bit                    | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |       |

|--------------------------------|------------------------|--------|--------|--------|--------|--------|--------|--------|--------|-------|

|                                | \$12 (\$32)            | PORTD7 | PORTD6 | PORTD5 | PORTD4 | PORTD3 | PORTD2 | PORTD1 | PORTD0 | PORTD |

|                                | Read/Write             | R/W    |       |

|                                | Initial Value          | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |       |

| Port D Data Direction Register |                        |        |        |        |        |        |        |        |        |       |

| – DDRD                         | Bit                    | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |       |

|                                | \$11 (\$31)            | DDD7   | DDD6   | DDD5   | DDD4   | DDD3   | DDD2   | DDD1   | DDD0   | DDRD  |

|                                | Read/Write             | R/W    |       |

|                                | Initial Value          | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |       |

| Port D Input Pins Address –    |                        |        |        |        |        |        |        |        |        |       |

| PIND                           | Bit                    | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |       |

|                                | \$10 (\$30)            | PIND7  | PIND6  | PIND5  | PIND4  | PIND3  | PIND2  | PIND1  | PIND0  | PIND  |

|                                | Read/Write             | R      | R      | R      | R      | R      | R      | R      | R      |       |

|                                | Initial Value          | N/A    |       |

|                                | The Port D the physica | •      |        | •      | ,      | •      |        |        |        |       |

**Port D as General Digital I/O** If DDDn is set (one), PDn is configured as an output pin. If DDDn is cleared (zero), PDn is configured as an input pin. If PDn is set (one) when configured as an input pin, the MOS pull-up resistor is activated. To switch the pull-up resistor off the PDn has to be cleared (zero) or the pin has to be configured as an output pin. The Port D pins are tristated when a reset condition becomes active, even if the clock is not active.

#### Table 24. DDDn Bits on Port D Pins

| DDDn | PORTDn | I/O    | Pull-up | Comment                                     |  |  |  |  |  |

|------|--------|--------|---------|---------------------------------------------|--|--|--|--|--|

| 0    | 0      | Input  | No      | Tri-state (high-Z)                          |  |  |  |  |  |

| 0    | 1      | Input  | Yes     | PDn will source current if ext. pulled low. |  |  |  |  |  |

| 1    | 0      | Output | No      | Push-pull Zero Output                       |  |  |  |  |  |

| 1    | 1      | Output | No      | Push-pull One Output                        |  |  |  |  |  |

read and when reading PIND, the logical values present on the pins are read.

Note: n: 7,6...0, pin number.

# Alternate Functions of Port D • RD – Port D, Bit 7

RD is the external data memory read control strobe. See "Interface to External SRAM" on page 60 for detailed information.

# • WR – Port D, Bit 6

WR is the external data memory write control strobe. See "Interface to External SRAM" on page 60 for detailed information.

# • OC1A - Port D, Bit 5

OC1A: Output compare match output. The PD5 pin can serve as an external output when the Timer/Counter1 compare matches. The PD5 pin has to be configured as an output (DDD5 set [one]) to serve this function. See the Timer/Counter1 description for further details and how to enable the output. The OC1A pin is also the output pin for the PWM mode timer function.

# AT90S8515

# **External Data Memory Timing**

|    |                      |                                                        | 8 MHz O | scillator | Variable                                    |                              |      |

|----|----------------------|--------------------------------------------------------|---------|-----------|---------------------------------------------|------------------------------|------|

|    | Symbol               | Parameter                                              | Min     | Мах       | Min                                         | Max                          | Unit |

| 0  | 1/t <sub>CLCL</sub>  | Oscillator Frequency                                   |         |           | 0.0                                         | 8.0                          | MHz  |

| 1  | t <sub>LHLL</sub>    | ALE Pulse Width                                        | 32.5    |           | 0.5 t <sub>CLCL</sub> - 30.0 <sup>(1)</sup> |                              | ns   |

| 2  | t <sub>AVLL</sub>    | Address Valid A to ALE Low                             | 22.5    |           | 0.5 t <sub>CLCL</sub> - 40.0 <sup>(1)</sup> |                              | ns   |

| За | t <sub>LLAX_ST</sub> | Address Hold after ALE Low,<br>ST/STD/STS Instructions | 67.5    |           | 0.5 t <sub>CLCL</sub> + 5.0 <sup>(2)</sup>  |                              | ns   |

| 3b | t <sub>LLAX_LD</sub> | Address Hold after ALE Low,<br>LD/LDD/LDS Instructions | 15.0    |           | 15.0                                        |                              | ns   |

| 4  | t <sub>AVLLC</sub>   | Address Valid C to ALE Low                             | 22.5    |           | 0.5 t <sub>CLCL</sub> - 40.0 <sup>(1)</sup> |                              | ns   |

| 5  | t <sub>AVRL</sub>    | Address Valid to RD Low                                | 95.0    |           | 1.0 t <sub>CLCL</sub> - 30.0                |                              | ns   |

| 6  | t <sub>AVWL</sub>    | Address Valid to WR Low                                | 157.5   |           | 1.5 t <sub>CLCL</sub> - 30.0 <sup>(1)</sup> |                              | ns   |

| 7  | t <sub>LLWL</sub>    | ALE Low to WR Low                                      | 105.0   | 145.0     | 1.0 t <sub>CLCL</sub> - 20.0                | 1.0 t <sub>CLCL</sub> + 20.0 | ns   |

| 8  | t <sub>LLRL</sub>    | ALE Low to RD Low                                      | 42.5    | 82.5      | 0.5 t <sub>CLCL</sub> - 20.0 <sup>(2)</sup> | $0.5 t_{CLCL} + 20.0^{(2)}$  | ns   |

| 9  | t <sub>DVRH</sub>    | Data Setup to RD High                                  | 60.0    |           | 60.0                                        |                              | ns   |

| 10 | t <sub>RLDV</sub>    | Read Low to Data Valid                                 |         | 70.0      |                                             | 1.0 t <sub>CLCL</sub> - 55.0 | ns   |

| 11 | t <sub>RHDX</sub>    | Data Hold after RD High                                | 0.0     |           | 0.0                                         |                              | ns   |

| 12 | t <sub>RLRH</sub>    | RD Pulse Width                                         | 105.0   |           | 1.0 t <sub>CLCL</sub> - 20.0                |                              | ns   |

| 13 | t <sub>DVWL</sub>    | Data Setup to WR Low                                   | 27.5    |           | 0.5 t <sub>CLCL</sub> - 35.0 <sup>(2)</sup> |                              | ns   |

| 14 | t <sub>WHDX</sub>    | Data Hold after WR High                                | 0.0     |           | 0.0                                         |                              | ns   |

| 15 | t <sub>DVWH</sub>    | Data Valid to WR High                                  | 95.0    |           | 1.0 t <sub>CLCL</sub> - 30.0                |                              | ns   |

| 16 | t <sub>wLWH</sub>    | WR Pulse Width                                         | 42.5    |           | 0.5 t <sub>CLCL</sub> - 20.0 <sup>(1)</sup> |                              | ns   |

# Table 38. External Data Memory Characteristics, 4.0V - 6.0V, One Cycle Wait State

|    |                     |                        | 8 MHz Os | scillator | Variable                                    | Oscillator                   |      |

|----|---------------------|------------------------|----------|-----------|---------------------------------------------|------------------------------|------|

|    | Symbol              | Parameter              | Min      | Max       | Min                                         | Max                          | Unit |

| 0  | 1/t <sub>CLCL</sub> | Oscillator Frequency   |          |           | 0.0                                         | 8.0                          | MHz  |

| 10 | t <sub>RLDV</sub>   | Read Low to Data Valid |          | 195.0     |                                             | 2.0 t <sub>CLCL</sub> - 55.0 | ns   |

| 12 | t <sub>RLRH</sub>   | RD Pulse Width         | 230.0    |           | 2.0 t <sub>CLCL</sub> - 20.0                |                              | ns   |

| 15 | t <sub>DVWH</sub>   | Data Valid to WR High  | 220.0    |           | 2.0 t <sub>CLCL</sub> - 30.0                |                              | ns   |

| 16 | t <sub>wLWH</sub>   | WR Pulse Width         | 167.5    |           | 1.5 t <sub>CLCL</sub> - 20.0 <sup>(2)</sup> |                              | ns   |

Notes: 1. This assumes 50% clock duty cycle. The half-period is actually the high time of the external clock, XTAL1.

2. This assumes 50% clock duty cycle. The half-period is actually the low time of the external clock, XTAL1.

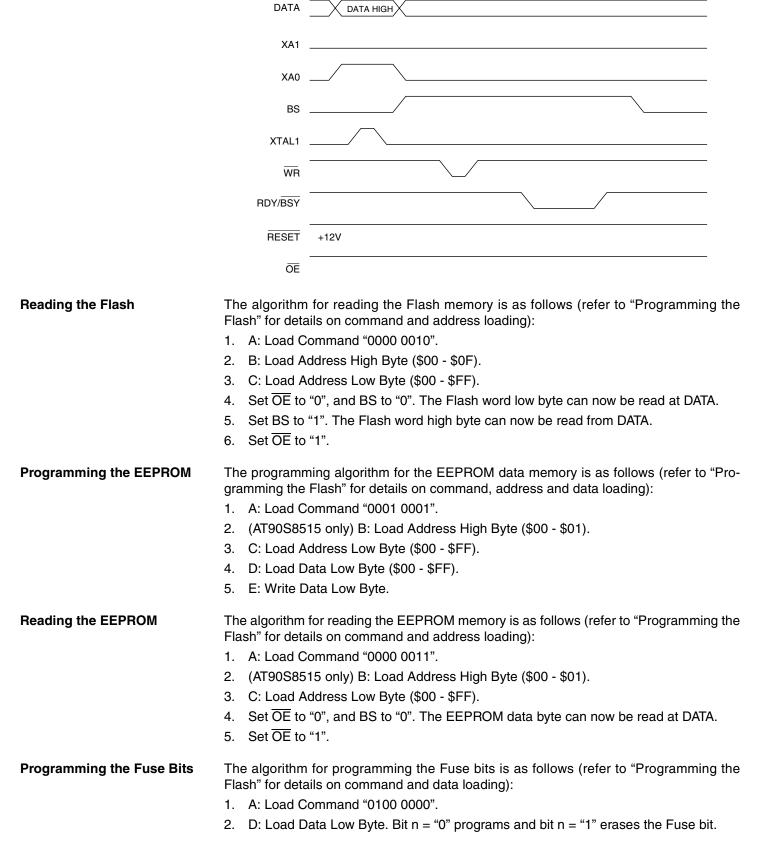

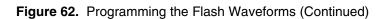

Figure 72. Idle Supply Current vs. V<sub>CC</sub>

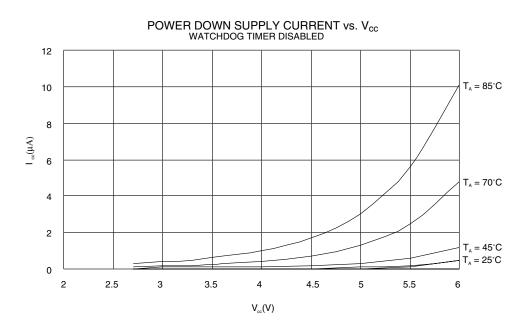

Figure 73. Power-down Supply Current vs. V<sub>CC</sub>

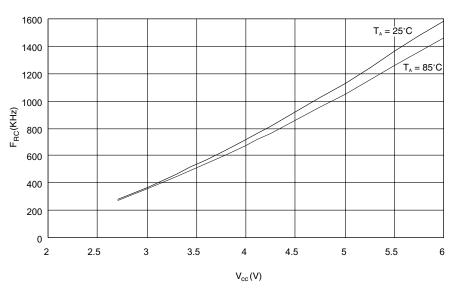

WATCHDOG OSCILLATOR FREQUENCY vs. V<sub>cc</sub>

# **Register Summary**

| Address                        | Name             | Bit 7  | Bit 6  | Bit 5      | Bit 4                          | Bit 3           | Bit 2          | Bit 1  | Bit 0  | Page               |

|--------------------------------|------------------|--------|--------|------------|--------------------------------|-----------------|----------------|--------|--------|--------------------|

| \$3F (\$5F)                    | SREG             | I      | Т      | Н          | S                              | V               | N              | Z      | С      | page 20            |

| \$3E (\$5E)                    | SPH              | SP15   | SP14   | SP13       | SP12                           | SP11            | SP10           | SP9    | SP8    | page 21            |

| \$3D (\$5D)                    | SPL              | SP7    | SP6    | SP5        | SP4                            | SP3             | SP2            | SP1    | SP0    | page 21            |

| \$3C (\$5C)                    | Reserved         |        |        |            |                                |                 |                |        |        |                    |

| \$3B (\$5B)                    | GIMSK            | INT1   | INT0   | -          | -                              | -               | -              | -      | -      | page 26            |

| \$3A (\$5A)                    | GIFR             | INTF1  | INTF0  |            |                                |                 |                |        |        | page 26            |

| \$39 (\$59)                    | TIMSK            | TOIE1  | OCIE1A | OCIE1B     | -                              | TICIE1          | -              | TOIE0  | -      | page 27            |

| \$38 (\$58)                    | TIFR             | TOV1   | OCF1A  | OCF1B      | -                              | ICF1            | -              | TOV0   | -      | page 28            |

| \$37 (\$57)                    | Reserved         |        |        |            |                                |                 |                |        |        |                    |

| \$36 (\$56)                    | Reserved         |        |        |            |                                |                 |                |        |        |                    |

| \$35 (\$55)                    | MCUCR            | SRE    | SRW    | SE         | SM                             | ISC11           | ISC10          | ISC01  | ISC00  | page 29            |

| \$34 (\$54)                    | Reserved         |        |        |            |                                |                 |                |        |        | P9                 |

| \$33 (\$53)                    | TCCR0            | -      | -      | -          | _                              | -               | CS02           | CS01   | CS00   | page 33            |

| \$32 (\$52)                    | TCNT0            |        |        |            | Timer/Cou                      | inter0 (8 Bits) | 0001           |        | 0000   | page 34            |

| ψυ <u>Σ</u> (ψυ <u>Σ</u> )<br> | Reserved         |        |        |            | 111101/000                     |                 |                |        |        | page 04            |

| \$2F (\$4F)                    | TCCR1A           | COM1A1 | COM1A0 | COM1B1     | COM1B0                         |                 |                | PWM11  | PWM10  | page 36            |

| \$2E (\$4E)                    | TCCR1B           | ICNC1  | ICES1  | -          | -                              | CTC1            | -<br>CS12      | CS11   | CS10   | page 30            |

| \$2E (\$4E)<br>\$2D (\$4D)     | TCOR IB          |        | 10201  |            | Counter1 – Co                  |                 |                | 0311   | 0310   |                    |

|                                | TCNT1H<br>TCNT1L | 1      |        |            | Counter1 – Co<br>Counter1 – Co |                 |                |        |        | page 38            |

| \$2C (\$4C)                    | OCR1AH           | 1      |        |            |                                |                 |                |        |        | page 38            |

| \$2B (\$4B)                    |                  |        |        |            | ter1 – Output C                |                 |                |        |        | page 38            |

| \$2A (\$4A)                    | OCR1AL           |        |        |            | iter1 – Output (               |                 |                |        |        | page 38            |

| \$29 (\$49)                    | OCR1BH           |        |        |            | ter1 – Output C                |                 |                |        |        | page 39            |

| \$28 (\$48)                    | OCR1BL           |        |        | Timer/Cour | iter1 – Output C               | Compare Regis   | ter B Low Byte |        |        | page 39            |

|                                | Reserved         |        |        |            |                                |                 |                |        |        |                    |

| \$25 (\$45)                    | ICR1H            |        |        |            | unter1 – Input                 |                 |                |        |        | page 39            |

| \$24 (\$44)                    | ICR1L            |        |        | Timer/Co   | ounter1 – Input                | Capture Regist  | er Low Byte    |        |        | page 39            |

|                                | Reserved         |        |        |            |                                | -               | -              | -      |        |                    |

| \$21 (\$41)                    | WDTCR            | -      | -      | -          | WDTOE                          | WDE             | WDP2           | WDP1   | WDP0   | page 42            |

| \$20 (\$40)                    | Reserved         |        |        |            |                                |                 |                |        |        |                    |

| \$1F (\$3F)                    | EEARH            | -      | -      | -          | -                              | -               | -              | -      | EEAR8  | page 44            |

| \$1E (\$3E)                    | EEARL            |        |        | EE         | EPROM Addres                   | s Register Low  | / Byte         |        |        | page 44            |

| \$1D (\$3D)                    | EEDR             |        |        |            | EEPROM                         | Data Register   |                |        |        | page 44            |

| \$1C (\$3C)                    | EECR             | -      | -      | -          | -                              | -               | EEMWE          | EEWE   | EERE   | page 44            |

| \$1B (\$3B)                    | PORTA            | PORTA7 | PORTA6 | PORTA5     | PORTA4                         | PORTA3          | PORTA2         | PORTA1 | PORTA0 | page 63            |

| \$1A (\$3A)                    | DDRA             | DDA7   | DDA6   | DDA5       | DDA4                           | DDA3            | DDA2           | DDA1   | DDA0   | page 63            |

| \$19 (\$39)                    | PINA             | PINA7  | PINA6  | PINA5      | PINA4                          | PINA3           | PINA2          | PINA1  | PINA0  | page 63            |

| \$18 (\$38)                    | PORTB            | PORTB7 | PORTB6 | PORTB5     | PORTB4                         | PORTB3          | PORTB2         | PORTB1 | PORTB0 | page 65            |

| \$17 (\$37)                    | DDRB             | DDB7   | DDB6   | DDB5       | DDB4                           | DDB3            | DDB2           | DDB1   | DDB0   | page 65            |

| \$16 (\$36)                    | PINB             | PINB7  | PINB6  | PINB5      | PINB4                          | PINB3           | PINB2          | PINB1  | PINB0  | page 65            |

| \$15 (\$35)                    | PORTC            | PORTC7 | PORTC6 | PORTC5     | PORTC4                         | PORTC3          | PORTC2         | PORTC1 | PORTC0 | page 70            |

| \$14 (\$34)                    | DDRC             | DDC7   | DDC6   | DDC5       | DDC4                           | DDC3            | DDC2           | DDC1   | DDC0   | page 70            |

| \$13 (\$33)                    | PINC             | PINC7  | PINC6  | PINC5      | PINC4                          | PINC3           | PINC2          | PINC1  | PINC0  | page 71<br>page 71 |

| \$12 (\$32)                    | PORTD            | PORTD7 | PORTD6 | PORTD5     | PORTD4                         | PORTD3          | PORTD2         | PORTD1 | PORTD0 | page 73            |

| \$11 (\$31)                    | DDRD             | DDD7   | DDD6   | DDD5       | DDD4                           | DDD3            | DDD2           | DDD1   | DDD0   | page 73            |

| \$10 (\$30)                    | PIND             | PIND7  | PIND6  | PIND5      | PIND4                          | PIND3           | PIND2          | PIND1  | PIND0  | page 73<br>page 73 |

|                                |                  |        |        | FINDS      |                                | a Register      | FINDZ          |        | FINDU  |                    |

| \$0F (\$2F)                    | SPDR             | 801F   | WCO    |            |                                | U U             |                |        |        | page 51            |

| \$0E (\$2E)                    | SPSR             | SPIF   | WCOL   | -          | -                              | -               | -              | -      | -      | page 50            |

| \$0D (\$2D)                    | SPCR             | SPIE   | SPE    | DORD       | MSTR                           | CPOL            | CPHA           | SPR1   | SPR0   | page 49            |

| \$0C (\$2C)                    | UDR              | D) (2  |        |            |                                | Data Register   |                |        |        | page 55            |

| \$0B (\$2B)                    | USR              | RXC    | TXC    | UDRE       | FE                             | OR              | -              | -      | -      | page 55            |

| \$0A (\$2A)                    | UCR              | RXCIE  | TXCIE  | UDRIE      | RXEN                           | TXEN            | CHR9           | RXB8   | TXB8   | page 56            |

| \$09 (\$29)                    | UBRR             |        |        | I          |                                | Rate Register   |                |        |        | page 58            |

| \$08 (\$28)                    | ACSR             | ACD    | -      | ACO        | ACI                            | ACIE            | ACIC           | ACIS1  | ACIS0  | page 59            |

|                                | Decembed         |        |        |            |                                |                 |                |        |        |                    |

|                                | Reserved         |        |        |            |                                |                 |                |        |        |                    |

Notes: 1. For compatibility with future devices, reserved bits should be written to zero if accessed. Reserved I/O memory addresses should never be written.

Some of the status flags are cleared by writing a logical "1" to them. Note that the CBI and SBI instructions will operate on all bits in the I/O register, writing a one back into any flag read as set, thus clearing the flag. The CBI and SBI instructions work with registers \$00 to \$1F only.