Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

# Details

| Detuils                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                 |

| Core Processor             | AVR                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 4MHz                                                                     |

| Connectivity               | SPI, UART/USART                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 32                                                                       |

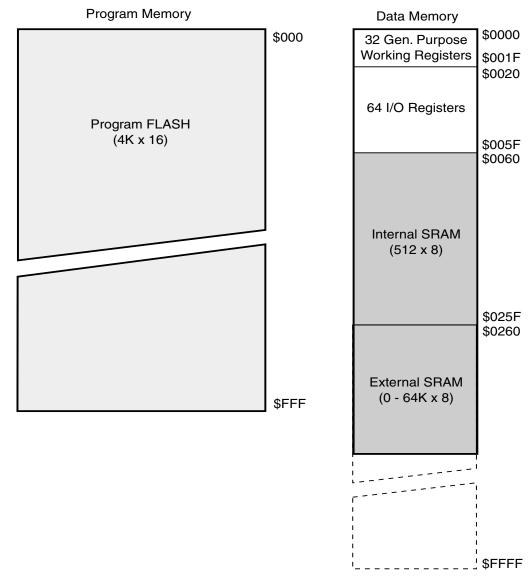

| Program Memory Size        | 8KB (4K x 16)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 512 x 8                                                                  |

| RAM Size                   | 512 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 6V                                                                |

| Data Converters            | -                                                                        |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C                                                             |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 44-LCC (J-Lead)                                                          |

| Supplier Device Package    | 44-PLCC (16.6x16.6)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at90s8515a-4ji |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

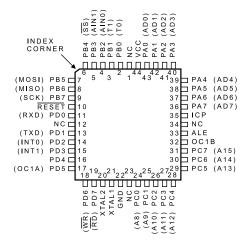

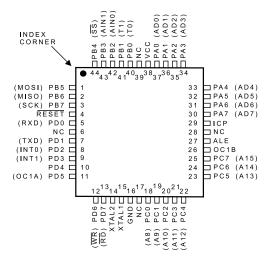

# **Pin Configurations**

PDIP

PLCC

|       | current if the pull-up resistors are activated. The Port D pins are tri-stated when a reset condition becomes active, even if the clock is not active.                                                                                                               |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | Port D also serves the functions of various special features of the AT90S8515 as listed on page 73.                                                                                                                                                                  |

| RESET | Reset input. A low level on this pin for more than 50 ns will generate a reset, even if the clock is not running. Shorter pulses are not guaranteed to generate a reset.                                                                                             |

| XTAL1 | Input to the inverting oscillator amplifier and input to the internal clock operating circuit.                                                                                                                                                                       |

| XTAL2 | Output from the inverting oscillator amplifier.                                                                                                                                                                                                                      |

| ICP   | ICP is the input pin for the Timer/Counter1 Input Capture function.                                                                                                                                                                                                  |

| OC1B  | OC1B is the output pin for the Timer/Counter1 Output CompareB function.                                                                                                                                                                                              |

| ALE   | ALE is the Address Latch Enable used when the External Memory is enabled. The ALE strobe is used to latch the low-order address (8 bits) into an address latch during the first access cycle, and the AD0 - 7 pins are used for data during the second access cycle. |

AT90S8515

Figure 5. Memory Maps

# General-purpose Register File

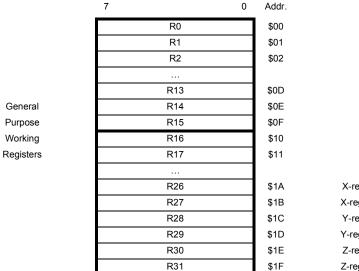

Figure 6 shows the structure of the 32 general-purpose working registers in the CPU.

# Figure 6. AVR CPU General-purpose Working Registers

X-register low byte X-register high byte Y-register low byte Y-register high byte Z-register low byte Z-register high byte

All the register operating instructions in the instruction set have direct and single-cycle access to all registers. The only exception are the five constant arithmetic and logic instructions SBCI, SUBI, CPI, ANDI and ORI between a constant and a register and the LDI instruction for load immediate constant data. These instructions apply to the second half of the registers in the register file (R16..R31). The general SBC, SUB, CP, AND and OR and all other operations between two registers or on a single register apply to the entire register file.

As shown in Figure 6, each register is also assigned a data memory address, mapping them directly into the first 32 locations of the user Data Space. Although not being physically implemented as SRAM locations, this memory organization provides great flexibility in access of the registers, as the X-, Y- and Z-registers can be set to index any register in the file.

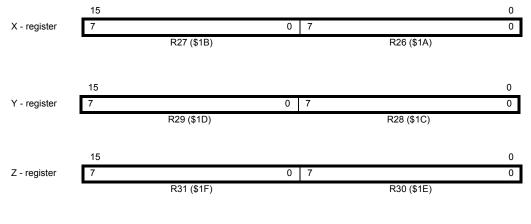

The registers R26..R31 have some added functions to their general-purpose usage. These registers are address pointers for indirect addressing of the Data Space. The three indirect address registers X, Y, and Z are defined as:

Figure 7. X-, Y-, and Z-registers

AT90S8515

X-register, Y-register and

**Z-register**

10

A 16-bit data address is contained in the 16 LSBs of a 2-word instruction. Rd/Rr specify the destination or source register.

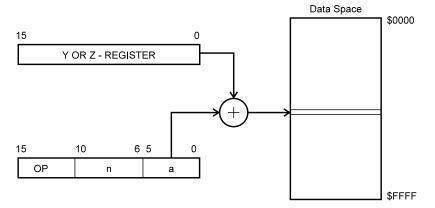

Operand address is the result of the Y- or Z-register contents added to the address contained in six bits of the instruction word.

# Figure 14. Data Indirect Addressing

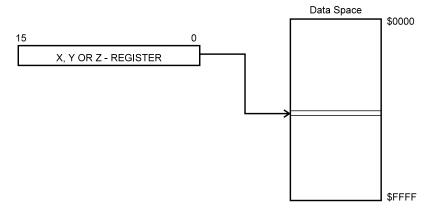

Operand address is the contents of the X-, Y-, or the Z-register.

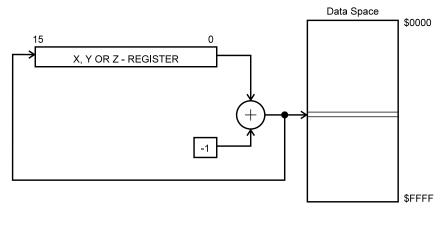

# Figure 15. Data Indirect Addressing with Pre-decrement

Data Indirect with Displacement

# **Data Indirect**

Data Indirect with Pre-

decrement

Figure

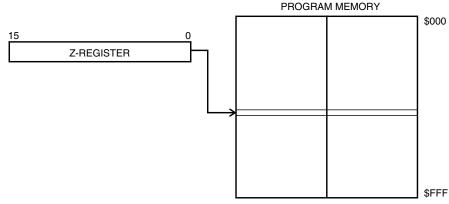

Indirect Program Addressing, Figure 18. Indirect Program Memory Addressing IJMP and ICALL

Program execution continues at address contained by the Z-register (i.e., the PC is loaded with the contents of the Z-register).

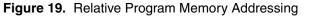

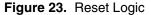

Program execution continues at address PC + k + 1. The relative address k is -2048 to 2047.

**EEPROM Data Memory** The AT90S8515 contains 512 bytes of data EEPROM memory. It is organized as a separate data space, in which single bytes can be read and written. The EEPROM has an endurance of at least 100,000 write/erase cycles. The access between the EEPROM and the CPU is described on page 44, specifying the EEPROM address registers, the EEPROM data register and the EEPROM control register.

For the SPI data downloading, see page 86 for a detailed description.

**Memory Access Times** This section describes the general access timing concepts for instruction execution and internal memory access.

The AVR CPU is driven by the System Clock  $\emptyset$ , directly generated from the external clock crystal for the chip. No internal clock division is used.

Figure 20 shows the parallel instruction fetches and instruction executions enabled by the Harvard architecture and the fast-access register file concept. This is the basic pipelining concept to obtain up to 1 MIPS per MHz with the corresponding unique results for functions per cost, functions per clocks and functions per power unit.

**Execution Timing**

**Relative Program Addressing,**

**RJMP and RCALL**

| \$00f | ldi r16,low(RAMEND) |

|-------|---------------------|

| \$010 | out SPL,r16         |

| \$011 | <instr> xxx</instr> |

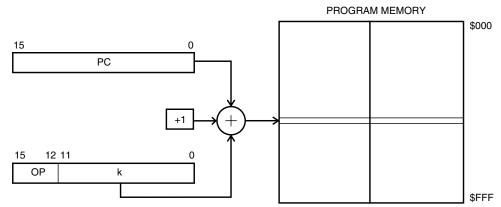

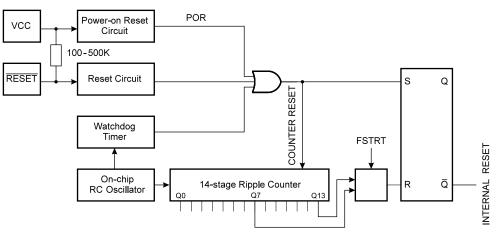

**Reset Sources**

- The AT90S8515 has three sources of reset:

- Power-on Reset. The MCU is reset when the supply voltage is below the Power-on Reset threshold (V<sub>POT</sub>).

- External Reset. The MCU is reset when a low level is present on the RESET pin for more than 50 ns.

- Watchdog Reset. The MCU is reset when the Watchdog timer period expires and the Watchdog is enabled.

During reset, all I/O registers are set to their initial values and the program starts execution from address \$000. The instruction placed in address \$000 must be an RJMP (relative jump) instruction to the reset handling routine. If the program never enables an interrupt source, the interrupt vectors are not used and regular program code can be placed at these locations. The circuit diagram in Figure 23 shows the reset logic. Table 3 defines the timing and electrical parameters of the reset circuitry.

Table 3. Reset Characteristics

| Symbol                           | Parameter                                         | Min  | Тур  | Max                 | Units |

|----------------------------------|---------------------------------------------------|------|------|---------------------|-------|

| V <sub>POT</sub> <sup>(Not</sup> | Power-on Reset Threshold Voltage (rising)         | 0.8  | 1.2  | 1.6                 | V     |

| e:)                              | Power-on Reset Threshold Voltage (falling)        | 0.2  | 0.4  | 0.6                 | V     |

| V <sub>RST</sub>                 | RESET Pin Threshold Voltage                       | _    | _    | 0.9 V <sub>CC</sub> | V     |

| t <sub>TOUT</sub>                | Reset Delay Time-out Period FSTRT<br>Unprogrammed | 11.0 | 16.0 | 21.0                | ms    |

| t <sub>TOUT</sub>                | Reset Delay Time-out Period FSTRT<br>Programmed   | 0.25 | 0.28 | 0.31                | ms    |

Note: The Power-on Reset will not work unless the supply voltage has been below  $\rm V_{POT}$  (falling).

# AT90S8515

# **External Interrupts** The external interrupts are triggered by the INT1 and INT0 pins. Observe that, if enabled, the interrupts will trigger even if the INT0/INT1 pins are configured as outputs. This feature provides a way of generating a software interrupt. The external interrupts can be triggered by a falling or rising edge or a low level. This is set up as indicated in the specification for the MCU Control Register (MCUCR). When the external interrupt is enabled and is configured as level-triggered, the interrupt will trigger as long as the pin is held low.

The external interrupts are set up as described in the specification for the MCU Control Register (MCUCR).

Interrupt Response Time The interrupt execution response for all the enabled AVR interrupts is four clock cycles minimum. Four clock cycles after the interrupt flag has been set, the program vector address for the actual interrupt handling routine is executed. During this 4-clock-cycle period, the Program Counter (2 bytes) is pushed onto the stack and the Stack Pointer is decremented by 2. The vector is normally a relative jump to the interrupt routine, and this jump takes two clock cycles. If an interrupt occurs during execution of a multi-cycle instruction, this instruction is completed before the interrupt is served.

A return from an interrupt handling routine (same as for a subroutine call routine) takes four clock cycles. During these four clock cycles, the Program Counter (2 bytes) is popped back from the stack, the Stack Pointer is incremented by 2 and the I-flag in SREG is set. When the AVR exits from an interrupt, it will always return to the main program and execute one more instruction before any pending interrupt is served.

Note that the Status Register (SREG) is not handled by the AVR hardware, for neither interrupts nor subroutines. For the interrupt handling routines requiring a storage of the SREG, this must be performed by user software.

For interrupts triggered by events that can remain static (e.g., the Output Compare Register1 A matching the value of Timer/Counter1), the interrupt flag is set when the event occurs. If the interrupt flag is cleared and the interrupt condition persists, the flag will not be set until the event occurs the next time. Note that an external level interrupt will only be remembered for as long as the interrupt condition is active.

# MCU Control Register – MCUCR

The MCU Control Register contains control bits for general MCU functions.

| Bit           | 7   | 6   | 5   | 4   | 3     | 2     | 1     | 0     |       |

|---------------|-----|-----|-----|-----|-------|-------|-------|-------|-------|

| \$35 (\$55)   | SRE | SRW | SE  | SM  | ISC11 | ISC10 | ISC01 | ISC00 | MCUCR |

| Read/Write    | R/W | R/W | R/W | R/W | R/W   | R/W   | R/W   | R/W   |       |

| Initial Value | 0   | 0   | 0   | 0   | 0     | 0     | 0     | 0     |       |

# • Bit 7 – SRE: External SRAM Enable

When the SRE bit is set (one), the external data SRAM is enabled and the pin functions AD0 - 7 (Port A), A8 - 15 (Port C),  $\overline{\text{WR}}$  and  $\overline{\text{RD}}$  (Port D) are activated as the alternate pin functions. Then the SRE bit overrides any pin direction settings in the respective data direction registers. See "SRAM Data Memory – Internal and External" on page 12 for a description of the external SRAM pin functions. When the SRE bit is cleared (zero), the external data SRAM is disabled and the normal pin and data direction settings are used.

# • Bit 6 – SRW: External SRAM Wait State

When the SRW bit is set (one), a one-cycle wait state is inserted in the external data SRAM access cycle. When the SRW bit is cleared (zero), the external data SRAM access is executed with the normal three-cycle scheme. See Figure 43 and Figure 44.

- 1. In the same operation, write a logical "1" to WDTOE and WDE. A logical "1" must be written to WDE even though it is set to one before the disable operation starts.

- 2. Within the next four clock cycles, write a logical "0" to WDE. This disables the Watchdog.

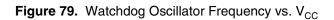

- Bits 2..0 WDP2, WDP1, WDP0: Watchdog Timer Prescaler 2, 1 and 0

The WDP2, WDP1 and WDP0 bits determine the Watchdog Timer prescaling when the Watchdog Timer is enabled. The different prescaling values and their corresponding Time-out periods are shown in Table 14.

| WDP2 | WDP1 | WDP0 | Number of WDT<br>Oscillator Cycles | Typical Time-out<br>at V <sub>CC</sub> = 3.0V | Typical Time-out<br>at V <sub>CC</sub> = 5.0V |

|------|------|------|------------------------------------|-----------------------------------------------|-----------------------------------------------|

| 0    | 0    | 0    | 16K cycles                         | 47.0 ms                                       | 15.0 ms                                       |

| 0    | 0    | 1    | 32K cycles                         | 94.0 ms                                       | 30.0 ms                                       |

| 0    | 1    | 0    | 64K cycles                         | 0.19 s                                        | 60.0 ms                                       |

| 0    | 1    | 1    | 128K cycles                        | 0.38 s                                        | 0.12 s                                        |

| 1    | 0    | 0    | 256K cycles                        | 0.75 s                                        | 0.24 s                                        |

| 1    | 0    | 1    | 512K cycles                        | 1.5 s                                         | 0.49 s                                        |

| 1    | 1    | 0    | 1,024K cycles                      | 3.0 s                                         | 0.97 s                                        |

| 1    | 1    | 1    | 2,048K cycles                      | 6.0 s                                         | 1.9 s                                         |

| Table 14. | Watchdog | Timer Pre | scale Select |

|-----------|----------|-----------|--------------|

|-----------|----------|-----------|--------------|

Note: The frequency of the Watchdog oscillator is voltage-dependent as shown in the Electrical Characteristics section.

The WDR (Watchdog Reset) instruction should always be executed before the Watchdog Timer is enabled. This ensures that the reset period will be in accordance with the Watchdog Timer prescale settings. If the Watchdog Timer is enabled without reset, the Watchdog Timer may not start to count from zero.

To avoid unintentional MCU reset, the Watchdog Timer should be disabled or reset before changing the Watchdog Timer Prescale Select.

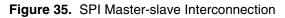

The system is single-buffered in the transmit direction and double-buffered in the receive direction. This means that bytes to be transmitted cannot be written to the SPI Data Register before the entire shift cycle is completed. When receiving data, however, a received byte must be read from the SPI Data Register before the next byte has been completely shifted in. Otherwise, the first byte is lost.

When the SPI is enabled, the data direction of the MOSI, MISO, SCK and  $\overline{SS}$  pins is overridden according to Table 15.

| Table 15. SPI Pin Overric |

|---------------------------|

|---------------------------|

| Pin  | Direction, Master SPI | Direction, Slave SPI |

|------|-----------------------|----------------------|

| MOSI | User Defined          | Input                |

| MISO | Input                 | User Defined         |

| SCK  | User Defined          | Input                |

| SS   | User Defined          | Input                |

Note: See "Alternate Functions of Port B" on page 66 for a detailed description of how to define the direction of the user-defined SPI pins.

**SS** Pin Functionality When the SPI is configured as a master (MSTR in SPCR is set), the user can determine the direction of the SS pin. If SS is configured as an output, the pin is a general output pin, which does not affect the SPI system. If SS is configured as an input, it must be held high to ensure master SPI operation. If the SS pin is driven low by peripheral circuitry when the SPI is configured as master with the SS pin defined as an input, the SPI system interprets this as another master selecting the SPI as a slave and starts to send data to it. To avoid bus contention, the SPI system takes the following actions:

- 1. The MSTR bit in SPCR is cleared and the SPI system becomes a slave. As a result of the SPI becoming a slave, the MOSI and SCK pins become inputs.

- 2. The SPIF flag in SPSR is set, and if the SPI interrupt is enabled and the I-bit in SREG is set, the interrupt routine will be executed.

Thus, when interrupt-driven SPI transmittal is used in Master Mode and there exists a possibility that  $\overline{SS}$  is driven low, the interrupt should always check that the MSTR bit is still set. Once the MSTR bit has been cleared by a slave select, it must be set by the user to re-enable SPI Master Mode.

When the SPI is configured as a slave, the  $\overline{SS}$  pin is always input. When  $\overline{SS}$  is held low, the SPI is activated and MISO becomes an output if configured so by the user. All other

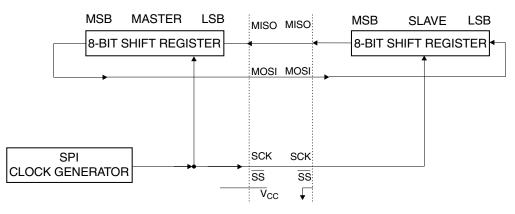

If the 10(11)-bit Transmitter shift register is empty, data is transferred from UDR to the shift register. At this time the UDRE (UART Data Register Empty) bit in the UART Status Register, USR, is set. When this bit is set (one), the UART is ready to receive the next character. At the same time as the data is transferred from UDR to the 10(11)-bit shift register, bit 0 of the shift register is cleared (start bit) and bit 9 or 10 is set (stop bit). If 9-bit data word is selected (the CHR9 bit in the UART Control Register, UCR is set), the TXB8 bit in UCR is transferred to bit 9 in the Transmit shift register.

On the baud rate clock following the transfer operation to the shift register, the start bit is shifted out on the TXD pin. Then follows the data, LSB first. When the stop bit has been shifted out, the shift register is loaded if any new data has been written to the UDR during the transmission. During loading, UDRE is set. If there is no new data in the UDR register to send when the stop bit is shifted out, the UDRE flag will remain set until UDR is written again. When no new data has been written and the stop bit has been present on TXD for one bit length, the TX Complete flag (TXC) in USR is set.

The TXEN bit in UCR enables the UART Transmitter when set (one). When this bit is cleared (zero), the PD1 pin can be used for general I/O. When TXEN is set, the UART Transmitter will be connected to PD1, which is forced to be an output pin regardless of the setting of the DDD1 bit in DDRD.

# **Data Reception** Figure 39 shows a block diagram of the UART Receiver.

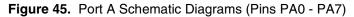

PORTAn has to be cleared (zero) or the pin has to be configured as an output pin. The Port A pins are tri-stated when a reset condition becomes active, even if the clock is not active..

Table 19. DDAn Effects on Port A Pins

| DDAn | PORTAn | I/O    | Pull-up | Comment                                     |

|------|--------|--------|---------|---------------------------------------------|

| 0    | 0      | Input  | No      | Tri-state (high-Z)                          |

| 0    | 1      | Input  | Yes     | PAn will source current if ext. pulled low. |

| 1    | 0      | Output | No      | Push-pull Zero Output                       |

| 1    | 1      | Output | No      | Push-pull One Output                        |

Note: n: 7,6...0, pin number.

**Port A Schematics** Note that all port pins are synchronized. The synchronization latch is, however, not shown in the figure.

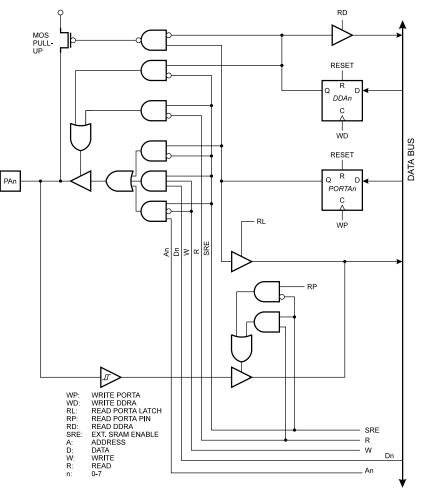

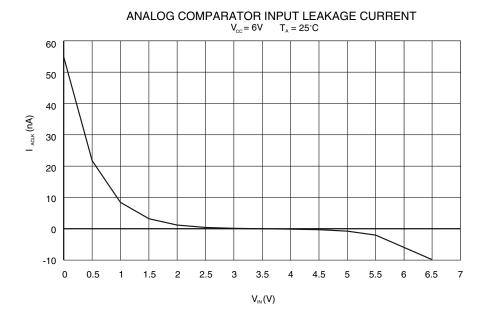

# • AIN0 – Port B, Bit 2

AINO: Analog Comparator Positive Input. When configured as an input (DDB2 is cleared [zero]) and with the internal MOS pull-up resistor switched off (PB2 is cleared [zero]), this pin also serves as the positive input of the On-chip Analog Comparator.

# • T1 – Port B, Bit 1

T1: Timer/Counter1 counter source. See the timer description for further details

# • T0 - Port B, Bit 0

T0: Timer/Counter0 counter source. See the timer description for further details.

**Port B Schematics** Note that all port pins are synchronized. The synchronization latches are, however, not shown in the figures.

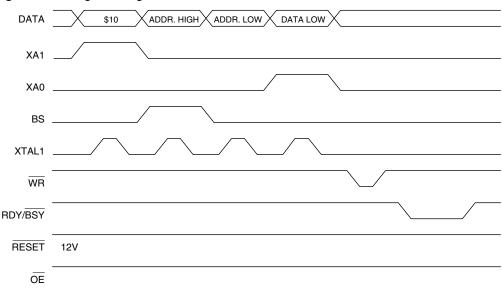

- 1. Set BS to "1". This selects high data.

- 2. Give WR a negative pulse. This starts programming of the data byte. RDY/BSY goes low.

- 3. Wait until RDY/BSY goes high to program the next byte.

(See Figure 62 for signal waveforms.)

The loaded command and address are retained in the device during programming. For efficient programming, the following should be considered:

- The command needs only be loaded once when writing or reading multiple memory locations.

- Address high byte needs only be loaded before programming a new 256-word page in the Flash.

- Skip writing the data value \$FF, that is, the contents of the entire Flash and EEPROM after a Chip Erase.

These considerations also apply to EEPROM programming and Flash, EEPROM and signature byte reading.

Figure 61. Programming the Flash Waveforms

# **External Data Memory Timing**

|    |                      |                                                        | 8 MHz Oscillator |       | Variable Oscillator                         |                              |      |

|----|----------------------|--------------------------------------------------------|------------------|-------|---------------------------------------------|------------------------------|------|

|    | Symbol               | Parameter                                              | Min              | Мах   | Min                                         | Max                          | Unit |

| 0  | 1/t <sub>CLCL</sub>  | Oscillator Frequency                                   |                  |       | 0.0                                         | 8.0                          | MHz  |

| 1  | t <sub>LHLL</sub>    | ALE Pulse Width                                        | 32.5             |       | 0.5 t <sub>CLCL</sub> - 30.0 <sup>(1)</sup> |                              | ns   |

| 2  | t <sub>AVLL</sub>    | Address Valid A to ALE Low                             | 22.5             |       | 0.5 t <sub>CLCL</sub> - 40.0 <sup>(1)</sup> |                              | ns   |

| За | t <sub>LLAX_ST</sub> | Address Hold after ALE Low,<br>ST/STD/STS Instructions | 67.5             |       | 0.5 t <sub>CLCL</sub> + 5.0 <sup>(2)</sup>  |                              | ns   |

| Зb | t <sub>LLAX_LD</sub> | Address Hold after ALE Low,<br>LD/LDD/LDS Instructions | 15.0             |       | 15.0                                        |                              | ns   |

| 4  | t <sub>AVLLC</sub>   | Address Valid C to ALE Low                             | 22.5             |       | 0.5 t <sub>CLCL</sub> - 40.0 <sup>(1)</sup> |                              | ns   |

| 5  | t <sub>AVRL</sub>    | Address Valid to RD Low                                | 95.0             |       | 1.0 t <sub>CLCL</sub> - 30.0                |                              | ns   |

| 6  | t <sub>AVWL</sub>    | Address Valid to WR Low                                | 157.5            |       | 1.5 t <sub>CLCL</sub> - 30.0 <sup>(1)</sup> |                              | ns   |

| 7  | t <sub>LLWL</sub>    | ALE Low to WR Low                                      | 105.0            | 145.0 | 1.0 t <sub>CLCL</sub> - 20.0                | 1.0 t <sub>CLCL</sub> + 20.0 | ns   |

| 8  | t <sub>LLRL</sub>    | ALE Low to RD Low                                      | 42.5             | 82.5  | 0.5 t <sub>CLCL</sub> - 20.0 <sup>(2)</sup> | $0.5 t_{CLCL} + 20.0^{(2)}$  | ns   |

| 9  | t <sub>DVRH</sub>    | Data Setup to RD High                                  | 60.0             |       | 60.0                                        |                              | ns   |

| 10 | t <sub>RLDV</sub>    | Read Low to Data Valid                                 |                  | 70.0  |                                             | 1.0 t <sub>CLCL</sub> - 55.0 | ns   |

| 11 | t <sub>RHDX</sub>    | Data Hold after RD High                                | 0.0              |       | 0.0                                         |                              | ns   |

| 12 | t <sub>RLRH</sub>    | RD Pulse Width                                         | 105.0            |       | 1.0 t <sub>CLCL</sub> - 20.0                |                              | ns   |

| 13 | t <sub>DVWL</sub>    | Data Setup to WR Low                                   | 27.5             |       | 0.5 t <sub>CLCL</sub> - 35.0 <sup>(2)</sup> |                              | ns   |

| 14 | t <sub>WHDX</sub>    | Data Hold after WR High                                | 0.0              |       | 0.0                                         |                              | ns   |

| 15 | t <sub>DVWH</sub>    | Data Valid to WR High                                  | 95.0             |       | 1.0 t <sub>CLCL</sub> - 30.0                |                              | ns   |

| 16 | t <sub>wLWH</sub>    | WR Pulse Width                                         | 42.5             |       | 0.5 t <sub>CLCL</sub> - 20.0 <sup>(1)</sup> |                              | ns   |

# Table 38. External Data Memory Characteristics, 4.0V - 6.0V, One Cycle Wait State

|    |                     |                        | 8 MHz Oscillator |       | Variable Oscillator                         |                              |      |

|----|---------------------|------------------------|------------------|-------|---------------------------------------------|------------------------------|------|

|    | Symbol              | Parameter              | Min              | Max   | Min                                         | Max                          | Unit |

| 0  | 1/t <sub>CLCL</sub> | Oscillator Frequency   |                  |       | 0.0                                         | 8.0                          | MHz  |

| 10 | t <sub>RLDV</sub>   | Read Low to Data Valid |                  | 195.0 |                                             | 2.0 t <sub>CLCL</sub> - 55.0 | ns   |

| 12 | t <sub>RLRH</sub>   | RD Pulse Width         | 230.0            |       | 2.0 t <sub>CLCL</sub> - 20.0                |                              | ns   |

| 15 | t <sub>DVWH</sub>   | Data Valid to WR High  | 220.0            |       | 2.0 t <sub>CLCL</sub> - 30.0                |                              | ns   |

| 16 | t <sub>wLWH</sub>   | WR Pulse Width         | 167.5            |       | 1.5 t <sub>CLCL</sub> - 20.0 <sup>(2)</sup> |                              | ns   |

Notes: 1. This assumes 50% clock duty cycle. The half-period is actually the high time of the external clock, XTAL1.

2. This assumes 50% clock duty cycle. The half-period is actually the low time of the external clock, XTAL1.

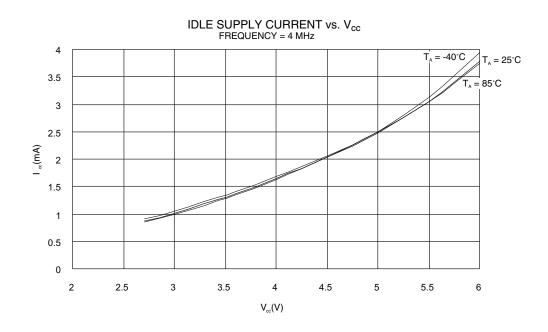

Figure 72. Idle Supply Current vs. V<sub>CC</sub>

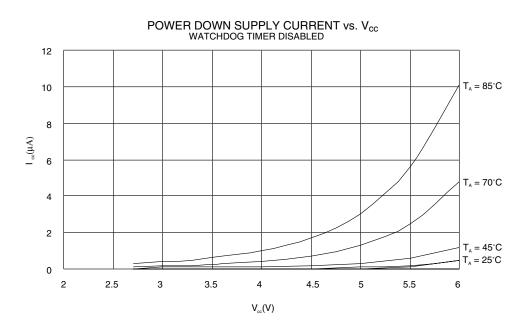

Figure 73. Power-down Supply Current vs. V<sub>CC</sub>

WATCHDOG OSCILLATOR FREQUENCY vs. V<sub>cc</sub>

# **Instruction Set Summary**

| Mnemonic     | Operands        | Description                            | Operation                                             | Flags     | # Clocks   |

|--------------|-----------------|----------------------------------------|-------------------------------------------------------|-----------|------------|

| ARITHMETIC A | ND LOGIC INSTRU | ICTIONS                                |                                                       | •         | _ <b>.</b> |

| ADD          | Rd, Rr          | Add Two Registers                      | $Rd \leftarrow Rd + Rr$                               | Z,C,N,V,H | 1          |

| ADC          | Rd, Rr          | Add with Carry Two Registers           | $Rd \leftarrow Rd + Rr + C$                           | Z,C,N,V,H | 1          |

| ADIW         | Rdl, K          | Add Immediate to Word                  | Rdh:RdI ← Rdh:RdI + K                                 | Z,C,N,V,S | 2          |

| SUB          | Rd, Rr          | Subtract Two Registers                 | $Rd \leftarrow Rd - Rr$                               | Z,C,N,V,H | 1          |

| SUBI         | Rd, K           | Subtract Constant from Register        | $Rd \leftarrow Rd - K$                                | Z,C,N,V,H | 1          |

| SBC          | Rd, Rr          | Subtract with Carry Two Registers      | $Rd \leftarrow Rd - Rr - C$                           | Z,C,N,V,H | 1          |

| SBCI         | Rd, K           | Subtract with Carry Constant from Reg. | $Rd \leftarrow Rd - K - C$                            | Z,C,N,V,H | 1          |

| SBIW         | Rdl, K          | Subtract Immediate from Word           | Rdh:RdI ← Rdh:RdI - K                                 | Z,C,N,V,S | 2          |

| AND          | Rd, Rr          | Logical AND Registers                  | $Rd \leftarrow Rd \bullet Rr$                         | Z,N,V     | 1          |

| ANDI         | Rd, K           | Logical AND Register and Constant      | $Rd \leftarrow Rd ullet K$                            | Z,N,V     | 1          |

| OR           | Rd, Rr          | Logical OR Registers                   | $Rd \leftarrow Rd \lor Rr$                            | Z,N,V     | 1          |

| ORI          | Rd, K           | Logical OR Register and Constant       | $Rd \leftarrow Rd \lor K$                             | Z,N,V     | 1          |

| EOR          | Rd, Rr          | Exclusive OR Registers                 | $Rd \leftarrow Rd \oplus Rr$                          | Z,N,V     | 1          |

| COM          | Rd              | One's Complement                       | $Rd \leftarrow \$FF - Rd$                             | Z,C,N,V   | 1          |

| NEG          | Rd              | Two's Complement                       | Rd ← \$00 - Rd                                        | Z,C,N,V,H | 1          |

| SBR          | Rd, K           | Set Bit(s) in Register                 | $Rd \leftarrow Rd \lor K$                             | Z,N,V     | 1          |

| CBR          | Rd, K           | Clear Bit(s) in Register               | $Rd \leftarrow Rd \bullet (\$FF - K)$                 | Z,N,V     | 1          |

| INC          | Rd              | Increment                              | $Rd \leftarrow Rd + 1$                                | Z,N,V     | 1          |

| DEC          | Rd              | Decrement                              | $Rd \leftarrow Rd$ - 1                                | Z,N,V     | 1          |

| TST          | Rd              | Test for Zero or Minus                 | $Rd \leftarrow Rd \bullet Rd$                         | Z,N,V     | 1          |

| CLR          | Rd              | Clear Register                         | $Rd \leftarrow Rd \oplus Rd$                          | Z,N,V     | 1          |

| SER          | Rd              | Set Register                           | $Rd \leftarrow FF$                                    | None      | 1          |

| BRANCH INSTR |                 |                                        |                                                       |           |            |

| RJMP         | k               | Relative Jump                          | $PC \leftarrow PC + k + 1$                            | None      | 2          |

| IJMP         |                 | Indirect Jump to (Z)                   | $PC \leftarrow Z$                                     | None      | 2          |

| RCALL        | k               | Relative Subroutine Call               | $PC \leftarrow PC + k + 1$                            | None      | 3          |

| ICALL        |                 | Indirect Call to (Z)                   | $PC \leftarrow Z$                                     | None      | 3          |

| RET          |                 | Subroutine Return                      | $PC \leftarrow STACK$                                 | None      | 4          |

| RETI         |                 | Interrupt Return                       | PC ← STACK                                            | 1         | 4          |

| CPSE         | Rd, Rr          | Compare, Skip if Equal                 | if (Rd = Rr) PC $\leftarrow$ PC + 2 or 3              | None      | 1/2/3      |

| CP           | Rd, Rr          | Compare                                | Rd - Rr                                               | Z,N,V,C,H | 1          |

| CPC          | Rd, Rr          | Compare with Carry                     | Rd - Rr - C                                           | Z,N,V,C,H | 1          |

| CPI          | Rd, K           | Compare Register with Immediate        | Rd - K                                                | Z,N,V,C,H | 1          |

| SBRC         | Rr, b           | Skip if Bit in Register Cleared        | if (Rr(b) = 0) PC $\leftarrow$ PC + 2 or 3            | None      | 1/2/3      |

| SBRS         | Rr, b           | Skip if Bit in Register is Set         | if $(Rr(b) = 1) PC \leftarrow PC + 2 \text{ or } 3$   | None      | 1/2/3      |

| SBIC         | P, b            | Skip if Bit in I/O Register Cleared    | if $(P(b) = 0) PC \leftarrow PC + 2 \text{ or } 3$    | None      | 1/2/3      |

| SBIS         | P, b            | Skip if Bit in I/O Register is Set     | if (P(b) = 1) PC $\leftarrow$ PC + 2 or 3             | None      | 1/2/3      |

| BRBS         | s, k            | Branch if Status Flag Set              | if (SREG(s) = 1) then PC $\leftarrow$ PC + k + 1      | None      | 1/2        |

| BRBC         | s, k            | Branch if Status Flag Cleared          | if (SREG(s) = 0) then PC $\leftarrow$ PC + k + 1      | None      | 1/2        |

| BREQ         | k               | Branch if Equal                        | if (Z = 1) then PC $\leftarrow$ PC + k + 1            | None      | 1/2        |

| BRNE         | k               | Branch if Not Equal                    | if (Z = 0) then PC $\leftarrow$ PC + k + 1            | None      | 1/2        |

| BRCS         | k               | Branch if Carry Set                    | if (C = 1) then PC $\leftarrow$ PC + k + 1            | None      | 1/2        |

| BRCC         | k               | Branch if Carry Cleared                | if (C = 0) then PC $\leftarrow$ PC + k + 1            | None      | 1/2        |

| BRSH         | k               | Branch if Same or Higher               | if (C = 0) then PC $\leftarrow$ PC + k + 1            | None      | 1/2        |

| BRLO         | k               | Branch if Lower                        | if (C = 1) then PC $\leftarrow$ PC + k + 1            | None      | 1/2        |

| BRMI         | k               | Branch if Minus                        | if (N = 1) then PC $\leftarrow$ PC + k + 1            | None      | 1/2        |

| BRPL         | k               | Branch if Plus                         | if (N = 0) then PC $\leftarrow$ PC + k + 1            | None      | 1/2        |

| BRGE         | k               | Branch if Greater or Equal, Signed     | if $(N \oplus V = 0)$ then PC $\leftarrow$ PC + k + 1 | None      | 1/2        |

| BRLT         | k               | Branch if Less Than Zero, Signed       | if $(N \oplus V = 1)$ then PC $\leftarrow$ PC + k + 1 | None      | 1/2        |

| BRHS         | k               | Branch if Half-carry Flag Set          | if (H = 1) then PC $\leftarrow$ PC + k + 1            | None      | 1/2        |

| BRHC         | k               | Branch if Half-carry Flag Cleared      | if (H = 0) then PC $\leftarrow$ PC + k + 1            | None      | 1/2        |

| BRTS         | k               | Branch if T-flag Set                   | if (T = 1) then PC $\leftarrow$ PC + k + 1            | None      | 1/2        |

| BRTC         | k               | Branch if T-flag Cleared               | if (T = 0) then PC $\leftarrow$ PC + k + 1            | None      | 1/2        |

| BRVS         | k               | Branch if Overflow Flag is Set         | if $(V = 1)$ then PC $\leftarrow$ PC + k + 1          | None      | 1/2        |

| BRVC         | k               | Branch if Overflow Flag is Cleared     | if $(V = 0)$ then PC $\leftarrow$ PC + k + 1          | None      | 1/2        |

| BRIE         | k               | Branch if Interrupt Enabled            | if (I = 1) then PC $\leftarrow$ PC + k + 1            | None      | 1/2        |

| BRID         | k               | Branch if Interrupt Disabled           | if (I = 0) then PC $\leftarrow$ PC + k + 1            | None      | 1/2        |

# AT90S8515 Ordering Information

| Speed (MHz) | Power Supply | Ordering Code | Package | Operation Range |

|-------------|--------------|---------------|---------|-----------------|

| 4           | 2.7V - 6.0V  | AT90S8515-4AC | 44A     | Commercial      |

|             |              | AT90S8515-4JC | 44J     | (0°C to 70°C)   |

|             |              | AT90S8515-4PC | 40P6    |                 |

|             |              | AT90S8515-4AI | 44A     | Industrial      |

|             |              | AT90S8515-4JI | 44J     | (-40°C to 85°C) |

|             |              | AT90S8515-4PI | 40P6    |                 |

| 8           | 4.0V - 6.0V  | AT90S8515-8AC | 44A     | Commercial      |

|             |              | AT90S8515-8JC | 44J     | (0°C to 70°C)   |

|             |              | AT90S8515-8PC | 40P6    |                 |

|             |              | AT90S8515-8AI | 44A     | Industrial      |

|             |              | AT90S8515-8JI | 44J     | (-40°C to 85°C) |

|             |              | AT90S8515-8PI | 40P6    |                 |

Note: Order AT90S8515A-XXX for devices with the FSTRT Fuse programmed.

| Package Type |                                                                   |  |

|--------------|-------------------------------------------------------------------|--|

| 44 <b>A</b>  | 44-lead, Thin (1.0 mm) Plastic Gull Wing Quad Flat Package (TQFP) |  |

| 44J          | 44J 44-lead, Plastic J-leaded Chip Carrier (PLCC)                 |  |

| 40P6         | 40-lead, 0.600" Wide, Plastic Dual Inline Package (PDIP)          |  |

# 108 AT90S8515

# **Atmel Headquarters**

Corporate Headquarters 2325 Orchard Parkway San Jose, CA 95131 TEL (408) 441-0311 FAX (408) 487-2600

# Europe

Atmel SarL Route des Arsenaux 41 Casa Postale 80 CH-1705 Fribourg Switzerland TEL (41) 26-426-5555 FAX (41) 26-426-5500

# Asia

Atmel Asia, Ltd. Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimhatsui East Kowloon Hong Kong TEL (852) 2721-9778 FAX (852) 2722-1369

## Japan

Atmel Japan K.K. 9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan TEL (81) 3-3523-3551 FAX (81) 3-3523-7581

# **Atmel Product Operations**

Atmel Colorado Springs 1150 E. Cheyenne Mtn. Blvd. Colorado Springs, CO 80906 TEL (719) 576-3300 FAX (719) 540-1759

# Atmel Grenoble

Avenue de Rochepleine BP 123 38521 Saint-Egreve Cedex, France TEL (33) 4-7658-3000 FAX (33) 4-7658-3480

## Atmel Heilbronn

Theresienstrasse 2 POB 3535 D-74025 Heilbronn, Germany TEL (49) 71 31 67 25 94 FAX (49) 71 31 67 24 23

# Atmel Nantes

La Chantrerie BP 70602 44306 Nantes Cedex 3, France TEL (33) 0 2 40 18 18 18 FAX (33) 0 2 40 18 19 60

# Atmel Rousset

Zone Industrielle 13106 Rousset Cedex, France TEL (33) 4-4253-6000 FAX (33) 4-4253-6001

# Atmel Smart Card ICs

Scottish Enterprise Technology Park East Kilbride, Scotland G75 0QR TEL (44) 1355-357-000 FAX (44) 1355-242-743

> *e-mail* literature@atmel.com

> Web Site http://www.atmel.com

BBS 1-(408) 436-4309

### © Atmel Corporation 2001.

Atmel Corporation makes no warranty for the use of its products, other than those expressly contained in the Company's standard warranty which is detailed in Atmel's Terms and Conditions located on the Company's web site. The Company assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of Atmel are granted by the Company in connection with the sale of Atmel products, expressly or by implication. Atmel's products are not authorized for use as critical components in life support devices or systems.

ATMEL® and AVR® are the registered trademarks of Atmel.

Other terms and product names may be the trademarks of others.