#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Obsolete                                                                 |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | AVR                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 8MHz                                                                     |

| Connectivity               | SPI, UART/USART                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 32                                                                       |

| Program Memory Size        | 8KB (4K x 16)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 512 x 8                                                                  |

| RAM Size                   | 512 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                  |

| Data Converters            | -                                                                        |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C                                                             |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 44-TQFP                                                                  |

| Supplier Device Package    | 44-TQFP (10x10)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at90s8515a-8ai |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|       | current if the pull-up resistors are activated. The Port D pins are tri-stated when a reset condition becomes active, even if the clock is not active.                                                                                                               |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | Port D also serves the functions of various special features of the AT90S8515 as listed on page 73.                                                                                                                                                                  |

| RESET | Reset input. A low level on this pin for more than 50 ns will generate a reset, even if the clock is not running. Shorter pulses are not guaranteed to generate a reset.                                                                                             |

| XTAL1 | Input to the inverting oscillator amplifier and input to the internal clock operating circuit.                                                                                                                                                                       |

| XTAL2 | Output from the inverting oscillator amplifier.                                                                                                                                                                                                                      |

| ICP   | ICP is the input pin for the Timer/Counter1 Input Capture function.                                                                                                                                                                                                  |

| OC1B  | OC1B is the output pin for the Timer/Counter1 Output CompareB function.                                                                                                                                                                                              |

| ALE   | ALE is the Address Latch Enable used when the External Memory is enabled. The ALE strobe is used to latch the low-order address (8 bits) into an address latch during the first access cycle, and the AD0 - 7 pins are used for data during the second access cycle. |

### General-purpose Register File

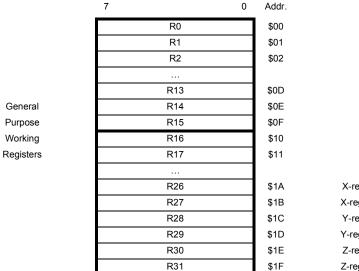

Figure 6 shows the structure of the 32 general-purpose working registers in the CPU.

### Figure 6. AVR CPU General-purpose Working Registers

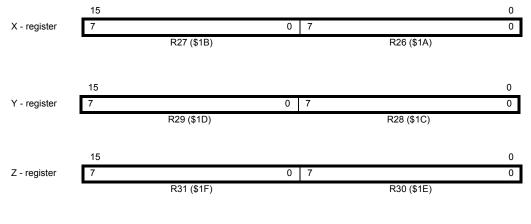

X-register low byte X-register high byte Y-register low byte Y-register high byte Z-register low byte Z-register high byte

All the register operating instructions in the instruction set have direct and single-cycle access to all registers. The only exception are the five constant arithmetic and logic instructions SBCI, SUBI, CPI, ANDI and ORI between a constant and a register and the LDI instruction for load immediate constant data. These instructions apply to the second half of the registers in the register file (R16..R31). The general SBC, SUB, CP, AND and OR and all other operations between two registers or on a single register apply to the entire register file.

As shown in Figure 6, each register is also assigned a data memory address, mapping them directly into the first 32 locations of the user Data Space. Although not being physically implemented as SRAM locations, this memory organization provides great flexibility in access of the registers, as the X-, Y- and Z-registers can be set to index any register in the file.

The registers R26..R31 have some added functions to their general-purpose usage. These registers are address pointers for indirect addressing of the Data Space. The three indirect address registers X, Y, and Z are defined as:

Figure 7. X-, Y-, and Z-registers

AT90S8515

X-register, Y-register and

**Z-register**

10

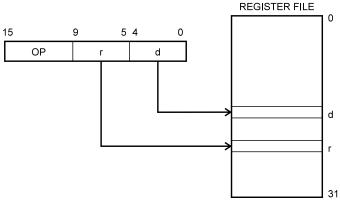

**Register Direct, Two Registers** Figure 10. Direct Register Addressing, Two Registers Rd and Rr

Operands are contained in register r (Rr) and d (Rd). The result is stored in register d (Rd).

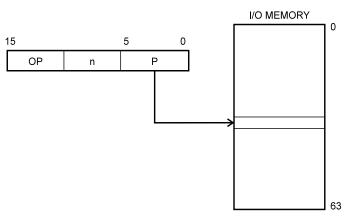

I/O Direct

### Figure 11. I/O Direct Addressing

Operand address is contained in six bits of the instruction word. n is the destination or source register address.

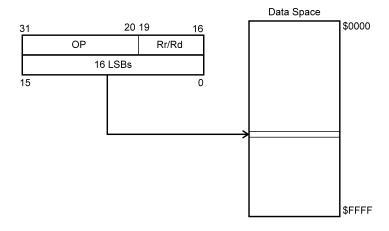

### Data Direct

Figure 12. Direct Data Addressing

The user can select the start-up time according to typical oscillator start-up. The number of WDT oscillator cycles used for each time-out is shown in Table 4. The frequency of the Watchdog Oscillator is voltage-dependent as shown in "Typical Characteristics" on page 95.

| Table 4. | Number of Watchdog Oscillator Cycles |  |

|----------|--------------------------------------|--|

|----------|--------------------------------------|--|

| FSTRT        | Time-out at V <sub>CC</sub> = 5V | Number of WDT Cycles |

|--------------|----------------------------------|----------------------|

| Programmed   | 0.28 ms                          | 256                  |

| Unprogrammed | 16.0 ms                          | 16K                  |

### **Power-on Reset**

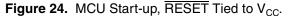

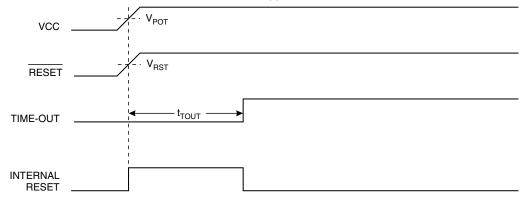

A Power-on Reset (POR) circuit ensures that the device is reset from power-on. As shown in Figure 23, an internal timer clocked from the Watchdog Timer oscillator prevents the MCU from starting until after a certain period after  $V_{CC}$  has reached the Power-on Threshold Voltage ( $V_{POT}$ ), regardless of the  $V_{CC}$  rise time (see Figure 24). The FSTRT Fuse bit in the Flash can be programmed to give a shorter start-up time if a certamic resonator or any other fast-start oscillator is used to clock the MCU.

If the built-in start-up delay is sufficient,  $\overline{\text{RESET}}$  can be connected to V<sub>CC</sub> directly or via an external pull-up resistor. By holding the pin low for a period after V<sub>CC</sub> has been applied, the Power-on Reset period can be extended. Refer to Figure 25 for a timing example of this.

### Figure 25. MCU Start-up, RESET Controlled Externally

interrupt. Some of the interrupt flags can also be cleared by writing a logical "1" to the flag bit position(s) to be cleared.

If an interrupt condition occurs when the corresponding interrupt enable bit is cleared (zero), the interrupt flag will be set and remembered until the interrupt is enabled or the flag is cleared by software.

If one or more interrupt conditions occur when the global interrupt enable bit is cleared (zero), the corresponding interrupt flag(s) will be set and remembered until the global interrupt enable bit is set (one) and will be executed by order of priority.

Note that external level interrupt does not have a flag and will only be remembered for as long as the interrupt condition is active.

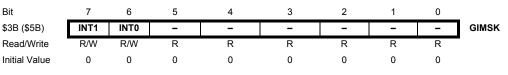

### General Interrupt Mask Register – GIMSK

### Bit 7 – INT1: External Interrupt Request 1 Enable

When the INT1 bit is set (one) and the I-bit in the Status Register (SREG) is set (one), the external pin interrupt is enabled. The Interrupt Sense Control1 bits 1/0 (ISC11 and ISC10) in the MCU general Control Register (MCUCR) define whether the external interrupt is activated on rising or falling edge of the INT1 pin or is level-sensed. Activity on the pin will cause an interrupt request even if INT1 is configured as an output. The corresponding interrupt of External Interrupt Request 1 is executed from program memory address \$002. See also "External Interrupts".

### • Bit 6 – INT0: External Interrupt Request 0 Enable

When the INT0 bit is set (one) and the I-bit in the Status Register (SREG) is set (one), the external pin interrupt is enabled. The Interrupt Sense Control0 bits 1/0 (ISC01 and ISC00) in the MCU general Control Register (MCUCR) define whether the external interrupt is activated on rising or falling edge of the INT0 pin or is level-sensed. Activity on the pin will cause an interrupt request even if INT0 is configured as an output. The corresponding interrupt of External Interrupt Request 0 is executed from program memory address \$001. See also "External Interrupts".

### • Bits 5..0 - Res: Reserved Bits

These bits are reserved bits in the AT90S8515 and always read as zero.

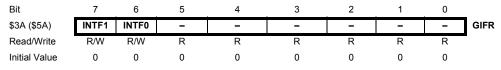

### General Interrupt Flag Register – GIFR

### • Bit 7 – INTF1: External Interrupt Flag1

When an edge on the INT1 pin triggers an interrupt request, the corresponding interrupt flag, INTF1 becomes set (one). If the I-bit in SREG and the corresponding interrupt enable bit, INT1 in GIMSK is set (one), the MCU will jump to the interrupt vector. The flag is cleared when the interrupt routine is executed. Alternatively, the flag can be cleared by writing a logical "1" to it. This flag is always cleared when INT1 is configured as level interrupt.

### Timer/Counter Interrupt Flag Register – TIFR

| Bit           | 7    | 6     | 5     | 4 | 3    | 2 | 1    | 0 | _    |

|---------------|------|-------|-------|---|------|---|------|---|------|

| \$38 (\$58)   | TOV1 | OCF1A | OCIFB | - | ICF1 | - | TOV0 | - | TIFR |

| Read/Write    | R/W  | R/W   | R/W   | R | R/W  | R | R/W  | R | -    |

| Initial Value | 0    | 0     | 0     | 0 | 0    | 0 | 0    | 0 |      |

### • Bit 7 – TOV1: Timer/Counter1 Overflow Flag

The TOV1 is set (one) when an overflow occurs in Timer/Counter1. TOV1 is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, TOV1 is cleared by writing a logical "1" to the flag. When the I-bit in SREG, TOIE1 (Timer/Counter1 Overflow Interrupt Enable) and TOV1 are set (one), the Timer/Counter1 Overflow interrupt is executed. In PWM mode, this bit is set when Timer/Counter1 changes counting direction at \$0000.

### • Bit 6 – OCF1A: Output Compare Flag 1A

The OCF1A bit is set (one) when compare match occurs between the Timer/Counter1 and the data in OCR1A (Output Compare Register 1A). OCF1A is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, OCF1A is cleared by writing a logical "1" to the flag. When the I-bit in SREG, OCIE1A (Timer/Counter1 Compare Match InterruptA Enable) and the OCF1A are set (one), the Timer/Counter1 CompareA Match interrupt is executed.

### • Bit 5 – OCF1B: Output Compare Flag 1B

The OCF1B bit is set (one) when compare match occurs between the Timer/Counter1 and the data in OCR1B (Output Compare Register 1B). OCF1B is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, OCF1B is cleared by writing a logical "1" to the flag. When the I-bit in SREG, OCIE1B (Timer/Counter1 Compare Match InterruptB Enable) and the OCF1B are set (one), the Timer/Counter1 CompareB Match interrupt is executed.

### • Bit 4 - Res: Reserved Bit

This bit is a reserved bit in the AT90S8515 and always reads zero.

### • Bit 3 – ICF1: Input Capture Flag 1

The ICF1 bit is set (one) to flag an input capture event, indicating that the Timer/Counter1 value has been transferred to the input capture register (ICR1). ICF1 is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, ICF1 is cleared by writing a logical "1" to the flag. When the SREG I-bit, TICIE1 (Timer/Counter1 Input Capture Interrupt Enable) and ICF1 are set (one), the Timer/Counter1 Capture interrupt is executed.

### • Bit 2 - Res: Reserved Bit

This bit is a reserved bit in the AT90S8515 and always reads zero.

### • Bit 1 – TOV: Timer/Counter0 Overflow Flag

The bit TOV0 is set (one) when an overflow occurs in Timer/Counter0. TOV0 is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, TOV0 is cleared by writing a logical "1" to the flag. When the SREG I-bit, TOIE0 (Timer/Counter0 Overflow Interrupt Enable) and TOV0 are set (one), the Timer/Counter0 Overflow interrupt is executed.

### • Bit 0 – Res: Reserved Bit

This bit is a reserved bit in the AT90S8515 and always reads zero.

# AT90S8515

# **External Interrupts** The external interrupts are triggered by the INT1 and INT0 pins. Observe that, if enabled, the interrupts will trigger even if the INT0/INT1 pins are configured as outputs. This feature provides a way of generating a software interrupt. The external interrupts can be triggered by a falling or rising edge or a low level. This is set up as indicated in the specification for the MCU Control Register (MCUCR). When the external interrupt is enabled and is configured as level-triggered, the interrupt will trigger as long as the pin is held low.

The external interrupts are set up as described in the specification for the MCU Control Register (MCUCR).

Interrupt Response Time The interrupt execution response for all the enabled AVR interrupts is four clock cycles minimum. Four clock cycles after the interrupt flag has been set, the program vector address for the actual interrupt handling routine is executed. During this 4-clock-cycle period, the Program Counter (2 bytes) is pushed onto the stack and the Stack Pointer is decremented by 2. The vector is normally a relative jump to the interrupt routine, and this jump takes two clock cycles. If an interrupt occurs during execution of a multi-cycle instruction, this instruction is completed before the interrupt is served.

A return from an interrupt handling routine (same as for a subroutine call routine) takes four clock cycles. During these four clock cycles, the Program Counter (2 bytes) is popped back from the stack, the Stack Pointer is incremented by 2 and the I-flag in SREG is set. When the AVR exits from an interrupt, it will always return to the main program and execute one more instruction before any pending interrupt is served.

Note that the Status Register (SREG) is not handled by the AVR hardware, for neither interrupts nor subroutines. For the interrupt handling routines requiring a storage of the SREG, this must be performed by user software.

For interrupts triggered by events that can remain static (e.g., the Output Compare Register1 A matching the value of Timer/Counter1), the interrupt flag is set when the event occurs. If the interrupt flag is cleared and the interrupt condition persists, the flag will not be set until the event occurs the next time. Note that an external level interrupt will only be remembered for as long as the interrupt condition is active.

### MCU Control Register – MCUCR

The MCU Control Register contains control bits for general MCU functions.

| Bit           | 7   | 6   | 5   | 4   | 3     | 2     | 1     | 0     |       |

|---------------|-----|-----|-----|-----|-------|-------|-------|-------|-------|

| \$35 (\$55)   | SRE | SRW | SE  | SM  | ISC11 | ISC10 | ISC01 | ISC00 | MCUCR |

| Read/Write    | R/W | R/W | R/W | R/W | R/W   | R/W   | R/W   | R/W   |       |

| Initial Value | 0   | 0   | 0   | 0   | 0     | 0     | 0     | 0     |       |

### • Bit 7 – SRE: External SRAM Enable

When the SRE bit is set (one), the external data SRAM is enabled and the pin functions AD0 - 7 (Port A), A8 - 15 (Port C),  $\overline{\text{WR}}$  and  $\overline{\text{RD}}$  (Port D) are activated as the alternate pin functions. Then the SRE bit overrides any pin direction settings in the respective data direction registers. See "SRAM Data Memory – Internal and External" on page 12 for a description of the external SRAM pin functions. When the SRE bit is cleared (zero), the external data SRAM is disabled and the normal pin and data direction settings are used.

### • Bit 6 – SRW: External SRAM Wait State

When the SRW bit is set (one), a one-cycle wait state is inserted in the external data SRAM access cycle. When the SRW bit is cleared (zero), the external data SRAM access is executed with the normal three-cycle scheme. See Figure 43 and Figure 44.

# <u>AIMEL</u>

### **Timer/Counters**

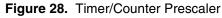

The AT90S8515 provides two general-purpose Timer/Counters – one 8-bit T/C and one 16-bit T/C. The Timer/Counters have individual prescaling selection from the same 10-bit prescaling timer. Both Timer/Counters can either be used as a timer with an internal clock time base or as a counter with an external pin connection that triggers the counting.

### Timer/Counter Prescaler

Figure 28 shows the general Timer/Counter prescaler.

The four different prescaled selections are: CK/8, CK/64, CK/256 and CK/1024, where CK is the oscillator clock. For the two Timer/Counters, added selections such as CK, external source and stop can be selected as clock sources.

### **8-bit Timer/Counter0** Figure 29 shows the block diagram for Timer/Counter0.

The 8-bit Timer/Counter0 can select clock source from CK, prescaled CK or an external pin. In addition, it can be stopped as described in the specification for the Timer/Counter0 Control Register (TCCR0). The overflow status flag is found in the Timer/Counter Insterrupt Flag Register (TIFR). Control signals are found in the Timer/Counter0 Control Register (TCCR0). The interrupt enable/disable settings for Timer/Counter0 are found in the Timer/Counter Insterrupt Kask Register (TIMSK).

When Timer/Counter0 is externally clocked, the external signal is synchronized with the oscillator frequency of the CPU. To assure proper sampling of the external clock, the minimum time between two external clock transitions must be at least one internal CPU clock period. The external clock signal is sampled on the rising edge of the internal CPU clock.

The 8-bit Timer/Counter0 features both a high-resolution and a high-accuracy usage with the lower prescaling opportunities. Similarly, the high prescaling opportunities make the Timer/Counter0 useful for lower speed functions or exact timing functions with infrequent actions.

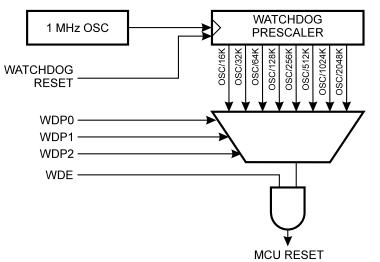

### Watchdog Timer

The Watchdog Timer is clocked from a separate On-chip oscillator that runs at 1 MHz. This is the typical value at  $V_{CC} = 5V$ . See characterization data for typical values at other  $V_{CC}$  levels. By controlling the Watchdog Timer prescaler, the Watchdog reset interval can be adjusted (see Table 14 for a detailed description). The WDR (Watchdog Reset) instruction resets the Watchdog Timer. Eight different clock cycle periods can be selected to determine the reset period. If the reset period expires without another Watchdog reset, the AT90S8515 resets and executes from the reset vector. For timing details on the Watchdog reset, refer to page 25.

To prevent unintentional disabling of the Watchdog, a special turn-off sequence must be followed when the Watchdog is disabled. Refer to the description of the Watchdog Timer Control Register for details.

### Figure 33. Watchdog Timer

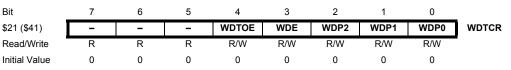

### Watchdog Timer Control Register – WDTCR

### • Bits 7..5 - Res: Reserved Bits

These bits are reserved bits in the AT90S8515 and will always read as zero.

### • Bit 4 – WDTOE: Watchdog Turn-off Enable

This bit must be set (one) when the WDE bit is cleared. Otherwise, the Watchdog will not be disabled. Once set, hardware will clear this bit to zero after four clock cycles. Refer to the description of the WDE bit for a Watchdog disable procedure.

### • Bit 3 – WDE: Watchdog Enable

When the WDE is set (one) the Watchdog Timer is enabled, and if the WDE is cleared (zero) the Watchdog Timer function is disabled. WDE can only be cleared if the WDTOE bit is set (one). To disable an enabled Watchdog Timer, the following procedure must be followed:

- 1. In the same operation, write a logical "1" to WDTOE and WDE. A logical "1" must be written to WDE even though it is set to one before the disable operation starts.

- 2. Within the next four clock cycles, write a logical "0" to WDE. This disables the Watchdog.

- Bits 2..0 WDP2, WDP1, WDP0: Watchdog Timer Prescaler 2, 1 and 0

The WDP2, WDP1 and WDP0 bits determine the Watchdog Timer prescaling when the Watchdog Timer is enabled. The different prescaling values and their corresponding Time-out periods are shown in Table 14.

| WDP2 | WDP1 | WDP0 | Number of WDT<br>Oscillator Cycles | Typical Time-out<br>at V <sub>CC</sub> = 3.0V | Typical Time-out<br>at V <sub>CC</sub> = 5.0V |

|------|------|------|------------------------------------|-----------------------------------------------|-----------------------------------------------|

| 0    | 0    | 0    | 16K cycles                         | 47.0 ms                                       | 15.0 ms                                       |

| 0    | 0    | 1    | 32K cycles                         | 94.0 ms                                       | 30.0 ms                                       |

| 0    | 1    | 0    | 64K cycles                         | 0.19 s                                        | 60.0 ms                                       |

| 0    | 1    | 1    | 128K cycles                        | 0.38 s                                        | 0.12 s                                        |

| 1    | 0    | 0    | 256K cycles                        | 0.75 s                                        | 0.24 s                                        |

| 1    | 0    | 1    | 512K cycles                        | 1.5 s                                         | 0.49 s                                        |

| 1    | 1    | 0    | 1,024K cycles                      | 3.0 s                                         | 0.97 s                                        |

| 1    | 1    | 1    | 2,048K cycles                      | 6.0 s                                         | 1.9 s                                         |

| Table 14. | Watchdog | Timer Pre | scale Select |

|-----------|----------|-----------|--------------|

|-----------|----------|-----------|--------------|

Note: The frequency of the Watchdog oscillator is voltage-dependent as shown in the Electrical Characteristics section.

The WDR (Watchdog Reset) instruction should always be executed before the Watchdog Timer is enabled. This ensures that the reset period will be in accordance with the Watchdog Timer prescale settings. If the Watchdog Timer is enabled without reset, the Watchdog Timer may not start to count from zero.

To avoid unintentional MCU reset, the Watchdog Timer should be disabled or reset before changing the Watchdog Timer Prescale Select.

pins are inputs. When  $\overline{SS}$  is driven high, all pins are inputs and the SPI is passive, which means that it will not receive incoming data. Note that the SPI logic will be reset once the  $\overline{SS}$  pin is brought high. If the  $\overline{SS}$  pin is brought high during a transmission, the SPI will stop sending and receiving immediately and both data received and data sent must be considered as lost.

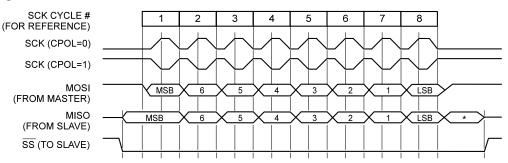

### **Data Modes**

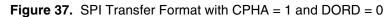

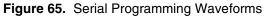

There are four combinations of SCK phase and polarity with respect to serial data, which are determined by control bits CPHA and CPOL. The SPI data transfer formats are shown in Figure 36 and Figure 37.

\* Not defined but normally MSB of character just received

\* Not defined but normally LSB of previously transmitted character

### **SPI Control Register – SPCR**

| Bit           | 7    | 6   | 5    | 4    | 3    | 2    | 1    | 0    | _    |

|---------------|------|-----|------|------|------|------|------|------|------|

| \$0D (\$2D)   | SPIE | SPE | DORD | MSTR | CPOL | CPHA | SPR1 | SPR0 | SPCR |

| Read/Write    | R/W  | R/W | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | -    |

| Initial Value | 0    | 0   | 0    | 0    | 0    | 0    | 0    | 0    |      |

• Bit 7 – SPIE: SPI Interrupt Enable

This bit causes the SPI interrupt to be executed if SPIF bit in the SPSR register is set and the global interrupts are enabled.

### Bit 6 – SPE: SPI Enable

When the SPE bit is set (one), the SPI is enabled. This bit must be set to enable any SPI operations.

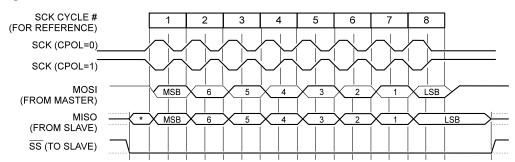

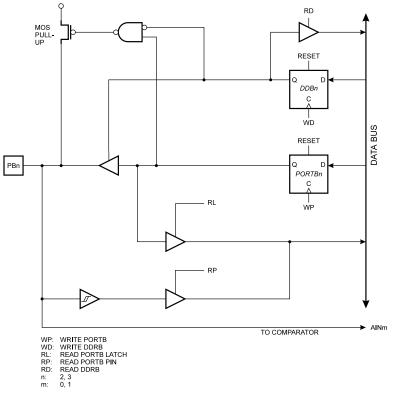

Figure 47. Port B Schematic Diagram (Pins PB2 and PB3)

Figure 48. Port B Schematic Diagram (Pin PB4)

### • INT1 - Port D, Bit 3

INT1: External Interrupt source 1. The PD3 pin can serve as an external interrupt source to the MCU. See the interrupt description for further details and how to enable the source.

• INT0 - Port D, Bit 2

INT0: External Interrupt source 0. The PD2 pin can serve as an external interrupt source to the MCU. See the interrupt description for further details and how to enable the source.

### • TXD – Port D, Bit 1

Transmit Data (data output pin for the UART). When the UART transmitter is enabled, this pin is configured as an output, regardless of the value of DDRD1.

### • RXD - Port D, Bit 0

Receive Data (data input pin for the UART). When the UART receiver is enabled, this pin is configured as an input, regardless of the value of DDRD0. When the UART forces this pin to be an input, a logical "1" in PORTD0 will turn on the internal pull-up.

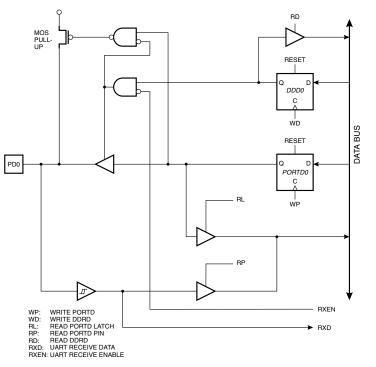

**Port D Schematics** Note that all port pins are synchronized. The synchronization latches are, however, not shown in the figures.

### Figure 53. Port D Schematic Diagram (Pin PD0)

### Table 32. Serial Programming Instruction Set

|                      |                   | Instructio         | on Format         |           |                                                                                                    |

|----------------------|-------------------|--------------------|-------------------|-----------|----------------------------------------------------------------------------------------------------|

| Instruction          | Byte 1            | Byte 2             | Byte 3            | Byte4     | Operation                                                                                          |

| Programming Enable   | 1010 1100         | 0101 0011          | XXXX XXXX         | XXXX XXXX | Enable serial programming while RESET is low.                                                      |

| Chip Erase           | 1010 1100         | 100x xxxx          | xxxx xxxx         | xxxx xxxx | Chip Erase Flash and EEPROM memory arrays.                                                         |

| Read Program Memory  | 0010 <b>H</b> 000 | xxxx <b>aaaa</b>   | bbbb bbbb         | 0000 0000 | Read <b>H</b> (high or low) data <b>o</b> from program memory at word address <b>a:b</b> .         |

| Write Program Memory | 0100 <b>H</b> 000 | xxxx <b>aaaa</b>   | bbbb bbbb         | iiii iiii | Write <b>H</b> (high or low) data <b>i</b> to program memory at word address <b>a</b> : <b>b</b> . |

| Read EEPROM Memory   | 1010 0000         | xxxx xxx <b>a</b>  | bbbb bbbb         | 0000 0000 | Read data o from EEPROM memory at address a:b.                                                     |

| Write EEPROM Memory  | 1100 0000         | XXXX XXX <b>a</b>  | bbbb bbbb         | 1111 1111 | Write data i to EEPROM memory at address a:b.                                                      |

| Write Lock Bits      | 1010 1100         | 111x x <b>21</b> x | xxxx xxxx         | xxxx xxxx | Write Lock bits. Set bits <b>1,2</b> = "0" to program Lock bits.                                   |

| Read Signature Bytes | 0011 0000         | xxxx xxxx          | xxxx xx <b>bb</b> | 0000 0000 | Read signature byte <b>o</b> at address <b>b</b> . <sup>(1)</sup>                                  |

**a** = address high bits

**b** = address low bits

$\mathbf{H} = 0 - \text{Low byte}, 1 - \text{High Byte}$

- $\mathbf{o} = data out$

- i = data in

- x = don't care

- 1 = Lock bit 1

- **2** = Lock bit 2

# AT90S8515

- Notes: 1. "Max" means the highest value where the pin is guaranteed to be read as low.

- 2. "Min" means the lowest value where the pin is guaranteed to be read as high.

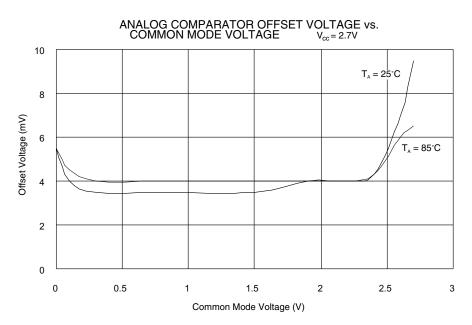

- Although each I/O port can sink more than the test conditions (20 mA at V<sub>CC</sub> = 5V, 10 mA at V<sub>CC</sub> = 3V) under steady state conditions (non-transient), the following must be observed:

- 1] The sum of all  $\mathrm{I}_{\mathrm{OL}},$  for all ports, should not exceed 200 mA.

- 2] The sum of all  $\rm I_{OL},$  for ports B0 B7, D0 D7 and XTAL2, should not exceed 100 mA.

- 3] The sum of all I<sub>OL</sub>, for ports A0 A7, ALE, OC1B and C0 C7 should not exceed 100 mA.

If  $I_{OL}$  exceeds the test condition,  $V_{OL}$  may exceed the related specification. Pins are not guaranteed to sink current greater than the listed test condition.

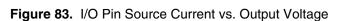

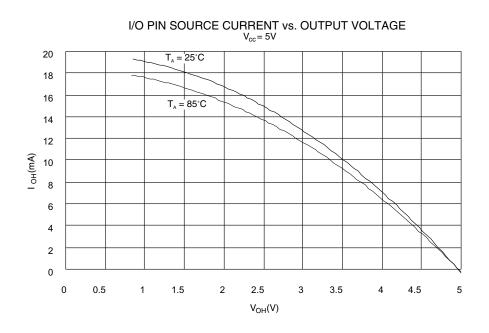

- Although each I/O port can source more than the test conditions (3 mA at V<sub>CC</sub> = 5V, 1.5 mA at V<sub>CC</sub> = 3V) under steady state conditions (non-transient), the following must be observed:

- 1] The sum of all  $I_{OH}$ , for all ports, should not exceed 200 mA.

- 2] The sum of all  $\rm I_{OH},$  for ports B0 B7, D0 D7 and XTAL2, should not exceed 100 mA.

3] The sum of all  $I_{OH}$ , for ports A0 - A7, ALE, OC1B and C0 - C7 should not exceed 100 mA.

If  $I_{OH}$  exceeds the test condition,  $V_{OH}$  may exceed the related specification. Pins are not guaranteed to source current greater than the listed test condition.

5. Minimum  $V_{CC}$  for power-down is 2V.

|    |                      |                                                        | 4 MHz O | scillator | Variable                                    | Oscillator                   |      |

|----|----------------------|--------------------------------------------------------|---------|-----------|---------------------------------------------|------------------------------|------|

|    | Symbol               | Parameter                                              | Min     | Мах       | Min                                         | Max                          | Unit |

| 0  | 1/t <sub>CLCL</sub>  | Oscillator Frequency                                   |         |           | 0.0                                         | 4.0                          | MHz  |

| 1  | t <sub>LHLL</sub>    | ALE Pulse Width                                        | 70.0    |           | 0.5 t <sub>CLCL</sub> - 55.0 <sup>(1)</sup> |                              | ns   |

| 2  | t <sub>AVLL</sub>    | Address Valid A to ALE Low                             | 60.0    |           | 0.5 t <sub>CLCL</sub> - 65.0 <sup>(1)</sup> |                              | ns   |

| За | t <sub>LLAX_ST</sub> | Address Hold after ALE Low,<br>ST/STD/STS Instructions | 130.0   |           | 0.5 t <sub>CLCL</sub> + 5.0 <sup>(2)</sup>  |                              | ns   |

| 3b | t <sub>LLAX_LD</sub> | Address Hold after ALE Low,<br>LD/LDD/LDS Instructions | 15.0    |           | 15.0                                        |                              | ns   |

| 4  | t <sub>AVLLC</sub>   | Address Valid C to ALE Low                             | 60.0    |           | 0.5 t <sub>CLCL</sub> - 65.0 <sup>(1)</sup> |                              | ns   |

| 5  | t <sub>AVRL</sub>    | Address Valid to RD Low                                | 200.0   |           | 1.0 t <sub>CLCL</sub> - 50.0                |                              | ns   |

| 6  | t <sub>AVWL</sub>    | Address Valid to WR Low                                | 325.0   |           | 1.5 t <sub>CLCL</sub> - 50.0 <sup>(1)</sup> |                              | ns   |

| 7  | t <sub>LLWL</sub>    | ALE Low to WR Low                                      | 230.0   | 270.0     | 1.0 t <sub>CLCL</sub> - 20.0                | 1.0 t <sub>CLCL</sub> + 20.0 | ns   |

| 8  | t <sub>LLRL</sub>    | ALE Low to RD Low                                      | 105.0   | 145.0     | 0.5 t <sub>CLCL</sub> - 20.0 <sup>(2)</sup> | $0.5 t_{CLCL} + 20.0^{(2)}$  | ns   |

| 9  | t <sub>DVRH</sub>    | Data Setup to RD High                                  | 95.0    |           | 95.0                                        |                              | ns   |

| 10 | t <sub>RLDV</sub>    | Read Low to Data Valid                                 |         | 170.0     |                                             | 1.0 t <sub>CLCL</sub> - 80.0 | ns   |

| 11 | t <sub>RHDX</sub>    | Data Hold after RD High                                | 0.0     |           | 0.0                                         |                              | ns   |

| 12 | t <sub>RLRH</sub>    | RD Pulse Width                                         | 230.0   |           | 1.0 t <sub>CLCL</sub> - 20.0                |                              | ns   |

| 13 | t <sub>DVWL</sub>    | Data Setup to WR Low                                   | 70.0    |           | 0.5 t <sub>CLCL</sub> - 55.0 <sup>(1)</sup> |                              | ns   |

| 14 | t <sub>WHDX</sub>    | Data Hold after WR High                                | 0.0     |           | 0.0                                         |                              | ns   |

| 15 | t <sub>DVWH</sub>    | Data Valid to WR High                                  | 210.0   |           | 1.0 t <sub>CLCL</sub> - 40.0                |                              | ns   |

| 16 | t <sub>wLWH</sub>    | WR Pulse Width                                         | 105.0   |           | 0.5 t <sub>CLCL</sub> - 20.0 <sup>(2)</sup> |                              | ns   |

### Table 39. External Data Memory Characteristics, 2.7V - 4.0V, No Wait State

### Table 40. External Data Memory Characteristics, 2.7V - 4.0V, One Cycle Wait State

|                     |                                                                                    | 4 MHz O                                                                                                                                                          | scillator                                                                                                                                                                                                                             | Variable (                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------------|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol              | Parameter                                                                          | Min                                                                                                                                                              | Max                                                                                                                                                                                                                                   | Min                                                                                                                                                                      | Max                                                                                                                                                                                                                                                                                                                                                                                | Unit                                                                                                                                                                                                                                                                                                                                                                                         |

| 1/t <sub>CLCL</sub> | Oscillator Frequency                                                               |                                                                                                                                                                  |                                                                                                                                                                                                                                       | 0.0                                                                                                                                                                      | 4.0                                                                                                                                                                                                                                                                                                                                                                                | MHz                                                                                                                                                                                                                                                                                                                                                                                          |

| t <sub>RLDV</sub>   | Read Low to Data Valid                                                             |                                                                                                                                                                  | 420.00                                                                                                                                                                                                                                |                                                                                                                                                                          | 2.0 t <sub>CLCL</sub> - 80.0                                                                                                                                                                                                                                                                                                                                                       | ns                                                                                                                                                                                                                                                                                                                                                                                           |

| t <sub>RLRH</sub>   | RD Pulse Width                                                                     | 480.0                                                                                                                                                            |                                                                                                                                                                                                                                       | 2.0 t <sub>CLCL</sub> - 20.0                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                    | ns                                                                                                                                                                                                                                                                                                                                                                                           |

| t <sub>DVWH</sub>   | Data Valid to WR High                                                              | 460.0                                                                                                                                                            |                                                                                                                                                                                                                                       | 2.0 t <sub>CLCL</sub> - 40.0                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                    | ns                                                                                                                                                                                                                                                                                                                                                                                           |

| t <sub>wLWH</sub>   | WR Pulse Width                                                                     | 355.0                                                                                                                                                            |                                                                                                                                                                                                                                       | 1.5 t <sub>CLCL</sub> - 20.0 <sup>(2)</sup>                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                    | ns                                                                                                                                                                                                                                                                                                                                                                                           |

|                     | 1/t <sub>CLCL</sub><br>t <sub>RLDV</sub><br>t <sub>RLRH</sub><br>t <sub>DVWH</sub> | 1/t <sub>CLCL</sub> Oscillator Frequency   t <sub>RLDV</sub> Read Low to Data Valid   t <sub>RLRH</sub> RD Pulse Width   t <sub>DVWH</sub> Data Valid to WR High | Symbol     Parameter     Min       1/t <sub>CLCL</sub> Oscillator Frequency        t <sub>RLDV</sub> Read Low to Data Valid        t <sub>RLRH</sub> RD Pulse Width     480.0       t <sub>DVWH</sub> Data Valid to WR High     460.0 | 1/t <sub>CLCL</sub> Oscillator Frequency   t <sub>RLDV</sub> Read Low to Data Valid   t <sub>RLRH</sub> RD Pulse Width   t <sub>DVWH</sub> Data Valid to WR High   460.0 | Symbol     Parameter     Min     Max     Min       1/t <sub>CLCL</sub> Oscillator Frequency      0.0     0.0       t <sub>RLDV</sub> Read Low to Data Valid     420.00     2.0 t <sub>CLCL</sub> - 20.0       t <sub>RLRH</sub> RD Pulse Width     480.0     2.0 t <sub>CLCL</sub> - 20.0       t <sub>DVWH</sub> Data Valid to WR High     460.0     2.0 t <sub>CLCL</sub> - 40.0 | Symbol     Parameter     Min     Max     Min     Max       1/t <sub>CLCL</sub> Oscillator Frequency      0.0     4.0       1/t <sub>CLCL</sub> Read Low to Data Valid     420.00     2.0 t <sub>CLCL</sub> - 80.0       t <sub>RLDP</sub> RD Pulse Width     480.0     2.0 t <sub>CLCL</sub> - 20.0       t <sub>DVWH</sub> Data Valid to WR High     460.0     2.0 t <sub>CLCL</sub> - 40.0 |

1. This assumes 50% clock duty cycle. The half-period is actually the high time of the external clock, XTAL1.

2. This assumes 50% clock duty cycle. The half-period is actually the low time of the external clock, XTAL1.

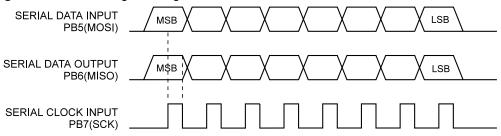

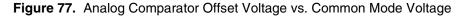

Analog Comparator offset voltage is measured as absolute offset.

Figure 76. Analog Comparator Offset Voltage vs. Common Mode Voltage

## **Instruction Set Summary**

| Mnemonic     | Operands        | Description                            | Operation                                             | Flags     | # Clocks   |

|--------------|-----------------|----------------------------------------|-------------------------------------------------------|-----------|------------|

| ARITHMETIC A | ND LOGIC INSTRU | ICTIONS                                |                                                       | •         | _ <b>-</b> |

| ADD          | Rd, Rr          | Add Two Registers                      | $Rd \leftarrow Rd + Rr$                               | Z,C,N,V,H | 1          |

| ADC          | Rd, Rr          | Add with Carry Two Registers           | $Rd \leftarrow Rd + Rr + C$                           | Z,C,N,V,H | 1          |

| ADIW         | Rdl, K          | Add Immediate to Word                  | Rdh:RdI ← Rdh:RdI + K                                 | Z,C,N,V,S | 2          |

| SUB          | Rd, Rr          | Subtract Two Registers                 | $Rd \leftarrow Rd - Rr$                               | Z,C,N,V,H | 1          |

| SUBI         | Rd, K           | Subtract Constant from Register        | $Rd \leftarrow Rd - K$                                | Z,C,N,V,H | 1          |

| SBC          | Rd, Rr          | Subtract with Carry Two Registers      | $Rd \leftarrow Rd - Rr - C$                           | Z,C,N,V,H | 1          |

| SBCI         | Rd, K           | Subtract with Carry Constant from Reg. | $Rd \leftarrow Rd - K - C$                            | Z,C,N,V,H | 1          |

| SBIW         | Rdl, K          | Subtract Immediate from Word           | Rdh:RdI ← Rdh:RdI - K                                 | Z,C,N,V,S | 2          |

| AND          | Rd, Rr          | Logical AND Registers                  | $Rd \leftarrow Rd \bullet Rr$                         | Z,N,V     | 1          |

| ANDI         | Rd, K           | Logical AND Register and Constant      | $Rd \leftarrow Rd ullet K$                            | Z,N,V     | 1          |

| OR           | Rd, Rr          | Logical OR Registers                   | $Rd \leftarrow Rd \lor Rr$                            | Z,N,V     | 1          |

| ORI          | Rd, K           | Logical OR Register and Constant       | $Rd \leftarrow Rd \lor K$                             | Z,N,V     | 1          |

| EOR          | Rd, Rr          | Exclusive OR Registers                 | $Rd \leftarrow Rd \oplus Rr$                          | Z,N,V     | 1          |

| COM          | Rd              | One's Complement                       | $Rd \leftarrow \$FF - Rd$                             | Z,C,N,V   | 1          |

| NEG          | Rd              | Two's Complement                       | Rd ← \$00 - Rd                                        | Z,C,N,V,H | 1          |

| SBR          | Rd, K           | Set Bit(s) in Register                 | $Rd \leftarrow Rd \lor K$                             | Z,N,V     | 1          |

| CBR          | Rd, K           | Clear Bit(s) in Register               | $Rd \leftarrow Rd \bullet (\$FF - K)$                 | Z,N,V     | 1          |

| INC          | Rd              | Increment                              | $Rd \leftarrow Rd + 1$                                | Z,N,V     | 1          |

| DEC          | Rd              | Decrement                              | $Rd \leftarrow Rd$ - 1                                | Z,N,V     | 1          |

| TST          | Rd              | Test for Zero or Minus                 | $Rd \leftarrow Rd \bullet Rd$                         | Z,N,V     | 1          |

| CLR          | Rd              | Clear Register                         | $Rd \leftarrow Rd \oplus Rd$                          | Z,N,V     | 1          |

| SER          | Rd              | Set Register                           | $Rd \leftarrow FF$                                    | None      | 1          |

| BRANCH INSTR |                 |                                        |                                                       |           |            |

| RJMP         | k               | Relative Jump                          | $PC \leftarrow PC + k + 1$                            | None      | 2          |

| IJMP         |                 | Indirect Jump to (Z)                   | $PC \leftarrow Z$                                     | None      | 2          |

| RCALL        | k               | Relative Subroutine Call               | $PC \leftarrow PC + k + 1$                            | None      | 3          |

| ICALL        |                 | Indirect Call to (Z)                   | $PC \leftarrow Z$                                     | None      | 3          |

| RET          |                 | Subroutine Return                      | $PC \leftarrow STACK$                                 | None      | 4          |

| RETI         |                 | Interrupt Return                       | PC ← STACK                                            | 1         | 4          |

| CPSE         | Rd, Rr          | Compare, Skip if Equal                 | if (Rd = Rr) PC $\leftarrow$ PC + 2 or 3              | None      | 1/2/3      |

| CP           | Rd, Rr          | Compare                                | Rd - Rr                                               | Z,N,V,C,H | 1          |

| CPC          | Rd, Rr          | Compare with Carry                     | Rd - Rr - C                                           | Z,N,V,C,H | 1          |

| CPI          | Rd, K           | Compare Register with Immediate        | Rd - K                                                | Z,N,V,C,H | 1          |

| SBRC         | Rr, b           | Skip if Bit in Register Cleared        | if (Rr(b) = 0) PC $\leftarrow$ PC + 2 or 3            | None      | 1/2/3      |

| SBRS         | Rr, b           | Skip if Bit in Register is Set         | if $(Rr(b) = 1) PC \leftarrow PC + 2 \text{ or } 3$   | None      | 1/2/3      |

| SBIC         | P, b            | Skip if Bit in I/O Register Cleared    | if $(P(b) = 0) PC \leftarrow PC + 2 \text{ or } 3$    | None      | 1/2/3      |

| SBIS         | P, b            | Skip if Bit in I/O Register is Set     | if (P(b) = 1) PC $\leftarrow$ PC + 2 or 3             | None      | 1/2/3      |

| BRBS         | s, k            | Branch if Status Flag Set              | if (SREG(s) = 1) then PC $\leftarrow$ PC + k + 1      | None      | 1/2        |

| BRBC         | s, k            | Branch if Status Flag Cleared          | if (SREG(s) = 0) then PC $\leftarrow$ PC + k + 1      | None      | 1/2        |

| BREQ         | k               | Branch if Equal                        | if (Z = 1) then PC $\leftarrow$ PC + k + 1            | None      | 1/2        |

| BRNE         | k               | Branch if Not Equal                    | if (Z = 0) then PC $\leftarrow$ PC + k + 1            | None      | 1/2        |

| BRCS         | k               | Branch if Carry Set                    | if (C = 1) then PC $\leftarrow$ PC + k + 1            | None      | 1/2        |

| BRCC         | k               | Branch if Carry Cleared                | if (C = 0) then PC $\leftarrow$ PC + k + 1            | None      | 1/2        |

| BRSH         | k               | Branch if Same or Higher               | if (C = 0) then PC $\leftarrow$ PC + k + 1            | None      | 1/2        |

| BRLO         | k               | Branch if Lower                        | if (C = 1) then PC $\leftarrow$ PC + k + 1            | None      | 1/2        |

| BRMI         | k               | Branch if Minus                        | if (N = 1) then PC $\leftarrow$ PC + k + 1            | None      | 1/2        |

| BRPL         | k               | Branch if Plus                         | if (N = 0) then PC $\leftarrow$ PC + k + 1            | None      | 1/2        |

| BRGE         | k               | Branch if Greater or Equal, Signed     | if $(N \oplus V = 0)$ then PC $\leftarrow$ PC + k + 1 | None      | 1/2        |

| BRLT         | k               | Branch if Less Than Zero, Signed       | if $(N \oplus V = 1)$ then PC $\leftarrow$ PC + k + 1 | None      | 1/2        |

| BRHS         | k               | Branch if Half-carry Flag Set          | if (H = 1) then PC $\leftarrow$ PC + k + 1            | None      | 1/2        |

| BRHC         | k               | Branch if Half-carry Flag Cleared      | if (H = 0) then PC $\leftarrow$ PC + k + 1            | None      | 1/2        |

| BRTS         | k               | Branch if T-flag Set                   | if (T = 1) then PC $\leftarrow$ PC + k + 1            | None      | 1/2        |

| BRTC         | k               | Branch if T-flag Cleared               | if (T = 0) then PC $\leftarrow$ PC + k + 1            | None      | 1/2        |

| BRVS         | k               | Branch if Overflow Flag is Set         | if $(V = 1)$ then PC $\leftarrow$ PC + k + 1          | None      | 1/2        |

| BRVC         | k               | Branch if Overflow Flag is Cleared     | if $(V = 0)$ then PC $\leftarrow$ PC + k + 1          | None      | 1/2        |

| BRIE         | k               | Branch if Interrupt Enabled            | if (I = 1) then PC $\leftarrow$ PC + k + 1            | None      | 1/2        |

| BRID         | k               | Branch if Interrupt Disabled           | if (I = 0) then PC $\leftarrow$ PC + k + 1            | None      | 1/2        |

## AT90S8515 Ordering Information

| Speed (MHz) | Power Supply | Ordering Code | Package | Operation Range |

|-------------|--------------|---------------|---------|-----------------|

| 4           | 2.7V - 6.0V  | AT90S8515-4AC | 44A     | Commercial      |

|             |              | AT90S8515-4JC | 44J     | (0°C to 70°C)   |

|             |              | AT90S8515-4PC | 40P6    |                 |

|             |              | AT90S8515-4AI | 44A     | Industrial      |

|             |              | AT90S8515-4JI | 44J     | (-40°C to 85°C) |

|             |              | AT90S8515-4PI | 40P6    |                 |

| 8           | 4.0V - 6.0V  | AT90S8515-8AC | 44A     | Commercial      |

|             |              | AT90S8515-8JC | 44J     | (0°C to 70°C)   |

|             |              | AT90S8515-8PC | 40P6    |                 |

|             |              | AT90S8515-8AI | 44A     | Industrial      |

|             |              | AT90S8515-8JI | 44J     | (-40°C to 85°C) |

|             |              | AT90S8515-8PI | 40P6    |                 |

Note: Order AT90S8515A-XXX for devices with the FSTRT Fuse programmed.

| Package Type |                                                                   |  |  |  |

|--------------|-------------------------------------------------------------------|--|--|--|

| 44 <b>A</b>  | 44-lead, Thin (1.0 mm) Plastic Gull Wing Quad Flat Package (TQFP) |  |  |  |

| 44J          | 44-lead, Plastic J-leaded Chip Carrier (PLCC)                     |  |  |  |

| 40P6         | 40-lead, 0.600" Wide, Plastic Dual Inline Package (PDIP)          |  |  |  |

# 108 AT90S8515