Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                 |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | AVR                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 8MHz                                                                     |

| Connectivity               | SPI, UART/USART                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 32                                                                       |

| Program Memory Size        | 8KB (4K x 16)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 512 x 8                                                                  |

| RAM Size                   | 512 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                  |

| Data Converters            | -                                                                        |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C                                                             |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                 |

| Supplier Device Package    | 40-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at90s8515a-8pi |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

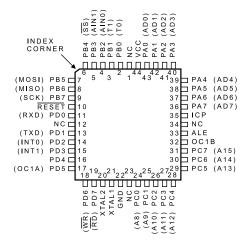

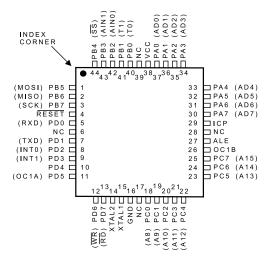

## **Pin Configurations**

PDIP

PLCC

# AT90S8515

d

31

|                                        | two additional clock cycles is used per byte. This has the following effect: Data transfer instructions take two extra clock cycles, whereas interrupt, subroutine calls and returns will need four clock cycles more than specified in the instruction set manual.                                                                                                                                                                    |

|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                        | The five different addressing modes for the data memory cover: Direct, Indirect with Displacement, Indirect, Indirect with Pre-decrement and Indirect with Post-increment. In the register file, registers R26 to R31 feature the indirect addressing pointer registers.                                                                                                                                                               |

|                                        | The direct addressing reaches the entire data space.                                                                                                                                                                                                                                                                                                                                                                                   |

|                                        | The Indirect with Displacement mode features 63 address locations reached from the base address given by the Y- or Z-register.                                                                                                                                                                                                                                                                                                         |

|                                        | When using register indirect addressing modes with automatic pre-decrement and post-<br>increment, the address registers X, Y and Z are decremented and incremented.                                                                                                                                                                                                                                                                   |

|                                        | The 32 general-purpose working registers, 64 I/O registers, the 512 bytes of internal data SRAM, and the 64K bytes of optional external data SRAM in the AT90S8515 are all accessible through all these addressing modes.                                                                                                                                                                                                              |

|                                        | See the next section for a detailed description of the different addressing modes.                                                                                                                                                                                                                                                                                                                                                     |

| Program and Data<br>Addressing Modes   | The AT90S8515 AVR RISC microcontroller supports powerful and efficient addressing modes for access to the program memory (Flash) and data memory (SRAM, Register file and I/O memory). This section describes the different addressing modes supported by the AVR architecture. In the figures, OP means the operation code part of the instruction word. To simplify, not all figures show the exact location of the addressing bits. |

| Register Direct, Single<br>Register RD | Figure 9. Direct Single Register Addressing                                                                                                                                                                                                                                                                                                                                                                                            |

|                                        | 15 4 0<br>OP d                                                                                                                                                                                                                                                                                                                                                                                                                         |

The operand is contained in register d (Rd).

| Address Hex | Name | Function                                      |  |

|-------------|------|-----------------------------------------------|--|

| \$11 (\$31) | DDRD | Data Direction Register, Port D               |  |

| \$10 (\$30) | PIND | Input Pins, Port D                            |  |

| \$0F (\$2F) | SPDR | SPI I/O Data Register                         |  |

| \$0E (\$2E) | SPSR | SPI Status Register                           |  |

| \$0D (\$2D) | SPCR | SPI Control Register                          |  |

| \$0C (\$2C) | UDR  | UART I/O Data Register                        |  |

| \$0B (\$2B) | USR  | UART Status Register                          |  |

| \$0A (\$2A) | UCR  | UART Control Register                         |  |

| \$09 (\$29) | UBRR | UART Baud Rate Register                       |  |

| \$08 (\$28) | ACSR | Analog Comparator Control and Status Register |  |

| Table 1. AT90S8515 I/O Space (Continu |

|---------------------------------------|

|---------------------------------------|

Note: Reserved and unused locations are not shown in the table.

All AT90S8515 I/Os and peripherals are placed in the I/O space. The I/O locations are accessed by the IN and OUT instructions transferring data between the 32 general-purpose working registers and the I/O space. I/O registers within the address range \$00 - \$1F are directly bit-accessible using the SBI and CBI instructions. In these registers, the value of single bits can be checked by using the SBIS and SBIC instructions. Refer to the instruction set section for more details. When using the I/O-specific commands IN and OUT, the I/O addresses \$00 - \$3F must be used. When addressing I/O registers as SRAM, \$20 must be added to this address. All I/O register addresses throughout this document are shown with the SRAM address in parentheses.

For compatibility with future devices, reserved bits should be written to zero if accessed. Reserved I/O memory addresses should never be written.

Some of the status flags are cleared by writing a logical "1" to them. Note that the CBI and SBI instructions will operate on all bits in the I/O register, writing a "1" back into any flag read as set, thus clearing the flag. The CBI and SBI instructions work with registers \$00 to \$1F only.

The I/O and peripherals control registers are explained in the following sections.

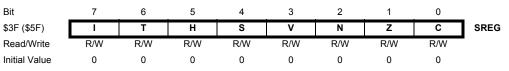

#### Status Register – SREG

The AVR status register (SREG) at I/O space location \$3F (\$5F) is defined as:

#### • Bit 7 – I: Global Interrupt Enable

The global interrupt enable bit must be set (one) for the interrupts to be enabled. The individual interrupt enable control is then performed in separate control registers. If the global interrupt enable bit is cleared (zero), none of the interrupts are enabled independent of the individual interrupt enable settings. The I-bit is cleared by hardware after an interrupt has occurred and is set by the RETI instruction to enable subsequent interrupts.

#### • Bit 6 – T: Bit Copy Storage

The bit copy instructions BLD (Bit LoaD) and BST (Bit STore) use the T-bit as source and destination for the operated bit. A bit from a register in the register file can be copied

# AT90S8515

# **External Interrupts** The external interrupts are triggered by the INT1 and INT0 pins. Observe that, if enabled, the interrupts will trigger even if the INT0/INT1 pins are configured as outputs. This feature provides a way of generating a software interrupt. The external interrupts can be triggered by a falling or rising edge or a low level. This is set up as indicated in the specification for the MCU Control Register (MCUCR). When the external interrupt is enabled and is configured as level-triggered, the interrupt will trigger as long as the pin is held low.

The external interrupts are set up as described in the specification for the MCU Control Register (MCUCR).

Interrupt Response Time The interrupt execution response for all the enabled AVR interrupts is four clock cycles minimum. Four clock cycles after the interrupt flag has been set, the program vector address for the actual interrupt handling routine is executed. During this 4-clock-cycle period, the Program Counter (2 bytes) is pushed onto the stack and the Stack Pointer is decremented by 2. The vector is normally a relative jump to the interrupt routine, and this jump takes two clock cycles. If an interrupt occurs during execution of a multi-cycle instruction, this instruction is completed before the interrupt is served.

A return from an interrupt handling routine (same as for a subroutine call routine) takes four clock cycles. During these four clock cycles, the Program Counter (2 bytes) is popped back from the stack, the Stack Pointer is incremented by 2 and the I-flag in SREG is set. When the AVR exits from an interrupt, it will always return to the main program and execute one more instruction before any pending interrupt is served.

Note that the Status Register (SREG) is not handled by the AVR hardware, for neither interrupts nor subroutines. For the interrupt handling routines requiring a storage of the SREG, this must be performed by user software.

For interrupts triggered by events that can remain static (e.g., the Output Compare Register1 A matching the value of Timer/Counter1), the interrupt flag is set when the event occurs. If the interrupt flag is cleared and the interrupt condition persists, the flag will not be set until the event occurs the next time. Note that an external level interrupt will only be remembered for as long as the interrupt condition is active.

#### MCU Control Register – MCUCR

The MCU Control Register contains control bits for general MCU functions.

| Bit           | 7   | 6   | 5   | 4   | 3     | 2     | 1     | 0     |       |

|---------------|-----|-----|-----|-----|-------|-------|-------|-------|-------|

| \$35 (\$55)   | SRE | SRW | SE  | SM  | ISC11 | ISC10 | ISC01 | ISC00 | MCUCR |

| Read/Write    | R/W | R/W | R/W | R/W | R/W   | R/W   | R/W   | R/W   |       |

| Initial Value | 0   | 0   | 0   | 0   | 0     | 0     | 0     | 0     |       |

#### • Bit 7 – SRE: External SRAM Enable

When the SRE bit is set (one), the external data SRAM is enabled and the pin functions AD0 - 7 (Port A), A8 - 15 (Port C),  $\overline{\text{WR}}$  and  $\overline{\text{RD}}$  (Port D) are activated as the alternate pin functions. Then the SRE bit overrides any pin direction settings in the respective data direction registers. See "SRAM Data Memory – Internal and External" on page 12 for a description of the external SRAM pin functions. When the SRE bit is cleared (zero), the external data SRAM is disabled and the normal pin and data direction settings are used.

#### • Bit 6 – SRW: External SRAM Wait State

When the SRW bit is set (one), a one-cycle wait state is inserted in the external data SRAM access cycle. When the SRW bit is cleared (zero), the external data SRAM access is executed with the normal three-cycle scheme. See Figure 43 and Figure 44.

#### • Bit 5 – SE: Sleep Enable

The SE bit must be set (one) to make the MCU enter the Sleep Mode when the SLEEP instruction is executed. To avoid the MCU entering the Sleep Mode, unless it is the programmer's purpose, it is recommended to set the Sleep Enable (SE) bit just before the execution of the SLEEP instruction.

#### • Bit 4 – SM: Sleep Mode

This bit selects between the two available sleep modes. When SM is cleared (zero), Idle Mode is selected as Sleep Mode. When SM is set (one), Power-down mode is selected as Sleep Mode. For details, refer to the section "Sleep Modes".

#### • Bits 3, 2 – ISC11, ISC10: Interrupt Sense Control 1, Bit 1 and Bit 0

The External Interrupt 1 is activated by the external pin INT1 if the SREG I-flag and the corresponding interrupt mask in the GIMSK are set. The level and edges on the external INT1 pin that activate the interrupt are defined in Table 5.

Table 5. Interrupt 1 Sense Control

| ISC11 | ISC10 | Description                                              |

|-------|-------|----------------------------------------------------------|

| 0     | 0     | The low level of INT1 generates an interrupt request.    |

| 0     | 1     | Reserved                                                 |

| 1     | 0     | The falling edge of INT1 generates an interrupt request. |

| 1     | 1     | The rising edge of INT1 generates an interrupt request.  |

#### • Bits 1, 0 – ISC01, ISC00: Interrupt Sense Control 0, Bit 1 and Bit 0

The External Interrupt 0 is activated by the external pin INT0 if the SREG I-flag and the corresponding interrupt mask are set. The level and edges on the external INT0 pin that activate the interrupt are defined in Table 6.

Table 6. Interrupt 0 Sense Control

| ISC01 | ISC00 | Description                                              |

|-------|-------|----------------------------------------------------------|

| 0     | 0     | The low level of INT0 generates an interrupt request.    |

| 0     | 1     | Reserved                                                 |

| 1     | 0     | The falling edge of INT0 generates an interrupt request. |

| 1     | 1     | The rising edge of INT0 generates an interrupt request.  |

The value on the INTn pin is sampled before detecting edges. If edge interrupt is selected, pulses with a duration longer than one CPU clock period will generate an interrupt. Shorter pulses are not guaranteed to generate an interrupt. If low-level interrupt is selected, the low level must be held until the completion of the currently executing instruction to generate an interrupt. If enabled, a level-triggered interrupt will generate an interrupt request as long as the pin is held low.

#### Timer/Counter1 Control Register A – TCCR1A

| Bit           | 7      | 6      | 5      | 4      | 3 | 2 | 1     | 0     |        |

|---------------|--------|--------|--------|--------|---|---|-------|-------|--------|

| \$2F (\$4F)   | COM1A1 | COM1A0 | COM1B1 | COM1B0 | - | - | PWM11 | PWM10 | TCCR1A |

| Read/Write    | R/W    | R/W    | R/W    | R/W    | R | R | R/W   | R/W   |        |

| Initial Value | 0      | 0      | 0      | 0      | 0 | 0 | 0     | 0     |        |

#### • Bits 7, 6 - COM1A1, COM1A0: Compare Output Mode1A, Bits 1 and 0

The COM1A1 and COM1A0 control bits determine any output pin action following a compare match in Timer/Counter1. Any output pin actions affect pin OC1A (Output CompareA pin 1). This is an alternative function to an I/O port and the corresponding direction control bit must be set (one) to control the output pin. The control configuration is shown in Table 8.

#### • Bits 5, 4 – COM1B1, COM1B0: Compare Output Mode1B, Bits 1 and 0

The COM1B1 and COM1B0 control bits determine any output pin action following a compare match in Timer/Counter1. Any output pin actions affect pin OC1B (Output CompareB). The control configuration is given in Table 8.

| Table 8. | Compare 1 | Mode Select |

|----------|-----------|-------------|

|----------|-----------|-------------|

| COM1X1 | COM1X0 | Description                                      |

|--------|--------|--------------------------------------------------|

| 0      | 0      | Timer/Counter1 disconnected from output pin OC1X |

| 0      | 1      | Toggle the OC1X output line.                     |

| 1      | 0      | Clear the OC1X output line (to zero).            |

| 1      | 1      | Set the OC1X output line (to one).               |

Note: X = A or B

In PWM mode, these bits have a different function. Refer to Table 12 on page 40 for a detailed description.

#### • Bits 3..2 - Res: Reserved Bits

These bits are reserved bits in the AT90S8515 and always read zero.

#### • Bits 1..0 – PWM11, PWM10: Pulse Width Modulator Select Bits 1 and 0

These bits select PWM operation of Timer/Counter1 as specified in Table 9. This mode is described on page 40.

Table 9.

PWM Mode Select

| PWM11 | PWM10 | Description                                 |

|-------|-------|---------------------------------------------|

| 0     | 0     | PWM operation of Timer/Counter1 is disabled |

| 0     | 1     | Timer/Counter1 is an 8-bit PWM              |

| 1     | 0     | Timer/Counter1 is a 9-bit PWM               |

| 1     | 1     | Timer/Counter1 is a 10-bit PWM              |

# AIMEL

The Stop condition provides a Timer Enable/Disable function. The CK down divided modes are scaled directly from the CK oscillator clock. If the external pin modes are used for Timer/Counter1, transitions on PB1/(T1) will clock the counter even if the pin is configured as an output. This feature can give the user software control of the counting.

#### Timer/Counter1 – TCNT1H AND TCNT1L

| Bit           | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   |        |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|--------|

| \$2D (\$4D)   | MSB |     |     |     |     |     |     |     | TCNT1H |

| \$2C (\$4C)   |     |     |     |     |     |     |     | LSB | TCNT1L |

|               | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   | •      |

| Read/Write    | R/W |        |

|               | R/W |        |

| Initial Value | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |        |

|               | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |        |

This 16-bit register contains the prescaled value of the 16-bit Timer/Counter1. To ensure that both the high and low bytes are read and written simultaneously when the CPU accesses these registers, the access is performed using an 8-bit temporary register (TEMP). This temporary register is also used when accessing OCR1A, OCR1B and ICR1. If the main program and interrupt routines perform access to registers using TEMP, interrupts must be disabled during access from the main program (and from interrupt routines if interrupts are allowed from within interrupt routines).

- TCNT1 Timer/Counter1 Write: When the CPU writes to the high byte TCNT1H, the written data is placed in the TEMP register. Next, when the CPU writes the low byte TCNT1L, this byte of data is combined with the byte data in the TEMP register, and all 16 bits are written to the TCNT1 Timer/Counter1 register simultaneously. Consequently, the high byte TCNT1H must be accessed first for a full 16-bit register write operation.

- TCNT1 Timer/Counter1 Read: When the CPU reads the low byte TCNT1L, the data of the low byte TCNT1L is sent to the CPU and the data of the high byte TCNT1H is placed in the TEMP register. When the CPU reads the data in the high byte TCNT1H, the CPU receives the data in the TEMP register. Consequently, the low byte TCNT1L must be accessed first for a full 16-bit register read operation.

The Timer/Counter1 is realized as an up or up/down (in PWM mode) counter with read and write access. If Timer/Counter1 is written to and a clock source is selected, the Timer/Counter1 continues counting in the timer clock cycle after it is preset with the written value.

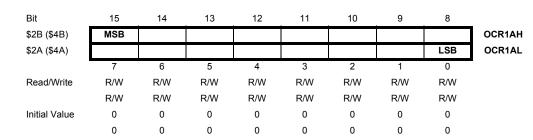

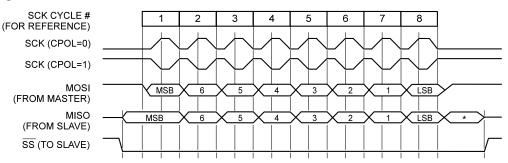

#### Timer/Counter1 Output Compare Register – OCR1AH AND OCR1AL

#### Timer/Counter1 Output Compare Register – OCR1BH AND OCR1BL

| Bit           | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   |        |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|--------|

| \$29 (\$49)   | MSB |     |     |     |     |     |     |     | OCR1BH |

| \$28 (\$48)   |     |     |     |     |     |     |     | LSB | OCR1BL |

|               | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   | -      |

| Read/Write    | R/W |        |

|               | R/W |        |

| Initial Value | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |        |

|               | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |        |

The output compare registers are 16-bit read/write registers.

The Timer/Counter1 Output Compare registers contain the data to be continuously compared with Timer/Counter1. Actions on compare matches are specified in the Timer/Counter1 Control and Status registers. A compare match only occurs if Timer/Counter1 counts to the OCR value. A software write that sets TCNT1 and OCR1A or OCR1B to the same value does not generate a compare match.

A compare match will set the compare interrupt flag in the CPU clock cycle following the compare event.

Since the Output Compare Registers (OCR1A and OCR1B) are 16-bit registers, a temporary register (TEMP) is used when OCR1A/B are written to ensure that both bytes are updated simultaneously. When the CPU writes the high byte, OCR1AH or OCR1BH, the data is temporarily stored in the TEMP register. When the CPU writes the low byte, OCR1AL or OCR1BL, the TEMP register is simultaneously written to OCR1AH or OCR1BH. Consequently, the high byte OCR1AH or OCR1BH must be written first for a full 16-bit register write operation.

The TEMP register is also used when accessing TCNT1 and ICR1. If the main program and interrupt routines perform access to registers using TEMP, interrupts must be disabled during access from the main program (and from interrupt routines if interrupts are allowed from within interrupt routines).

| Bit           | 15  | 14 | 13 | 12 | 11 | 10 | 9 | 8   |       |

|---------------|-----|----|----|----|----|----|---|-----|-------|

| \$25 (\$45)   | MSB |    |    |    |    |    |   |     | ICR1H |

| \$24 (\$44)   |     |    |    |    |    |    |   | LSB | ICR1L |

|               | 7   | 6  | 5  | 4  | 3  | 2  | 1 | 0   | •     |

| Read/Write    | R   | R  | R  | R  | R  | R  | R | R   |       |

|               | R   | R  | R  | R  | R  | R  | R | R   |       |

| Initial Value | 0   | 0  | 0  | 0  | 0  | 0  | 0 | 0   |       |

|               | 0   | 0  | 0  | 0  | 0  | 0  | 0 | 0   |       |

#### Timer/Counter1 Input Capture Register – ICR1H AND ICR1L

The input capture register is a 16-bit read-only register.

When the rising or falling edge (according to the input capture edge setting [ICES1]) of the signal at the input capture pin (ICP) is detected, the current value of the Timer/Counter1 is transferred to the Input Capture Register (ICR1). At the same time, the input capture flag (ICF1) is set (one).

Since the Input Capture Register (ICR1) is a 16-bit register, a temporary register (TEMP) is used when ICR1 is read to ensure that both bytes are read simultaneously. When the CPU reads the low byte ICR1L, the data is sent to the CPU and the data of the high byte ICR1H is placed in the TEMP register. When the CPU reads the data in the high byte ICR1H, the CPU receives the data in the TEMP register. Consequently, the low byte ICR1L must be accessed first for a full 16-bit register read operation.

- 1. In the same operation, write a logical "1" to WDTOE and WDE. A logical "1" must be written to WDE even though it is set to one before the disable operation starts.

- 2. Within the next four clock cycles, write a logical "0" to WDE. This disables the Watchdog.

- Bits 2..0 WDP2, WDP1, WDP0: Watchdog Timer Prescaler 2, 1 and 0

The WDP2, WDP1 and WDP0 bits determine the Watchdog Timer prescaling when the Watchdog Timer is enabled. The different prescaling values and their corresponding Time-out periods are shown in Table 14.

| WDP2 | WDP1 | WDP0 | Number of WDT<br>Oscillator Cycles | Typical Time-out<br>at V <sub>CC</sub> = 3.0V | Typical Time-out<br>at V <sub>CC</sub> = 5.0V |

|------|------|------|------------------------------------|-----------------------------------------------|-----------------------------------------------|

| 0    | 0    | 0    | 16K cycles                         | 47.0 ms                                       | 15.0 ms                                       |

| 0    | 0    | 1    | 32K cycles                         | 94.0 ms                                       | 30.0 ms                                       |

| 0    | 1    | 0    | 64K cycles                         | 0.19 s                                        | 60.0 ms                                       |

| 0    | 1    | 1    | 128K cycles                        | 0.38 s                                        | 0.12 s                                        |

| 1    | 0    | 0    | 256K cycles                        | 0.75 s                                        | 0.24 s                                        |

| 1    | 0    | 1    | 512K cycles                        | 1.5 s                                         | 0.49 s                                        |

| 1    | 1    | 0    | 1,024K cycles                      | 3.0 s                                         | 0.97 s                                        |

| 1    | 1    | 1    | 2,048K cycles                      | 6.0 s                                         | 1.9 s                                         |

| Table 14. | Watchdog | Timer Pre | scale Select |

|-----------|----------|-----------|--------------|

|-----------|----------|-----------|--------------|

Note: The frequency of the Watchdog oscillator is voltage-dependent as shown in the Electrical Characteristics section.

The WDR (Watchdog Reset) instruction should always be executed before the Watchdog Timer is enabled. This ensures that the reset period will be in accordance with the Watchdog Timer prescale settings. If the Watchdog Timer is enabled without reset, the Watchdog Timer may not start to count from zero.

To avoid unintentional MCU reset, the Watchdog Timer should be disabled or reset before changing the Watchdog Timer Prescale Select.

# AIMEL

#### Prevent EEPROM Corruption

During periods of low V<sub>CC</sub>, the EEPROM data can be corrupted because the supply voltage is too low for the CPU and the EEPROM to operate properly. These issues are the same as for board level systems using the EEPROM and the same design solutions should be applied.

An EEPROM data corruption can be caused by two situations when the voltage is too low. First, a regular write sequence to the EEPROM requires a minimum voltage to operate correctly. Second, the CPU itself can execute instructions incorrectly if the supply voltage for executing instructions is too low.

EEPROM data corruption can easily be avoided by following these design recommendations (one is sufficient):

- Keep the AVR RESET active (low) during periods of insufficient power supply voltage. This is best done by an external low V<sub>CC</sub> Reset Protection circuit, often referred to as a Brown-out Detector (BOD). Please refer to application note AVR 180 for design considerations regarding power-on reset and low-voltage detection.

- Keep the AVR core in Power-down Sleep mode during periods of low V<sub>CC</sub>. This will prevent the CPU from attempting to decode and execute instructions, effectively protecting the EEPROM registers from unintentional writes.

- 3. Store constants in Flash memory if the ability to change memory contents from software is not required. Flash memory cannot be updated by the CPU and will not be subject to corruption.

pins are inputs. When  $\overline{SS}$  is driven high, all pins are inputs and the SPI is passive, which means that it will not receive incoming data. Note that the SPI logic will be reset once the  $\overline{SS}$  pin is brought high. If the  $\overline{SS}$  pin is brought high during a transmission, the SPI will stop sending and receiving immediately and both data received and data sent must be considered as lost.

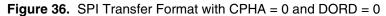

#### **Data Modes**

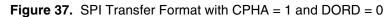

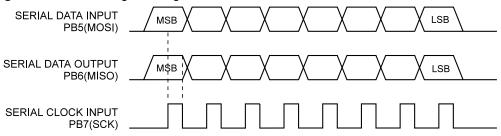

There are four combinations of SCK phase and polarity with respect to serial data, which are determined by control bits CPHA and CPOL. The SPI data transfer formats are shown in Figure 36 and Figure 37.

\* Not defined but normally MSB of character just received

\* Not defined but normally LSB of previously transmitted character

#### **SPI Control Register – SPCR**

| Bit           | 7    | 6   | 5    | 4    | 3    | 2    | 1    | 0    | _    |

|---------------|------|-----|------|------|------|------|------|------|------|

| \$0D (\$2D)   | SPIE | SPE | DORD | MSTR | CPOL | CPHA | SPR1 | SPR0 | SPCR |

| Read/Write    | R/W  | R/W | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | -    |

| Initial Value | 0    | 0   | 0    | 0    | 0    | 0    | 0    | 0    |      |

• Bit 7 – SPIE: SPI Interrupt Enable

This bit causes the SPI interrupt to be executed if SPIF bit in the SPSR register is set and the global interrupts are enabled.

#### Bit 6 – SPE: SPI Enable

When the SPE bit is set (one), the SPI is enabled. This bit must be set to enable any SPI operations.

## **Analog Comparator**

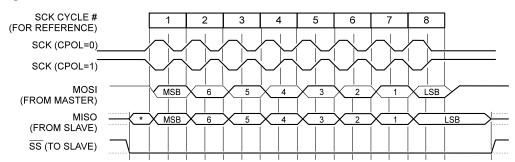

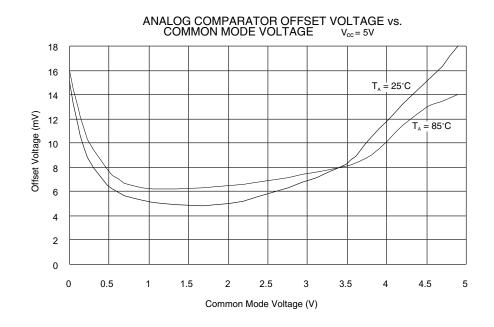

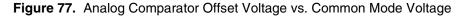

The Analog Comparator compares the input values on the positive input PB2 (AIN0) and negative input PB3 (AIN1). When the voltage on the positive input PB2 (AIN0) is higher than the voltage on the negative input PB3 (AIN1), the Analog Comparator Output (ACO) is set (one). The comparator's output can be set to trigger the Timer/Counter1 Input Capture function. In addition, the comparator can trigger a separate interrupt, exclusive to the Analog Comparator. The user can select interrupt triggering on comparator output rise, fall or toggle. A block diagram of the comparator and its surrounding logic is shown in Figure 41.

#### Analog Comparator Control and Status Register – ACSR

| Bit           | 7   | 6 | 5   | 4   | 3    | 2    | 1     | 0     | _    |

|---------------|-----|---|-----|-----|------|------|-------|-------|------|

| \$08 (\$28)   | ACD | - | ACO | ACI | ACIE | ACIC | ACIS1 | ACIS0 | ACSR |

| Read/Write    | R/W | R | R   | R/W | R/W  | R/W  | R/W   | R/W   | •    |

| Initial Value | 0   | 0 | N/A | 0   | 0    | 0    | 0     | 0     |      |

#### • Bit 7 – ACD: Analog Comparator Disable

When this bit is set (one), the power to the Analog Comparator is switched off. This bit can be set at any time to turn off the Analog Comparator. This will reduce power consumption in active and idle mode. When changing the ACD bit, the Analog Comparator interrupt must be disabled by clearing the ACIE bit in ACSR. Otherwise an interrupt can occur when the bit is changed.

• Bit 6 - Res: Reserved Bit

This bit is a reserved bit in the AT90S8515 and will always read as zero.

Bit 5 – ACO: Analog Comparator Output

ACO is directly connected to the comparator output.

• Bit 4 – ACI: Analog Comparator Interrupt Flag

This bit is set (one) when a comparator output event triggers the interrupt mode defined by ACI1 and ACI0. The Analog Comparator Interrupt routine is executed if the ACIE bit is set (one) and the I-bit in SREG is set (one). ACI is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, ACI is cleared by writing a logical "1" to the flag. Observe however, that if another bit in this register is modified

Port C

Port C is an 8-bit bi-directional I/O port. Three I/O memory address locations are allocated for the Port C, one each for the Data Register – PORTC, \$15(\$35), Data Direction Register – DDRC, \$14(\$34) and the Port C Input Pins – PINC, \$13(\$33). The Port C Input Pins address is read-only, while the Data Register and the Data Direction Register are read/write.

All port pins have individually selectable pull-up resistors. The Port C output buffers can sink 20 mA and thus drive LED displays directly. When pins PC0 to PC7 are used as inputs and are externally pulled low, they will source current if the internal pull-up resistors are activated.

The Port C pins have alternate functions related to the optional external data SRAM. Port C can be configured to be the high-order address byte during accesses to external data memory. When Port C is set to the alternate function by the SRE (external SRAM enable) bit in the MCUCR (MCU Control Register), the alternate settings override the Data Direction Register.

#### Port C Data Register – PORTC

| Bit           | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |       |

|---------------|--------|--------|--------|--------|--------|--------|--------|--------|-------|

| \$15 (\$35)   | PORTC7 | PORTC6 | PORTC5 | PORTC4 | PORTC3 | PORTC2 | PORTC1 | PORTC0 | PORTC |

| Read/Write    | R/W    |       |

| Initial Value | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |       |

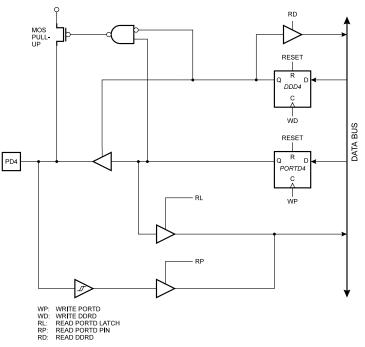

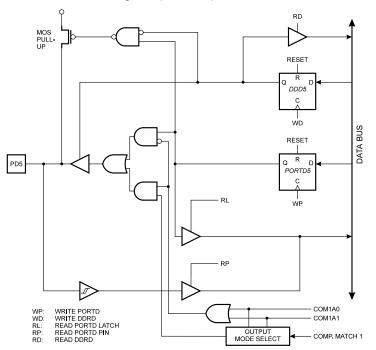

Figure 57. Port D Schematic Diagram (Pin PD5)

# AT90S8515

|                     |                              | ing the third byte of the Programming E<br>correct or not, all four bytes of the instr<br>not echo back, give SCK a positive puls<br>instruction. If the \$53 is not seen within<br>connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | uction must be tra<br>se and issue a ne                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ansmitted. If the \$53 did<br>w Programming Enable                                                                                                              |

|---------------------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     | 4.                           | If a Chip Erase is performed (must be or<br>after the instruction, give RESET a pos<br>Table 34 on page 89 for t <sub>WD_ERASE</sub> value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | itive pulse and sta                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                 |

|                     | 5.                           | The Flash or EEPROM array is program<br>address and data together with the app<br>memory location is first automatically e<br>Data Polling to detect when the next by<br>ten. If polling is not used, wait t <sub>WD_PROG</sub><br>See Table 35 on page 89 for t <sub>WD_PROG</sub><br>data file(s) need to be programmed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | propriate Write instances of the second s<br>second second second<br>second second second<br>second second second<br>second second second<br>second second second<br>second second second<br>second second se | struction. An EEPROM<br>v data is written. Use<br>r EEPROM can be writ-<br>ing the next instruction.                                                            |

|                     | 6.                           | Any memory location can be verified by the content at the selected address at | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                 |

|                     | 7.                           | At the end of the programming session normal operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | , RESET can be                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | set high to commence                                                                                                                                            |

|                     | 8.                           | Power-off sequence (if needed):                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                 |

|                     |                              | Set XTAL1 to "0" (if a crystal is not use                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | d).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                 |

|                     |                              | Set RESET to "1".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                 |

|                     |                              | Turn $V_{CC}$ power off.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                 |