Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | 80C51                                                                   |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 30/20MHz                                                                |

| Connectivity               | UART/USART                                                              |

| Peripherals                | POR                                                                     |

| Number of I/O              | 32                                                                      |

| Program Memory Size        | 8KB (8K × 8)                                                            |

| Program Memory Type        | OTP                                                                     |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 256 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                             |

| Data Converters            | -                                                                       |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 44-QFP                                                                  |

| Supplier Device Package    | 44-PQFP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/ts87c52x2-lcc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Table 1. Memory Size

|           | ROM (bytes) | EPROM (bytes) | TOTAL RAM (bytes) |  |

|-----------|-------------|---------------|-------------------|--|

| TS80C32X2 | 0           | 0             | 256               |  |

| TS80C52X2 | 8k          | 0             | 256               |  |

| TS87C52X2 | 0           | 8k            | 256               |  |

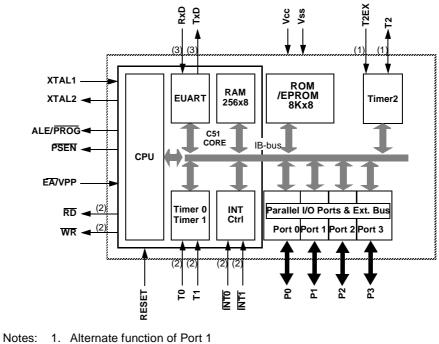

# **Block Diagram**

2. Alternate function of Port 3

# SFR Mapping

The Special Function Registers (SFRs) of the TS80C52X2 fall into the following categories:

- C51 core registers: ACC, B, DPH, DPL, PSW, SP, AUXR1

- I/O port registers: P0, P1, P2, P3

- Timer registers: T2CON, T2MOD, TCON, TH0, TH1, TH2, TMOD, TL0, TL1, TL2, RCAP2L, RCAP2H

- Serial I/O port registers: SADDR, SADEN, SBUF, SCON

- Power and clock control registers: PCON

- Interrupt system registers: IE, IP, IPH

- Others: AUXR, CKCON

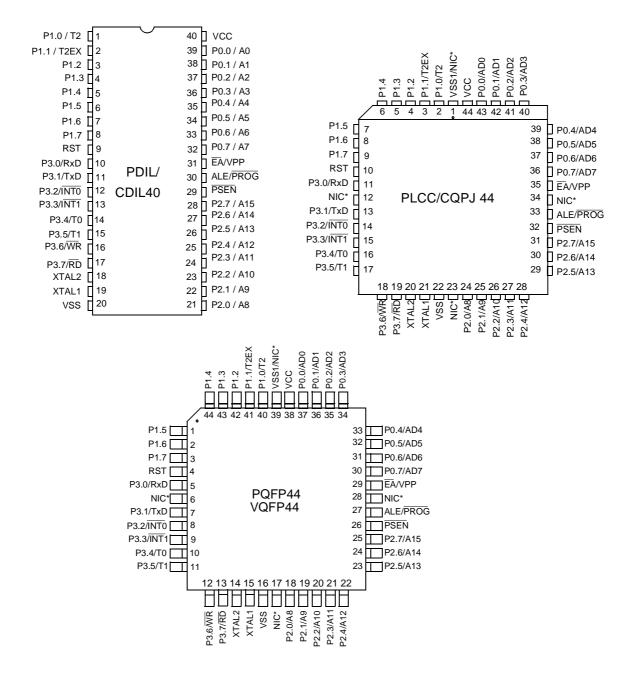

# **Pin Configuration**

\*NIC: No Internal Connection

| Mnemonic           | I   | Pin Nu | mber        | Туре  | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------|-----|--------|-------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    | DIL | LCC    | VQFP<br>1.4 |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                    | 13  | 15     | 9           | I     | INT1 (P3.3): External interrupt 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                    | 14  | 16     | 10          | I     | T0 (P3.4): Timer 0 external input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                    | 15  | 17     | 11          | I     | T1 (P3.5): Timer 1 external input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                    | 16  | 18     | 12          | 0     | WR (P3.6): External data memory write strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                    | 17  | 19     | 13          | 0     | RD (P3.7): External data memory read strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

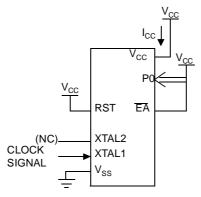

| Reset              | 9   | 10     | 4           | I     | <b>Reset:</b> A high on this pin for two machine cycles while the oscillator is running, resets the device. An internal diffused resistor to $V_{SS}$ permits a power-on reset using only an external capacitor to $V_{CC}$ .                                                                                                                                                                                                                                                                                                                                                                                                        |

| ALE/PROG           | 30  | 33     | 27          | O (I) | Address Latch Enable/Program Pulse: Output pulse for<br>latching the low byte of the address during an access to<br>external memory. In normal operation, ALE is emitted at a<br>constant rate of 1/6 (1/3 in X2 mode) the oscillator frequency,<br>and can be used for external timing or clocking. Note that one<br>ALE pulse is skipped during each access to external data<br>memory. This pin is also the program pulse input (PROG)<br>during EPROM programming. ALE can be disabled by setting<br>SFR's AUXR.0 bit. With this bit set, ALE will be inactive<br>during internal fetches.                                       |

| PSEN               | 29  | 32     | 26          | 0     | Program Store ENable: The read strobe to external program<br>memory. When executing code from the external program<br>memory, <u>PSEN</u> is activated twice each machine cycle, except<br>that two <u>PSEN</u> activations are skipped during each access to<br>external data memory. <u>PSEN</u> is not activated during fetches<br>from internal program memory.                                                                                                                                                                                                                                                                  |

| ĒĀ/V <sub>PP</sub> | 31  | 35     | 29          | I     | External Access Enable/Programming Supply Voltage:<br>EA must be externally held low to enable the device to fetch<br>code from external program memory locations 0000H and<br>3FFFH (RB) or 7FFFH (RC), or FFFFH (RD). If EA is held<br>high, the device executes from internal program memory<br>unless the program counter contains an address greater than<br>3FFFH (RB) or 7FFFH (RC) EA must be held low for<br>ROMless devices. This pin also receives the 12.75V<br>programming supply voltage (V <sub>PP</sub> ) during EPROM<br>programming. If security level 1 is programmed, EA will be<br>internally latched on Reset. |

| XTAL1              | 19  | 21     | 15          | I     | Crystal 1: Input to the inverting oscillator amplifier and input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                    |     |        |             |       | to the internal clock generator circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| XTAL2              | 18  | 20     | 14          | 0     | Crystal 2: Output from the inverting oscillator amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

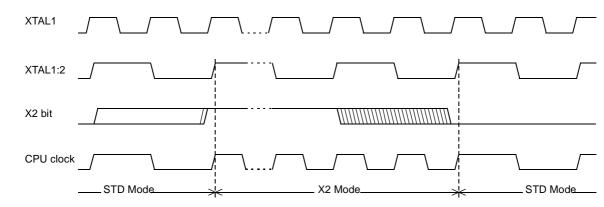

Figure 2. Mode Switching Waveforms

The X2 bit in the CKCON register (See Table 3.) allows to switch from 12 clock cycles per instruction to 6 clock cycles and vice versa. At reset, the standard speed is activated (STD mode). Setting this bit activates the X2 feature (X2 mode).

Note: In order to prevent any incorrect operation while operating in X2 mode, user must be aware that all peripherals using clock frequency as time reference (UART, timers) will have their time reference divided by two. For example a free running timer generating an interrupt every 20 ms will then generate an interrupt every 10 ms. UART with 4800 baud rate will have 9600 baud rate.

# Table 3. CKCON Register

CKCON - Clock Control Register (8Fh)

| 7             | 6               | 5                                                                               | 4                                                                                                                                                                                                               | 3               | 2              | 1            | 0  |  |

|---------------|-----------------|---------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------|--------------|----|--|

| -             | -               | -                                                                               | -                                                                                                                                                                                                               | -               | -              | -            | X2 |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                     |                                                                                                                                                                                                                 |                 |                |              |    |  |

| 7             | -               | Reserved<br>The value rea                                                       | ad from this b                                                                                                                                                                                                  | it is indetermi | nate. Do not s | et this bit. |    |  |

| 6             | -               | Reserved<br>The value rea                                                       | ad from this b                                                                                                                                                                                                  | it is indetermi | nate. Do not s | et this bit. |    |  |

| 5             | -               | Reserved<br>The value rea                                                       | ad from this b                                                                                                                                                                                                  | it is indetermi | nate. Do not s | et this bit. |    |  |

| 4             | -               | Reserved<br>The value rea                                                       | ad from this b                                                                                                                                                                                                  | it is indetermi | nate. Do not s | et this bit. |    |  |

| 3             | -               | Reserved<br>The value rea                                                       | ad from this b                                                                                                                                                                                                  | it is indetermi | nate. Do not s | et this bit. |    |  |

| 2             | -               | Reserved<br>The value rea                                                       | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                                 |                 |                |              |    |  |

| 1             | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                                                                                                                                                                                                                 |                 |                |              |    |  |

| 0             | X2              | Clear to sele                                                                   | <b>CPU and peripheral clock bit</b><br>Clear to select 12 clock periods per machine cycle (STD mode, $F_{OSC}=F_{XTAL}/2$ ).<br>Set to select 6 clock periods per machine cycle (X2 mode, $F_{OSC}=F_{XTAL}$ ). |                 |                |              |    |  |

Reset Value = XXXX XXX0b

Not bit addressable

For further details on the X2 feature, please refer to ANM072 available on the web (http://www.atmel.com)

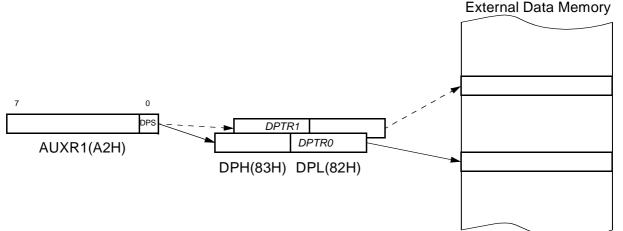

# Dual Data Pointer Register (Ddptr)

The additional data pointer can be used to speed up code execution and reduce code size in a number of ways.

The dual DPTR structure is a way by which the chip will specify the address of an external data memory location. There are two 16-bit DPTR registers that address the external memory, and a single bit called

DPS = AUXR1/bit0 (See Table 5.) that allows the program code to switch between them (Refer to Figure 3).

# Figure 3. Use of Dual Pointer

# Table 4. AUXR1: Auxiliary Register 1

| 7             | 6               | 5                                               | 4                                                                                      | 3               | 2             | 1             | 0   |  |  |

|---------------|-----------------|-------------------------------------------------|----------------------------------------------------------------------------------------|-----------------|---------------|---------------|-----|--|--|

| -             | -               | -                                               | -                                                                                      | GF3             | 0             | -             | DPS |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                     | Description                                                                            |                 |               |               |     |  |  |

| 7             | -               | Reserved<br>The value re                        | ead from this                                                                          | bit is indeterm | inate. Do not | set this bit. |     |  |  |

| 6             | -               | Reserved<br>The value re                        | ead from this                                                                          | bit is indeterm | inate. Do not | set this bit. |     |  |  |

| 5             | -               | Reserved<br>The value re                        | ead from this                                                                          | bit is indeterm | inate. Do not | set this bit. |     |  |  |

| 4             | -               | Reserved<br>The value re                        | ead from this                                                                          | bit is indeterm | inate. Do not | set this bit. |     |  |  |

| 3             | GF3             | This bit is a                                   | general purp                                                                           | ose user flag   |               |               |     |  |  |

| 2             | 0               | Reserved<br>Always stud                         | Reserved<br>Always stuck at 0                                                          |                 |               |               |     |  |  |

| 1             | -               | Reserved<br>The value re                        | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit. |                 |               |               |     |  |  |

| 0             | DPS             | Data Pointe<br>Clear to select<br>Set to select |                                                                                        |                 |               |               |     |  |  |

Reset Value = XXXX XXX0 Not bit addressable

| Table 5 | T2CON | Register |

|---------|-------|----------|

|---------|-------|----------|

T2CON - Timer 2 Control Register (C8h)

| 7             | 6               | 5                                                                                                                                                                                                                                    | 4                                                                                                         | 3                                   | 2               | 1               | 0       |  |

|---------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-------------------------------------|-----------------|-----------------|---------|--|

| TF2           | EXF2            | RCLK                                                                                                                                                                                                                                 | TCLK                                                                                                      | EXEN2                               | TR2             | C/T2#           | CP/RL2# |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                                                                                          |                                                                                                           |                                     |                 |                 |         |  |

| 7             | TF2             | Timer 2 overf<br>Must be cleare<br>Set by hardwa                                                                                                                                                                                     | d by software                                                                                             |                                     | CLK = 0 and T   | CLK = 0.        |         |  |

| 6             | EXF2            | Set when a ca<br>EXEN2=1.<br>When set, cau<br>interrupt is ena<br>Must be cleare                                                                                                                                                     | Timer 2 External Flag<br>Set when a capture or a reload is caused by a negative transition on T2EX pin if |                                     |                 |                 |         |  |

| 5             | RCLK            | Receive Clock<br>Clear to use time<br>Set to use time                                                                                                                                                                                | mer 1 overflov                                                                                            |                                     |                 | •               |         |  |

| 4             | TCLK            | Transmit Cloc<br>Clear to use tin<br>Set to use time                                                                                                                                                                                 | mer 1 overflov                                                                                            |                                     |                 | •               |         |  |

| 3             | EXEN2           | Timer 2 Exter<br>Clear to ignore<br>Set to cause a<br>detected, if tim                                                                                                                                                               | e events on Ta<br>capture or re                                                                           | 2EX pin for tim<br>load when a n    | egative transi  |                 | pin is  |  |

| 2             | TR2             | Clear to turn o                                                                                                                                                                                                                      | Timer 2 Run control bit<br>Clear to turn off timer 2.<br>Set to turn on timer 2.                          |                                     |                 |                 |         |  |

| 1             | C/T2#           | <b>Timer/Counter 2 select bit</b><br>Clear for timer operation (input from internal clock system: F <sub>OSC</sub> ).<br>Set for counter operation (input from T2 input pin, falling edge trigger). Must be 0<br>for clock out mode. |                                                                                                           |                                     |                 |                 |         |  |

| 0             | CP/RL2#         | Timer 2 Captu<br>If RCLK=1 or 7<br>timer 2 overflo<br>Clear to Auto-r<br>EXEN2=1.<br>Set to capture                                                                                                                                  | CLK=1, CP/F<br>w.<br>eload on time                                                                        | RL2# is ignored<br>er 2 overflows o | or negative tra | ansitions on T2 |         |  |

Reset Value = 0000 0000b Bit addressable

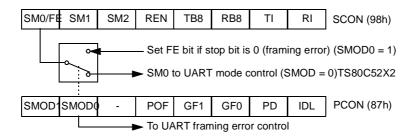

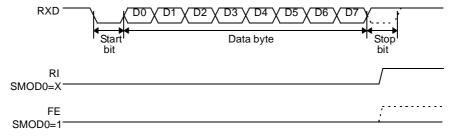

# **TS80C52X2 Serial I/O**<br/>PortThe serial I/O port in the TS80C52X2 is compatible with the serial I/O port in the 80C52.<br/>It provides both synchronous and asynchronous communication modes. It operates as<br/>an Universal Asynchronous Receiver and Transmitter (UART) in three full-duplex<br/>modes (Modes 1, 2 and 3). Asynchronous transmission and reception can occur simul-<br/>taneously and at different baud rates<br/>Serial I/O port includes the following enhancements:<br/> Framing Error DetectionFraming bit error detection is provided for the three asynchronous modes (modes 1, 2<br/>and 3). To enable the framing bit error detection feature, set SMOD0 bit in PCON regis-<br/>ter (See Figure 6).

### Figure 6. Framing Error Block Diagram

When this feature is enabled, the receiver checks each incoming data frame for a valid stop bit. An invalid stop bit may result from noise on the serial lines or from simultaneous transmission by two CPUs. If a valid stop bit is not found, the Framing Error bit (FE) in SCON register (See Table 9.) bit is set.

Software may examine FE bit after each reception to check for data errors. Once set, only software or a reset can clear FE bit. Subsequently received frames with valid stop bits cannot clear FE bit. When FE feature is enabled, RI rises on stop bit instead of the last data bit (See Figure 7. and Figure 8.).

# Figure 7. UART Timings in Mode 1

1111 0000b).

For slave A, bit 1 is a 1; for slaves B and C, bit 1 is a don't care bit. To communicate with slaves B and C, but not slave A, the master must send an address with bits 0 and 1 both set (e.g. 1111 0011b).

To communicate with slaves A, B and C, the master must send an address with bit 0 set, bit 1 clear, and bit 2 clear (e.g. 1111 0001b).

**Broadcast Address** A broadcast address is formed from the logical OR of the SADDR and SADEN registers with zeros defined as don't-care bits, e.g.:

SADDR 0101 0110b SADEN 1111 1100b Broadcast =SADDR OR SADEN1111 111Xb

The use of don't-care bits provides flexibility in defining the broadcast address, however in most applications, a broadcast address is FFh. The following is an example of using broadcast addresses:

Slave A:SADDR1111 0001b <u>SADEN1111 1010b</u> Broadcast1111 1X11b, Slave B:SADDR1111 0011b <u>SADEN1111 1001b</u> Broadcast1111 1X11B,

Slave C:SADDR=1111 0010b <u>SADEN1111 1101b</u> Broadcast1111 1111b

For slaves A and B, bit 2 is a don't care bit; for slave C, bit 2 is set. To communicate with all of the slaves, the master must send an address FFh. To communicate with slaves A and B, but not slave C, the master can send and address FBh.

Reset AddressesOn reset, the SADDR and SADEN registers are initialized to 00h, i.e. the given and<br/>broadcast addresses are XXXX XXXb (all don't-care bits). This ensures that the serial<br/>port will reply to any address, and so, that it is backwards compatible with the 80C51<br/>microcontrollers that do not support automatic address recognition.

Table 7.

SADEN Register

| 7                                   | 6          | 5           | 4             | 3 | 2        | 1 | 0 |

|-------------------------------------|------------|-------------|---------------|---|----------|---|---|

|                                     |            |             |               |   |          |   |   |

| Decet Valu                          |            | 0006        |               |   | <u>.</u> |   |   |

| Reset Valu                          |            | 0000        |               |   |          |   |   |

| Not bit add                         | ressable   |             |               |   |          |   |   |

|                                     |            |             |               |   |          |   |   |

|                                     |            |             |               |   |          |   |   |

| Table 8 S                           |            | vietor      |               |   |          |   |   |

|                                     | -          |             |               |   |          |   |   |

|                                     | -          |             | er (A9h)      |   |          |   |   |

| <b>Table 8.</b> S<br>SADDR - S<br>7 | -          |             | er (A9h)<br>4 | 3 | 2        | 1 | 0 |

| SADDR - S                           | lave Addre | ess Registe | er (A9h)<br>4 | 3 | 2        | 1 | 0 |

| SADDR - S                           | lave Addre | ess Registe | er (A9h)<br>4 | 3 | 2        | 1 | 0 |

Not bit addressable

Exit from power-down by reset redefines all the SFRs, exit from power-down by external interrupt does no affect the SFRs.

Exit from power-down by either reset or external interrupt does not affect the internal RAM content.

Note: If idle mode is activated with power-down mode (IDL and PD bits set), the exit sequence is unchanged, when execution is vectored to interrupt, PD and IDL bits are cleared and idle mode is not entered.

| Mode          | Program<br>Memory | ALE | PSEN | PORT0                       | PORT1     | PORT2     | PORT3     |

|---------------|-------------------|-----|------|-----------------------------|-----------|-----------|-----------|

| Idle          | Internal          | 1   | 1    | Port<br>Data <sup>(1)</sup> | Port Data | Port Data | Port Data |

| Idle          | External          | 1   | 1    | Floating                    | Port Data | Address   | Port Data |

| Power<br>Down | Internal          | 0   | 0    | Port<br>Data <sup>(1)</sup> | Port Data | Port Data | Port Data |

| Power<br>Down | External          | 0   | 0    | Floating                    | Port Data | Port Data | Port Data |

**Table 15.** The State of Ports During Idle and Power-down Modes

Note: 1. Port 0 can force a "zero" level. A "one" will leave port floating.

# **Reduced EMI Mode**

The ALE signal is used to demultiplex address and data buses on port 0 when used with external program or data memory. Nevertheless, during internal code execution, ALE signal is still generated. In order to reduce EMI, ALE signal can be disabled by setting AO bit.

The AO bit is located in AUXR register at bit location 0. As soon as AO is set, ALE is no longer output but remains active during MOVX and MOVC instructions and external fetches. During ALE disabling, ALE pin is weakly pulled high.

## Table 18. AUXR Register

AUXR - Auxiliary Register (8Eh)

| 7             | 6               | 5                               | 4                                                                               | 3                                 | 2              | 1            | 0  |

|---------------|-----------------|---------------------------------|---------------------------------------------------------------------------------|-----------------------------------|----------------|--------------|----|

| -             | -               | -                               | -                                                                               | -                                 | -              | -            | AO |

| Bit<br>Number | Bit<br>Mnemonic | Description                     |                                                                                 |                                   |                |              |    |

| 7             | -               | Reserved<br>The value re        | ad from this b                                                                  | it is indetermi                   | nate. Do not s | et this bit. |    |

| 6             | -               | Reserved<br>The value re        | ad from this b                                                                  | it is indetermi                   | nate. Do not s | et this bit. |    |

| 5             | -               | <b>Reserved</b><br>The value re | ad from this b                                                                  | it is indetermi                   | nate. Do not s | et this bit. |    |

| 4             | -               | <b>Reserved</b><br>The value re | ad from this b                                                                  | it is indetermi                   | nate. Do not s | et this bit. |    |

| 3             | -               | Reserved<br>The value re        | ad from this b                                                                  | it is indetermi                   | nate. Do not s | et this bit. |    |

| 2             | -               | <b>Reserved</b><br>The value re | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                                   |                |              |    |

| 1             | -               | Reserved<br>The value re        | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                                   |                |              |    |

| 0             | AO              |                                 | ore ALE opera                                                                   | ation during in<br>on during inte |                |              |    |

Reset Value = XXXX XXX0b Not bit addressable 12,000  $\mu$ W/cm<sup>2</sup> rating for 30 minutes, at a distance of about 25 mm, should be sufficient. An exposure of 1 hour is recommended with most of standard erasers.

Erasure of the EPROM begins to occur when the chip is exposed to light with wavelength shorter than approximately 4,000 Å. Since sunlight and fluorescent lighting have wavelengths in this range, exposure to these light sources over an extended time (about 1 week in sunlight, or 3 years in room-level fluorescent lighting) could cause inadvertent erasure. If an application subjects the device to this type of exposure, it is suggested that an opaque label be placed over the window.

**Signature Bytes** The TS80/87C52X2 has four signature bytes in location 30h, 31h, 60h and 61h. To read these bytes follow the procedure for EPROM verify but activate the control lines provided in Table 31. for Read Signature Bytes. Table 35. shows the content of the signature byte for the TS80/87C52X2.

| Location | Contents | Comment                  |

|----------|----------|--------------------------|

| 30h      | 58h      | Manufacturer Code: Atmel |

| 31h      | 57h      | Family Code: C51 X2      |

| 60h      | 2Dh      | Product name: TS80C52X2  |

| 60h      | ADh      | Product name:TS87C52X2   |

| 60h      | 20h      | Product name: TS80C32X2  |

| 61h      | FFh      | Product revision number  |

Table 21. Signature Bytes Content

# TS8xCx2X2

| Table 22. DC Parameters in Standard Voltage (Continued | Table 22. | eters in Standard Voltage (Continued) |

|--------------------------------------------------------|-----------|---------------------------------------|

|--------------------------------------------------------|-----------|---------------------------------------|

| Symbol                            | Parameter                                         | Min                                                                     | Тур               | Мах                                                   | Unit        | Test Conditions                                                                                                   |

|-----------------------------------|---------------------------------------------------|-------------------------------------------------------------------------|-------------------|-------------------------------------------------------|-------------|-------------------------------------------------------------------------------------------------------------------|

| V <sub>OH</sub>                   | Output High Voltage, ports 1, 2, 3                | V <sub>CC</sub> - 0.3<br>V <sub>CC</sub> - 0.7<br>V <sub>CC</sub> - 1.5 |                   |                                                       | V<br>V<br>V | I <sub>OH</sub> = -10 μA<br>I <sub>OH</sub> = -30 μA<br>I <sub>OH</sub> = -60 μA<br>V <sub>CC</sub> = 5V ± 10%    |

| V <sub>OH1</sub>                  | Output High Voltage, port 0                       | V <sub>CC</sub> - 0.3<br>V <sub>CC</sub> - 0.7<br>V <sub>CC</sub> - 1.5 |                   |                                                       | V<br>V<br>V | I <sub>OH</sub> = -200 μA<br>I <sub>OH</sub> = -3.2 mA<br>I <sub>OH</sub> = -7.0 mA<br>V <sub>CC</sub> = 5V ± 10% |

| V <sub>OH2</sub>                  | Output High Voltage,ALE, PSEN                     | V <sub>CC</sub> - 0.3<br>V <sub>CC</sub> - 0.7<br>V <sub>CC</sub> - 1.5 |                   |                                                       | V<br>V<br>V | $I_{OH}$ = -100 µA<br>$I_{OH}$ = -1.6 mA<br>$I_{OH}$ = -3.5 mA<br>$V_{CC}$ = 5V ± 10%                             |

| R <sub>RST</sub>                  | RST Pulldown Resistor                             | 50                                                                      | 90 <sup>(5)</sup> | 200                                                   | kΩ          |                                                                                                                   |

| I <sub>IL</sub>                   | Logical 0 Input Current ports 1, 2 and 3          |                                                                         |                   | -50                                                   | μΑ          | Vin = 0.45V                                                                                                       |

| ILI                               | Input Leakage Current                             |                                                                         |                   | ±10                                                   | μΑ          | $0.45V < Vin < V_{CC}$                                                                                            |

| I <sub>TL</sub>                   | Logical 1 to 0 Transition Current, ports 1, 2, 3  |                                                                         |                   | -650                                                  | μΑ          | Vin = 2.0 V                                                                                                       |

| C <sub>IO</sub>                   | Capacitance of I/O Buffer                         |                                                                         |                   | 10                                                    | pF          | Fc = 1 MHz<br>TA = 25°C                                                                                           |

| I <sub>PD</sub>                   | Power Down Current                                |                                                                         | 20 (5)            | 50                                                    | μΑ          | $2.0 \ {\rm V} < {\rm V_{CC}}_< 5.5 {\rm V}^{(3)}$                                                                |

| I <sub>CC</sub><br>under<br>RESET | Power Supply Current Maximum values, X1 mode: (7) |                                                                         |                   | 1 + 0.4 Freq<br>(MHz)<br>at12MHz 5.8<br>at16MHz 7.4   | mA          | $V_{\rm CC} = 5.5 V^{(1)}$                                                                                        |

| I <sub>CC</sub><br>operating      | Power Supply Current Maximum values, X1 mode: (7) |                                                                         |                   | 3 + 0.6 Freq<br>(MHz)<br>at12MHz 10.2<br>at16MHz 12.6 | mA          | $V_{CC} = 5.5 V^{(8)}$                                                                                            |

| l <sub>cc</sub><br>idle           | Power Supply Current Maximum values, X1 mode: (7) |                                                                         |                   | 0.25+0.3 Freq<br>(MHz)<br>at12MHz 3.9<br>at16MHz 5.1  | mA          | $V_{\rm CC} = 5.5 V^{(2)}$                                                                                        |

####

Table 23. DC Parameters for Low Voltage

| Symbol                            | Parameter                                                    | Min                       | Тур                                    | Max                                                  | Unit | Test Conditions                                                                                     |

|-----------------------------------|--------------------------------------------------------------|---------------------------|----------------------------------------|------------------------------------------------------|------|-----------------------------------------------------------------------------------------------------|

| V <sub>IL</sub>                   | Input Low Voltage                                            | -0.5                      |                                        | 0.2 V <sub>CC</sub> - 0.1                            | V    |                                                                                                     |

| V <sub>IH</sub>                   | Input High Voltage except XTAL1, RST                         | 0.2 V <sub>CC</sub> + 0.9 |                                        | V <sub>CC</sub> + 0.5                                | V    |                                                                                                     |

| V <sub>IH1</sub>                  | Input High Voltage, XTAL1, RST                               | 0.7 V <sub>CC</sub>       |                                        | V <sub>CC</sub> + 0.5                                | V    |                                                                                                     |

| V <sub>OL</sub>                   | Output Low Voltage, ports 1, 2, 3 (6)                        |                           |                                        | 0.45                                                 | V    | I <sub>OL</sub> = 0.8 mA <sup>(4)</sup>                                                             |

| V <sub>OL1</sub>                  | Output Low Voltage, port 0, ALE, PSEN (6)                    |                           |                                        | 0.45                                                 | V    | I <sub>OL</sub> = 1.6 mA <sup>(4)</sup>                                                             |

| V <sub>OH</sub>                   | Output High Voltage, ports 1, 2, 3                           | 0.9 V <sub>CC</sub>       |                                        |                                                      | V    | I <sub>OH</sub> = -10 μA                                                                            |

| V <sub>OH1</sub>                  | Output High Voltage, port 0, ALE, PSEN                       | 0.9 V <sub>CC</sub>       |                                        |                                                      | V    | I <sub>OH</sub> = -40 μA                                                                            |

| I <sub>IL</sub>                   | Logical 0 Input Current ports 1, 2 and 3                     |                           |                                        | -50                                                  | μA   | Vin = 0.45V                                                                                         |

| ILI                               | Input Leakage Current                                        |                           |                                        | ±10                                                  | μA   | $0.45V < Vin < V_{CC}$                                                                              |

| I <sub>TL</sub>                   | Logical 1 to 0 Transition Current, ports 1, 2, 3             |                           |                                        | -650                                                 | μA   | Vin = 2.0 V                                                                                         |

| R <sub>RST</sub>                  | RST Pulldown Resistor                                        | 50                        | 90 <sup>(5)</sup>                      | 200                                                  | kΩ   |                                                                                                     |

| CIO                               | Capacitance of I/O Buffer                                    |                           |                                        | 10                                                   | pF   | Fc = 1 MHz<br>T <sub>A</sub> = 25°C                                                                 |

| I <sub>PD</sub>                   | Power Down Current                                           |                           | 20 <sup>(5)</sup><br>10 <sup>(5)</sup> | 50<br>30                                             | μA   | $V_{CC} = 2.0 \text{ V to } 5.5 \text{V}^{(3)}$<br>$V_{CC} = 2.0 \text{ V to } 3.3 \text{ V}^{(3)}$ |

| I <sub>cc</sub><br>under<br>RESET | Power Supply Current Maximum values, X1 mode: <sup>(7)</sup> |                           |                                        | 1 + 0.2 Freq<br>(MHz)<br>at12MHz 3.4<br>at16MHz 4.2  | mA   | $V_{CC} = 3.3 V^{(1)}$                                                                              |

| I <sub>CC</sub><br>operating      | Power Supply Current Maximum values, X1 mode: <sup>(7)</sup> |                           |                                        | 1 + 0.3 Freq<br>(MHz)<br>at12MHz 4.6<br>at16MHz 5.8  | mA   | V <sub>CC</sub> = 3.3 V <sup>(8)</sup>                                                              |

| I <sub>CC</sub><br>idle           | Power Supply Current Maximum values, X1 mode: <sup>(7)</sup> |                           |                                        | 0.15 Freq<br>(MHz) + 0.2<br>at12MHz 2<br>at16MHz 2.6 | mA   | V <sub>CC</sub> = 3.3 V <sup>(2)</sup>                                                              |

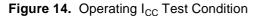

Notes: 1. I<sub>CC</sub> under reset is measured with all output pins disconnected; XTAL1 driven with T<sub>CLCH</sub>, T<sub>CHCL</sub> = 5 ns (see Figure 17.), V<sub>IL</sub> = V<sub>SS</sub> + 0.5V,

$V_{IH} = V_{CC} - 0.5V$ ; XTAL2 N.C.;  $\overline{EA} = RST = Port 0 = V_{CC}$ .  $I_{CC}$  would be slightly higher if a crystal oscillator used..

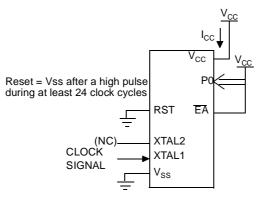

2. Idle I<sub>CC</sub> is measured with all out<u>put</u> pins disconnected; XTAL1 driven with  $T_{CLCH}$ ,  $T_{CHCL} = 5$  ns,  $V_{IL} = V_{SS} + 0.5V$ ,  $V_{IH} = V_{CC} - 0.5V$ ; XTAL2 N.C; Port 0 =  $V_{CC}$ ; EA = RST =  $V_{SS}$  (see Figure 15.).

Power Down I<sub>CC</sub> is measured with all output pins disconnected; EA = V<sub>SS</sub>, PORT 0 = V<sub>CC</sub>; XTAL2 NC.; RST = V<sub>SS</sub> (see Figure 16.).

4. Capacitance loading on Ports 0 and 2 may cause spurious noise pulses to be superimposed on the V<sub>OL</sub>s of ALE and Ports 1 and 3. The noise is due to external bus capacitance discharging into the Port 0 and Port 2 pins when these pins make 1 to 0 transitions during bus operation. In the worst cases (capacitive loading 100pF), the noise pulse on the ALE line may exceed 0.45V with maxi V<sub>OL</sub> peak 0.6V. A Schmitt Trigger use is not necessary.

5. Typicals are based on a limited number of samples and are not guaranteed. The values listed are at room temperature and 5V.

Under steady state (non-transient) conditions, I<sub>OL</sub> must be externally limited as follows: Maximum I<sub>OL</sub> per port pin: 10 mA Maximum I<sub>OL</sub> per 8-bit port:

TS8xCx2X2

Port 0: 26 mA Ports 1, 2 and 3: 15 mA Maximum total  $I_{OL}$  for all output pins: 71 mA If  $I_{OL}$  exceeds the test condition,  $V_{OL}$  may exceed the related specification. Pins are not guaranteed to sink current greater than the listed test conditions.

- 7. For other values, please contact your sales office.

- Operating I<sub>CC</sub> is measured with all output pins disconnected; XTAL1 driven with T<sub>CLCH</sub>, T<sub>CHCL</sub> = 5 ns (see Figure 17.), V<sub>IL</sub> = V<sub>SS</sub> + 0.5V,

$V_{IH} = V_{CC} - 0.5V$ ; XTAL2 N.C.;  $\overline{EA} = Port 0 = V_{CC}$ ; RST =  $V_{SS}$ . The internal ROM runs the code 80 FE (label: SJMP label). I<sub>CC</sub> would be slightly higher if a crystal oscillator is used. Measurements are made with OTP products when possible, which is the worst case.

Figure 13.  $I_{CC}$  Test Condition, under reset

All other pins are disconnected.

All other pins are disconnected.

Figure 15. I<sub>CC</sub> Test Condition, Idle Mode

All other pins are disconnected.

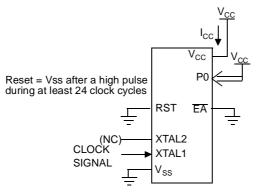

| Speed             |     | M<br>MHz | X2 n<br>30 l<br>60 l | V<br>node<br>MHz<br>MHz<br>uiv. | stan<br>mod | V<br>dard<br>le 40<br>Hz | X2 n<br>20 l<br>40 l | L<br>node<br>MHz<br>MHz<br>uiv. | stan<br>mo | L<br>dard<br>ode<br>MHz | Units |

|-------------------|-----|----------|----------------------|---------------------------------|-------------|--------------------------|----------------------|---------------------------------|------------|-------------------------|-------|

| Symbol            | Min | Max      | Min                  | Max                             | Min         | Max                      | Min                  | Max                             | Min        | Max                     |       |

| Т                 | 25  |          | 33                   |                                 | 25          |                          | 50                   |                                 | 33         |                         | ns    |

| T <sub>LHLL</sub> | 40  |          | 25                   |                                 | 42          |                          | 35                   |                                 | 52         |                         | ns    |

| T <sub>AVLL</sub> | 10  |          | 4                    |                                 | 12          |                          | 5                    |                                 | 13         |                         | ns    |

| T <sub>LLAX</sub> | 10  |          | 4                    |                                 | 12          |                          | 5                    |                                 | 13         |                         | ns    |

| T <sub>LLIV</sub> |     | 70       |                      | 45                              |             | 78                       |                      | 65                              |            | 98                      | ns    |

| T <sub>LLPL</sub> | 15  |          | 9                    |                                 | 17          |                          | 10                   |                                 | 18         |                         | ns    |

| T <sub>PLPH</sub> | 55  |          | 35                   |                                 | 60          |                          | 50                   |                                 | 75         |                         | ns    |

| T <sub>PLIV</sub> |     | 35       |                      | 25                              |             | 50                       |                      | 30                              |            | 55                      | ns    |

| T <sub>PXIX</sub> | 0   |          | 0                    |                                 | 0           |                          | 0                    |                                 | 0          |                         | ns    |

| T <sub>PXIZ</sub> |     | 18       |                      | 12                              |             | 20                       |                      | 10                              |            | 18                      | ns    |

| T <sub>AVIV</sub> |     | 85       |                      | 53                              |             | 95                       |                      | 80                              |            | 122                     | ns    |

| T <sub>PLAZ</sub> |     | 10       |                      | 10                              |             | 10                       |                      | 10                              |            | 10                      | ns    |

Table 28. AC Parameters for a Variable Clock: derating formula

| Symbol            | Туре | Standard<br>Clock | X2 Clock  | -М | -V | -L | Units |

|-------------------|------|-------------------|-----------|----|----|----|-------|

| T <sub>LHLL</sub> | Min  | 2 T - x           | T - x     | 10 | 8  | 15 | ns    |

| T <sub>AVLL</sub> | Min  | T - x             | 0.5 T - x | 15 | 13 | 20 | ns    |

| T <sub>LLAX</sub> | Min  | T - x             | 0.5 T - x | 15 | 13 | 20 | ns    |

| T <sub>LLIV</sub> | Max  | 4 T - x           | 2 T - x   | 30 | 22 | 35 | ns    |

| T <sub>LLPL</sub> | Min  | T - x             | 0.5 T - x | 10 | 8  | 15 | ns    |

| T <sub>PLPH</sub> | Min  | 3 T - x           | 1.5 T - x | 20 | 15 | 25 | ns    |

| T <sub>PLIV</sub> | Max  | 3 T - x           | 1.5 T - x | 40 | 25 | 45 | ns    |

| T <sub>PXIX</sub> | Min  | х                 | х         | 0  | 0  | 0  | ns    |

| T <sub>PXIZ</sub> | Max  | T - x             | 0.5 T - x | 7  | 5  | 15 | ns    |

| T <sub>AVIV</sub> | Max  | 5 T - x           | 2.5 T - x | 40 | 30 | 45 | ns    |

| T <sub>PLAZ</sub> | Max  | х                 | х         | 10 | 10 | 10 | ns    |

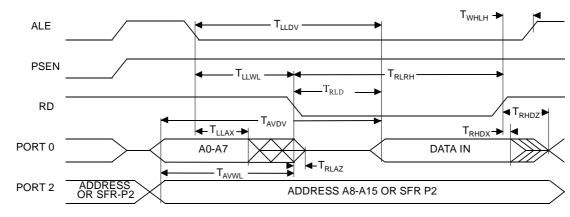

# External Program Memory Read Cycle

Figure 18. External Program Memory Read Cycle

#### External Data Memory Characteristics

Table 29.

Symbol Description

| Symbol            | Parameter                   |

|-------------------|-----------------------------|

| T <sub>RLRH</sub> | RD Pulse Width              |

| T <sub>WLWH</sub> | WR Pulse Width              |

| T <sub>RLDV</sub> | RD to Valid Data In         |

| T <sub>RHDX</sub> | Data Hold After RD          |

| T <sub>RHDZ</sub> | Data Float After RD         |

| T <sub>LLDV</sub> | ALE to Valid Data In        |

| T <sub>AVDV</sub> | Address to Valid Data In    |

| T <sub>LLWL</sub> | ALE to WR or RD             |

| T <sub>AVWL</sub> | Address to WR or RD         |

| T <sub>QVWX</sub> | Data Valid to WR Transition |

| T <sub>QVWH</sub> | Data set-up to WR High      |

| T <sub>WHQX</sub> | Data Hold After WR          |

| T <sub>RLAZ</sub> | RD Low to Address Float     |

| T <sub>WHLH</sub> | RD or WR High to ALE high   |

# External Data Memory Read Cycle

Figure 20. External Data Memory Read Cycle

# Serial Port Timing - Shift Register Mode

Table 32. Symbol Description

| Symbol            | Parameter                                |

|-------------------|------------------------------------------|

| T <sub>XLXL</sub> | Serial port clock cycle time             |

| T <sub>QVHX</sub> | Output data set-up to clock rising edge  |

| T <sub>XHQX</sub> | Output data hold after clock rising edge |

| T <sub>XHDX</sub> | Input data hold after clock rising edge  |

| T <sub>XHDV</sub> | Clock rising edge to input data valid    |

| Speed             | -I<br>40 I | M<br>MHz |     | ИНz | stan<br>mod | V<br>dard<br>le 40<br>Hz |     | node<br>MHz<br>MHz | stan<br>mo | L<br>dard<br>ode<br>MHz | Units |

|-------------------|------------|----------|-----|-----|-------------|--------------------------|-----|--------------------|------------|-------------------------|-------|

| Symbol            | Min        | Max      | Min | Max | Min         | Max                      | Min | Max                | Min        | Max                     |       |

| T <sub>XLXL</sub> | 300        |          | 200 |     | 300         |                          | 300 |                    | 400        |                         | ns    |

| T <sub>QVHX</sub> | 200        |          | 117 |     | 200         |                          | 200 |                    | 283        |                         | ns    |

| T <sub>XHQX</sub> | 30         |          | 13  |     | 30          |                          | 30  |                    | 47         |                         | ns    |

| T <sub>XHDX</sub> | 0          |          | 0   |     | 0           |                          | 0   |                    | 0          |                         | ns    |

| $T_{XHDV}$        |            | 117      |     | 34  |             | 117                      |     | 117                |            | 200                     | ns    |

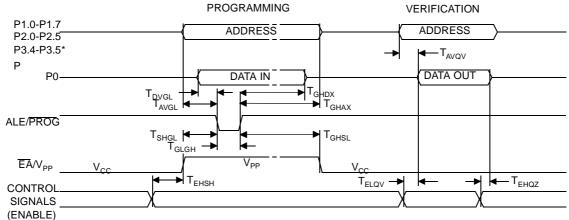

# **EPROM Programming and** Verification Characteristics

$T_A$  = 21°C to 27°C;  $V_{SS}$  = 0V;  $~V_{CC}$  = 5V  $\pm$  10% while programming.  $V_{CC}$  = operating range while verifying.

Table 35.

EPROM Programming Parameters

| Symbol              | Parameter                         | Min                  | Мах                  | Units |

|---------------------|-----------------------------------|----------------------|----------------------|-------|

| V <sub>PP</sub>     | Programming Supply Voltage        | 12.5                 | 13                   | V     |

| I <sub>PP</sub>     | Programming Supply Current        |                      | 75                   | mA    |

| 1/T <sub>CLCL</sub> | Oscillator Frquency               | 4                    | 6                    | MHz   |

| T <sub>AVGL</sub>   | Address Setup to PROG Low         | 48 T <sub>CLCL</sub> |                      |       |

| T <sub>GHAX</sub>   | Adress Hold after PROG            | 48 T <sub>CLCL</sub> |                      |       |

| T <sub>DVGL</sub>   | Data Setup to PROG Low            | 48 T <sub>CLCL</sub> |                      |       |

| T <sub>GHDX</sub>   | Data Hold after PROG              | 48 T <sub>CLCL</sub> |                      |       |

| T <sub>EHSH</sub>   | (Enable) High to V <sub>PP</sub>  | 48 T <sub>CLCL</sub> |                      |       |

| T <sub>SHGL</sub>   | V <sub>PP</sub> Setup to PROG Low | 10                   |                      | μs    |

| T <sub>GHSL</sub>   | V <sub>PP</sub> Hold after PROG   | 10                   |                      | μs    |

| T <sub>GLGH</sub>   | PROG Width                        | 90                   | 110                  | μs    |

| T <sub>AVQV</sub>   | Address to Valid Data             |                      | 48 T <sub>CLCL</sub> |       |

| T <sub>ELQV</sub>   | ENABLE Low to Data Valid          |                      | 48 T <sub>CLCL</sub> |       |

| T <sub>EHQZ</sub>   | Data Float after ENABLE           | 0                    | 48 T <sub>CLCL</sub> |       |

# EPROM Programming and Verification Waveforms

## Figure 22. EPROM Programming and Verification Waveforms

\* 8KB: up to P2.4, 16KB: up to P2.5, 32KB: up to P3.4, 64KB: up to P3.5

## Table 37. Possible Ordering Entries (Continued)

| Part Number <sup>(3)</sup> | Memory Size | Supply Voltage  | Temperature<br>Range | Max Frequency         | Package | Packing |

|----------------------------|-------------|-----------------|----------------------|-----------------------|---------|---------|

| AT80C32X2-RLTUL            | ROMLess     | 2.7 to 5.5V     | Industrial & Green   | 30 MHz <sup>(1)</sup> | VQFP44  | Tray    |

| AT80C32X2-3CSUV            | ROMLess     | 5V ±10%         | Industrial & Green   | 60 MHz <sup>(3)</sup> | PDIL40  | Stick   |

| AT80C32X2-SLSUV            | ROMLess     | 5V ±10%         | Industrial & Green   | 60 MHz <sup>(3)</sup> | PLCC44  | Stick   |

| AT80C32X2-RLTUV            | ROMLess     | 5V ±10%         | Industrial & Green   | 60 MHz <sup>(3)</sup> | VQFP44  | Tray    |

|                            |             |                 |                      |                       |         |         |

| TS80C52X2zzz-MCA           | 8K ROM      | 2.7 to 5.5V     | Commercial           | 40 MHz <sup>(1)</sup> | PDIL40  | Stick   |

| TS80C52X2zzz-MCB           | 8K ROM      | 2.7 to 5.5V     | Commercial           | 40 MHz <sup>(1)</sup> | PLCC44  | Stick   |

| TS80C52X2zzz-MCC           | 8K ROM      | 2.7 to 5.5V     | Commercial           | 40 MHz <sup>(1)</sup> | PQFP44  | Tray    |

| TS80C52X2zzz-MCE           | 8K ROM      | 2.7 to 5.5V     | Commercial           | 40 MHz <sup>(1)</sup> | VQFP44  | Tray    |

| TS80C52X2zzz-LCA           | 8K ROM      | 2.7 to 5.5V     | Commercial           | 30 MHz <sup>(1)</sup> | PDIL40  | Stick   |

| TS80C52X2zzz-LCB           | 8K ROM      | 2.7 to 5.5V     | Commercial           | 30 MHz <sup>(1)</sup> | PLCC44  | Stick   |

| TS80C52X2zzz-LCC           | 8K ROM      | 2.7 to 5.5V     | Commercial           | 30 MHz <sup>(1)</sup> | PQFP44  | Tray    |

| TS80C52X2zzz-LCE           | 8K ROM      | 2.7 to 5.5V     | Commercial           | 30 MHz <sup>(1)</sup> | VQFP44  | Tray    |

| TS80C52X2zzz-VCA           | 8K ROM      | 5V <u>±</u> 10% | Commercial           | 60 MHz <sup>(3)</sup> | PDIL40  | Stick   |

| TS80C52X2zzz-VCB           | 8K ROM      | 5V ±10%         | Commercial           | 60 MHz <sup>(3)</sup> | PLCC44  | Stick   |

| TS80C52X2zzz-VCC           | 8K ROM      | 5V ±10%         | Commercial           | 60 MHz <sup>(3)</sup> | PQFP44  | Tray    |

| TS80C52X2zzz-VCE           | 8K ROM      | 5V ±10%         | Commercial           | 60 MHz <sup>(3)</sup> | VQFP44  | Tray    |

| TS80C52X2zzz-MIA           | 8K ROM      | 5V ±10%         | Industrial           | 40 MHz <sup>(1)</sup> | PDIL40  | Stick   |

| TS80C52X2zzz-MIB           | 8K ROM      | 5V ±10%         | Industrial           | 40 MHz <sup>(1)</sup> | PLCC44  | Stick   |

| TS80C52X2zzz-MIC           | 8K ROM      | 5V ±10%         | Industrial           | 40 MHz <sup>(1)</sup> | PQFP44  | Tray    |

| TS80C52X2zzz-MIE           | 8K ROM      | 5V ±10%         | Industrial           | 40 MHz <sup>(1)</sup> | VQFP44  | Tray    |

| TS80C52X2zzz-LIA           | 8K ROM      | 2.7 to 5.5V     | Industrial           | 30 MHz <sup>(1)</sup> | PDIL40  | Stick   |

| TS80C52X2zzz-LIB           | 8K ROM      | 2.7 to 5.5V     | Industrial           | 30 MHz <sup>(1)</sup> | PLCC44  | Stick   |

| TS80C52X2zzz-LIC           | 8K ROM      | 2.7 to 5.5V     | Industrial           | 30 MHz <sup>(1)</sup> | PQFP44  | Tray    |

| TS80C52X2zzz-LIE           | 8K ROM      | 2.7 to 5.5V     | Industrial           | 30 MHz <sup>(1)</sup> | VQFP44  | Tray    |

| TS80C52X2zzz-VIA           | 8K ROM      | 5V ±10%         | Industrial           | 60 MHz <sup>(3)</sup> | PDIL40  | Stick   |

| TS80C52X2zzz-VIB           | 8K ROM      | 5V ±10%         | Industrial           | 60 MHz <sup>(3)</sup> | PLCC44  | Stick   |

| TS80C52X2zzz-VIC           | 8K ROM      | 5V ±10%         | Industrial           | 60 MHz <sup>(3)</sup> | PQFP44  | Tray    |

| TS80C52X2zzz-VIE           | 8K ROM      | 5V ±10%         | Industrial           | 60 MHz <sup>(3)</sup> | VQFP44  | Tray    |

|                            |             |                 |                      |                       |         |         |

| AT80C52X2zzz-3CSUM         | 8K ROM      | 5V ±10%         | Industrial & Green   | 40 MHz <sup>(1)</sup> | PDIL40  | Stick   |

| AT80C52X2zzz-SLSUM         | 8K ROM      | 5V ±10%         | Industrial & Green   | 40 MHz <sup>(1)</sup> | PLCC44  | Stick   |

| AT80C52X2zzz-RLTUM         | 8K ROM      | 5V ±10%         | Industrial & Green   | 40 MHz <sup>(1)</sup> | VQFP44  | Tray    |