Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detano                     |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                |

| Core Processor             | 80C51                                                                   |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 40/20MHz                                                                |

| Connectivity               | UART/USART                                                              |

| Peripherals                | POR                                                                     |

| Number of I/O              | 32                                                                      |

| Program Memory Size        | 8KB (8K x 8)                                                            |

| Program Memory Type        | OTP                                                                     |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 256 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                             |

| Data Converters            | -                                                                       |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 44-LCC (J-Lead)                                                         |

| Supplier Device Package    | 44-PLCC (16.6x16.6)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/ts87c52x2-mcb |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### SFR Mapping

The Special Function Registers (SFRs) of the TS80C52X2 fall into the following categories:

- C51 core registers: ACC, B, DPH, DPL, PSW, SP, AUXR1

- I/O port registers: P0, P1, P2, P3

- Timer registers: T2CON, T2MOD, TCON, TH0, TH1, TH2, TMOD, TL0, TL1, TL2, RCAP2L, RCAP2H

- Serial I/O port registers: SADDR, SADEN, SBUF, SCON

- Power and clock control registers: PCON

- Interrupt system registers: IE, IP, IPH

- Others: AUXR, CKCON

#### Table 2. All SFRs with their address and their reset value

|         | Bit<br>Addressable |                    | Non Bit Addressable |                     |                  |                  |                  |                    |     |  |

|---------|--------------------|--------------------|---------------------|---------------------|------------------|------------------|------------------|--------------------|-----|--|

|         | 0/8                | 1/9                | 2/A                 | 3/B                 | 4/C              | 5/D              | 6/E              | 7/F                |     |  |

| F8h     |                    |                    |                     |                     |                  |                  |                  |                    | FFh |  |

| F0h     | B<br>0000 0000     |                    |                     |                     |                  |                  |                  |                    | F7h |  |

| E8h     |                    |                    |                     |                     |                  |                  |                  |                    | EFh |  |

| E0h     | ACC<br>0000 0000   |                    |                     |                     |                  |                  |                  |                    | E7h |  |

| D8<br>h |                    |                    |                     |                     |                  |                  |                  |                    | DFh |  |

| D0<br>h | PSW<br>0000 0000   |                    |                     |                     |                  |                  |                  |                    | D7h |  |

| C8<br>h | T2CON<br>0000 0000 | T2MOD<br>XXXX XX00 | RCAP2L<br>0000 0000 | RCAP2H<br>0000 0000 | TL2<br>0000 0000 | TH2<br>0000 0000 |                  |                    | CFh |  |

| C0<br>h |                    |                    |                     |                     |                  |                  |                  |                    | C7h |  |

| B8h     | IP<br>XX00 0000    | SADEN<br>0000 0000 |                     |                     |                  |                  |                  |                    | BFh |  |

| B0h     | P3<br>1111 1111    |                    |                     |                     |                  |                  |                  | IPH<br>XX00 0000   | B7h |  |

| A8h     | IE<br>0X00 0000    | SADDR<br>0000 0000 |                     |                     |                  |                  |                  |                    | AFh |  |

| A0h     | P2<br>1111 1111    |                    | AUXR1<br>XXXX XXX0  |                     |                  |                  |                  |                    | A7h |  |

| 98h     | SCON<br>0000 0000  | SBUF<br>XXXX XXXX  |                     |                     |                  |                  |                  |                    | 9Fh |  |

| 90h     | P1<br>1111 1111    |                    |                     |                     |                  |                  |                  |                    | 97h |  |

| 88h     | TCON<br>0000 0000  | TMOD<br>0000 0000  | TL0<br>0000 0000    | TL1<br>0000 0000    | TH0<br>0000 0000 | TH1<br>0000 0000 | AUXR<br>XXXXXXX0 | CKCON<br>XXXX XXX0 | 8Fh |  |

| 80h     | P0<br>1111 1111    | SP<br>0000 0111    | DPL<br>0000 0000    | DPH<br>0000 0000    |                  |                  |                  | PCON<br>00X1 0000  | 87h |  |

|         | 0/8                | 1/9                | 2/A                 | 3/B                 | 4/C              | 5/D              | 6/E              | 7/F                |     |  |

Reserved

| Mnemonic           | I   | Pin Nu | mber        | Туре  | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------|-----|--------|-------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    | DIL | LCC    | VQFP<br>1.4 |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                    | 13  | 15     | 9           | I     | INT1 (P3.3): External interrupt 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                    | 14  | 16     | 10          | I     | T0 (P3.4): Timer 0 external input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                    | 15  | 17     | 11          | I     | T1 (P3.5): Timer 1 external input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                    | 16  | 18     | 12          | 0     | WR (P3.6): External data memory write strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                    | 17  | 19     | 13          | 0     | RD (P3.7): External data memory read strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Reset              | 9   | 10     | 4           | I     | <b>Reset:</b> A high on this pin for two machine cycles while the oscillator is running, resets the device. An internal diffused resistor to $V_{SS}$ permits a power-on reset using only an external capacitor to $V_{CC}$ .                                                                                                                                                                                                                                                                                                                                                                                                        |

| ALE/PROG           | 30  | 33     | 27          | O (I) | Address Latch Enable/Program Pulse: Output pulse for<br>latching the low byte of the address during an access to<br>external memory. In normal operation, ALE is emitted at a<br>constant rate of 1/6 (1/3 in X2 mode) the oscillator frequency,<br>and can be used for external timing or clocking. Note that one<br>ALE pulse is skipped during each access to external data<br>memory. This pin is also the program pulse input (PROG)<br>during EPROM programming. ALE can be disabled by setting<br>SFR's AUXR.0 bit. With this bit set, ALE will be inactive<br>during internal fetches.                                       |

| PSEN               | 29  | 32     | 26          | 0     | Program Store ENable: The read strobe to external program<br>memory. When executing code from the external program<br>memory, <u>PSEN</u> is activated twice each machine cycle, except<br>that two <u>PSEN</u> activations are skipped during each access to<br>external data memory. <u>PSEN</u> is not activated during fetches<br>from internal program memory.                                                                                                                                                                                                                                                                  |

| ĒĀ/V <sub>PP</sub> | 31  | 35     | 29          | I     | External Access Enable/Programming Supply Voltage:<br>EA must be externally held low to enable the device to fetch<br>code from external program memory locations 0000H and<br>3FFFH (RB) or 7FFFH (RC), or FFFFH (RD). If EA is held<br>high, the device executes from internal program memory<br>unless the program counter contains an address greater than<br>3FFFH (RB) or 7FFFH (RC) EA must be held low for<br>ROMless devices. This pin also receives the 12.75V<br>programming supply voltage (V <sub>PP</sub> ) during EPROM<br>programming. If security level 1 is programmed, EA will be<br>internally latched on Reset. |

| XTAL1              | 19  | 21     | 15          | I     | Crystal 1: Input to the inverting oscillator amplifier and input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                    |     |        |             |       | to the internal clock generator circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| XTAL2              | 18  | 20     | 14          | 0     | Crystal 2: Output from the inverting oscillator amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

### TS80C52X2 Enhanced Features

In comparison to the original 80C52, the TS80C52X2 implements some new features, which are:

- The X2 option

- The Dual Data Pointer

- The 4 level interrupt priority system

- The power-off flag

- The ONCE mode

- The ALE disabling

- Some enhanced features are also located in the UART and the Timer 2

**X2 Feature** The TS80C52X2 core needs only 6 clock periods per machine cycle. This feature called "X2" provides the following advantages:

- Divide frequency crystals by 2 (cheaper crystals) while keeping same CPU power

- Save power consumption while keeping same CPU power (oscillator power saving)

- Save power consumption by dividing dynamically operating frequency by 2 in operating and idle modes

- Increase CPU power by 2 while keeping same crystal frequency

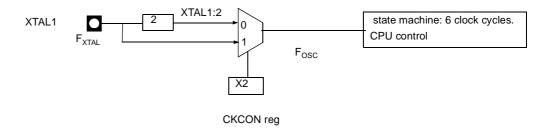

In order to keep the original C51 compatibility, a divider by 2 is inserted between the XTAL1 signal and the main clock input of the core (phase generator). This divider may be disabled by software.

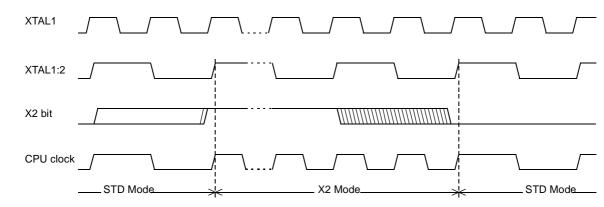

DescriptionThe clock for the whole circuit and peripheral is first divided by two before being used by<br/>the CPU core and peripherals. This allows any cyclic ratio to be accepted on XTAL1<br/>input. In X2 mode, as this divider is bypassed, the signals on XTAL1 must have a cyclic<br/>ratio between 40 to 60%. Figure 1. shows the clock generation block diagram. X2 bit is<br/>validated on XTAL1÷2 rising edge to avoid glitches when switching from X2 to STD<br/>mode. Figure 2 shows the mode switching waveforms.

Figure 1. Clock Generation Diagram

8

Figure 2. Mode Switching Waveforms

The X2 bit in the CKCON register (See Table 3.) allows to switch from 12 clock cycles per instruction to 6 clock cycles and vice versa. At reset, the standard speed is activated (STD mode). Setting this bit activates the X2 feature (X2 mode).

Note: In order to prevent any incorrect operation while operating in X2 mode, user must be aware that all peripherals using clock frequency as time reference (UART, timers) will have their time reference divided by two. For example a free running timer generating an interrupt every 20 ms will then generate an interrupt every 10 ms. UART with 4800 baud rate will have 9600 baud rate.

#### Table 3. CKCON Register

CKCON - Clock Control Register (8Fh)

| 7             | 6               | 5                         | 4                                                                               | 3                                              | 2              | 1            | 0  |  |  |  |  |

|---------------|-----------------|---------------------------|---------------------------------------------------------------------------------|------------------------------------------------|----------------|--------------|----|--|--|--|--|

| -             | -               | -                         | -                                                                               | -                                              | -              | -            | X2 |  |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description               | Description                                                                     |                                                |                |              |    |  |  |  |  |

| 7             | -               | Reserved<br>The value rea | ad from this b                                                                  | it is indetermi                                | nate. Do not s | et this bit. |    |  |  |  |  |

| 6             | -               | Reserved<br>The value rea | ad from this b                                                                  | it is indetermi                                | nate. Do not s | et this bit. |    |  |  |  |  |

| 5             | -               | Reserved<br>The value rea | ad from this b                                                                  | it is indetermi                                | nate. Do not s | et this bit. |    |  |  |  |  |

| 4             | -               | Reserved<br>The value rea | ad from this b                                                                  | it is indetermi                                | nate. Do not s | et this bit. |    |  |  |  |  |

| 3             | -               | Reserved<br>The value rea | ad from this b                                                                  | it is indetermi                                | nate. Do not s | et this bit. |    |  |  |  |  |

| 2             | -               | Reserved<br>The value rea | ad from this b                                                                  | it is indetermi                                | nate. Do not s | et this bit. |    |  |  |  |  |

| 1             | -               | Reserved<br>The value rea | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                                                |                |              |    |  |  |  |  |

| 0             | X2              |                           | ct 12 clock pe                                                                  | <b>k bit</b><br>riods per mac<br>ds per machin |                |              |    |  |  |  |  |

Reset Value = XXXX XXX0b

Not bit addressable

For further details on the X2 feature, please refer to ANM072 available on the web (http://www.atmel.com)

| Timer 2          | The timer 2 in the TS80C52X2 is compatible with the timer 2 in the 80C52.<br>It is a 16-bit timer/counter: the count is maintained by two eight-bit timer registers, TH2 and TL2, connected in cascade. It is controlled by T2CON register (See Table 5) and T2MOD register (See Table 6). Timer 2 operation is similar to Timer 0 and Timer 1. C/T2 selects $F_{OSC}/12$ (timer operation) or external pin T2 (counter operation) as the timer clock input. Setting TR2 allows TL2 to be incremented by the selected input. |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  | Timer 2 has 3 operating modes: capture, autoreload and Baud Rate <u>Generator</u> . These modes are selected by the combination of RCLK, TCLK and CP/RL2 (T2CON), as described in the Atmel 8-bit Microcontroller Hardware description.                                                                                                                                                                                                                                                                                      |

|                  | Refer to the Atmel 8-bit Microcontroller Hardware description for the description of Cap-<br>ture and Baud Rate Generator Modes.                                                                                                                                                                                                                                                                                                                                                                                             |

|                  | In TS80C52X2 Timer 2 includes the following enhancements:                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                  | Auto-reload mode with up or down counter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                  | Programmable clock-output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Auto-reload Mode | The Auto-reload mode configures timer 2 as a 16-bit timer or event counter with auto-<br>matic reload. If DCEN bit in T2MOD is cleared, timer 2 behaves as in 80C52 (refer to the<br>Atmel 8-bit Microcontroller Hardware description). If DCEN bit is set, timer 2 acts as an<br>Up/down timer/counter as shown in Figure 4. In this mode the T2EX pin controls the<br>direction of count.                                                                                                                                  |

|                  | When T2EX is high, timer 2 counts up. Timer overflow occurs at FFFFh which sets the TF2 flag and generates an interrupt request. The overflow also causes the 16-bit value in RCAP2H and RCAP2L registers to be loaded into the timer registers TH2 and TL2.                                                                                                                                                                                                                                                                 |

|                  | When T2EX is low, timer 2 counts down. Timer underflow occurs when the count in the timer registers TH2 and TL2 equals the value stored in RCAP2H and RCAP2L registers. The underflow sets TF2 flag and reloads FFFFh into the timer registers.                                                                                                                                                                                                                                                                              |

|                  | The EXF2 bit toggles when timer 2 overflows or underflows according to the the direc-<br>tion of the count. EXF2 does not generate any interrupt. This bit can be used to provide                                                                                                                                                                                                                                                                                                                                            |

17-bit resolution.

12 **TS8xCx2X2**

| Table 5 | T2CON | Register |

|---------|-------|----------|

|---------|-------|----------|

T2CON - Timer 2 Control Register (C8h)

| 7             | 6               | 5                                                                                                   | 4                                                                                                                                                                                                                                                                                                                 | 3                                   | 2               | 1               | 0       |  |  |  |

|---------------|-----------------|-----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-----------------|-----------------|---------|--|--|--|

| TF2           | EXF2            | RCLK                                                                                                | TCLK                                                                                                                                                                                                                                                                                                              | EXEN2                               | TR2             | C/T2#           | CP/RL2# |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                         |                                                                                                                                                                                                                                                                                                                   |                                     |                 |                 |         |  |  |  |

| 7             | TF2             | Must be cleare                                                                                      | <b>Timer 2 overflow Flag</b><br>Must be cleared by software.<br>Set by hardware on timer 2 overflow, if RCLK = 0 and TCLK = 0.                                                                                                                                                                                    |                                     |                 |                 |         |  |  |  |

| 6             | EXF2            | Set when a ca<br>EXEN2=1.<br>When set, cau<br>interrupt is ena                                      | Timer 2 External Flag<br>Set when a capture or a reload is caused by a negative transition on T2EX pin if<br>EXEN2=1.<br>When set, causes the CPU to vector to timer 2 interrupt routine when timer 2<br>interrupt is enabled.<br>Must be cleared by software. EXF2 doesn't cause an interrupt in Up/down counter |                                     |                 |                 |         |  |  |  |

| 5             | RCLK            | Receive Clock<br>Clear to use time<br>Set to use time                                               | mer 1 overflov                                                                                                                                                                                                                                                                                                    |                                     |                 | •               |         |  |  |  |

| 4             | TCLK            | Transmit Cloc<br>Clear to use tin<br>Set to use time                                                | mer 1 overflov                                                                                                                                                                                                                                                                                                    |                                     |                 | •               |         |  |  |  |

| 3             | EXEN2           | Timer 2 Exter<br>Clear to ignore<br>Set to cause a<br>detected, if tim                              | e events on Ta<br>capture or re                                                                                                                                                                                                                                                                                   | 2EX pin for tim<br>load when a n    | egative transi  |                 | pin is  |  |  |  |

| 2             | TR2             | Timer 2 Run of<br>Clear to turn of<br>Set to turn on                                                | ff timer 2.                                                                                                                                                                                                                                                                                                       |                                     |                 |                 |         |  |  |  |

| 1             | C/T2#           | Clear for timer<br>Set for counter                                                                  | <b>Timer/Counter 2 select bit</b><br>Clear for timer operation (input from internal clock system: F <sub>OSC</sub> ).<br>Set for counter operation (input from T2 input pin, falling edge trigger). Must be 0<br>for clock out mode.                                                                              |                                     |                 |                 |         |  |  |  |

| 0             | CP/RL2#         | Timer 2 Captu<br>If RCLK=1 or 7<br>timer 2 overflo<br>Clear to Auto-r<br>EXEN2=1.<br>Set to capture | CLK=1, CP/F<br>w.<br>eload on time                                                                                                                                                                                                                                                                                | RL2# is ignored<br>er 2 overflows o | or negative tra | ansitions on T2 |         |  |  |  |

Reset Value = 0000 0000b Bit addressable

#### Table 6. T2MOD Register

T2MOD - Timer 2 Mode Control Register (C9h)

| 7             | 6               | 5                                | 4                                                                                                                                   | 3                                 | 2               | 1            | 0    |  |  |

|---------------|-----------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-----------------|--------------|------|--|--|

| -             | -               | -                                | -                                                                                                                                   | -                                 | -               | T2OE         | DCEN |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                      |                                                                                                                                     |                                   |                 |              |      |  |  |

| 7             | -               | <b>Reserved</b><br>The value rea | ad from this b                                                                                                                      | it is indetermir                  | nate. Do not s  | et this bit. |      |  |  |

| 6             | -               | <b>Reserved</b><br>The value rea | ad from this b                                                                                                                      | it is indetermir                  | nate. Do not s  | et this bit. |      |  |  |

| 5             | -               | <b>Reserved</b><br>The value rea | ad from this b                                                                                                                      | it is indetermir                  | nate. Do not s  | et this bit. |      |  |  |

| 4             | -               | Reserved<br>The value rea        | ad from this b                                                                                                                      | it is indetermir                  | nate. Do not se | et this bit. |      |  |  |

| 3             | -               | <b>Reserved</b><br>The value rea | ad from this b                                                                                                                      | it is indetermir                  | nate. Do not s  | et this bit. |      |  |  |

| 2             | -               | <b>Reserved</b><br>The value rea | ad from this b                                                                                                                      | it is indetermir                  | nate. Do not s  | et this bit. |      |  |  |

| 1             | T2OE            | Clear to prog                    | <b>Timer 2 Output Enable bit</b><br>Clear to program P1.0/T2 as clock input or I/O port.<br>Set to program P1.0/T2 as clock output. |                                   |                 |              |      |  |  |

| 0             | DCEN            | Clear to disa                    |                                                                                                                                     | t<br>up/down cou<br>b/down counte |                 |              |      |  |  |

Reset Value = XXXX XX00b Not bit addressable 1111 0000b).

For slave A, bit 1 is a 1; for slaves B and C, bit 1 is a don't care bit. To communicate with slaves B and C, but not slave A, the master must send an address with bits 0 and 1 both set (e.g. 1111 0011b).

To communicate with slaves A, B and C, the master must send an address with bit 0 set, bit 1 clear, and bit 2 clear (e.g. 1111 0001b).

**Broadcast Address** A broadcast address is formed from the logical OR of the SADDR and SADEN registers with zeros defined as don't-care bits, e.g.:

SADDR 0101 0110b SADEN 1111 1100b Broadcast =SADDR OR SADEN1111 111Xb

The use of don't-care bits provides flexibility in defining the broadcast address, however in most applications, a broadcast address is FFh. The following is an example of using broadcast addresses:

Slave A:SADDR1111 0001b <u>SADEN1111 1010b</u> Broadcast1111 1X11b, Slave B:SADDR1111 0011b <u>SADEN1111 1001b</u> Broadcast1111 1X11B,

Slave C:SADDR=1111 0010b <u>SADEN1111 1101b</u> Broadcast1111 1111b

For slaves A and B, bit 2 is a don't care bit; for slave C, bit 2 is set. To communicate with all of the slaves, the master must send an address FFh. To communicate with slaves A and B, but not slave C, the master can send and address FBh.

Reset AddressesOn reset, the SADDR and SADEN registers are initialized to 00h, i.e. the given and<br/>broadcast addresses are XXXX XXXb (all don't-care bits). This ensures that the serial<br/>port will reply to any address, and so, that it is backwards compatible with the 80C51<br/>microcontrollers that do not support automatic address recognition.

Table 7.

SADEN Register

| 7                                   | 6          | 5           | 4             | 3 | 2        | 1 | 0 |

|-------------------------------------|------------|-------------|---------------|---|----------|---|---|

|                                     |            |             |               |   |          |   |   |

| Decet Valu                          |            | 0006        |               |   | <u>.</u> |   |   |

| Reset Valu                          |            | 0000        |               |   |          |   |   |

| Not bit add                         | ressable   |             |               |   |          |   |   |

|                                     |            |             |               |   |          |   |   |

|                                     |            |             |               |   |          |   |   |

| Table 8 S                           |            | vietor      |               |   |          |   |   |

|                                     | -          |             |               |   |          |   |   |

|                                     | -          |             | er (A9h)      |   |          |   |   |

| <b>Table 8.</b> S<br>SADDR - S<br>7 | -          |             | er (A9h)<br>4 | 3 | 2        | 1 | 0 |

| SADDR - S                           | lave Addre | ess Registe | er (A9h)<br>4 | 3 | 2        | 1 | 0 |

| SADDR - S                           | lave Addre | ess Registe | er (A9h)<br>4 | 3 | 2        | 1 | 0 |

Not bit addressable

**Table 10.** PCON RegisterPCON - Power Control Register (87h)

| 7             | 6               | 5                     | 4                                                                                                                   | 3                                | 2               | 1              | 0             |  |  |

|---------------|-----------------|-----------------------|---------------------------------------------------------------------------------------------------------------------|----------------------------------|-----------------|----------------|---------------|--|--|

| SMOD1         | SMOD0           | -                     | POF                                                                                                                 | GF1                              | GF0             | PD             | IDL           |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Descriptio            | n                                                                                                                   |                                  |                 |                |               |  |  |

| 7             | SMOD1           |                       | t <b>Mode bit 1</b><br>act double bau                                                                               | ud rate in mode                  | e 1, 2 or 3.    |                |               |  |  |

| 6             | SMOD0           | Clear to se           |                                                                                                                     | n SCON regist<br>SCON registe    |                 |                |               |  |  |

| 5             | -               | Reserved<br>The value | read from this                                                                                                      | bit is indeterm                  | ninate. Do not  | set this bit.  |               |  |  |

| 4             | POF             |                       | cognize next i<br>dware when V                                                                                      | reset type.<br>/CC rises from    | 0 to its nomina | al voltage. Ca | n also be set |  |  |

| 3             | GF1             | Cleared by            |                                                                                                                     | eral purpose us<br>purpose usage |                 |                |               |  |  |

| 2             | GF0             | Cleared by            | <b>General purpose Flag</b><br>Cleared by user for general purpose usage.<br>Set by user for general purpose usage. |                                  |                 |                |               |  |  |

| 1             | PD              | Cleared by            | Power-down mode bit<br>Cleared by hardware when reset occurs.<br>Set to enter power-down mode.                      |                                  |                 |                |               |  |  |

| 0             | IDL             | -                     |                                                                                                                     | i interrupt or re                | eset occurs.    |                |               |  |  |

Reset Value = 00X1 0000b Not bit addressable

Power-off flag reset value will be 1 only after a power on (cold reset). A warm reset doesn't affect the value of this bit.

**Table 13.** IP RegisterIP - Interrupt Priority Register (B8h)

| 7             | 6               | 5                     | 4                                        | 3                                 | 2              | 1             | 0   |  |  |  |

|---------------|-----------------|-----------------------|------------------------------------------|-----------------------------------|----------------|---------------|-----|--|--|--|

| -             | -               | PT2                   | PS                                       | PT1                               | PX1            | PT0           | PX0 |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Descriptio            | Description                              |                                   |                |               |     |  |  |  |

| 7             | -               | Reserved<br>The value | read from this                           | bit is indetern                   | ninate. Do not | set this bit. |     |  |  |  |

| 6             | -               | Reserved<br>The value | read from this                           | bit is indetern                   | ninate. Do not | set this bit. |     |  |  |  |

| 5             | PT2             |                       | erflow interr<br>2H for priority         | <b>upt Priority b</b><br>y level. | it             |               |     |  |  |  |

| 4             | PS              |                       | t <b>Priority bit</b><br>SH for priority | level.                            |                |               |     |  |  |  |

| 3             | PT1             |                       | erflow interr                            | <b>upt Priority b</b><br>y level. | it             |               |     |  |  |  |

| 2             | PX1             |                       | nterrupt 1 Pri                           | •                                 |                |               |     |  |  |  |

| 1             | PT0             |                       | erflow interr                            | <b>upt Priority b</b><br>y level. | it             |               |     |  |  |  |

| 0             | PX0             |                       | nterrupt 0 Pri                           |                                   |                |               |     |  |  |  |

Reset Value = XX00 0000b Bit addressable

# Table 14.IPH RegisterIPH - Interrupt Priority High Register (B7h)

| 7             | 6               | 5                                                                                                                                        | 4                                                                               | 3                           | 2              | 1           | 0    |  |  |

|---------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-----------------------------|----------------|-------------|------|--|--|

| -             | -               | PT2H                                                                                                                                     | PSH                                                                             | PT1H                        | PX1H           | РТОН        | РХОН |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                              |                                                                                 |                             |                |             |      |  |  |

| 7             | -               | Reserved<br>The value rea                                                                                                                | ad from this bit                                                                | t is indetermina            | ate. Do not se | t this bit. |      |  |  |

| 6             | -               | Reserved<br>The value rea                                                                                                                | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                             |                |             |      |  |  |

| 5             | PT2H            | Timer 2 over           PT2H         PT2           0         0           1         0           1         1                                |                                                                                 | t Priority Higl<br><u>회</u> | n bit          |             |      |  |  |

| 4             | PSH             | Serial port P           PSH         PS           0         0           1         0           1         1                                 | riority High b<br>Priority Leve<br>Lowest<br>Highest                            |                             |                |             |      |  |  |

| 3             | PT1H            | Timer 1 over           PT1H         PT1           0         0           1         0           1         1                                |                                                                                 | t Priority Higi<br>키        | n bit          |             |      |  |  |

| 2             | PX1H            |                                                                                                                                          | Priority Leve<br>Driority Leve<br>Lowest<br>Highest                             |                             |                |             |      |  |  |

| 1             | PT0H            |                                                                                                                                          | flow interrup<br>Priority Leve<br>Lowest<br>Highest                             | t Priority Higl<br>한        | n bit          |             |      |  |  |

| 0             | PX0H            | External interpretent           PX0H         PX0           0         0           0         1           1         0           1         1 | <b>Priority Leve</b><br><u>Priority Leve</u><br>Lowest<br>Highest               | ty High bit<br><u>키</u>     |                |             |      |  |  |

Reset Value = XX00 0000b Not bit addressable

Exit from power-down by reset redefines all the SFRs, exit from power-down by external interrupt does no affect the SFRs.

Exit from power-down by either reset or external interrupt does not affect the internal RAM content.

Note: If idle mode is activated with power-down mode (IDL and PD bits set), the exit sequence is unchanged, when execution is vectored to interrupt, PD and IDL bits are cleared and idle mode is not entered.

| Mode          | Program<br>Memory | ALE | PSEN | PORT0                       | PORT1     | PORT2     | PORT3     |

|---------------|-------------------|-----|------|-----------------------------|-----------|-----------|-----------|

| Idle          | Internal          | 1   | 1    | Port<br>Data <sup>(1)</sup> | Port Data | Port Data | Port Data |

| Idle          | External          | 1   | 1    | Floating                    | Port Data | Address   | Port Data |

| Power<br>Down | Internal          | 0   | 0    | Port<br>Data <sup>(1)</sup> | Port Data | Port Data | Port Data |

| Power<br>Down | External          | 0   | 0    | Floating                    | Port Data | Port Data | Port Data |

**Table 15.** The State of Ports During Idle and Power-down Modes

Note: 1. Port 0 can force a "zero" level. A "one" will leave port floating.

### **Reduced EMI Mode**

The ALE signal is used to demultiplex address and data buses on port 0 when used with external program or data memory. Nevertheless, during internal code execution, ALE signal is still generated. In order to reduce EMI, ALE signal can be disabled by setting AO bit.

The AO bit is located in AUXR register at bit location 0. As soon as AO is set, ALE is no longer output but remains active during MOVX and MOVC instructions and external fetches. During ALE disabling, ALE pin is weakly pulled high.

#### Table 18. AUXR Register

AUXR - Auxiliary Register (8Eh)

| 7             | 6               | 5                                | 4                                                                               | 3                                  | 2              | 1            | 0  |  |  |  |

|---------------|-----------------|----------------------------------|---------------------------------------------------------------------------------|------------------------------------|----------------|--------------|----|--|--|--|

| -             | -               | -                                | -                                                                               | -                                  | -              | -            | AO |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                      | Description                                                                     |                                    |                |              |    |  |  |  |

| 7             | -               | Reserved<br>The value rea        | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                                    |                |              |    |  |  |  |

| 6             | -               | <b>Reserved</b><br>The value rea | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                                    |                |              |    |  |  |  |

| 5             | -               | <b>Reserved</b><br>The value rea | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                                    |                |              |    |  |  |  |

| 4             | -               | <b>Reserved</b><br>The value rea | ad from this b                                                                  | it is indetermi                    | nate. Do not s | et this bit. |    |  |  |  |

| 3             | -               | Reserved<br>The value rea        | ad from this b                                                                  | it is indetermi                    | nate. Do not s | et this bit. |    |  |  |  |

| 2             | -               | Reserved<br>The value rea        | ad from this b                                                                  | it is indetermi                    | nate. Do not s | et this bit. |    |  |  |  |

| 1             | -               | Reserved<br>The value rea        | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                                    |                |              |    |  |  |  |

| 0             | AO              |                                  | ore ALE operation                                                               | ation during in<br>ion during inte |                |              |    |  |  |  |

Reset Value = XXXX XXX0b Not bit addressable

## Electrical Characteristics

# Absolute Maximum Ratings<sup>(1)</sup>

| Ambiant Temperature Under Bias:               |                                |

|-----------------------------------------------|--------------------------------|

| C = commercial                                | 0°C to 70°C                    |

| I = industrial                                | 40°C to 85°C                   |

| Storage Temperature                           | 65°C to + 150°C                |

| Voltage on V <sub>CC</sub> to V <sub>SS</sub> | 0.5V to + 7 V                  |

| Voltage on V <sub>PP</sub> to V <sub>SS</sub> | 0.5V to + 13 V                 |

| Voltage on Any Pin to V <sub>SS</sub>         | 0.5V to V <sub>CC</sub> + 0.5V |

| Power Dissipation                             | 1 W <sup>(2)</sup>             |

|                                               |                                |

|                                               |                                |

- Notes: 1. Stresses at or above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- 2. This value is based on the maximum allowable die temperature and the thermal resistance of the package.

**Power Consumption Measurement** Since the introduction of the first C51 devices, every manufacturer made operating lcc measurements under reset, which made sense for the designs were the CPU was running under reset. In Atmel new devices, the CPU is no more active during reset, so the power consumption is very low but is not really representative of what will happen in the customer system. That's why, while keeping measurements under Reset, Atmel presents a new way to measure the operating lcc:

Using an internal test ROM, the following code is executed:

Label: SJMP Label (80 FE)

Ports 1, 2, 3 are disconnected, Port 0 is tied to FFh, EA = Vcc, RST = Vss, XTAL2 is not connected and XTAL1 is driven by the clock.

This is much more representative of the real operating Icc.

| DC Parameters for | TA = 0°C to +70°C; $V_{SS}$ = 0 V; $V_{CC}$ = 5V ± 10%; F = 0 to 40 MHz.       |

|-------------------|--------------------------------------------------------------------------------|

| Standard Voltage  | TA = -40°C to +85°C; $V_{SS} = 0$ V; $V_{CC} = 5V \pm 10\%$ ; F = 0 to 40 MHz. |

| Table 22. | DC Parameters | in | Standard | Voltage |

|-----------|---------------|----|----------|---------|

|-----------|---------------|----|----------|---------|

| Symbol           | Parameter                                        | Min                       | Тур | Max                       | Unit        | Test Conditions                                                                          |

|------------------|--------------------------------------------------|---------------------------|-----|---------------------------|-------------|------------------------------------------------------------------------------------------|

| V <sub>IL</sub>  | Input Low Voltage                                | -0.5                      |     | 0.2 V <sub>CC</sub> - 0.1 | V           |                                                                                          |

| V <sub>IH</sub>  | Input High Voltage except XTAL1, RST             | 0.2 V <sub>CC</sub> + 0.9 |     | V <sub>CC</sub> + 0.5     | V           |                                                                                          |

| V <sub>IH1</sub> | Input High Voltage, XTAL1, RST                   | 0.7 V <sub>CC</sub>       |     | V <sub>CC</sub> + 0.5     | V           |                                                                                          |

| V <sub>OL</sub>  | Output Low Voltage, ports 1, 2, 3 <sup>(6)</sup> |                           |     | 0.3<br>0.45<br>1.0        | V<br>V<br>V | $I_{OL} = 100 \ \mu A^{(4)}$<br>$I_{OL} = 1.6 \ m A^{(4)}$<br>$I_{OL} = 3.5 \ m A^{(4)}$ |

| V <sub>OL1</sub> | Output Low Voltage, port 0 <sup>(6)</sup>        |                           |     | 0.3<br>0.45<br>1.0        | V<br>V<br>V | $I_{OL} = 200 \ \mu A^{(4)}$<br>$I_{OL} = 3.2 \ m A^{(4)}$<br>$I_{OL} = 7.0 \ m A^{(4)}$ |

| V <sub>OL2</sub> | Output Low Voltage, ALE, PSEN                    |                           |     | 0.3<br>0.45<br>1.0        | V<br>V<br>V | $I_{OL} = 100 \ \mu A^{(4)}$ $I_{OL} = 1.6 \ m A^{(4)}$ $I_{OL} = 3.5 \ m A^{(4)}$       |

# TS8xCx2X2

| Table 22. DC Parameters in Standard Voltage (Continued | Table 22. | eters in Standard Voltage (Continued) |

|--------------------------------------------------------|-----------|---------------------------------------|

|--------------------------------------------------------|-----------|---------------------------------------|

| Symbol                            | Parameter                                         | Min                                                                     | Тур               | Мах                                                   | Unit        | Test Conditions                                                                                                   |

|-----------------------------------|---------------------------------------------------|-------------------------------------------------------------------------|-------------------|-------------------------------------------------------|-------------|-------------------------------------------------------------------------------------------------------------------|

| V <sub>OH</sub>                   | Output High Voltage, ports 1, 2, 3                | V <sub>CC</sub> - 0.3<br>V <sub>CC</sub> - 0.7<br>V <sub>CC</sub> - 1.5 |                   |                                                       | V<br>V<br>V | I <sub>OH</sub> = -10 μA<br>I <sub>OH</sub> = -30 μA<br>I <sub>OH</sub> = -60 μA<br>V <sub>CC</sub> = 5V ± 10%    |

| V <sub>OH1</sub>                  | Output High Voltage, port 0                       | V <sub>CC</sub> - 0.3<br>V <sub>CC</sub> - 0.7<br>V <sub>CC</sub> - 1.5 |                   |                                                       | V<br>V<br>V | I <sub>OH</sub> = -200 μA<br>I <sub>OH</sub> = -3.2 mA<br>I <sub>OH</sub> = -7.0 mA<br>V <sub>CC</sub> = 5V ± 10% |

| V <sub>OH2</sub>                  | Output High Voltage,ALE, PSEN                     | V <sub>CC</sub> - 0.3<br>V <sub>CC</sub> - 0.7<br>V <sub>CC</sub> - 1.5 |                   |                                                       | V<br>V<br>V | $I_{OH}$ = -100 µA<br>$I_{OH}$ = -1.6 mA<br>$I_{OH}$ = -3.5 mA<br>$V_{CC}$ = 5V ± 10%                             |

| R <sub>RST</sub>                  | RST Pulldown Resistor                             | 50                                                                      | 90 <sup>(5)</sup> | 200                                                   | kΩ          |                                                                                                                   |

| I <sub>IL</sub>                   | Logical 0 Input Current ports 1, 2 and 3          |                                                                         |                   | -50                                                   | μΑ          | Vin = 0.45V                                                                                                       |

| ILI                               | Input Leakage Current                             |                                                                         |                   | ±10                                                   | μΑ          | $0.45V < Vin < V_{CC}$                                                                                            |

| I <sub>TL</sub>                   | Logical 1 to 0 Transition Current, ports 1, 2, 3  |                                                                         |                   | -650                                                  | μΑ          | Vin = 2.0 V                                                                                                       |

| C <sub>IO</sub>                   | Capacitance of I/O Buffer                         |                                                                         |                   | 10                                                    | pF          | Fc = 1 MHz<br>TA = 25°C                                                                                           |

| I <sub>PD</sub>                   | Power Down Current                                |                                                                         | 20 (5)            | 50                                                    | μΑ          | $2.0~{\rm V} < {\rm V_{CC}}_< 5.5 {\rm V}^{(3)}$                                                                  |

| I <sub>CC</sub><br>under<br>RESET | Power Supply Current Maximum values, X1 mode: (7) |                                                                         |                   | 1 + 0.4 Freq<br>(MHz)<br>at12MHz 5.8<br>at16MHz 7.4   | mA          | $V_{\rm CC} = 5.5 V^{(1)}$                                                                                        |

| I <sub>CC</sub><br>operating      | Power Supply Current Maximum values, X1 mode: (7) |                                                                         |                   | 3 + 0.6 Freq<br>(MHz)<br>at12MHz 10.2<br>at16MHz 12.6 | mA          | $V_{CC} = 5.5 V^{(8)}$                                                                                            |

| l <sub>cc</sub><br>idle           | Power Supply Current Maximum values, X1 mode: (7) |                                                                         |                   | 0.25+0.3 Freq<br>(MHz)<br>at12MHz 3.9<br>at16MHz 5.1  | mA          | $V_{\rm CC} = 5.5 V^{(2)}$                                                                                        |

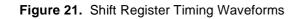

| Symbol            | Туре | Standard<br>Clock | X2 Clock | -М  | -V  | -L  | Units |

|-------------------|------|-------------------|----------|-----|-----|-----|-------|

| T <sub>XLXL</sub> | Min  | 12 T              | 6 T      |     |     |     | ns    |

| T <sub>QVHX</sub> | Min  | 10 T - x          | 5 T - x  | 50  | 50  | 50  | ns    |

| T <sub>XHQX</sub> | Min  | 2 T - x           | T - x    | 20  | 20  | 20  | ns    |

| T <sub>XHDX</sub> | Min  | х                 | х        | 0   | 0   | 0   | ns    |

| T <sub>XHDV</sub> | Max  | 10 T - x          | 5 T- x   | 133 | 133 | 133 | ns    |

Table 34. AC Parameters for a Variable Clock: Derating Formula

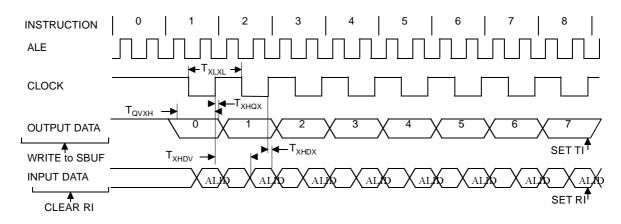

# Shift Register Timing Waveforms

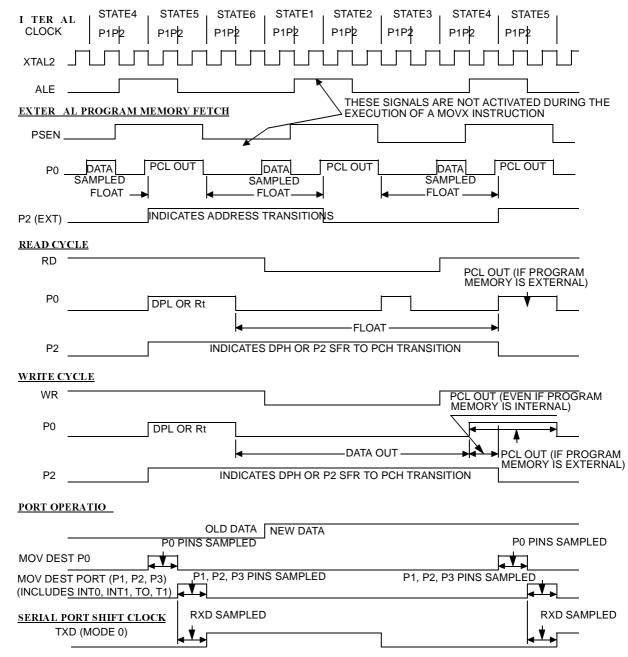

Figure 26. Clock Waveforms

This diagram indicates when signals are clocked internally. The time it takes the signals to propagate to the pins, however, ranges from 25 to 125 ns. This propagation delay is dependent on variables such as temperature and pin loading. Propagation also varies from output to output and component. Typically though ( $T_A = 25^{\circ}C$  fully loaded) RD and WR propagation delays are approximately 50ns. The other signals are typically 85 ns. Propagation delays are incorporated in the AC specifications.

# **Ordering Information**

#### Table 37. Possible Ordering Entries

| Part Number <sup>(3)</sup> | Memory Size | Supply Voltage  | Temperature<br>Range | Max Frequency         | Package | Packing     |

|----------------------------|-------------|-----------------|----------------------|-----------------------|---------|-------------|

| TS80C32X2-MCA              | ROMLess     | 5V <u>±</u> 10% | Commercial           | 40 MHz <sup>(1)</sup> | PDIL40  | Stick       |

| TS80C32X2-MCB              | ROMLess     | 5V <u>±</u> 10% | Commercial           | 40 MHz <sup>(1)</sup> | PLCC44  | Stick       |

| TS80C32X2-MCC              | ROMLess     | 5V <u>±</u> 10% | Commercial           | 40 MHz <sup>(1)</sup> | PQFP44  | Tray        |

| TS80C32X2-MCE              | ROMLess     | 5V <u>±</u> 10% | Commercial           | 40 MHz <sup>(1)</sup> | VQFP44  | Tray        |

| TS80C32X2-LCA              | ROMLess     | 2.7 to 5.5V     | Commercial           | 30 MHz <sup>(1)</sup> | PDIL40  | Stick       |

| TS80C32X2-LCB              | ROMLess     | 2.7 to 5.5V     | Commercial           | 30 MHz <sup>(1)</sup> | PLCC44  | Stick       |

| TS80C32X2-LCC              | ROMLess     | 2.7 to 5.5V     | Commercial           | 30 MHz <sup>(1)</sup> | PQFP44  | Tray        |

| TS80C32X2-LCE              | ROMLess     | 2.7 to 5.5V     | Commercial           | 30 MHz <sup>(1)</sup> | VQFP44  | Tray        |

| TS80C32X2-VCA              | ROMLess     | 5V <u>±</u> 10% | Commercial           | 60 MHz <sup>(3)</sup> | PDIL40  | Stick       |

| TS80C32X2-VCB              | ROMLess     | 5V <u>±</u> 10% | Commercial           | 60 MHz <sup>(3)</sup> | PLCC44  | Stick       |

| TS80C32X2-VCC              | ROMLess     | 5V <u>±</u> 10% | Commercial           | 60 MHz <sup>(3)</sup> | PQFP44  | Tray        |

| TS80C32X2-VCE              | ROMLess     | 5V <u>±</u> 10% | Commercial           | 60 MHz <sup>(3)</sup> | VQFP44  | Tray        |

| TS80C32X2-MIA              | ROMLess     | 5V <u>±</u> 10% | Industrial           | 40 MHz <sup>(1)</sup> | PDIL40  | Stick       |

| TS80C32X2-MIB              | ROMLess     | 5V <u>±</u> 10% | Industrial           | 40 MHz <sup>(1)</sup> | PLCC44  | Stick       |

| TS80C32X2-MIC              | ROMLess     | 5V <u>±</u> 10% | Industrial           | 40 MHz <sup>(1)</sup> | PQFP44  | Tray        |

| TS80C32X2-MIE              | ROMLess     | 5V <u>±</u> 10% | Industrial           | 40 MHz <sup>(1)</sup> | VQFP44  | Tray        |

| TS80C32X2-LIA              | ROMLess     | 2.7 to 5.5V     | Industrial           | 30 MHz <sup>(1)</sup> | PDIL40  | Stick       |

| TS80C32X2-LIB              | ROMLess     | 2.7 to 5.5V     | Industrial           | 30 MHz <sup>(1)</sup> | PLCC44  | Stick       |

| TS80C32X2-LIC              | ROMLess     | 2.7 to 5.5V     | Industrial           | 30 MHz <sup>(1)</sup> | PQFP44  | Tray        |

| TS80C32X2-LIE              | ROMLess     | 2.7 to 5.5V     | Industrial           | 30 MHz <sup>(1)</sup> | VQFP44  | Tray        |

| TS80C32X2-VIA              | ROMLess     | 5V <u>±</u> 10% | Industrial           | 60 MHz <sup>(3)</sup> | PDIL40  | Stick       |

| TS80C32X2-VIB              | ROMLess     | 5V <u>±</u> 10% | Industrial           | 60 MHz <sup>(3)</sup> | PLCC44  | Stick       |

| TS80C32X2-VIC              | ROMLess     | 5V <u>±</u> 10% | Industrial           | 60 MHz <sup>(3)</sup> | PQFP44  | Tray        |

| TS80C32X2-VIE              | ROMLess     | 5V <u>±</u> 10% | Industrial           | 60 MHz <sup>(3)</sup> | VQFP44  | Tray        |

|                            |             |                 |                      |                       |         |             |

| AT80C32X2-3CSUM            | ROMLess     | 5V ±10%         | Industrial & Green   | 40 MHz <sup>(1)</sup> | PDIL40  | Stick       |

| AT80C32X2-SLSUM            | ROMLess     | 5V ±10%         | Industrial & Green   | 40 MHz <sup>(1)</sup> | PLCC44  | Stick       |

| AT80C32X2-RLTUM            | ROMLess     | 5V ±10%         | Industrial & Green   | 40 MHz <sup>(1)</sup> | VQFP44  | Tray        |

| AT80C32X2-RLTUM            | ROMLess     | 5V ±10%         | Industrial & Green   | 40 MHz <sup>(1)</sup> | VQFP44  | Tape & Reel |

| AT80C32X2-3CSUL            | ROMLess     | 2.7 to 5.5V     | Industrial & Green   | 30 MHz <sup>(1)</sup> | PDIL40  | Stick       |

| AT80C32X2-SLSUL            | ROMLess     | 2.7 to 5.5V     | Industrial & Green   | 30 MHz <sup>(1)</sup> | PLCC44  | Stick       |

#### Table 37. Possible Ordering Entries (Continued)

| Part Number <sup>(3)</sup> | Memory Size | Supply Voltage  | Temperature<br>Range | Max Frequency         | Package | Packing |

|----------------------------|-------------|-----------------|----------------------|-----------------------|---------|---------|

| AT80C32X2-RLTUL            | ROMLess     | 2.7 to 5.5V     | Industrial & Green   | 30 MHz <sup>(1)</sup> | VQFP44  | Tray    |

| AT80C32X2-3CSUV            | ROMLess     | 5V ±10%         | Industrial & Green   | 60 MHz <sup>(3)</sup> | PDIL40  | Stick   |

| AT80C32X2-SLSUV            | ROMLess     | 5V ±10%         | Industrial & Green   | 60 MHz <sup>(3)</sup> | PLCC44  | Stick   |

| AT80C32X2-RLTUV            | ROMLess     | 5V ±10%         | Industrial & Green   | 60 MHz <sup>(3)</sup> | VQFP44  | Tray    |

|                            |             |                 |                      |                       |         |         |

| TS80C52X2zzz-MCA           | 8K ROM      | 2.7 to 5.5V     | Commercial           | 40 MHz <sup>(1)</sup> | PDIL40  | Stick   |

| TS80C52X2zzz-MCB           | 8K ROM      | 2.7 to 5.5V     | Commercial           | 40 MHz <sup>(1)</sup> | PLCC44  | Stick   |

| TS80C52X2zzz-MCC           | 8K ROM      | 2.7 to 5.5V     | Commercial           | 40 MHz <sup>(1)</sup> | PQFP44  | Tray    |

| TS80C52X2zzz-MCE           | 8K ROM      | 2.7 to 5.5V     | Commercial           | 40 MHz <sup>(1)</sup> | VQFP44  | Tray    |

| TS80C52X2zzz-LCA           | 8K ROM      | 2.7 to 5.5V     | Commercial           | 30 MHz <sup>(1)</sup> | PDIL40  | Stick   |

| TS80C52X2zzz-LCB           | 8K ROM      | 2.7 to 5.5V     | Commercial           | 30 MHz <sup>(1)</sup> | PLCC44  | Stick   |

| TS80C52X2zzz-LCC           | 8K ROM      | 2.7 to 5.5V     | Commercial           | 30 MHz <sup>(1)</sup> | PQFP44  | Tray    |

| TS80C52X2zzz-LCE           | 8K ROM      | 2.7 to 5.5V     | Commercial           | 30 MHz <sup>(1)</sup> | VQFP44  | Tray    |

| TS80C52X2zzz-VCA           | 8K ROM      | 5V <u>±</u> 10% | Commercial           | 60 MHz <sup>(3)</sup> | PDIL40  | Stick   |

| TS80C52X2zzz-VCB           | 8K ROM      | 5V ±10%         | Commercial           | 60 MHz <sup>(3)</sup> | PLCC44  | Stick   |

| TS80C52X2zzz-VCC           | 8K ROM      | 5V ±10%         | Commercial           | 60 MHz <sup>(3)</sup> | PQFP44  | Tray    |

| TS80C52X2zzz-VCE           | 8K ROM      | 5V ±10%         | Commercial           | 60 MHz <sup>(3)</sup> | VQFP44  | Tray    |

| TS80C52X2zzz-MIA           | 8K ROM      | 5V ±10%         | Industrial           | 40 MHz <sup>(1)</sup> | PDIL40  | Stick   |

| TS80C52X2zzz-MIB           | 8K ROM      | 5V ±10%         | Industrial           | 40 MHz <sup>(1)</sup> | PLCC44  | Stick   |

| TS80C52X2zzz-MIC           | 8K ROM      | 5V ±10%         | Industrial           | 40 MHz <sup>(1)</sup> | PQFP44  | Tray    |

| TS80C52X2zzz-MIE           | 8K ROM      | 5V ±10%         | Industrial           | 40 MHz <sup>(1)</sup> | VQFP44  | Tray    |

| TS80C52X2zzz-LIA           | 8K ROM      | 2.7 to 5.5V     | Industrial           | 30 MHz <sup>(1)</sup> | PDIL40  | Stick   |

| TS80C52X2zzz-LIB           | 8K ROM      | 2.7 to 5.5V     | Industrial           | 30 MHz <sup>(1)</sup> | PLCC44  | Stick   |

| TS80C52X2zzz-LIC           | 8K ROM      | 2.7 to 5.5V     | Industrial           | 30 MHz <sup>(1)</sup> | PQFP44  | Tray    |

| TS80C52X2zzz-LIE           | 8K ROM      | 2.7 to 5.5V     | Industrial           | 30 MHz <sup>(1)</sup> | VQFP44  | Tray    |

| TS80C52X2zzz-VIA           | 8K ROM      | 5V ±10%         | Industrial           | 60 MHz <sup>(3)</sup> | PDIL40  | Stick   |

| TS80C52X2zzz-VIB           | 8K ROM      | 5V ±10%         | Industrial           | 60 MHz <sup>(3)</sup> | PLCC44  | Stick   |

| TS80C52X2zzz-VIC           | 8K ROM      | 5V ±10%         | Industrial           | 60 MHz <sup>(3)</sup> | PQFP44  | Tray    |

| TS80C52X2zzz-VIE           | 8K ROM      | 5V ±10%         | Industrial           | 60 MHz <sup>(3)</sup> | VQFP44  | Tray    |

|                            |             |                 |                      |                       |         |         |

| AT80C52X2zzz-3CSUM         | 8K ROM      | 5V ±10%         | Industrial & Green   | 40 MHz <sup>(1)</sup> | PDIL40  | Stick   |

| AT80C52X2zzz-SLSUM         | 8K ROM      | 5V ±10%         | Industrial & Green   | 40 MHz <sup>(1)</sup> | PLCC44  | Stick   |

| AT80C52X2zzz-RLTUM         | 8K ROM      | 5V ±10%         | Industrial & Green   | 40 MHz <sup>(1)</sup> | VQFP44  | Tray    |