Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | 80C51                                                                   |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 60/30MHz                                                                |

| Connectivity               | UART/USART                                                              |

| Peripherals                | POR                                                                     |

| Number of I/O              | 32                                                                      |

| Program Memory Size        | 8KB (8K x 8)                                                            |

| Program Memory Type        | OTP                                                                     |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 256 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                             |

| Data Converters            | -                                                                       |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                         |

| Mounting Type              | Through Hole                                                            |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                |

| Supplier Device Package    | 40-PDIL                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/ts87c52x2-vca |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## SFR Mapping

The Special Function Registers (SFRs) of the TS80C52X2 fall into the following categories:

- C51 core registers: ACC, B, DPH, DPL, PSW, SP, AUXR1

- I/O port registers: P0, P1, P2, P3

- Timer registers: T2CON, T2MOD, TCON, TH0, TH1, TH2, TMOD, TL0, TL1, TL2, RCAP2L, RCAP2H

- Serial I/O port registers: SADDR, SADEN, SBUF, SCON

- Power and clock control registers: PCON

- Interrupt system registers: IE, IP, IPH

- Others: AUXR, CKCON

#### Table 2. All SFRs with their address and their reset value

|         | Bit<br>Addressable |                    |                     | Nc                  | on Bit Addressal | ble              |                  |                    |     |

|---------|--------------------|--------------------|---------------------|---------------------|------------------|------------------|------------------|--------------------|-----|

|         | 0/8                | 1/9                | 2/A                 | 3/B                 | 4/C              | 5/D              | 6/E              | 7/F                |     |

| F8h     |                    |                    |                     |                     |                  |                  |                  |                    | FFh |

| F0h     | B<br>0000 0000     |                    |                     |                     |                  |                  |                  |                    | F7h |

| E8h     |                    |                    |                     |                     |                  |                  |                  |                    | EFh |

| E0h     | ACC<br>0000 0000   |                    |                     |                     |                  |                  |                  |                    | E7h |

| D8<br>h |                    |                    |                     |                     |                  |                  |                  |                    | DFh |

| D0<br>h | PSW<br>0000 0000   |                    |                     |                     |                  |                  |                  |                    | D7h |

| C8<br>h | T2CON<br>0000 0000 | T2MOD<br>XXXX XX00 | RCAP2L<br>0000 0000 | RCAP2H<br>0000 0000 | TL2<br>0000 0000 | TH2<br>0000 0000 |                  |                    | CFh |

| C0<br>h |                    |                    |                     |                     |                  |                  |                  |                    | C7h |

| B8h     | IP<br>XX00 0000    | SADEN<br>0000 0000 |                     |                     |                  |                  |                  |                    | BFh |

| B0h     | P3<br>1111 1111    |                    |                     |                     |                  |                  |                  | IPH<br>XX00 0000   | B7h |

| A8h     | IE<br>0X00 0000    | SADDR<br>0000 0000 |                     |                     |                  |                  |                  |                    | AFh |

| A0h     | P2<br>1111 1111    |                    | AUXR1<br>XXXX XXX0  |                     |                  |                  |                  |                    | A7h |

| 98h     | SCON<br>0000 0000  | SBUF<br>XXXX XXXX  |                     |                     |                  |                  |                  |                    | 9Fh |

| 90h     | P1<br>1111 1111    |                    |                     |                     |                  |                  |                  |                    | 97h |

| 88h     | TCON<br>0000 0000  | TMOD<br>0000 0000  | TL0<br>0000 0000    | TL1<br>0000 0000    | TH0<br>0000 0000 | TH1<br>0000 0000 | AUXR<br>XXXXXXX0 | CKCON<br>XXXX XXX0 | 8Fh |

| 80h     | P0<br>1111 1111    | SP<br>0000 0111    | DPL<br>0000 0000    | DPH<br>0000 0000    |                  |                  |                  | PCON<br>00X1 0000  | 87h |

|         | 0/8                | 1/9                | 2/A                 | 3/B                 | 4/C              | 5/D              | 6/E              | 7/F                |     |

Reserved

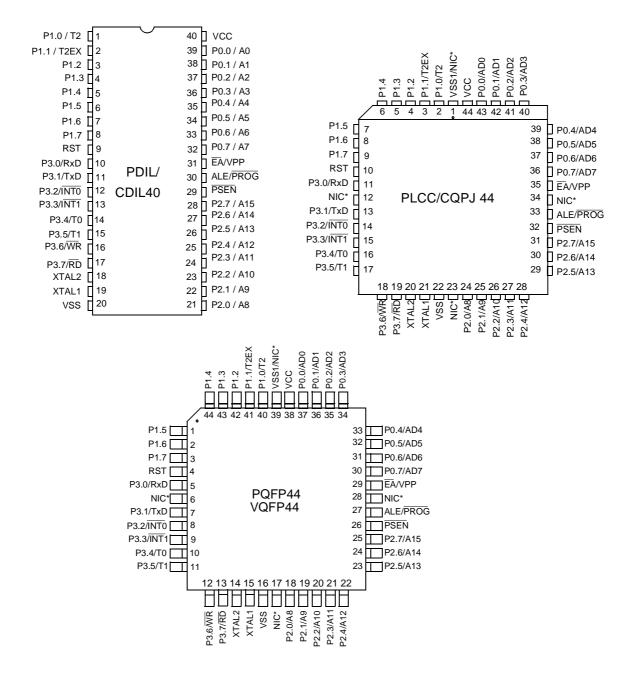

## **Pin Configuration**

\*NIC: No Internal Connection

| Mnemonic        | Pin Number |                  | Pin Number   |     | Туре                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Name and Function |  |

|-----------------|------------|------------------|--------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--|

|                 | DIL        | LCC              | VQFP<br>1.4  |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                   |  |

| V <sub>SS</sub> | 20         | 22               | 16           | I   | Ground: 0V reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                   |  |

| Vss1            |            | 1                | 39           | I   | Optional Ground: Contact the Sales Office for ground connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                   |  |

| V <sub>CC</sub> | 40         | 44               | 38           | I   | <b>Power Supply:</b> This is the power supply voltage for normal, idle and power-down operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                   |  |

| P0.0-P0.7       | 39-<br>32  | 43-<br>36        | 37-30        | I/O | <b>Port 0</b> : Port 0 is an open-drain, bidirectional I/O port. Port 0 pins that have 1s written to them float and can be used as high impedance inputs.Port 0 pins must be polarized to Vcc                                                                                                                                                                                                                                                                                                                                                                                                                         |                   |  |

|                 |            |                  |              |     | or Vss in order to prevent any parasitic current consumption.<br>Port 0 is also the multiplexed low-order address and data bus<br>during access to external program and data memory. In this<br>application, it uses strong internal pull-up when emitting 1s.<br>Port 0 also inputs the code bytes during EPROM<br>programming. External pull-ups are required during program<br>verification during which P0 outputs the code bytes.                                                                                                                                                                                |                   |  |

| P1.0-P1.7       | 1-8        | 2-9              | 40-44<br>1-3 | I/O | Port 1: Port 1 is an 8-bit bidirectional I/O port with internal pull-ups. Port 1 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As                                                                                                                                                                                                                                                                                                                                                                                                                             |                   |  |

|                 |            |                  |              |     | inputs, Port 1 pins that are externally pulled low will source<br>current because of the internal pull-ups. Port 1 also receives<br>the low-order address byte during memory programming and<br>verification.                                                                                                                                                                                                                                                                                                                                                                                                         |                   |  |

|                 |            |                  |              |     | Alternate functions for Port 1 include:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                   |  |

|                 | 1          | 2                | 40           | I/O | T2 (P1.0): Timer/Counter 2 external count input/Clockout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                   |  |

|                 | 2          | 3                | 41           | I   | <b>T2EX (P1.1):</b> Timer/Counter 2 Reload/Capture/Direction Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                   |  |

| P2.0-P2.7       | 21-<br>28  | 24-<br>31        | 18-25        | I/O | <b>Port 2</b> : Port 2 is an 8-bit bidirectional I/O port with internal pull-ups. Port 2 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As                                                                                                                                                                                                                                                                                                                                                                                                                     |                   |  |

|                 |            |                  |              |     | inputs, Port 2 pins that are externally pulled low will source<br>current because of the internal pull-ups. Port 2 emits the high-<br>order address byte during fetches from external program<br>memory and during accesses to external data memory that<br>use 16-bit addresses (MOVX atDPTR). In this application, it<br>uses strong internal pull-ups emitting 1s. During accesses to<br>external data memory that use 8-bit addresses (MOVX atRi),<br>port 2 emits the contents of the P2 SFR. Some Port 2 pins<br>receive the high order address bits during EPROM<br>programming and verification: P2.0 to P2.4 |                   |  |

| P3.0-P3.7       | 10-<br>17  | 11,<br>13-<br>19 | 5,<br>7-13   | I/O | Port 3: Port 3 is an 8-bit bidirectional I/O port with internal pull-ups. Port 3 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 3 pins that are externally pulled low will source                                                                                                                                                                                                                                                                                                                                                              |                   |  |

|                 |            |                  |              |     | current because of the internal pull-ups. Port 3 also serves<br>the special features of the 80C51 family, as listed below.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                   |  |

|                 | 10         | 11               | 5            | I   | RXD (P3.0): Serial input port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                   |  |

|                 | 11         | 13               | 7            | 0   | TXD (P3.1): Serial output port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                   |  |

|                 | 12         | 14               | 8            | Ι   | INT0 (P3.2): External interrupt 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                   |  |

TS8xCx2X2

6

## 14 **TS8xCx2X2**

**Table 10.** PCON RegisterPCON - Power Control Register (87h)

| 7             | 6               | 5                                                                                             | 4                                                                                                                                                      | 3                                | 2              | 1             | 0   |  |  |

|---------------|-----------------|-----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|----------------|---------------|-----|--|--|

| SMOD1         | SMOD0           | -                                                                                             | POF                                                                                                                                                    | GF1                              | GF0            | PD            | IDL |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Descriptio                                                                                    | n                                                                                                                                                      |                                  |                |               |     |  |  |

| 7             | SMOD1           |                                                                                               | t <b>Mode bit 1</b><br>act double bau                                                                                                                  | ud rate in mode                  | e 1, 2 or 3.   |               |     |  |  |

| 6             | SMOD0           | Clear to se                                                                                   | Serial port Mode bit 0<br>Clear to select SM0 bit in SCON register.<br>Set to to select FE bit in SCON register.                                       |                                  |                |               |     |  |  |

| 5             | -               | Reserved<br>The value                                                                         | read from this                                                                                                                                         | bit is indeterm                  | ninate. Do not | set this bit. |     |  |  |

| 4             | POF             | Clear to ree<br>Set by hard                                                                   | Power-off Flag<br>Clear to recognize next reset type.<br>Set by hardware when VCC rises from 0 to its nominal voltage. Can also be set<br>by software. |                                  |                |               |     |  |  |

| 3             | GF1             | Cleared by                                                                                    |                                                                                                                                                        | eral purpose us<br>purpose usage |                |               |     |  |  |

| 2             | GF0             | Cleared by                                                                                    | General purpose Flag<br>Cleared by user for general purpose usage.<br>Set by user for general purpose usage.                                           |                                  |                |               |     |  |  |

| 1             | PD              | Cleared by                                                                                    | Power-down mode bit<br>Cleared by hardware when reset occurs.<br>Set to enter power-down mode.                                                         |                                  |                |               |     |  |  |

| 0             | IDL             | Idle mode bit<br>Clear by hardware when interrupt or reset occurs.<br>Set to enter idle mode. |                                                                                                                                                        |                                  |                |               |     |  |  |

Reset Value = 00X1 0000b Not bit addressable

Power-off flag reset value will be 1 only after a power on (cold reset). A warm reset doesn't affect the value of this bit.

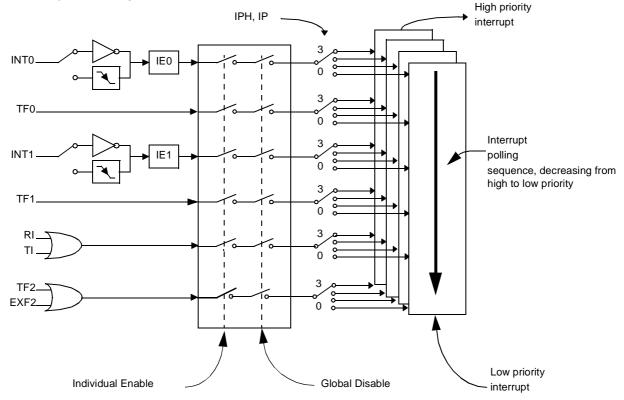

### **Interrupt System**

The TS80C52X2 has a total of 6 interrupt vectors: two external interrupts (INT0 and INT1), three timer interrupts (timers 0, 1 and 2) and the serial port interrupt. These interrupts are shown in Figure 9.

#### Figure 9. Interrupt Control System

Each of the interrupt sources can be individually enabled or disabled by setting or clearing a bit in the Interrupt Enable register (See Table 12.). This register also contains a global disable bit, which must be cleared to disable all interrupts at once.

Each interrupt source can also be individually programmed to one out of four priority levels by setting or clearing a bit in the Interrupt Priority register (See Table 13.) and in the Interrupt Priority High register (See Table 14.). shows the bit values and priority levels associated with each combination.

| Table 11. | Priority | Level Bit | Values |

|-----------|----------|-----------|--------|

|           |          |           |        |

|           |          |           |        |

| IPH.x | IP.x | Interrupt Level Priority |

|-------|------|--------------------------|

| 0     | 0    | 0 (Lowest)               |

| 0     | 1    | 1                        |

| 1     | 0    | 2                        |

| 1     | 1    | 3 (Highest)              |

A low-priority interrupt can be interrupted by a high priority interrupt, but not by another low-priority interrupt. A high-priority interrupt can't be interrupted by any other interrupt source.

If two interrupt requests of different priority levels are received simultaneously, the request of higher priority level is serviced. If interrupt requests of the same priority level

# Table 14.IPH RegisterIPH - Interrupt Priority High Register (B7h)

| 7             | 6               | 5                                                                                                                                | 4                                                                  | 3                       | 2              | 1           | 0    |

|---------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-------------------------|----------------|-------------|------|

| -             | -               | PT2H                                                                                                                             | PSH                                                                | PT1H                    | PX1H           | РТОН        | РХОН |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                      |                                                                    |                         |                |             |      |

| 7             | -               | <b>Reserved</b><br>The value rea                                                                                                 | d from this bit                                                    | is indetermina          | ate. Do not se | t this bit. |      |

| 6             | -               | <b>Reserved</b><br>The value rea                                                                                                 | d from this bit                                                    | is indetermina          | ate. Do not se | t this bit. |      |

| 5             | PT2H            | Timer 2 over           PT2H         PT2           0         0           1         0           1         1                        | f <b>low interrup</b><br><u>Priority Leve</u><br>Lowest<br>Highest | t Priority High<br>한    | n bit          |             |      |

| 4             | PSH             | Serial port P           PSH         PS           0         0           0         1           1         0           1         1   | riority High b<br><u>Priority Leve</u><br>Lowest<br>Highest        |                         |                |             |      |

| 3             | PT1H            | Timer 1 over           PT1H         PT1           0         0           0         1           1         0           1         1  |                                                                    | t Priority High<br>키    | n bit          |             |      |

| 2             | PX1H            | External inte           PX1H         PX1           0         0           1         0           1         1           1         1 | rrupt 1 Priori<br>Priority Leve<br>Lowest<br>Highest               |                         |                |             |      |

| 1             | РТОН            | Timer 0 over           PT0H         PT0           0         0           1         0           1         1                        |                                                                    | t Priority High<br>한    | n bit          |             |      |

| 0             | РХОН            | External inte           PX0H         PX0           0         0           1         1           1         1                       | <b>rrupt 0 Priori</b><br><u>Priority Leve</u><br>Lowest<br>Highest | ty High bit<br><u>키</u> |                |             |      |

Reset Value = XX00 0000b Not bit addressable

## ONCE<sup>™</sup> Mode (ON Chip Emulation)

The ONCE mode facilitates testing and debugging of systems using TS80C52X2 without removing the circuit from the board. The ONCE mode is invoked by driving certain pins of the TS80C52X2; the following sequence must be exercised:

- Pull ALE low while the device is in reset (RST high) and PSEN is high.

- Hold ALE low as RST is deactivated.

While the TS80C52X2 is in ONCE mode, an emulator or test CPU can be used to drive the circuit Table 26. shows the status of the port pins during ONCE mode.

Normal operation is restored when normal reset is applied.

Table 16. External Pin Status during ONCE Mode

| ALE              | PSEN             | Port 0 | Port 1           | Port 2           | Port 3           | XTAL1/2 |

|------------------|------------------|--------|------------------|------------------|------------------|---------|

| Weak pull-<br>up | Weak pull-<br>up | Float  | Weak pull-<br>up | Weak pull-<br>up | Weak pull-<br>up | Active  |

## **Power-off Flag**

The power-off flag allows the user to distinguish between a "cold start" reset and a "warm start" reset.

A cold start reset is the one induced by  $V_{CC}$  switch-on. A warm start reset occurs while  $V_{CC}$  is still applied to the device and could be generated for example by an exit from power-down.

The power-off flag (POF) is located in PCON register (See Table 17.). POF is set by hardware when  $V_{CC}$  rises from 0 to its nominal voltage. The POF can be set or cleared by software allowing the user to determine the type of reset.

The POF value is only relevant with a Vcc range from 4.5V to 5.5V. For lower Vcc value, reading POF bit will return indeterminate value.

| 7             | 6              | 5                       | 4                                                                                                                                                                  | 3              | 2             | 1  | 0   |  |

|---------------|----------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|---------------|----|-----|--|

| SMOD1         | SMOD0          | -                       | POF                                                                                                                                                                | GF1            | GF0           | PD | IDL |  |

| Bit<br>Number | Bit<br>Mnemoni | c Descript              | ion                                                                                                                                                                |                |               |    |     |  |

| 7             | SMOD1          |                         | rt Mode bit 1<br>lect double ba                                                                                                                                    | aud rate in mo | de 1, 2 or 3. |    |     |  |

| 6             | SMOD0          | Clear to s              | Serial port Mode bit 0<br>Clear to select SM0 bit in SCON register.<br>Set to to select FE bit in SCON register.                                                   |                |               |    |     |  |

| 5             | -              |                         | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                                    |                |               |    |     |  |

| 4             | POF            | Clear to r<br>Set by ha | <b>Power-off Flag</b><br>Clear to recognize next reset type.<br>Set by hardware when $V_{CC}$ rises from 0 to its nominal voltage. Can also be<br>set by software. |                |               |    |     |  |

| 3             | GF1            | Cleared b               | General purpose Flag<br>Cleared by user for general purpose usage.<br>Set by user for general purpose usage.                                                       |                |               |    |     |  |

| 2             | GF0            | Cleared b               | General purpose Flag<br>Cleared by user for general purpose usage.<br>Set by user for general purpose usage.                                                       |                |               |    |     |  |

| 1             | PD             | Cleared b               | <b>Power-down mode bit</b><br>Cleared by hardware when reset occurs.<br>Set to enter power-down mode.                                                              |                |               |    |     |  |

| 0             | IDL            | Clear by                | Idle mode bit<br>Clear by hardware when interrupt or reset occurs.<br>Set to enter idle mode.                                                                      |                |               |    |     |  |

#### Table 17. PCON Register

PCON - Power Control Register (87h)

Reset Value = 00X1 0000b Not bit addressable

#### **Reduced EMI Mode**

The ALE signal is used to demultiplex address and data buses on port 0 when used with external program or data memory. Nevertheless, during internal code execution, ALE signal is still generated. In order to reduce EMI, ALE signal can be disabled by setting AO bit.

The AO bit is located in AUXR register at bit location 0. As soon as AO is set, ALE is no longer output but remains active during MOVX and MOVC instructions and external fetches. During ALE disabling, ALE pin is weakly pulled high.

#### Table 18. AUXR Register

AUXR - Auxiliary Register (8Eh)

| 7             | 6               | 5                               | 4                                                                                                                                  | 3               | 2              | 1            | 0  |  |

|---------------|-----------------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------|--------------|----|--|

| -             | -               | -                               | -                                                                                                                                  | -               | -              | -            | AO |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                     |                                                                                                                                    |                 |                |              |    |  |

| 7             | -               | Reserved<br>The value re        | ad from this b                                                                                                                     | it is indetermi | nate. Do not s | et this bit. |    |  |

| 6             | -               | Reserved<br>The value re        | ad from this b                                                                                                                     | it is indetermi | nate. Do not s | et this bit. |    |  |

| 5             | -               | <b>Reserved</b><br>The value re | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                    |                 |                |              |    |  |

| 4             | -               | <b>Reserved</b><br>The value re | ad from this b                                                                                                                     | it is indetermi | nate. Do not s | et this bit. |    |  |

| 3             | -               | Reserved<br>The value re        | ad from this b                                                                                                                     | it is indetermi | nate. Do not s | et this bit. |    |  |

| 2             | -               | <b>Reserved</b><br>The value re | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                    |                 |                |              |    |  |

| 1             | -               | Reserved<br>The value re        | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                    |                 |                |              |    |  |

| 0             | AO              | Clear to rest                   | ALE Output bit<br>Clear to restore ALE operation during internal fetches.<br>Set to disable ALE operation during internal fetches. |                 |                |              |    |  |

Reset Value = XXXX XXX0b Not bit addressable

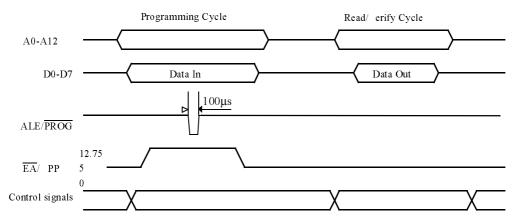

| Programming Algorithm | The Improved Quick Pulse algorithm is based on the Quick Pulse algorithm and decreases the number of pulses applied during byte programming from 25 to 1.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                       | <ul> <li>To program the TS87C52X2 the following sequence must be exercised:</li> <li>Step 1: Activate the combination of control signals.</li> <li>Step 2: Input the valid address on the address lines.</li> <li>Step 3: Input the appropriate data on the data lines.</li> <li>Step 4: Raise EA/VPP from VCC to VPP (typical 12.75V).</li> <li>Step 5: Pulse ALE/PROG once.</li> <li>Step 6: Lower EA/VPP from VPP to VCC</li> <li>Repeat step 2 through 6 changing the address and data for the entire array or until the end of the object file is reached (See Figure 12.).</li> </ul> |

Verify Algorithm Code array verify must be done after each byte or block of bytes is programmed. In either case, a complete verify of the programmed array will ensure reliable programming of the TS87C52X2.

P 2.7 is used to enable data output.

To verify the TS87C52X2 code the following sequence must be exercised:

- Step 1: Activate the combination of program and control signals.

- Step 2: Input the valid address on the address lines.

- Step 3: Read data on the data lines.

Repeat step 2 through 3 changing the address for the entire array verification (See Figure 12.)

The encryption array cannot be directly verified. Verification of the encryption array is done by observing that the code array is well encrypted.

#### Figure 12. Programming and Verification Signal's Waveform

EPROM Erasure (Windowed Packages Only) Erasing the EPROM erases the code array, the encryption array and the lock bits returning the parts to full functionality.

Erasure leaves all the EPROM cells in a 1's state (FF).

**Erasure Characteristics** The recommended erasure procedure is exposure to ultraviolet light (at 2537 Å) to an integrated dose at least 15 W-sec/cm<sup>2</sup>. Exposing the EPROM to an ultraviolet lamp of

12,000  $\mu$ W/cm<sup>2</sup> rating for 30 minutes, at a distance of about 25 mm, should be sufficient. An exposure of 1 hour is recommended with most of standard erasers.

Erasure of the EPROM begins to occur when the chip is exposed to light with wavelength shorter than approximately 4,000 Å. Since sunlight and fluorescent lighting have wavelengths in this range, exposure to these light sources over an extended time (about 1 week in sunlight, or 3 years in room-level fluorescent lighting) could cause inadvertent erasure. If an application subjects the device to this type of exposure, it is suggested that an opaque label be placed over the window.

**Signature Bytes** The TS80/87C52X2 has four signature bytes in location 30h, 31h, 60h and 61h. To read these bytes follow the procedure for EPROM verify but activate the control lines provided in Table 31. for Read Signature Bytes. Table 35. shows the content of the signature byte for the TS80/87C52X2.

| Location | Contents | Comment                  |

|----------|----------|--------------------------|

| 30h      | 58h      | Manufacturer Code: Atmel |

| 31h      | 57h      | Family Code: C51 X2      |

| 60h      | 2Dh      | Product name: TS80C52X2  |

| 60h      | ADh      | Product name:TS87C52X2   |

| 60h      | 20h      | Product name: TS80C32X2  |

| 61h      | FFh      | Product revision number  |

Table 21. Signature Bytes Content

####

Table 23. DC Parameters for Low Voltage

| Symbol                            | Parameter                                                    | Min                       | Тур                                    | Max                                                  | Unit | Test Conditions                                                                                     |

|-----------------------------------|--------------------------------------------------------------|---------------------------|----------------------------------------|------------------------------------------------------|------|-----------------------------------------------------------------------------------------------------|

| V <sub>IL</sub>                   | Input Low Voltage                                            | -0.5                      |                                        | 0.2 V <sub>CC</sub> - 0.1                            | V    |                                                                                                     |

| V <sub>IH</sub>                   | Input High Voltage except XTAL1, RST                         | 0.2 V <sub>CC</sub> + 0.9 |                                        | V <sub>CC</sub> + 0.5                                | V    |                                                                                                     |

| V <sub>IH1</sub>                  | Input High Voltage, XTAL1, RST                               | 0.7 V <sub>CC</sub>       |                                        | V <sub>CC</sub> + 0.5                                | V    |                                                                                                     |

| V <sub>OL</sub>                   | Output Low Voltage, ports 1, 2, 3 (6)                        |                           |                                        | 0.45                                                 | V    | I <sub>OL</sub> = 0.8 mA <sup>(4)</sup>                                                             |

| V <sub>OL1</sub>                  | Output Low Voltage, port 0, ALE, PSEN (6)                    |                           |                                        | 0.45                                                 | V    | I <sub>OL</sub> = 1.6 mA <sup>(4)</sup>                                                             |

| V <sub>OH</sub>                   | Output High Voltage, ports 1, 2, 3                           | 0.9 V <sub>CC</sub>       |                                        |                                                      | V    | I <sub>OH</sub> = -10 μA                                                                            |

| V <sub>OH1</sub>                  | Output High Voltage, port 0, ALE, PSEN                       | 0.9 V <sub>CC</sub>       |                                        |                                                      | V    | I <sub>OH</sub> = -40 μA                                                                            |

| I <sub>IL</sub>                   | Logical 0 Input Current ports 1, 2 and 3                     |                           |                                        | -50                                                  | μA   | Vin = 0.45V                                                                                         |

| ILI                               | Input Leakage Current                                        |                           |                                        | ±10                                                  | μA   | $0.45V < Vin < V_{CC}$                                                                              |

| I <sub>TL</sub>                   | Logical 1 to 0 Transition Current, ports 1, 2, 3             |                           |                                        | -650                                                 | μA   | Vin = 2.0 V                                                                                         |

| R <sub>RST</sub>                  | RST Pulldown Resistor                                        | 50                        | 90 <sup>(5)</sup>                      | 200                                                  | kΩ   |                                                                                                     |

| CIO                               | Capacitance of I/O Buffer                                    |                           |                                        | 10                                                   | pF   | Fc = 1 MHz<br>T <sub>A</sub> = 25°C                                                                 |

| I <sub>PD</sub>                   | Power Down Current                                           |                           | 20 <sup>(5)</sup><br>10 <sup>(5)</sup> | 50<br>30                                             | μΑ   | $V_{CC} = 2.0 \text{ V to } 5.5 \text{V}^{(3)}$<br>$V_{CC} = 2.0 \text{ V to } 3.3 \text{ V}^{(3)}$ |

| I <sub>cc</sub><br>under<br>RESET | Power Supply Current Maximum values, X1 mode: <sup>(7)</sup> |                           |                                        | 1 + 0.2 Freq<br>(MHz)<br>at12MHz 3.4<br>at16MHz 4.2  | mA   | V <sub>CC</sub> = 3.3 V <sup>(1)</sup>                                                              |

| I <sub>CC</sub><br>operating      | Power Supply Current Maximum values, X1 mode: <sup>(7)</sup> |                           |                                        | 1 + 0.3 Freq<br>(MHz)<br>at12MHz 4.6<br>at16MHz 5.8  | mA   | $V_{CC} = 3.3 V^{(8)}$                                                                              |

| I <sub>CC</sub><br>idle           | Power Supply Current Maximum values, X1 mode: <sup>(7)</sup> |                           |                                        | 0.15 Freq<br>(MHz) + 0.2<br>at12MHz 2<br>at16MHz 2.6 | mA   | $V_{CC} = 3.3 V^{(2)}$                                                                              |

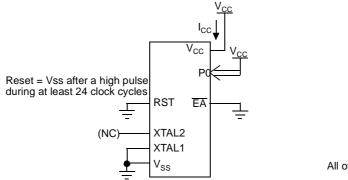

Notes: 1. I<sub>CC</sub> under reset is measured with all output pins disconnected; XTAL1 driven with T<sub>CLCH</sub>, T<sub>CHCL</sub> = 5 ns (see Figure 17.), V<sub>IL</sub> = V<sub>SS</sub> + 0.5V,

$V_{IH} = V_{CC} - 0.5V$ ; XTAL2 N.C.;  $\overline{EA} = RST = Port 0 = V_{CC}$ .  $I_{CC}$  would be slightly higher if a crystal oscillator used..

2. Idle I<sub>CC</sub> is measured with all out<u>put</u> pins disconnected; XTAL1 driven with  $T_{CLCH}$ ,  $T_{CHCL} = 5$  ns,  $V_{IL} = V_{SS} + 0.5V$ ,  $V_{IH} = V_{CC} - 0.5V$ ; XTAL2 N.C; Port 0 =  $V_{CC}$ ; EA = RST =  $V_{SS}$  (see Figure 15.).

Power Down I<sub>CC</sub> is measured with all output pins disconnected; EA = V<sub>SS</sub>, PORT 0 = V<sub>CC</sub>; XTAL2 NC.; RST = V<sub>SS</sub> (see Figure 16.).

4. Capacitance loading on Ports 0 and 2 may cause spurious noise pulses to be superimposed on the V<sub>OL</sub>s of ALE and Ports 1 and 3. The noise is due to external bus capacitance discharging into the Port 0 and Port 2 pins when these pins make 1 to 0 transitions during bus operation. In the worst cases (capacitive loading 100pF), the noise pulse on the ALE line may exceed 0.45V with maxi V<sub>OL</sub> peak 0.6V. A Schmitt Trigger use is not necessary.

5. Typicals are based on a limited number of samples and are not guaranteed. The values listed are at room temperature and 5V.

Under steady state (non-transient) conditions, I<sub>OL</sub> must be externally limited as follows: Maximum I<sub>OL</sub> per port pin: 10 mA Maximum I<sub>OL</sub> per 8-bit port:

Figure 16.  $I_{CC}$  Test Condition, Power-down Mode

All other pins are disconnected.

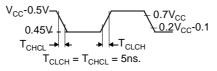

Figure 17. Clock Signal Waveform for  $I_{CC}$  Tests in Active and Idle Modes

### **AC Parameters**

| Explanation of the AC<br>Symbols | time). The oth                                                                                                                                   | symbol has 5 characters<br>her characters, depending<br>status of that signal. The<br>r.                                                                        | g on their positions, stand                                                                                                   | I for the name of a signal                                                                                                     |  |  |  |

|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                  |                                                                                                                                                  | <sub>_L</sub> = Time for Addr <u>ess V</u> al<br>e for ALE Low to PSEN L                                                                                        |                                                                                                                               |                                                                                                                                |  |  |  |

|                                  | ranges.<br>$T_A = -40^{\circ}C$ to<br>-V ranges.<br>$T_A = 0$ to +70<br>range.<br>$T_A = -40^{\circ}C$ to<br>range.<br>Table 24. giv             | °C (commercial temperat<br>+85°C (industrial temper<br>D°C (commercial temper<br>o +85°C (industrial temper<br>es the maximum applica<br>d PSEN signals. Timing | ature range); $V_{SS} = 0 V$ ;<br>rature range); $V_{SS} = 0 V$<br>erature range); $V_{SS} = 0 V$<br>ble load capacitance for | $V_{CC} = 5V \pm 10\%$ ; -M and<br>; 2.7 V < $V_{CC}$ = 5.5V; -L<br>/; 2.7 V < $V_{CC}$ = 5.5V; -L<br>Port 0, Port 1, 2 and 3, |  |  |  |

|                                  | respected. Higher capacitance values can be used, but timings will then be degrad<br><b>Table 24.</b> Load Capacitance versus speed range, in pF |                                                                                                                                                                 |                                                                                                                               |                                                                                                                                |  |  |  |

|                                  | -M -V -L                                                                                                                                         |                                                                                                                                                                 |                                                                                                                               |                                                                                                                                |  |  |  |

|                                  | Port 0         100         50         100                                                                                                        |                                                                                                                                                                 |                                                                                                                               |                                                                                                                                |  |  |  |

|                                  | Port 1, 2, 3         80         50         80                                                                                                    |                                                                                                                                                                 |                                                                                                                               |                                                                                                                                |  |  |  |

|                                  | ALE / PSEN                                                                                                                                       | 100                                                                                                                                                             | 30                                                                                                                            | 100                                                                                                                            |  |  |  |

Table 5., Table 29. and Table 32. give the description of each AC symbols.

Table 27., Table 30. and Table 33. give for each range the AC parameter.

| Speed             |     | M<br>MHz | X2 n<br>30 l<br>60 l | V<br>node<br>MHz<br>MHz<br>uiv. | stan<br>mod | V<br>dard<br>le 40<br>Hz | X2 n<br>20 l<br>40 l | L<br>node<br>MHz<br>MHz<br>uiv. | stan<br>mo | L<br>dard<br>ode<br>MHz | Units |

|-------------------|-----|----------|----------------------|---------------------------------|-------------|--------------------------|----------------------|---------------------------------|------------|-------------------------|-------|

| Symbol            | Min | Max      | Min                  | Max                             | Min         | Max                      | Min                  | Max                             | Min        | Max                     |       |

| Т                 | 25  |          | 33                   |                                 | 25          |                          | 50                   |                                 | 33         |                         | ns    |

| T <sub>LHLL</sub> | 40  |          | 25                   |                                 | 42          |                          | 35                   |                                 | 52         |                         | ns    |

| T <sub>AVLL</sub> | 10  |          | 4                    |                                 | 12          |                          | 5                    |                                 | 13         |                         | ns    |

| T <sub>LLAX</sub> | 10  |          | 4                    |                                 | 12          |                          | 5                    |                                 | 13         |                         | ns    |

| T <sub>LLIV</sub> |     | 70       |                      | 45                              |             | 78                       |                      | 65                              |            | 98                      | ns    |

| T <sub>LLPL</sub> | 15  |          | 9                    |                                 | 17          |                          | 10                   |                                 | 18         |                         | ns    |

| T <sub>PLPH</sub> | 55  |          | 35                   |                                 | 60          |                          | 50                   |                                 | 75         |                         | ns    |

| T <sub>PLIV</sub> |     | 35       |                      | 25                              |             | 50                       |                      | 30                              |            | 55                      | ns    |

| T <sub>PXIX</sub> | 0   |          | 0                    |                                 | 0           |                          | 0                    |                                 | 0          |                         | ns    |

| T <sub>PXIZ</sub> |     | 18       |                      | 12                              |             | 20                       |                      | 10                              |            | 18                      | ns    |

| T <sub>AVIV</sub> |     | 85       |                      | 53                              |             | 95                       |                      | 80                              |            | 122                     | ns    |

| T <sub>PLAZ</sub> |     | 10       |                      | 10                              |             | 10                       |                      | 10                              |            | 10                      | ns    |

Table 28. AC Parameters for a Variable Clock: derating formula

| Symbol            | Туре | Standard<br>Clock | X2 Clock  | -М | -V | -L | Units |

|-------------------|------|-------------------|-----------|----|----|----|-------|

| T <sub>LHLL</sub> | Min  | 2 T - x           | T - x     | 10 | 8  | 15 | ns    |

| T <sub>AVLL</sub> | Min  | T - x             | 0.5 T - x | 15 | 13 | 20 | ns    |

| T <sub>LLAX</sub> | Min  | T - x             | 0.5 T - x | 15 | 13 | 20 | ns    |

| T <sub>LLIV</sub> | Max  | 4 T - x           | 2 T - x   | 30 | 22 | 35 | ns    |

| T <sub>LLPL</sub> | Min  | T - x             | 0.5 T - x | 10 | 8  | 15 | ns    |

| T <sub>PLPH</sub> | Min  | 3 T - x           | 1.5 T - x | 20 | 15 | 25 | ns    |

| T <sub>PLIV</sub> | Max  | 3 T - x           | 1.5 T - x | 40 | 25 | 45 | ns    |

| T <sub>PXIX</sub> | Min  | х                 | х         | 0  | 0  | 0  | ns    |

| T <sub>PXIZ</sub> | Max  | T - x             | 0.5 T - x | 7  | 5  | 15 | ns    |

| T <sub>AVIV</sub> | Max  | 5 T - x           | 2.5 T - x | 40 | 30 | 45 | ns    |

| T <sub>PLAZ</sub> | Max  | х                 | х         | 10 | 10 | 10 | ns    |

| Symbol            | Туре | Standard<br>Clock | X2 Clock  | -М | -V | -L | Units |

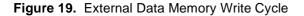

|-------------------|------|-------------------|-----------|----|----|----|-------|

| T <sub>RLRH</sub> | Min  | 6 T - x           | 3 T - x   | 20 | 15 | 25 | ns    |

| T <sub>WLWH</sub> | Min  | 6 T - x           | 3 T - x   | 20 | 15 | 25 | ns    |

| T <sub>RLDV</sub> | Max  | 5 T - x           | 2.5 T - x | 25 | 23 | 30 | ns    |

| T <sub>RHDX</sub> | Min  | х                 | х         | 0  | 0  | 0  | ns    |

| T <sub>RHDZ</sub> | Max  | 2 T - x           | T - x     | 20 | 15 | 25 | ns    |

| T <sub>LLDV</sub> | Max  | 8 T - x           | 4T -x     | 40 | 35 | 45 | ns    |

| T <sub>AVDV</sub> | Max  | 9 T - x           | 4.5 T - x | 60 | 50 | 65 | ns    |

| T <sub>LLWL</sub> | Min  | 3 T - x           | 1.5 T - x | 25 | 20 | 30 | ns    |

| T <sub>LLWL</sub> | Max  | 3 T + x           | 1.5 T + x | 25 | 20 | 30 | ns    |

| T <sub>AVWL</sub> | Min  | 4 T - x           | 2 T - x   | 25 | 20 | 30 | ns    |

| T <sub>QVWX</sub> | Min  | T - x             | 0.5 T - x | 15 | 10 | 20 | ns    |

| T <sub>QVWH</sub> | Min  | 7 T - x           | 3.5 T - x | 15 | 10 | 20 | ns    |

| T <sub>WHQX</sub> | Min  | T - x             | 0.5 T - x | 10 | 8  | 15 | ns    |

| T <sub>RLAZ</sub> | Max  | х                 | х         | 0  | 0  | 0  | ns    |

| T <sub>WHLH</sub> | Min  | T - x             | 0.5 T - x | 15 | 10 | 20 | ns    |

| T <sub>WHLH</sub> | Max  | T + x             | 0.5 T + x | 15 | 10 | 20 | ns    |

Table 31. AC Parameters for a Variable Clock: Derating Formula

# External Data Memory Write Cycle

| Symbol            | Туре | Standard<br>Clock | X2 Clock | -М  | -V  | -L  | Units |

|-------------------|------|-------------------|----------|-----|-----|-----|-------|

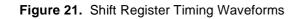

| T <sub>XLXL</sub> | Min  | 12 T              | 6 T      |     |     |     | ns    |

| T <sub>QVHX</sub> | Min  | 10 T - x          | 5 T - x  | 50  | 50  | 50  | ns    |

| T <sub>XHQX</sub> | Min  | 2 T - x           | T - x    | 20  | 20  | 20  | ns    |

| T <sub>XHDX</sub> | Min  | х                 | х        | 0   | 0   | 0   | ns    |

| T <sub>XHDV</sub> | Max  | 10 T - x          | 5 T- x   | 133 | 133 | 133 | ns    |

Table 34. AC Parameters for a Variable Clock: Derating Formula

#### Shift Register Timing Waveforms

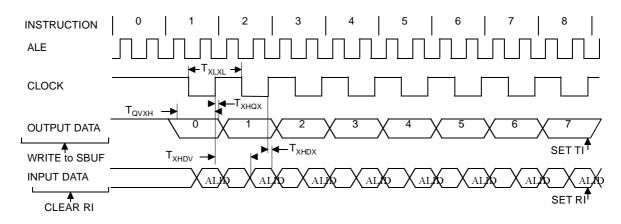

#### **EPROM Programming and** Verification Characteristics

$T_A$  = 21°C to 27°C;  $V_{SS}$  = 0V;  $~V_{CC}$  = 5V  $\pm$  10% while programming.  $V_{CC}$  = operating range while verifying.

Table 35.

EPROM Programming Parameters

| Symbol              | Parameter                         | Min                  | Мах                  | Units |

|---------------------|-----------------------------------|----------------------|----------------------|-------|

| V <sub>PP</sub>     | Programming Supply Voltage        | 12.5                 | 13                   | V     |

| I <sub>PP</sub>     | Programming Supply Current        |                      | 75                   | mA    |

| 1/T <sub>CLCL</sub> | Oscillator Frquency               | 4                    | 6                    | MHz   |

| T <sub>AVGL</sub>   | Address Setup to PROG Low         | 48 T <sub>CLCL</sub> |                      |       |

| T <sub>GHAX</sub>   | Adress Hold after PROG            | 48 T <sub>CLCL</sub> |                      |       |

| T <sub>DVGL</sub>   | Data Setup to PROG Low            | 48 T <sub>CLCL</sub> |                      |       |

| T <sub>GHDX</sub>   | Data Hold after PROG              | 48 T <sub>CLCL</sub> |                      |       |

| T <sub>EHSH</sub>   | (Enable) High to V <sub>PP</sub>  | 48 T <sub>CLCL</sub> |                      |       |

| T <sub>SHGL</sub>   | V <sub>PP</sub> Setup to PROG Low | 10                   |                      | μs    |

| T <sub>GHSL</sub>   | V <sub>PP</sub> Hold after PROG   | 10                   |                      | μs    |

| T <sub>GLGH</sub>   | PROG Width                        | 90                   | 110                  | μs    |

| T <sub>AVQV</sub>   | Address to Valid Data             |                      | 48 T <sub>CLCL</sub> |       |

| T <sub>ELQV</sub>   | ENABLE Low to Data Valid          |                      | 48 T <sub>CLCL</sub> |       |

| T <sub>EHQZ</sub>   | Data Float after ENABLE           | 0                    | 48 T <sub>CLCL</sub> |       |

## EPROM Programming and Verification Waveforms

#### Figure 22. EPROM Programming and Verification Waveforms

\* 8KB: up to P2.4, 16KB: up to P2.5, 32KB: up to P3.4, 64KB: up to P3.5

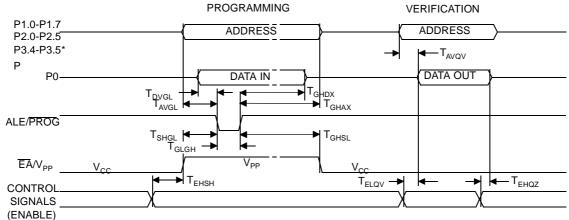

#### External Clock Drive Characteristics (XTAL1)

Table 36. AC Parameters

| Symbol                               | Parameter               | Min | Max | Units |

|--------------------------------------|-------------------------|-----|-----|-------|

| T <sub>CLCL</sub>                    | Oscillator Period       | 25  |     | ns    |

| T <sub>CHCX</sub>                    | High Time               | 5   |     | ns    |

| T <sub>CLCX</sub>                    | Low Time                | 5   |     | ns    |

| T <sub>CLCH</sub>                    | Rise Time               |     | 5   | ns    |

| T <sub>CHCL</sub>                    | Fall Time               |     | 5   | ns    |

| T <sub>CHCX</sub> /T <sub>CLCX</sub> | Cyclic ratio in X2 mode | 40  | 60  | %     |

## External Clock Drive Waveforms

Figure 23. External Clock Drive Waveforms

#### AC Testing Input/Output Waveforms

Figure 24. AC Testing Input/Output Waveforms

INPUT/OUTPUT

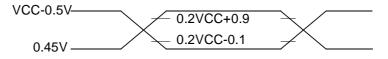

AC inputs during testing are driven at V<sub>CC</sub> - 0.5 for a logic "1" and 0.45V for a logic "0". Timing measurement are made at V<sub>IH</sub> min for a logic "1" and V<sub>IL</sub> max for a logic "0".

#### **Float Waveforms**

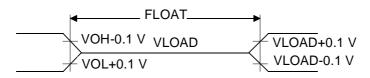

#### Figure 25. Float Waveforms

For timing purposes a port pin is no longer floating when a 100 mV change from load voltage occurs and begins to float when a 100 mV change from the loaded V<sub>OH</sub>/V<sub>OL</sub> level occurs.  $I_{OL}/I_{OH} \ge \pm 20$ mA.