Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Obsolete                                                                |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | 80C51                                                                   |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 60/30MHz                                                                |

| Connectivity               | UART/USART                                                              |

| Peripherals                | POR                                                                     |

| Number of I/O              | 32                                                                      |

| Program Memory Size        | 8KB (8K x 8)                                                            |

| Program Memory Type        | OTP                                                                     |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 256 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                             |

| Data Converters            | -                                                                       |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 44-LCC (J-Lead)                                                         |

| Supplier Device Package    | 44-PLCC (16.6x16.6)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/ts87c52x2-vib |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Table 1. Memory Size

|           | ROM (bytes) | EPROM (bytes) | TOTAL RAM (bytes) |

|-----------|-------------|---------------|-------------------|

| TS80C32X2 | 0           | 0             | 256               |

| TS80C52X2 | 8k          | 0             | 256               |

| TS87C52X2 | 0           | 8k            | 256               |

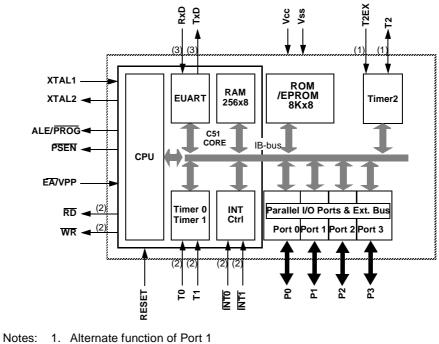

# **Block Diagram**

2. Alternate function of Port 3

2

| Mnemonic        | I         | Pin Nu           | mber         | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|-----------------|-----------|------------------|--------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                 | DIL       | LCC              | VQFP<br>1.4  |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| V <sub>SS</sub> | 20        | 22               | 16           | I    | Ground: 0V reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| Vss1            |           | 1                | 39           | I    | Optional Ground: Contact the Sales Office for ground connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| V <sub>CC</sub> | 40        | 44               | 38           | I    | <b>Power Supply:</b> This is the power supply voltage for normal, idle and power-down operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| P0.0-P0.7       | 39-<br>32 | 43-<br>36        | 37-30        | I/O  | <b>Port 0</b> : Port 0 is an open-drain, bidirectional I/O port. Port 0 pins that have 1s written to them float and can be used as high impedance inputs.Port 0 pins must be polarized to Vcc                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|                 |           |                  |              |      | or Vss in order to prevent any parasitic current consumption.<br>Port 0 is also the multiplexed low-order address and data bus<br>during access to external program and data memory. In this<br>application, it uses strong internal pull-up when emitting 1s.<br>Port 0 also inputs the code bytes during EPROM<br>programming. External pull-ups are required during program<br>verification during which P0 outputs the code bytes.                                                                                                                                                                                |  |  |  |

| P1.0-P1.7       | 1-8       | 2-9              | 40-44<br>1-3 | I/O  | Port 1: Port 1 is an 8-bit bidirectional I/O port with internal pull-ups. Port 1 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|                 |           |                  |              |      | inputs, Port 1 pins that are externally pulled low will source<br>current because of the internal pull-ups. Port 1 also receives<br>the low-order address byte during memory programming and<br>verification.                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|                 |           |                  |              |      | Alternate functions for Port 1 include:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|                 | 1         | 2                | 40           | I/O  | T2 (P1.0): Timer/Counter 2 external count input/Clockout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|                 | 2         | 3                | 41           | I    | <b>T2EX (P1.1):</b> Timer/Counter 2 Reload/Capture/Direction Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| P2.0-P2.7       | 21-<br>28 | 24-<br>31        | 18-25        | I/O  | <b>Port 2</b> : Port 2 is an 8-bit bidirectional I/O port with internal pull-ups. Port 2 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|                 |           |                  |              |      | inputs, Port 2 pins that are externally pulled low will source<br>current because of the internal pull-ups. Port 2 emits the high-<br>order address byte during fetches from external program<br>memory and during accesses to external data memory that<br>use 16-bit addresses (MOVX atDPTR). In this application, it<br>uses strong internal pull-ups emitting 1s. During accesses to<br>external data memory that use 8-bit addresses (MOVX atRi),<br>port 2 emits the contents of the P2 SFR. Some Port 2 pins<br>receive the high order address bits during EPROM<br>programming and verification: P2.0 to P2.4 |  |  |  |

| P3.0-P3.7       | 10-<br>17 | 11,<br>13-<br>19 | 5,<br>7-13   | I/O  | Port 3: Port 3 is an 8-bit bidirectional I/O port with internal pull-ups. Port 3 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 3 pins that are externally pulled low will source                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|                 |           |                  |              |      | current because of the internal pull-ups. Port 3 also serves<br>the special features of the 80C51 family, as listed below.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|                 | 10        | 11               | 5            | I    | RXD (P3.0): Serial input port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|                 | 11        | 13               | 7            | 0    | TXD (P3.1): Serial output port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|                 | 12        | 14               | 8            | Ι    | INT0 (P3.2): External interrupt 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

TS8xCx2X2

6

Programmable Clock-output

In the clock-out mode, timer 2 operates as a 50%-duty-cycle, programmable clock generator (See Figure 5). The input clock increments TL2 at frequency F<sub>OSC</sub>/2. The timer repeatedly counts to overflow from a loaded value. At overflow, the contents of RCAP2H and RCAP2L registers are loaded into TH2 and TL2. In this mode, timer 2 overflows do not generate interrupts. The formula gives the clock-out frequency as a function of the system oscillator frequency and the value in the RCAP2H and RCAP2L registers :

$$Clock - OutFrequency = \frac{F_{osc}}{4 \times (65536 - RCAP2H/RCAP2L)}$$

For a 16 MHz system clock, timer 2 has a programmable frequency range of 61 Hz  $(F_{OSC}/2^{16})$  to 4 MHz  $(F_{OSC}/4)$ . The generated clock signal is brought out to T2 pin (P1.0).

Timer 2 is programmed for the clock-out mode as follows:

- Set T2OE bit in T2MOD register.

- Clear C/T2 bit in T2CON register.

- Determine the 16-bit reload value from the formula and enter it in RCAP2H/RCAP2L registers.

- Enter a 16-bit initial value in timer registers TH2/TL2. It can be the same as the reload value or a different one depending on the application.

- To start the timer, set TR2 run control bit in T2CON register.

It is possible to use timer 2 as a baud rate generator and a clock generator simultaneously. For this configuration, the baud rates and clock frequencies are not independent since both functions use the values in the RCAP2H and RCAP2L registers.

# Table 6. T2MOD Register

T2MOD - Timer 2 Mode Control Register (C9h)

| 7             | 6               | 5                                | 4                                                                                                                            | 3                                 | 2               | 1            | 0    |  |  |  |

|---------------|-----------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-----------------|--------------|------|--|--|--|

| -             | -               | -                                | -                                                                                                                            | -                                 | -               | T2OE         | DCEN |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                      |                                                                                                                              |                                   |                 |              |      |  |  |  |

| 7             | -               | <b>Reserved</b><br>The value rea | ad from this b                                                                                                               | it is indetermir                  | nate. Do not s  | et this bit. |      |  |  |  |

| 6             | -               | <b>Reserved</b><br>The value rea | ad from this b                                                                                                               | it is indetermir                  | nate. Do not s  | et this bit. |      |  |  |  |

| 5             | -               | <b>Reserved</b><br>The value rea | ad from this b                                                                                                               | it is indetermir                  | nate. Do not s  | et this bit. |      |  |  |  |

| 4             | -               | Reserved<br>The value rea        | ad from this b                                                                                                               | it is indetermir                  | nate. Do not se | et this bit. |      |  |  |  |

| 3             | -               | <b>Reserved</b><br>The value rea | ad from this b                                                                                                               | it is indetermir                  | nate. Do not s  | et this bit. |      |  |  |  |

| 2             | -               | <b>Reserved</b><br>The value rea | ad from this b                                                                                                               | it is indetermir                  | nate. Do not s  | et this bit. |      |  |  |  |

| 1             | T2OE            | Clear to prog                    | Timer 2 Output Enable bit<br>Clear to program P1.0/T2 as clock input or I/O port.<br>Set to program P1.0/T2 as clock output. |                                   |                 |              |      |  |  |  |

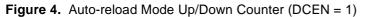

| 0             | DCEN            | Clear to disa                    |                                                                                                                              | t<br>up/down cou<br>b/down counte |                 |              |      |  |  |  |

Reset Value = XXXX XX00b Not bit addressable

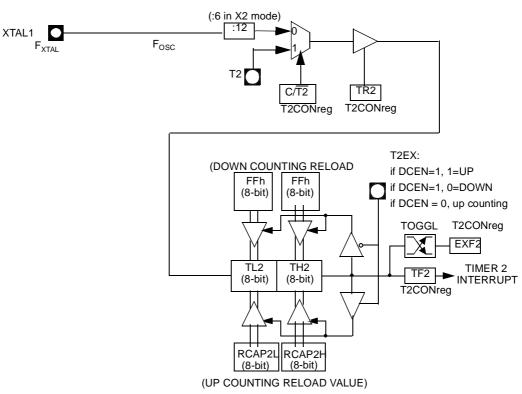

For slave A, bit 0 (the LSB) is a don't-care bit; for slaves B and C, bit 0 is a 1. To communicate with slave A only, the master must send an address where bit 0 is clear (e.g.

18 **TS8xCx2X2**

1111 0000b).

For slave A, bit 1 is a 1; for slaves B and C, bit 1 is a don't care bit. To communicate with slaves B and C, but not slave A, the master must send an address with bits 0 and 1 both set (e.g. 1111 0011b).

To communicate with slaves A, B and C, the master must send an address with bit 0 set, bit 1 clear, and bit 2 clear (e.g. 1111 0001b).

**Broadcast Address** A broadcast address is formed from the logical OR of the SADDR and SADEN registers with zeros defined as don't-care bits, e.g.:

SADDR 0101 0110b SADEN 1111 1100b Broadcast =SADDR OR SADEN1111 111Xb

The use of don't-care bits provides flexibility in defining the broadcast address, however in most applications, a broadcast address is FFh. The following is an example of using broadcast addresses:

Slave A:SADDR1111 0001b <u>SADEN1111 1010b</u> Broadcast1111 1X11b, Slave B:SADDR1111 0011b <u>SADEN1111 1001b</u> Broadcast1111 1X11B,

Slave C:SADDR=1111 0010b <u>SADEN1111 1101b</u> Broadcast1111 1111b

For slaves A and B, bit 2 is a don't care bit; for slave C, bit 2 is set. To communicate with all of the slaves, the master must send an address FFh. To communicate with slaves A and B, but not slave C, the master can send and address FBh.

Reset AddressesOn reset, the SADDR and SADEN registers are initialized to 00h, i.e. the given and<br/>broadcast addresses are XXXX XXXb (all don't-care bits). This ensures that the serial<br/>port will reply to any address, and so, that it is backwards compatible with the 80C51<br/>microcontrollers that do not support automatic address recognition.

Table 7.

SADEN Register

| 7                                   | 6          | 5           | 4             | 3 | 2        | 1 | 0 |

|-------------------------------------|------------|-------------|---------------|---|----------|---|---|

|                                     |            |             |               |   |          |   |   |

| Decet Valu                          |            | 0006        |               |   | <u>.</u> |   |   |

| Reset Valu                          |            | 0000        |               |   |          |   |   |

| Not bit add                         | ressable   |             |               |   |          |   |   |

|                                     |            |             |               |   |          |   |   |

|                                     |            |             |               |   |          |   |   |

| Table 8 S                           |            | vietor      |               |   |          |   |   |

|                                     | -          |             |               |   |          |   |   |

|                                     | -          |             | er (A9h)      |   |          |   |   |

| <b>Table 8.</b> S<br>SADDR - S<br>7 | -          |             | er (A9h)<br>4 | 3 | 2        | 1 | 0 |

| SADDR - S                           | lave Addre | ess Registe | er (A9h)<br>4 | 3 | 2        | 1 | 0 |

| SADDR - S                           | lave Addre | ess Registe | er (A9h)<br>4 | 3 | 2        | 1 | 0 |

Not bit addressable

**Table 10.** PCON RegisterPCON - Power Control Register (87h)

| 7             | 6               | 5                     | 4                                                                                              | 3                                | 2               | 1              | 0             |  |  |

|---------------|-----------------|-----------------------|------------------------------------------------------------------------------------------------|----------------------------------|-----------------|----------------|---------------|--|--|

| SMOD1         | SMOD0           | -                     | POF                                                                                            | GF1                              | GF0             | PD             | IDL           |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Descriptio            | n                                                                                              |                                  |                 |                |               |  |  |

| 7             | SMOD1           |                       | t <b>Mode bit 1</b><br>ect double bau                                                          | ud rate in mode                  | e 1, 2 or 3.    |                |               |  |  |

| 6             | SMOD0           | Clear to se           |                                                                                                | n SCON regist<br>SCON registe    |                 |                |               |  |  |

| 5             | -               | Reserved<br>The value | read from this                                                                                 | bit is indeterm                  | ninate. Do not  | set this bit.  |               |  |  |

| 4             | POF             |                       | cognize next i<br>dware when V                                                                 | reset type.<br>/CC rises from    | 0 to its nomina | al voltage. Ca | n also be set |  |  |

| 3             | GF1             | Cleared by            |                                                                                                | eral purpose us<br>purpose usage |                 |                |               |  |  |

| 2             | GF0             | Cleared by            | -                                                                                              | eral purpose us<br>purpose usage | -               |                |               |  |  |

| 1             | PD              | Cleared by            | Power-down mode bit<br>Cleared by hardware when reset occurs.<br>Set to enter power-down mode. |                                  |                 |                |               |  |  |

| 0             | IDL             | -                     |                                                                                                | interrupt or re                  | eset occurs.    |                |               |  |  |

Reset Value = 00X1 0000b Not bit addressable

Power-off flag reset value will be 1 only after a power on (cold reset). A warm reset doesn't affect the value of this bit.

are received simultaneously, an internal polling sequence determines which request is serviced. Thus within each priority level there is a second priority structure determined by the polling sequence.

# Table 12. IE Register

IE - Interrupt Enable Register (A8h)

| 7             | 6               | 5                                                                                     | 4                                                                                                                                         | 3               | 2               | 1             | 0          |  |  |  |  |

|---------------|-----------------|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------|---------------|------------|--|--|--|--|

| EA            | -               | ET2                                                                                   | ET2 ES ET1 EX1                                                                                                                            |                 |                 |               |            |  |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                           | Description                                                                                                                               |                 |                 |               |            |  |  |  |  |

| 7             | EA              | Enable All int<br>Clear to disab<br>Set to enable<br>If EA=1, each<br>clearing its ow | le all interrupt<br>all interrupts.<br>interrupt sour                                                                                     | ce is individua | illy enabled or | disabled by s | setting or |  |  |  |  |

| 6             | -               | Reserved<br>The value read                                                            | d from this bit                                                                                                                           | is indetermina  | ate. Do not se  | t this bit.   |            |  |  |  |  |

| 5             | ET2             | Timer 2 overf<br>Clear to disab<br>Set to enable                                      | le timer 2 ove                                                                                                                            | rflow interrupt |                 |               |            |  |  |  |  |

| 4             | ES              | Serial port Er<br>Clear to disab<br>Set to enable                                     | le serial port i                                                                                                                          | •               |                 |               |            |  |  |  |  |

| 3             | ET1             | Timer 1 overf<br>Clear to disab<br>Set to enable                                      | le timer 1 ove                                                                                                                            | rflow interrupt |                 |               |            |  |  |  |  |

| 2             | EX1             | External inter<br>Clear to disab<br>Set to enable                                     | le external int                                                                                                                           | errupt 1.       |                 |               |            |  |  |  |  |

| 1             | ET0             | Clear to disab                                                                        | <b>Timer 0 overflow interrupt Enable bit</b><br>Clear to disable timer 0 overflow interrupt.<br>Set to enable timer 0 overflow interrupt. |                 |                 |               |            |  |  |  |  |

| 0             | EX0             | External inter<br>Clear to disab<br>Set to enable                                     | le external int                                                                                                                           | errupt 0.       |                 |               |            |  |  |  |  |

Reset Value = 0X00 0000b Bit addressable

**Table 13.** IP RegisterIP - Interrupt Priority Register (B8h)

| 7             | 6               | 5                     | 4                                                                            | 3                                 | 2              | 1             | 0   |  |  |

|---------------|-----------------|-----------------------|------------------------------------------------------------------------------|-----------------------------------|----------------|---------------|-----|--|--|

| -             | -               | PT2                   | PS                                                                           | PT1                               | PX1            | PT0           | PX0 |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Descriptio            | n                                                                            |                                   |                |               |     |  |  |

| 7             | -               | Reserved<br>The value | read from this                                                               | bit is indetern                   | ninate. Do not | set this bit. |     |  |  |

| 6             | -               | Reserved<br>The value | read from this                                                               | bit is indetern                   | ninate. Do not | set this bit. |     |  |  |

| 5             | PT2             |                       | erflow interr<br>2H for priority                                             | <b>upt Priority b</b><br>y level. | it             |               |     |  |  |

| 4             | PS              |                       | t <b>Priority bit</b><br>SH for priority                                     | level.                            |                |               |     |  |  |

| 3             | PT1             |                       | erflow interr                                                                | <b>upt Priority b</b><br>y level. | it             |               |     |  |  |

| 2             | PX1             |                       | nterrupt 1 Pri                                                               | •                                 |                |               |     |  |  |

| 1             | PT0             |                       | Timer 0 overflow interrupt Priority bit<br>Refer to PT0H for priority level. |                                   |                |               |     |  |  |

| 0             | PX0             |                       | nterrupt 0 Pri                                                               |                                   |                |               |     |  |  |

Reset Value = XX00 0000b Bit addressable

# Table 14.IPH RegisterIPH - Interrupt Priority High Register (B7h)

| 7             | 6               | 5                                                                                                                                | 4                                                                  | 3                       | 2              | 1           | 0    |

|---------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-------------------------|----------------|-------------|------|

| -             | -               | PT2H                                                                                                                             | PSH                                                                | PT1H                    | PX1H           | РТОН        | РХОН |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                      |                                                                    |                         |                |             |      |

| 7             | -               | <b>Reserved</b><br>The value rea                                                                                                 | d from this bit                                                    | is indetermina          | ate. Do not se | t this bit. |      |

| 6             | -               | <b>Reserved</b><br>The value rea                                                                                                 | d from this bit                                                    | is indetermina          | ate. Do not se | t this bit. |      |

| 5             | PT2H            | Timer 2 over           PT2H         PT2           0         0           1         0           1         1                        | f <b>low interrup</b><br><u>Priority Leve</u><br>Lowest<br>Highest | t Priority High<br>한    | n bit          |             |      |

| 4             | PSH             | Serial port P           PSH         PS           0         0           0         1           1         0           1         1   | riority High b<br><u>Priority Leve</u><br>Lowest<br>Highest        |                         |                |             |      |

| 3             | PT1H            | Timer 1 over           PT1H         PT1           0         0           0         1           1         0           1         1  |                                                                    | t Priority High<br>키    | n bit          |             |      |

| 2             | PX1H            | External inte           PX1H         PX1           0         0           1         0           1         1           1         1 | rrupt 1 Priori<br>Priority Leve<br>Lowest<br>Highest               |                         |                |             |      |

| 1             | РТОН            | Timer 0 over           PT0H         PT0           0         0           1         0           1         1                        |                                                                    | t Priority High<br>한    | n bit          |             |      |

| 0             | РХОН            | External inte           PX0H         PX0           0         0           1         1           1         1                       | <b>rrupt 0 Priori</b><br><u>Priority Leve</u><br>Lowest<br>Highest | ty High bit<br><u>키</u> |                |             |      |

Reset Value = XX00 0000b Not bit addressable

# ONCE<sup>™</sup> Mode (ON Chip Emulation)

The ONCE mode facilitates testing and debugging of systems using TS80C52X2 without removing the circuit from the board. The ONCE mode is invoked by driving certain pins of the TS80C52X2; the following sequence must be exercised:

- Pull ALE low while the device is in reset (RST high) and PSEN is high.

- Hold ALE low as RST is deactivated.

While the TS80C52X2 is in ONCE mode, an emulator or test CPU can be used to drive the circuit Table 26. shows the status of the port pins during ONCE mode.

Normal operation is restored when normal reset is applied.

Table 16. External Pin Status during ONCE Mode

| ALE              | PSEN             | Port 0 | Port 1           | Port 2           | Port 3           | XTAL1/2 |

|------------------|------------------|--------|------------------|------------------|------------------|---------|

| Weak pull-<br>up | Weak pull-<br>up | Float  | Weak pull-<br>up | Weak pull-<br>up | Weak pull-<br>up | Active  |

TS8xCx2X2

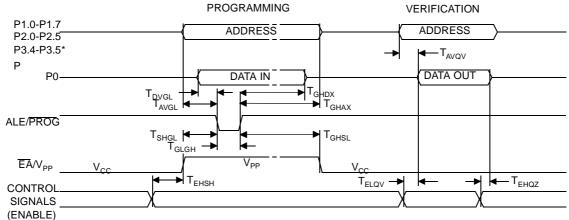

Control and program signals must be held at the levels indicated in Table 35.

**Definition of terms**

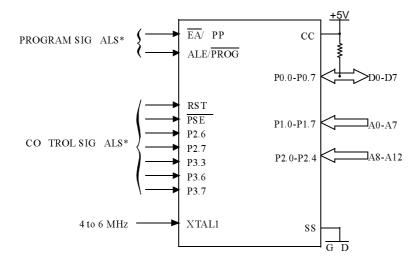

Address Lines: P1.0-P1.7, P2.0-P2.4 respectively for A0-A12 Data Lines: P0.0-P0.7 for D0-D7 Control Signals: RST, PSEN, P2.6, P2.7, P3.3, P3.6, P3.7. Program Signals: ALE/PROG, EA/VPP.

Table 20. EPROM Set-up Modes

| Mode                                      | RST | PSEN | ALE/<br>PROG | EA/<br>VPP | P2.6 | P2.7 | P3.3 | P3.6 | P3.7 |

|-------------------------------------------|-----|------|--------------|------------|------|------|------|------|------|

| Program Code data                         | 1   | 0    | IJ           | 12.75V     | 0    | 1    | 1    | 1    | 1    |

| Verify Code data                          | 1   | 0    | 1            | 1          | 0    |      | 0    | 1    | 1    |

| Program Encryption<br>Array Address 0-3Fh | 1   | 0    | U            | 12.75V     | 0    | 1    | 1    | 0    | 1    |

| Read Signature Bytes                      | 1   | 0    | 1            | 1          | 0    |      | 0    | 0    | 0    |

| Program Lock bit 1                        | 1   | 0    | ប            | 12.75V     | 1    | 1    | 1    | 1    | 1    |

| Program Lock bit 2                        | 1   | 0    | ъ            | 12.75V     | 1    | 1    | 1    | 0    | 0    |

| Program Lock bit 3                        | 1   | 0    | Ъ            | 12.75V     | 1    | 0    | 1    | 1    | 0    |

### Figure 11. Set-Up Modes Configuration

\* See Table 31. for proper value on these inputs

12,000  $\mu$ W/cm<sup>2</sup> rating for 30 minutes, at a distance of about 25 mm, should be sufficient. An exposure of 1 hour is recommended with most of standard erasers.

Erasure of the EPROM begins to occur when the chip is exposed to light with wavelength shorter than approximately 4,000 Å. Since sunlight and fluorescent lighting have wavelengths in this range, exposure to these light sources over an extended time (about 1 week in sunlight, or 3 years in room-level fluorescent lighting) could cause inadvertent erasure. If an application subjects the device to this type of exposure, it is suggested that an opaque label be placed over the window.

**Signature Bytes** The TS80/87C52X2 has four signature bytes in location 30h, 31h, 60h and 61h. To read these bytes follow the procedure for EPROM verify but activate the control lines provided in Table 31. for Read Signature Bytes. Table 35. shows the content of the signature byte for the TS80/87C52X2.

| Location | Contents | Comment                  |  |  |

|----------|----------|--------------------------|--|--|

| 30h      | 58h      | Manufacturer Code: Atmel |  |  |

| 31h      | 57h      | Family Code: C51 X2      |  |  |

| 60h      | 2Dh      | Product name: TS80C52X2  |  |  |

| 60h      | ADh      | Product name:TS87C52X2   |  |  |

| 60h      | 20h      | Product name: TS80C32X2  |  |  |

| 61h      | FFh      | Product revision number  |  |  |

Table 21. Signature Bytes Content

# TS8xCx2X2

| Table 22. DC Parameters in Standard Voltage (Continued | Table 22. | tage (Continued) |

|--------------------------------------------------------|-----------|------------------|

|--------------------------------------------------------|-----------|------------------|

| Symbol                            | Parameter                                         | Min                                                                     | Тур               | Мах                                                   | Unit        | Test Conditions                                                                                                |

|-----------------------------------|---------------------------------------------------|-------------------------------------------------------------------------|-------------------|-------------------------------------------------------|-------------|----------------------------------------------------------------------------------------------------------------|

| V <sub>OH</sub>                   | Output High Voltage, ports 1, 2, 3                | V <sub>CC</sub> - 0.3<br>V <sub>CC</sub> - 0.7<br>V <sub>CC</sub> - 1.5 |                   |                                                       | V<br>V<br>V | I <sub>OH</sub> = -10 μA<br>I <sub>OH</sub> = -30 μA<br>I <sub>OH</sub> = -60 μA<br>V <sub>CC</sub> = 5V ± 10% |

| V <sub>OH1</sub>                  | Output High Voltage, port 0                       | V <sub>CC</sub> - 0.3<br>V <sub>CC</sub> - 0.7<br>V <sub>CC</sub> - 1.5 |                   |                                                       | V<br>V<br>V | $I_{OH}$ = -200 µA<br>$I_{OH}$ = -3.2 mA<br>$I_{OH}$ = -7.0 mA<br>$V_{CC}$ = 5V ± 10%                          |

| V <sub>OH2</sub>                  | Output High Voltage,ALE, PSEN                     | V <sub>CC</sub> - 0.3<br>V <sub>CC</sub> - 0.7<br>V <sub>CC</sub> - 1.5 |                   |                                                       | V<br>V<br>V | $I_{OH}$ = -100 µA<br>$I_{OH}$ = -1.6 mA<br>$I_{OH}$ = -3.5 mA<br>$V_{CC}$ = 5V ± 10%                          |

| R <sub>RST</sub>                  | RST Pulldown Resistor                             | 50                                                                      | 90 <sup>(5)</sup> | 200                                                   | kΩ          |                                                                                                                |

| IIL                               | Logical 0 Input Current ports 1, 2 and 3          |                                                                         |                   | -50                                                   | μΑ          | Vin = 0.45V                                                                                                    |

| ILI                               | Input Leakage Current                             |                                                                         |                   | ±10                                                   | μΑ          | $0.45V < Vin < V_{CC}$                                                                                         |

| I <sub>TL</sub>                   | Logical 1 to 0 Transition Current, ports 1, 2, 3  |                                                                         |                   | -650                                                  | μΑ          | Vin = 2.0 V                                                                                                    |

| C <sub>IO</sub>                   | Capacitance of I/O Buffer                         |                                                                         |                   | 10                                                    | pF          | Fc = 1 MHz<br>Ta = 25°C                                                                                        |

| I <sub>PD</sub>                   | Power Down Current                                |                                                                         | 20 (5)            | 50                                                    | μA          | $2.0 \text{ V} < \text{V}_{\text{CC}} < 5.5 \text{V}^{(3)}$                                                    |

| I <sub>CC</sub><br>under<br>RESET | Power Supply Current Maximum values, X1 mode: (7) |                                                                         |                   | 1 + 0.4 Freq<br>(MHz)<br>at12MHz 5.8<br>at16MHz 7.4   | mA          | $V_{\rm CC} = 5.5 V^{(1)}$                                                                                     |

| I <sub>CC</sub><br>operating      | Power Supply Current Maximum values, X1 mode: (7) |                                                                         |                   | 3 + 0.6 Freq<br>(MHz)<br>at12MHz 10.2<br>at16MHz 12.6 | mA          | $V_{CC} = 5.5 V^{(8)}$                                                                                         |

| I <sub>CC</sub><br>idle           | Power Supply Current Maximum values, X1 mode: (7) |                                                                         |                   | 0.25+0.3 Freq<br>(MHz)<br>at12MHz 3.9<br>at16MHz 5.1  | mA          | $V_{\rm CC} = 5.5 V^{(2)}$                                                                                     |

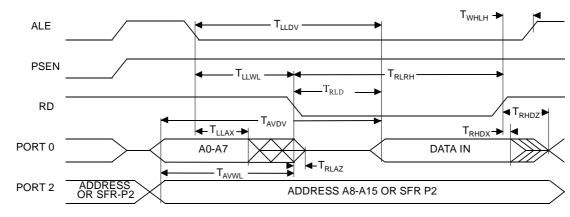

# External Data Memory Read Cycle

Figure 20. External Data Memory Read Cycle

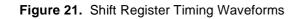

# Serial Port Timing - Shift Register Mode

Table 32. Symbol Description

| Symbol            | Parameter                                |

|-------------------|------------------------------------------|

| T <sub>XLXL</sub> | Serial port clock cycle time             |

| T <sub>QVHX</sub> | Output data set-up to clock rising edge  |

| T <sub>XHQX</sub> | Output data hold after clock rising edge |

| T <sub>XHDX</sub> | Input data hold after clock rising edge  |

| T <sub>XHDV</sub> | Clock rising edge to input data valid    |

| Speed             | -I<br>40 I | M<br>MHz |     | ИНz | stan<br>mod | V<br>dard<br>le 40<br>Hz |     | node<br>MHz<br>MHz | stan<br>mo | L<br>dard<br>ode<br>MHz | Units |

|-------------------|------------|----------|-----|-----|-------------|--------------------------|-----|--------------------|------------|-------------------------|-------|

| Symbol            | Min        | Max      | Min | Max | Min         | Max                      | Min | Max                | Min        | Max                     |       |

| T <sub>XLXL</sub> | 300        |          | 200 |     | 300         |                          | 300 |                    | 400        |                         | ns    |

| T <sub>QVHX</sub> | 200        |          | 117 |     | 200         |                          | 200 |                    | 283        |                         | ns    |

| T <sub>XHQX</sub> | 30         |          | 13  |     | 30          |                          | 30  |                    | 47         |                         | ns    |

| T <sub>XHDX</sub> | 0          |          | 0   |     | 0           |                          | 0   |                    | 0          |                         | ns    |

| $T_{XHDV}$        |            | 117      |     | 34  |             | 117                      |     | 117                |            | 200                     | ns    |

| Symbol            | Туре | Standard<br>Clock | X2 Clock | -М  | -V  | -L  | Units |

|-------------------|------|-------------------|----------|-----|-----|-----|-------|

| T <sub>XLXL</sub> | Min  | 12 T              | 6 T      |     |     |     | ns    |

| T <sub>QVHX</sub> | Min  | 10 T - x          | 5 T - x  | 50  | 50  | 50  | ns    |

| T <sub>XHQX</sub> | Min  | 2 T - x           | T - x    | 20  | 20  | 20  | ns    |

| T <sub>XHDX</sub> | Min  | х                 | х        | 0   | 0   | 0   | ns    |

| T <sub>XHDV</sub> | Max  | 10 T - x          | 5 T- x   | 133 | 133 | 133 | ns    |

Table 34. AC Parameters for a Variable Clock: Derating Formula

# Shift Register Timing Waveforms

# **EPROM Programming and** Verification Characteristics

$T_A$  = 21°C to 27°C;  $V_{SS}$  = 0V;  $~V_{CC}$  = 5V  $\pm$  10% while programming.  $V_{CC}$  = operating range while verifying.

Table 35.

EPROM Programming Parameters

| Symbol              | Parameter                         | Min                  | Мах                  | Units |

|---------------------|-----------------------------------|----------------------|----------------------|-------|

| V <sub>PP</sub>     | Programming Supply Voltage        | 12.5                 | 13                   | V     |

| I <sub>PP</sub>     | Programming Supply Current        |                      | 75                   | mA    |

| 1/T <sub>CLCL</sub> | Oscillator Frquency               | 4                    | 6                    | MHz   |

| T <sub>AVGL</sub>   | Address Setup to PROG Low         | 48 T <sub>CLCL</sub> |                      |       |

| T <sub>GHAX</sub>   | Adress Hold after PROG            | 48 T <sub>CLCL</sub> |                      |       |

| T <sub>DVGL</sub>   | Data Setup to PROG Low            | 48 T <sub>CLCL</sub> |                      |       |

| T <sub>GHDX</sub>   | Data Hold after PROG              | 48 T <sub>CLCL</sub> |                      |       |

| T <sub>EHSH</sub>   | (Enable) High to V <sub>PP</sub>  | 48 T <sub>CLCL</sub> |                      |       |

| T <sub>SHGL</sub>   | V <sub>PP</sub> Setup to PROG Low | 10                   |                      | μs    |

| T <sub>GHSL</sub>   | V <sub>PP</sub> Hold after PROG   | 10                   |                      | μs    |

| T <sub>GLGH</sub>   | PROG Width                        | 90                   | 110                  | μs    |

| T <sub>AVQV</sub>   | Address to Valid Data             |                      | 48 T <sub>CLCL</sub> |       |

| T <sub>ELQV</sub>   | ENABLE Low to Data Valid          |                      | 48 T <sub>CLCL</sub> |       |

| T <sub>EHQZ</sub>   | Data Float after ENABLE           | 0                    | 48 T <sub>CLCL</sub> |       |

# EPROM Programming and Verification Waveforms

### Figure 22. EPROM Programming and Verification Waveforms

\* 8KB: up to P2.4, 16KB: up to P2.5, 32KB: up to P3.4, 64KB: up to P3.5

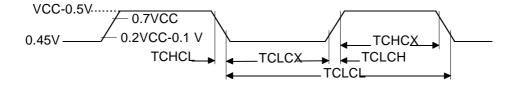

# External Clock Drive Characteristics (XTAL1)

Table 36. AC Parameters

| Symbol                               | Parameter               | Min | Max | Units |

|--------------------------------------|-------------------------|-----|-----|-------|

| T <sub>CLCL</sub>                    | Oscillator Period       | 25  |     | ns    |

| T <sub>CHCX</sub>                    | High Time               | 5   |     | ns    |

| T <sub>CLCX</sub>                    | Low Time                | 5   |     | ns    |

| T <sub>CLCH</sub>                    | Rise Time               |     | 5   | ns    |

| T <sub>CHCL</sub>                    | Fall Time               |     | 5   | ns    |

| T <sub>CHCX</sub> /T <sub>CLCX</sub> | Cyclic ratio in X2 mode | 40  | 60  | %     |

# External Clock Drive Waveforms

Figure 23. External Clock Drive Waveforms

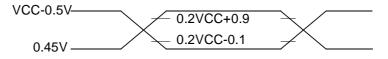

## AC Testing Input/Output Waveforms

Figure 24. AC Testing Input/Output Waveforms

INPUT/OUTPUT

AC inputs during testing are driven at V<sub>CC</sub> - 0.5 for a logic "1" and 0.45V for a logic "0". Timing measurement are made at V<sub>IH</sub> min for a logic "1" and V<sub>IL</sub> max for a logic "0".

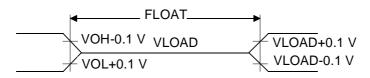

# **Float Waveforms**

## Figure 25. Float Waveforms

For timing purposes a port pin is no longer floating when a 100 mV change from load voltage occurs and begins to float when a 100 mV change from the loaded V<sub>OH</sub>/V<sub>OL</sub> level occurs.  $I_{OL}/I_{OH} \ge \pm 20$ mA.

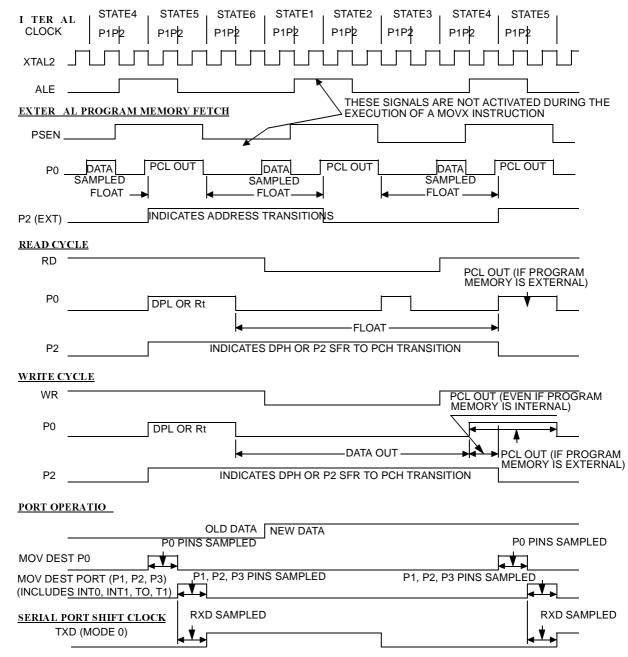

Figure 26. Clock Waveforms

This diagram indicates when signals are clocked internally. The time it takes the signals to propagate to the pins, however, ranges from 25 to 125 ns. This propagation delay is dependent on variables such as temperature and pin loading. Propagation also varies from output to output and component. Typically though ( $T_A = 25^{\circ}C$  fully loaded) RD and WR propagation delays are approximately 50ns. The other signals are typically 85 ns. Propagation delays are incorporated in the AC specifications.

### Table 37. Possible Ordering Entries (Continued)

| Part Number <sup>(3)</sup> | Memory Size | Supply Voltage  | Temperature<br>Range | Max Frequency         | Package | Packing |

|----------------------------|-------------|-----------------|----------------------|-----------------------|---------|---------|

| AT80C32X2-RLTUL            | ROMLess     | 2.7 to 5.5V     | Industrial & Green   | 30 MHz <sup>(1)</sup> | VQFP44  | Tray    |

| AT80C32X2-3CSUV            | ROMLess     | 5V ±10%         | Industrial & Green   | 60 MHz <sup>(3)</sup> | PDIL40  | Stick   |

| AT80C32X2-SLSUV            | ROMLess     | 5V ±10%         | Industrial & Green   | 60 MHz <sup>(3)</sup> | PLCC44  | Stick   |

| AT80C32X2-RLTUV            | ROMLess     | 5V ±10%         | Industrial & Green   | 60 MHz <sup>(3)</sup> | VQFP44  | Tray    |

|                            |             |                 |                      |                       |         |         |

| TS80C52X2zzz-MCA           | 8K ROM      | 2.7 to 5.5V     | Commercial           | 40 MHz <sup>(1)</sup> | PDIL40  | Stick   |

| TS80C52X2zzz-MCB           | 8K ROM      | 2.7 to 5.5V     | Commercial           | 40 MHz <sup>(1)</sup> | PLCC44  | Stick   |

| TS80C52X2zzz-MCC           | 8K ROM      | 2.7 to 5.5V     | Commercial           | 40 MHz <sup>(1)</sup> | PQFP44  | Tray    |

| TS80C52X2zzz-MCE           | 8K ROM      | 2.7 to 5.5V     | Commercial           | 40 MHz <sup>(1)</sup> | VQFP44  | Tray    |

| TS80C52X2zzz-LCA           | 8K ROM      | 2.7 to 5.5V     | Commercial           | 30 MHz <sup>(1)</sup> | PDIL40  | Stick   |

| TS80C52X2zzz-LCB           | 8K ROM      | 2.7 to 5.5V     | Commercial           | 30 MHz <sup>(1)</sup> | PLCC44  | Stick   |

| TS80C52X2zzz-LCC           | 8K ROM      | 2.7 to 5.5V     | Commercial           | 30 MHz <sup>(1)</sup> | PQFP44  | Tray    |

| TS80C52X2zzz-LCE           | 8K ROM      | 2.7 to 5.5V     | Commercial           | 30 MHz <sup>(1)</sup> | VQFP44  | Tray    |

| TS80C52X2zzz-VCA           | 8K ROM      | 5V <u>±</u> 10% | Commercial           | 60 MHz <sup>(3)</sup> | PDIL40  | Stick   |

| TS80C52X2zzz-VCB           | 8K ROM      | 5V ±10%         | Commercial           | 60 MHz <sup>(3)</sup> | PLCC44  | Stick   |

| TS80C52X2zzz-VCC           | 8K ROM      | 5V ±10%         | Commercial           | 60 MHz <sup>(3)</sup> | PQFP44  | Tray    |

| TS80C52X2zzz-VCE           | 8K ROM      | 5V ±10%         | Commercial           | 60 MHz <sup>(3)</sup> | VQFP44  | Tray    |

| TS80C52X2zzz-MIA           | 8K ROM      | 5V ±10%         | Industrial           | 40 MHz <sup>(1)</sup> | PDIL40  | Stick   |

| TS80C52X2zzz-MIB           | 8K ROM      | 5V ±10%         | Industrial           | 40 MHz <sup>(1)</sup> | PLCC44  | Stick   |

| TS80C52X2zzz-MIC           | 8K ROM      | 5V ±10%         | Industrial           | 40 MHz <sup>(1)</sup> | PQFP44  | Tray    |

| TS80C52X2zzz-MIE           | 8K ROM      | 5V ±10%         | Industrial           | 40 MHz <sup>(1)</sup> | VQFP44  | Tray    |

| TS80C52X2zzz-LIA           | 8K ROM      | 2.7 to 5.5V     | Industrial           | 30 MHz <sup>(1)</sup> | PDIL40  | Stick   |

| TS80C52X2zzz-LIB           | 8K ROM      | 2.7 to 5.5V     | Industrial           | 30 MHz <sup>(1)</sup> | PLCC44  | Stick   |

| TS80C52X2zzz-LIC           | 8K ROM      | 2.7 to 5.5V     | Industrial           | 30 MHz <sup>(1)</sup> | PQFP44  | Tray    |

| TS80C52X2zzz-LIE           | 8K ROM      | 2.7 to 5.5V     | Industrial           | 30 MHz <sup>(1)</sup> | VQFP44  | Tray    |

| TS80C52X2zzz-VIA           | 8K ROM      | 5V ±10%         | Industrial           | 60 MHz <sup>(3)</sup> | PDIL40  | Stick   |

| TS80C52X2zzz-VIB           | 8K ROM      | 5V ±10%         | Industrial           | 60 MHz <sup>(3)</sup> | PLCC44  | Stick   |

| TS80C52X2zzz-VIC           | 8K ROM      | 5V ±10%         | Industrial           | 60 MHz <sup>(3)</sup> | PQFP44  | Tray    |

| TS80C52X2zzz-VIE           | 8K ROM      | 5V ±10%         | Industrial           | 60 MHz <sup>(3)</sup> | VQFP44  | Tray    |

|                            |             |                 |                      |                       |         |         |

| AT80C52X2zzz-3CSUM         | 8K ROM      | 5V ±10%         | Industrial & Green   | 40 MHz <sup>(1)</sup> | PDIL40  | Stick   |

| AT80C52X2zzz-SLSUM         | 8K ROM      | 5V ±10%         | Industrial & Green   | 40 MHz <sup>(1)</sup> | PLCC44  | Stick   |

| AT80C52X2zzz-RLTUM         | 8K ROM      | 5V ±10%         | Industrial & Green   | 40 MHz <sup>(1)</sup> | VQFP44  | Tray    |