#### NXP USA Inc. - MKV31F256VLH12P Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 120MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | DMA, PWM, WDT                                                           |

| Number of I/O              | 46                                                                      |

| Program Memory Size        | 256KB (256K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 48K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                            |

| Data Converters            | A/D 2x16b; D/A 1x12b                                                    |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 64-LQFP                                                                 |

| Supplier Device Package    | 64-LQFP (10x10)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mkv31f256vlh12p |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

• Up to 70 general-purpose I/O (GPIO)

- Implements Field Orient Control (FOC) using Back EMF to improve motor efficiency

- Utilizes SpinTAC control theory that improves overall system performance and reliability

#### **Ordering Information**

| Part Number     | Mei        | Number of GPIOs |    |

|-----------------|------------|-----------------|----|

|                 | Flash (KB) | SRAM (KB)       |    |

| MKV31F256VLL12  | 256        | 48              | 70 |

| MKV31F256VLH12  | 256        | 48              | 46 |

| MKV31F256VLH12P | 248        | 48              | 46 |

#### **Related Resources**

| Туре                           | Description                                                                                                                     | Resource                                                               |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| Selector<br>Guide              | The Freescale Solution Advisor is a web-based tool that features interactive application wizards and a dynamic product selector | Product Selector                                                       |

| Product Brief                  | The Product Brief contains concise overview/summary information to enable quick evaluation of a device for design suitability.  | KV30FKV31FPB                                                           |

| Reference<br>Manual            | The Reference Manual contains a comprehensive description of the structure and function (operation) of a device.                | KV31P100M120SF8RM                                                      |

| Data Sheet                     | The Data Sheet is this document. It includes electrical characteristics and signal connections.                                 | KV31P100M120SF8                                                        |

| Chip Errata                    | The chip mask set Errata provides additional or corrective information for a particular device mask set.                        | KINETIS_xN51M <sup>1</sup>                                             |

| KMS User<br>Guide              | The KMS User Guide provides a comprehensive description of the features and functions of the Kinetis Motor Suite solution.      | Kinetis Motor Suite User's Guide (KMS100UG) <sup>2</sup>               |

| KMS API<br>Reference<br>Manual | The KMS API reference manual provides a comprehensive description of the API of the Kinetis Motor Suite function blocks.        | Kinetis Motor Suite API<br>Reference Manual<br>(KMS100RM) <sup>2</sup> |

| Package<br>drawing             | Package dimensions are provided by part number:<br>• MKV31F256VLL12<br>• MKV31F256VLH12<br>• MKV31F256VLH12P                    | Package drawing:<br>• 98ASS23308W<br>• 98ASS23234W<br>• 98ASS23234W    |

1. To find the associated resource, go to freescale.com and perform a search using this term with the *x* replaced by the revision of the device you are using.

2. To find the associated resource, go to freescale.com and perform a search using Document ID

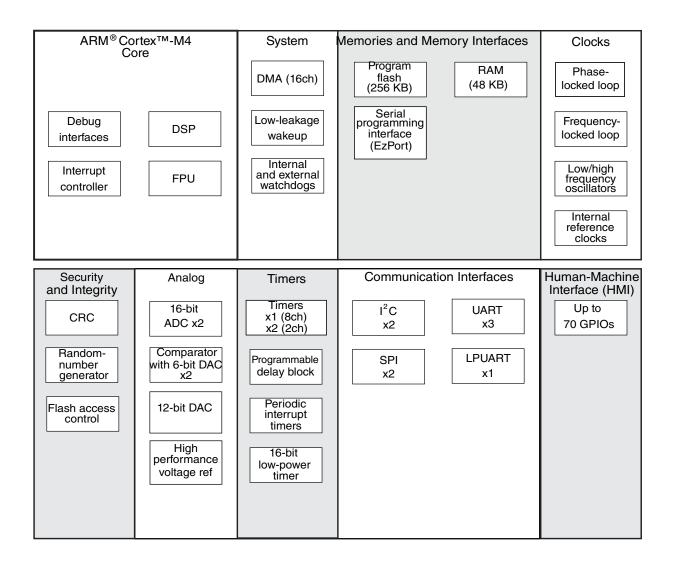

Figure 1 shows the functional modules in the chip.

### Figure 1. Functional block diagram

| Symbol           | Description                                                                                         | Min. | Тур.  | Max. | Unit | Notes |

|------------------|-----------------------------------------------------------------------------------------------------|------|-------|------|------|-------|

|                  | $2.7 \text{ V} \le \text{V}_{\text{DD}} \le 3.6 \text{ V}, \text{I}_{\text{OL}} = 3 \text{ mA}$     | —    | _     | 0.5  | V    |       |

|                  | $1.71 \text{ V} \le \text{V}_{\text{DD}} \le 2.7 \text{ V}, \text{ I}_{\text{OL}} = 1.5 \text{ mA}$ | _    | —     | 0.5  | V    |       |

| I <sub>OLT</sub> | Output low current total for all ports                                                              | —    | —     | 100  | mA   |       |

| I <sub>IN</sub>  | Input leakage current (per pin) for full temperature range                                          |      |       |      |      |       |

|                  | All pins other than high drive port pins                                                            | _    | 0.002 | 0.5  | μA   | 1, 2  |

|                  | High drive port pins                                                                                | _    | 0.004 | 0.5  | μA   |       |

| I <sub>IN</sub>  | Input leakage current (total all pins) for full temperature range                                   |      | —     | 1.0  | μA   | 2     |

| R <sub>PU</sub>  | Internal pullup resistors                                                                           | 20   |       | 50   | kΩ   | 3     |

| R <sub>PD</sub>  | Internal pulldown resistors                                                                         | 20   |       | 50   | kΩ   | 4     |

Table 3. Voltage and current operating behaviors (continued)

1. PTB0, PTB1, PTC3, PTC4, PTD4, PTD5, PTD6, and PTD7 I/O have both high drive and normal drive capability selected by the associated PTx\_PCRn[DSE] control bit. All other GPIOs are normal drive only.

2. Measured at VDD=3.6V

3. Measured at V<sub>DD</sub> supply voltage = V<sub>DD</sub> min and Vinput = V<sub>SS</sub>

4. Measured at  $V_{DD}$  supply voltage =  $V_{DD}$  min and Vinput =  $V_{DD}$

## 2.2.4 Power mode transition operating behaviors

All specifications except  $t_{POR}$ , and VLLSx $\rightarrow$ RUN recovery times in the following table assume this clock configuration:

- CPU and system clocks = 80 MHz

- Bus clock = 40 MHz

- Flash clock = 20 MHz

- MCG mode: FEI

#### Table 4. Power mode transition operating behaviors

| Symbol           | Description                                                                                                                                                        | Min. | Тур. | Max. | Unit | Notes |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|-------|

| t <sub>POR</sub> | After a POR event, amount of time from the point $V_{DD}$ reaches 1.71 V to execution of the first instruction across the operating temperature range of the chip. | _    | _    | 300  | μs   | 1     |

|                  | • VLLS0 $\rightarrow$ RUN                                                                                                                                          | _    | _    | 140  | μs   |       |

|                  | • VLLS1 $\rightarrow$ RUN                                                                                                                                          | _    | _    | 140  | μs   |       |

|                  | • VLLS2 $\rightarrow$ RUN                                                                                                                                          |      |      | 80   | μs   |       |

Table continues on the next page...

9

| Symbol | Description                     | Min. | Тур. | Max. | Unit | Notes |

|--------|---------------------------------|------|------|------|------|-------|

|        | <ul> <li>VLLS3 → RUN</li> </ul> |      |      |      |      |       |

|        |                                 | —    |      | 80   | μs   |       |

|        | <ul> <li>LLS2 → RUN</li> </ul>  |      |      | 6    |      |       |

|        |                                 | —    |      |      | μs   |       |

|        | <ul> <li>LLS3 → RUN</li> </ul>  |      |      | 6    |      |       |

|        |                                 | —    |      |      | μs   |       |

|        | <ul> <li>VLPS → RUN</li> </ul>  |      |      |      |      |       |

|        |                                 | —    | —    | 5.7  | μs   |       |

|        | STOP → RUN                      |      |      |      |      |       |

|        |                                 |      |      | 5.7  | μs   |       |

Table 4. Power mode transition operating behaviors (continued)

1. Normal boot (FTFA\_OPT[LPBOOT]=1)

## 2.2.5 Power consumption operating behaviors

The current parameters in the table below are derived from code executing a while(1) loop from flash, unless otherwise noted.

The IDD typical values represent the statistical mean at 25°C, and the IDD maximum values for RUN, WAIT, VLPR, and VLPW represent data collected at 125°C junction temperature unless otherwise noted. The maximum values represent characterized results equivalent to the mean plus three times the standard deviation (mean + 3 sigma).

| Symbol                | Description                                                                                                      | Min. | Тур.  | Max.     | Unit | Notes   |

|-----------------------|------------------------------------------------------------------------------------------------------------------|------|-------|----------|------|---------|

| I <sub>DDA</sub>      | Analog supply current                                                                                            | —    | —     | See note | mA   | 1       |

| I <sub>DD_HSRUN</sub> | High Speed Run mode current - all peripheral<br>clocks disabled, CoreMark benchmark code<br>executing from flash |      |       |          |      |         |

|                       | @ 1.8V                                                                                                           | _    | 25.66 | 26.35    | mA   | 2, 3, 4 |

|                       | @ 3.0V                                                                                                           | _    | 25.75 | 26.44    | mA   |         |

| I <sub>DD_HSRUN</sub> | High Speed Run mode current - all peripheral clocks disabled, code executing from flash                          |      |       |          |      |         |

|                       | @ 1.8V                                                                                                           | _    | 23.6  | 24.29    | mA   | 2       |

|                       | @ 3.0V                                                                                                           | _    | 23.7  | 24.39    | mA   |         |

| I <sub>DD_HSRUN</sub> | High Speed Run mode current — all peripheral clocks enabled, code executing from flash                           |      |       |          |      |         |

|                       | @ 1.8V                                                                                                           | _    | 31.9  | 32.59    | mA   | 5       |

|                       | @ 3.0V                                                                                                           | _    | 32.0  | 32.69    | mA   |         |

Table 5. Power consumption operating behaviors

| Symbol                | Description                                                                    | Min. | Тур. | Max. | Unit | Notes |

|-----------------------|--------------------------------------------------------------------------------|------|------|------|------|-------|

|                       | @ 70°C                                                                         | _    | 1.79 | 2.10 | μA   |       |

|                       | @ 85°C                                                                         | —    | 2.9  | 4.70 | μA   |       |

|                       | @ 105°C                                                                        | —    | 5.7  | 8.10 | μA   |       |

| I <sub>DD_VLLS0</sub> | Very low-leakage stop mode 0 current at 3.0 V with POR detect circuit enabled  |      |      |      |      |       |

|                       | @ -40°C to 25°C                                                                | —    | 0.40 | 0.56 | μA   |       |

|                       | @ 70°C                                                                         | —    | 1.39 | 1.70 | μA   |       |

|                       | @ 85°C                                                                         | —    | 2.5  | 4.25 | μA   |       |

|                       | @ 105°C                                                                        | —    | 5.3  | 7.50 | μA   |       |

| I <sub>DD_VLLS0</sub> | Very low-leakage stop mode 0 current at 3.0 V with POR detect circuit disabled |      |      |      |      |       |

|                       | @ -40°C to 25°C                                                                | —    | 0.12 | 0.38 | μA   |       |

|                       | @ 70°C                                                                         | —    | 1.05 | 1.38 | μA   |       |

|                       | @ 85°C                                                                         | —    | 2.20 | 3.95 | μA   |       |

|                       | @ 105°C                                                                        | —    | 4.9  | 7.10 | μA   |       |

#### Table 5. Power consumption operating behaviors (continued)

- 1. The analog supply current is the sum of the active or disabled current for each of the analog modules on the device. See each module's specification for its supply current.

- 120MHz core and system clock, 60MHz bus clock, and 24MHz flash clock. MCG configured for PEE mode. All peripheral clocks disabled.

- 3. Cache on and prefetch on, low compiler optimization.

- 4. Coremark benchmark compiled using IAR 7.2 with optimization level low.

- 5. 120MHz core and system clock, 60MHz bus clock, and 24MHz flash clock. MCG configured for PEE mode. All peripheral clocks enabled.

- 6. 80 MHz core and system clock, 40 MHz bus clock, and 26.67 MHz flash clock. MCG configured for PEE mode. Compute operation.

- 7. 80MHz core and system clock, 40MHz bus clock, and 26.67MHz flash clock. MCG configured for FEI mode. All peripheral clocks disabled.

- 8. 80MHz core and system clock, 40MHz bus clock, and 26.67MHz flash clock. MCG configured for FEI mode. All peripheral clocks enabled.

- 9. 80MHz core and system clock, 40MHz bus clock, and 26.67MHz flash clock. MCG configured for FEI mode. Compute operation.

- 10. 25MHz core and system clock, 25MHz bus clock, and 25MHz flash clock. MCG configured for FEI mode.

- 11. 4 MHz core, system, and bus clock and 1MHz flash clock. MCG configured for BLPE mode. Compute operation. Code executing from flash.

- 12. 4 MHz core, system, and bus clock and 1MHz flash clock. MCG configured for BLPE mode. All peripheral clocks disabled. Code executing from flash.

- 13. 4 MHz core, system, and bus clock and 1MHz flash clock. MCG configured for BLPE mode. All peripheral clocks enabled but peripherals are not in active operation. Code executing from flash.

- 14. 4 MHz core, system, and bus clock and 1MHz flash clock. MCG configured for BLPE mode. All peripheral clocks disabled.

| Table 6. | Low power | mode peripheral | adders—typical value |

|----------|-----------|-----------------|----------------------|

|----------|-----------|-----------------|----------------------|

| Symbol                     | Description                                                                                                                                                                                                        |     |     | Tempera | ature (°C | <u>)</u> |     | Unit |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|---------|-----------|----------|-----|------|

|                            |                                                                                                                                                                                                                    | -40 | 25  | 50      | 70        | 85       | 105 |      |

| I <sub>IREFSTEN4MHz</sub>  | 4 MHz internal reference clock (IRC)<br>adder. Measured by entering STOP or<br>VLPS mode with 4 MHz IRC enabled.                                                                                                   | 56  | 56  | 56      | 56        | 56       | 56  | μA   |

| I <sub>IREFSTEN32KHz</sub> | 32 kHz internal reference clock (IRC)<br>adder. Measured by entering STOP<br>mode with the 32 kHz IRC enabled.                                                                                                     | 52  | 52  | 52      | 52        | 52       | 52  | μA   |

| I <sub>EREFSTEN4MHz</sub>  | External 4 MHz crystal clock adder.<br>Measured by entering STOP or VLPS<br>mode with the crystal enabled.                                                                                                         | 206 | 228 | 237     | 245       | 251      | 258 | uA   |

| I <sub>EREFSTEN32KHz</sub> | External 32 kHz crystal clock adder by<br>means of the OSC0_CR[EREFSTEN<br>and EREFSTEN] bits. Measured by<br>entering all modes with the crystal<br>enabled.                                                      |     |     |         |           |          |     |      |

|                            | VLLS1                                                                                                                                                                                                              | 440 | 490 | 540     | 560       | 570      | 580 | n A  |

|                            | VLLS3                                                                                                                                                                                                              | 440 | 490 | 540     | 560       | 570      | 580 |      |

|                            | LLS                                                                                                                                                                                                                | 490 | 490 | 540     | 560       | 570      | 680 |      |

|                            | VLPS                                                                                                                                                                                                               | 510 | 560 | 560     | 560       | 610      | 680 |      |

|                            | STOP                                                                                                                                                                                                               | 510 | 560 | 560     | 560       | 610      | 680 |      |

| I <sub>48MIRC</sub>        | 48 Mhz internal reference clock                                                                                                                                                                                    | 350 | 350 | 350     | 350       | 350      | 350 | μA   |

| I <sub>CMP</sub>           | CMP peripheral adder measured by<br>placing the device in VLLS1 mode with<br>CMP enabled using the 6-bit DAC and a<br>single external input for compare.<br>Includes 6-bit DAC power consumption.                  | 22  | 22  | 22      | 22        | 22       | 22  | μA   |

| I <sub>UART</sub>          | UART peripheral adder measured by<br>placing the device in STOP or VLPS<br>mode with selected clock source waiting<br>for RX data at 115200 baud rate.<br>Includes selected clock source power<br>consumption.     |     |     |         |           |          |     |      |

|                            | MCGIRCLK (4 MHz internal reference                                                                                                                                                                                 | 66  | 66  | 66      | 66        | 66       | 66  | μA   |

|                            | clock)<br>>OSCERCLK (4 MHz external crystal)                                                                                                                                                                       | 214 | 237 | 246     | 254       | 260      | 268 |      |

| I <sub>BG</sub>            | Bandgap adder when BGEN bit is set<br>and device is placed in VLPx, LLS, or<br>VLLSx mode.                                                                                                                         | 45  | 45  | 45      | 45        | 45       | 45  | μA   |

| I <sub>ADC</sub>           | ADC peripheral adder combining the measured values at $V_{DD}$ and $V_{DDA}$ by placing the device in STOP or VLPS mode. ADC is configured for low power mode using the internal clock and continuous conversions. | 42  | 42  | 42      | 42        | 42       | 42  | μA   |

| Symbol                   | Description                    | Min. | Max. | Unit | Notes |

|--------------------------|--------------------------------|------|------|------|-------|

| f <sub>LPTMR_pin</sub>   | LPTMR clock                    | —    | 25   | MHz  |       |

| f <sub>LPTMR_ERCLK</sub> | LPTMR external reference clock | —    | 16   | MHz  |       |

| Table 9. | Device clock s | pecifications | (continued) |  |

|----------|----------------|---------------|-------------|--|

|          |                |               |             |  |

1. The frequency limitations in VLPR mode here override any frequency specification listed in the timing specification for any other module.

## 2.3.2 General switching specifications

These general purpose specifications apply to all signals configured for GPIO, UART, and timers.

Table 10. General switching specifications

| Symbol | Description                                                                                                  | Min. | Max. | Unit                | Notes |

|--------|--------------------------------------------------------------------------------------------------------------|------|------|---------------------|-------|

|        | GPIO pin interrupt pulse width (digital glitch filter disabled) — Synchronous path                           | 1.5  | _    | Bus clock<br>cycles | 1, 2  |

|        | External RESET and NMI pin interrupt pulse width — Asynchronous path                                         | 100  | _    | ns                  | 3     |

|        | GPIO pin interrupt pulse width (digital glitch filter disabled, passive filter disabled) — Asynchronous path | 50   | _    | ns                  | 4     |

|        | Mode select (EZP_CS) hold time after reset deassertion                                                       | 2    | _    | Bus clock<br>cycles |       |

|        | Port rise and fall time                                                                                      |      |      |                     | 5     |

|        | Slew disabled                                                                                                | _    |      |                     |       |

|        | <ul> <li>1.71 ≤ V<sub>DD</sub> ≤ 2.7V</li> </ul>                                                             | _    | 10   | ns                  |       |

|        | • $2.7 \le V_{DD} \le 3.6V$                                                                                  |      | 5    | ns                  |       |

|        | Slew enabled                                                                                                 | _    |      |                     |       |

|        | • 1.71 ≤ V <sub>DD</sub> ≤ 2.7V                                                                              | _    | 30   | ns                  |       |

|        | • $2.7 \le V_{DD} \le 3.6V$                                                                                  |      | 16   | ns                  |       |

- 1. This is the minimum pulse width that is guaranteed to pass through the pin synchronization circuitry. Shorter pulses may or may not be recognized. In Stop, VLPS, LLS, and VLLSx modes, the synchronizer is bypassed so shorter pulses can be recognized in that case.

- 2. The greater of synchronous and asynchronous timing must be met.

- 3. These pins have a passive filter enabled on the inputs. This is the shortest pulse width that is guaranteed to be recognized.

- 4. These pins do not have a passive filter on the inputs. This is the shortest pulse width that is guaranteed to be recognized.

- 5. 25 pF load

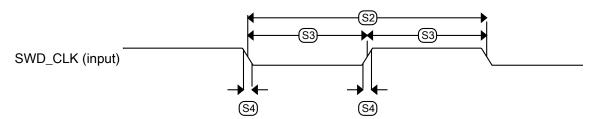

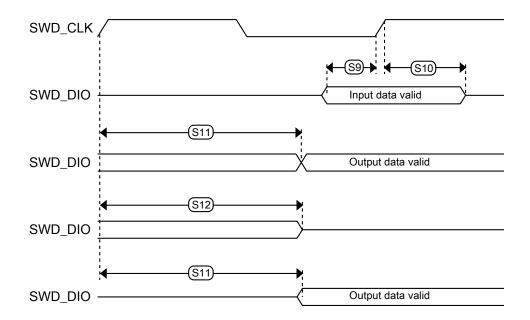

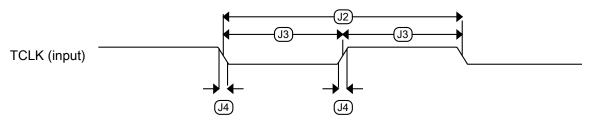

Figure 5. Serial wire clock input timing

## 3.1.2 JTAG electricals

#### Table 13. JTAG limited voltage range electricals

| Symbol | Description                 | Min. | Max. | Unit |

|--------|-----------------------------|------|------|------|

|        | Operating voltage           | 2.7  | 3.6  | V    |

| J1     | TCLK frequency of operation |      |      | MHz  |

|        | Boundary Scan               | 0    | 10   |      |

|        | JTAG and CJTAG              | 0    | 20   |      |

| J2     | TCLK cycle period           | 1/J1 | _    | ns   |

| J3     | TCLK clock pulse width      |      |      |      |

|        |                             | 50   | _    | ns   |

| Symbol | Description                                        | Min. | Max. | Unit |

|--------|----------------------------------------------------|------|------|------|

|        | Boundary Scan                                      | 25   |      | ns   |

|        | JTAG and CJTAG                                     |      |      |      |

| J4     | TCLK rise and fall times                           | —    | 3    | ns   |

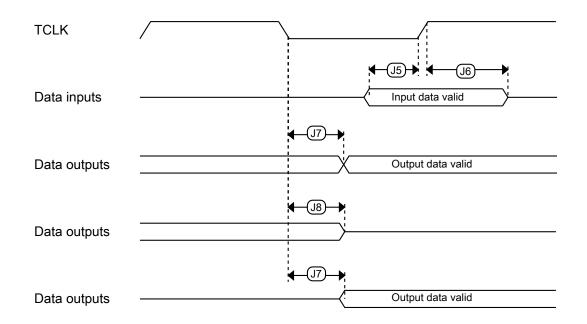

| J5     | Boundary scan input data setup time to TCLK rise   | 20   | _    | ns   |

| J6     | Boundary scan input data hold time after TCLK rise | 1    | _    | ns   |

| J7     | TCLK low to boundary scan output data valid        | —    | 25   | ns   |

| J8     | TCLK low to boundary scan output high-Z            | —    | 25   | ns   |

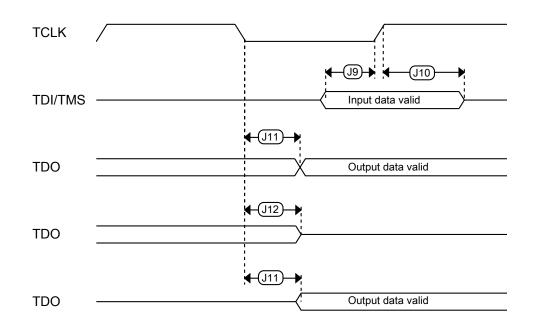

| J9     | TMS, TDI input data setup time to TCLK rise        | 8    | _    | ns   |

| J10    | TMS, TDI input data hold time after TCLK rise      | 1    | _    | ns   |

| J11    | TCLK low to TDO data valid                         | —    | 19   | ns   |

| J12    | TCLK low to TDO high-Z                             | —    | 19   | ns   |

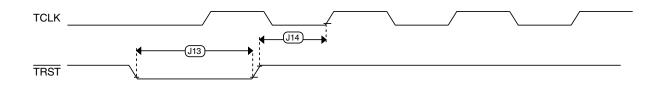

| J13    | TRST assert time                                   | 100  | _    | ns   |

| J14    | TRST setup time (negation) to TCLK high            | 8    | _    | ns   |

Table 13. JTAG limited voltage range electricals (continued)

Table 14. JTAG full voltage range electricals

| Symbol | Description                                        | Min. | Max. | Unit |

|--------|----------------------------------------------------|------|------|------|

|        | Operating voltage                                  | 1.71 | 3.6  | V    |

| J1     | TCLK frequency of operation                        |      |      | MHz  |

|        | Boundary Scan                                      | 0    | 10   |      |

|        | JTAG and CJTAG                                     | 0    | 15   |      |

| J2     | TCLK cycle period                                  | 1/J1 |      | ns   |

| J3     | TCLK clock pulse width                             |      |      |      |

|        | Boundary Scan                                      | 50   | _    | ns   |

|        | JTAG and CJTAG                                     | 33   | _    | ns   |

| J4     | TCLK rise and fall times                           | —    | 3    | ns   |

| J5     | Boundary scan input data setup time to TCLK rise   | 20   | _    | ns   |

| J6     | Boundary scan input data hold time after TCLK rise | 1.4  | _    | ns   |

| J7     | TCLK low to boundary scan output data valid        | _    | 27   | ns   |

| J8     | TCLK low to boundary scan output high-Z            | _    | 27   | ns   |

| J9     | TMS, TDI input data setup time to TCLK rise        | 8    | _    | ns   |

| J10    | TMS, TDI input data hold time after TCLK rise      | 1.4  | _    | ns   |

| J11    | TCLK low to TDO data valid                         | —    | 26.2 | ns   |

| J12    | TCLK low to TDO high-Z                             | —    | 26.2 | ns   |

| J13    | TRST assert time                                   | 100  | _    | ns   |

| J14    | TRST setup time (negation) to TCLK high            | 8    | _    | ns   |

Figure 7. Test clock input timing

Figure 8. Boundary scan (JTAG) timing

Figure 9. Test Access Port timing

# 3.2 System modules

There are no specifications necessary for the device's system modules.

# 3.3 Clock modules

| Symbol                   | Description                |                                                                                  | Min.   | Тур.  | Max.                                | Unit | Notes |

|--------------------------|----------------------------|----------------------------------------------------------------------------------|--------|-------|-------------------------------------|------|-------|

|                          |                            | $2197 \times f_{fll_{ref}}$                                                      |        |       | 1                                   |      |       |

|                          |                            | High range (DRS=11)                                                              | —      | 95.98 | —                                   | MHz  | -     |

|                          |                            | $2929 \times f_{fll\_ref}$                                                       |        |       |                                     |      |       |

| J <sub>cyc_fll</sub>     | FLL period jitter          | 1                                                                                | _      | _     | _                                   | ps   |       |

|                          | • f <sub>VCO</sub> = 48 M  |                                                                                  |        | 180   |                                     |      |       |

|                          | • f <sub>VCO</sub> = 98 M  | 1Hz                                                                              |        | 150   |                                     |      |       |

| t <sub>fll_acquire</sub> | FLL target freque          | ncy acquisition time                                                             | —      |       | 1                                   | ms   | 7     |

|                          |                            | Р                                                                                | ĹĹ     |       |                                     |      | !     |

| f <sub>vco</sub>         | VCO operating fre          | equency                                                                          | 48.0   |       | 120                                 | MHz  |       |

| I <sub>pll</sub>         | PLL operating cu           |                                                                                  | _      | 1060  | _                                   | μA   | 8     |

|                          | • PLL @ 96 P<br>= 2 MHz, V | MHz (f <sub>osc_hi_1</sub> = 8 MHz, f <sub>pll_ref</sub><br>DIV multiplier = 48) |        |       |                                     | -    |       |

| I <sub>pll</sub>         | PLL operating cu           |                                                                                  | _      | 600   |                                     | μA   | 8     |

|                          |                            | MHz (f <sub>osc_hi_1</sub> = 8 MHz, f <sub>pll_ref</sub><br>DIV multiplier = 24) |        | 000   |                                     | pro  |       |

| f <sub>pll_ref</sub>     | PLL reference fre          | quency range                                                                     | 2.0    | _     | 4.0                                 | MHz  |       |

| J <sub>cyc_pll</sub>     | PLL period jitter (        | RMS)                                                                             | _      | 120   | _                                   | ps   | 9     |

|                          | • f <sub>vco</sub> = 48 MI | Hz                                                                               | _      | 75    |                                     | ps   |       |

|                          | • f <sub>vco</sub> = 100 M | ſHz                                                                              |        |       |                                     | F -  |       |

| J <sub>acc_pll</sub>     | PLL accumulated            | jitter over 1µs (RMS)                                                            | _      | 1350  |                                     | ps   | 9     |

|                          | • f <sub>vco</sub> = 48 Mł | Hz                                                                               | _      | 600   |                                     | ps   |       |

|                          | • f <sub>vco</sub> = 100 M | 1Hz                                                                              |        | 000   |                                     | po   |       |

| D <sub>lock</sub>        | Lock entry freque          | ncy tolerance                                                                    | ± 1.49 |       | ± 2.98                              | %    |       |

| D <sub>unl</sub>         | Lock exit frequen          | cy tolerance                                                                     | ± 4.47 |       | ± 5.97                              | %    |       |

| t <sub>pll_lock</sub>    | Lock detector det          | ection time                                                                      | —      | —     | 150 × 10 <sup>-6</sup>              | S    | 10    |

|                          |                            |                                                                                  |        |       | + 1075(1/<br>f <sub>pll_ref</sub> ) |      |       |

| Table 15. | MCG specifications | (continued) |

|-----------|--------------------|-------------|

|-----------|--------------------|-------------|

- 1. This parameter is measured with the internal reference (slow clock) being used as a reference to the FLL (FEI clock mode).

- 2. 2.0 V <= VDD <= 3.6 V.

- 3. These typical values listed are with the slow internal reference clock (FEI) using factory trim and DMX32=0.

- The resulting system clock frequencies should not exceed their maximum specified values. The DCO frequency deviation (Δf<sub>dco\_t</sub>) over voltage and temperature should be considered.

- 5. These typical values listed are with the slow internal reference clock (FEI) using factory trim and DMX32=1.

- 6. The resulting clock frequency must not exceed the maximum specified clock frequency of the device.

- This specification applies to any time the FLL reference source or reference divider is changed, trim value is changed, DMX32 bit is changed, DRS bits are changed, or changing from FLL disabled (BLPE, BLPI) to FLL enabled (FEI, FEE, FBE, FBI). If a crystal/resonator is being used as the reference, this specification assumes it is already running.

- 8. Excludes any oscillator currents that are also consuming power while PLL is in operation.

- 9. This specification was obtained using a Freescale developed PCB. PLL jitter is dependent on the noise characteristics of each PCB and results will vary.

- This specification applies to any time the PLL VCO divider or reference divider is changed, or changing from PLL disabled (BLPE, BLPI) to PLL enabled (PBE, PEE). If a crystal/resonator is being used as the reference, this specification assumes it is already running.

26

| Symbol                | Description                        | Min. | Тур. | Max. | Unit | Notes |

|-----------------------|------------------------------------|------|------|------|------|-------|

| t <sub>hvpgm4</sub>   | Longword Program high-voltage time | —    | 7.5  | 18   | μs   | —     |

| t <sub>hversscr</sub> | Sector Erase high-voltage time     | —    | 13   | 113  | ms   | 1     |

| t <sub>hversall</sub> | Erase All high-voltage time        | —    | 104  | 904  | ms   | 1     |

Table 19.

NVM program/erase timing specifications

1. Maximum time based on expectations at cycling end-of-life.

#### 3.4.1.2 Flash timing specifications — commands Table 20. Flash command timing specifications

| Symbol                | Description                                   | Min. | Тур. | Max. | Unit | Notes |

|-----------------------|-----------------------------------------------|------|------|------|------|-------|

| t <sub>rd1sec2k</sub> | Read 1s Section execution time (flash sector) | _    | —    | 60   | μs   | 1     |

| t <sub>pgmchk</sub>   | Program Check execution time                  | _    | —    | 45   | μs   | 1     |

| t <sub>rdrsrc</sub>   | Read Resource execution time                  | _    | —    | 30   | μs   | 1     |

| t <sub>pgm4</sub>     | Program Longword execution time               | _    | 65   | 145  | μs   |       |

| t <sub>ersscr</sub>   | Erase Flash Sector execution time             | _    | 14   | 114  | ms   | 2     |

| t <sub>rd1all</sub>   | Read 1s All Blocks execution time             | _    | _    | 1.8  | ms   | 1     |

| t <sub>rdonce</sub>   | Read Once execution time                      | _    | —    | 30   | μs   | 1     |

| t <sub>pgmonce</sub>  | Program Once execution time                   | _    | 100  | —    | μs   |       |

| t <sub>ersall</sub>   | Erase All Blocks execution time               | _    | 175  | 1300 | ms   | 2     |

| t <sub>vfykey</sub>   | Verify Backdoor Access Key execution time     | _    | —    | 30   | μs   | 1     |

1. Assumes 25 MHz flash clock frequency.

2. Maximum times for erase parameters based on expectations at cycling end-of-life.

## 3.4.1.3 Flash high voltage current behaviors Table 21. Flash high voltage current behaviors

| Symbol              | Description                                                           | Min. | Тур. | Max. | Unit |

|---------------------|-----------------------------------------------------------------------|------|------|------|------|

| I <sub>DD_PGM</sub> | Average current adder during high voltage flash programming operation |      | 2.5  | 6.0  | mA   |

| I <sub>DD_ERS</sub> | Average current adder during high voltage flash erase operation       |      | 1.5  | 4.0  | mA   |

#### 3.4.1.4 Reliability specifications Table 22. NVM reliability specifications

| Symbol | Description   | Min. | Typ. <sup>1</sup> | Max. | Unit | Notes |  |  |

|--------|---------------|------|-------------------|------|------|-------|--|--|

|        | Program Flash |      |                   |      |      |       |  |  |

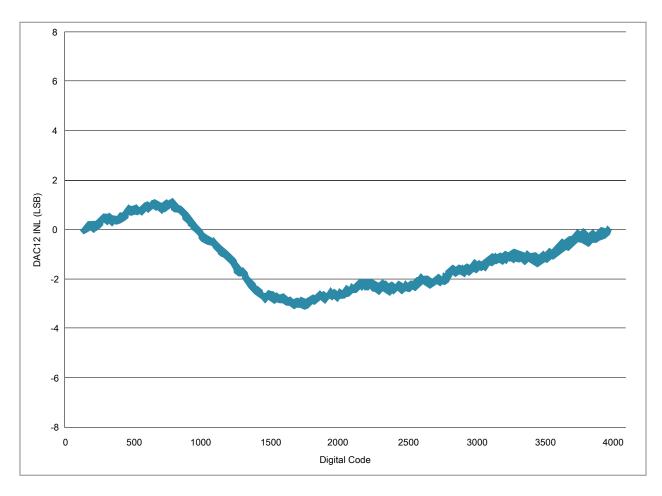

Figure 17. Typical INL error vs. digital code

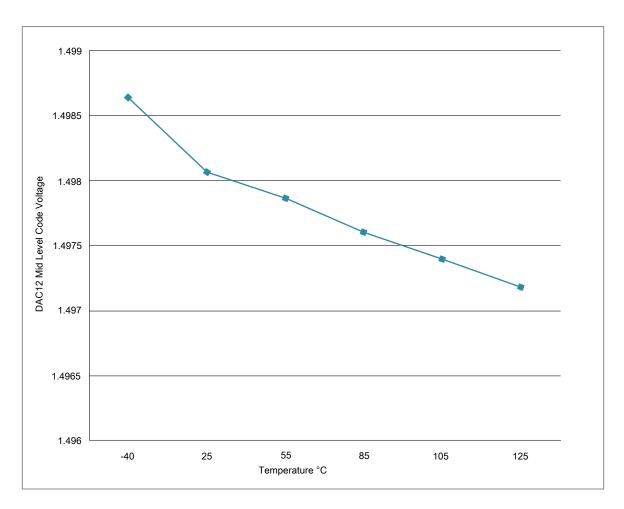

Figure 18. Offset at half scale vs. temperature

# 3.6.4 Voltage reference electrical specifications

| Table 29. | VREF full-range | operating | requirements |

|-----------|-----------------|-----------|--------------|

|-----------|-----------------|-----------|--------------|

| Symbol           | Description             | Min.                                      | Max. | Unit | Notes |

|------------------|-------------------------|-------------------------------------------|------|------|-------|

| V <sub>DDA</sub> | Supply voltage          | 1.71                                      | 3.6  | V    |       |

| T <sub>A</sub>   | Temperature             | Operating temperature range of the device |      | °C   |       |

| CL               | Output load capacitance | 100                                       |      | nF   | 1, 2  |

1. C<sub>L</sub> must be connected to VREF\_OUT if the VREF\_OUT functionality is being used for either an internal or external reference.

The load capacitance should not exceed +/-25% of the nominal specified C<sub>L</sub> value over the operating temperature range of the device.

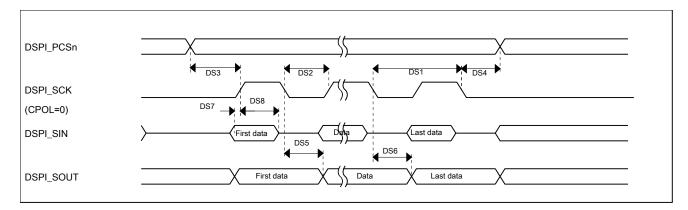

# 3.8.2 DSPI switching specifications (full voltage range)

The Deserial Serial Peripheral Interface (DSPI) provides a synchronous serial bus with master and slave operations. Many of the transfer attributes are programmable. The tables below provides DSPI timing characteristics for classic SPI timing modes. Refer to the SPI chapter of the Reference Manual for information on the modified transfer formats used for communicating with slower peripheral devices.

| Num | Description                         | Min.                          | Max.                     | Unit | Notes |

|-----|-------------------------------------|-------------------------------|--------------------------|------|-------|

|     | Operating voltage                   | 1.71                          | 3.6                      | V    | 1     |

|     | Frequency of operation              | —                             | 15                       | MHz  |       |

| DS1 | DSPI_SCK output cycle time          | 4 x t <sub>BUS</sub>          | _                        | ns   |       |

| DS2 | DSPI_SCK output high/low time       | (t <sub>SCK</sub> /2) - 4     | (t <sub>SCK/2)</sub> + 4 | ns   |       |

| DS3 | DSPI_PCSn valid to DSPI_SCK delay   | (t <sub>BUS</sub> x 2) –<br>4 | _                        | ns   | 2     |

| DS4 | DSPI_SCK to DSPI_PCSn invalid delay | (t <sub>BUS</sub> x 2) –<br>4 | _                        | ns   | 3     |

| DS5 | DSPI_SCK to DSPI_SOUT valid         | —                             | 10                       | ns   |       |

| DS6 | DSPI_SCK to DSPI_SOUT invalid       | -4.5                          | —                        | ns   |       |

| DS7 | DSPI_SIN to DSPI_SCK input setup    | 24.6                          | —                        | ns   |       |

| DS8 | DSPI_SCK to DSPI_SIN input hold     | 0                             | —                        | ns   |       |

1. The DSPI module can operate across the entire operating voltage for the processor, but to run across the full voltage range the maximum frequency of operation is reduced.

- 2. The delay is programmable in SPIx\_CTARn[PSSCK] and SPIx\_CTARn[CSSCK].

- 3. The delay is programmable in SPIx\_CTARn[PASC] and SPIx\_CTARn[ASC].

## Figure 21. DSPI classic SPI timing — master mode

| 100<br>LQFP | 64<br>LQFP | Pin Name                                         | Default                                          | ALT0                                             | ALT1                | ALT2            | ALT3     | ALT4      | ALT5            | ALT6          | ALT7                       | EzPort   |

|-------------|------------|--------------------------------------------------|--------------------------------------------------|--------------------------------------------------|---------------------|-----------------|----------|-----------|-----------------|---------------|----------------------------|----------|

| 17          | -          | ADC1_DM1/<br>ADC0_DM2                            | ADC1_DM1/<br>ADC0_DM2                            | ADC1_DM1/<br>ADC0_DM2                            |                     |                 |          |           |                 |               |                            |          |

| 18          | 9          | ADC0_DP0/<br>ADC1_DP3                            | ADC0_DP0/<br>ADC1_DP3                            | ADC0_DP0/<br>ADC1_DP3                            |                     |                 |          |           |                 |               |                            |          |

| 19          | 10         | ADC0_DM0/<br>ADC1_DM3                            | ADC0_DM0/<br>ADC1_DM3                            | ADC0_DM0/<br>ADC1_DM3                            |                     |                 |          |           |                 |               |                            |          |

| 20          | 11         | ADC1_DP0/<br>ADC0_DP3                            | ADC1_DP0/<br>ADC0_DP3                            | ADC1_DP0/<br>ADC0_DP3                            |                     |                 |          |           |                 |               |                            |          |

| 21          | 12         | ADC1_DM0/<br>ADC0_DM3                            | ADC1_DM0/<br>ADC0_DM3                            | ADC1_DM0/<br>ADC0_DM3                            |                     |                 |          |           |                 |               |                            |          |

| 22          | 13         | VDDA                                             | VDDA                                             | VDDA                                             |                     |                 |          |           |                 |               |                            |          |

| 23          | 14         | VREFH                                            | VREFH                                            | VREFH                                            |                     |                 |          |           |                 |               |                            |          |

| 24          | 15         | VREFL                                            | VREFL                                            | VREFL                                            |                     |                 |          |           |                 |               |                            |          |

| 25          | 16         | VSSA                                             | VSSA                                             | VSSA                                             |                     |                 |          |           |                 |               |                            |          |

| 26          | 17         | VREF_OUT/<br>CMP1_IN5/<br>CMP0_IN5/<br>ADC1_SE18 | VREF_OUT/<br>CMP1_IN5/<br>CMP0_IN5/<br>ADC1_SE18 | VREF_OUT/<br>CMP1_IN5/<br>CMP0_IN5/<br>ADC1_SE18 |                     |                 |          |           |                 |               |                            |          |

| 27          | 18         | DAC0_OUT/<br>CMP1_IN3/<br>ADC0_SE23              | DAC0_OUT/<br>CMP1_IN3/<br>ADC0_SE23              | DAC0_OUT/<br>CMP1_IN3/<br>ADC0_SE23              |                     |                 |          |           |                 |               |                            |          |

| 28          | 19         | CMP0_IN4/<br>ADC1_SE23                           | CMP0_IN4/<br>ADC1_SE23                           | CMP0_IN4/<br>ADC1_SE23                           |                     |                 |          |           |                 |               |                            |          |

| 29          | -          | VSS                                              | VSS                                              | VSS                                              |                     |                 |          |           |                 |               |                            |          |

| 30          | -          | VDD                                              | VDD                                              | VDD                                              |                     |                 |          |           |                 |               |                            |          |

| 31          | 20         | PTE24                                            | ADC0_SE17                                        | ADC0_SE17                                        | PTE24               |                 | FTM0_CH0 |           | I2C0_SCL        | EWM_OUT_<br>b |                            |          |

| 32          | 21         | PTE25                                            | ADC0_SE18                                        | ADC0_SE18                                        | PTE25               |                 | FTM0_CH1 |           | I2C0_SDA        | EWM_IN        |                            |          |

| 33          | -          | PTE26/<br>CLKOUT32K                              | DISABLED                                         |                                                  | PTE26/<br>CLKOUT32K |                 |          |           |                 |               |                            |          |

| 34          | 22         | PTA0                                             | JTAG_TCLK/<br>SWD_CLK/<br>EZP_CLK                |                                                  | PTA0                | UARTO_<br>CTS_b | FTM0_CH5 |           | EWM_IN          |               | JTAG_TCLK/<br>SWD_CLK      | EZP_CLK  |

| 35          | 23         | PTA1                                             | JTAG_TDI/<br>EZP_DI                              |                                                  | PTA1                | UART0_RX        | FTM0_CH6 | CMP0_OUT  | FTM2_QD_<br>PHA | FTM1_CH1      | JTAG_TDI                   | EZP_DI   |

| 36          | 24         | PTA2                                             | JTAG_TDO/<br>TRACE_<br>SWO/<br>EZP_DO            |                                                  | PTA2                | UART0_TX        | FTM0_CH7 | CMP1_OUT  | FTM2_QD_<br>PHB | FTM1_CH0      | JTAG_TDO/<br>TRACE_<br>SWO | EZP_DO   |

| 37          | 25         | PTA3                                             | JTAG_TMS/<br>SWD_DIO                             |                                                  | PTA3                | UART0_<br>RTS_b | FTM0_CH0 | FTM2_FLT0 | EWM_OUT_<br>b   |               | JTAG_TMS/<br>SWD_DIO       |          |

| 38          | 26         | PTA4/<br>LLWU_P3                                 | NMI_b/<br>EZP_CS_b                               |                                                  | PTA4/<br>LLWU_P3    |                 | FTM0_CH1 |           | FTM0_FLT3       |               | NMI_b                      | EZP_CS_b |

| 39          | 27         | PTA5                                             | DISABLED                                         |                                                  | PTA5                |                 | FTM0_CH2 |           |                 |               | JTAG_<br>TRST_b            |          |

| 40          | _          | VDD                                              | VDD                                              | VDD                                              |                     |                 |          |           |                 |               |                            |          |

| 100<br>LQFP | 64<br>LQFP | Pin Name          | Default   | ALT0      | ALT1              | ALT2      | ALT3            | ALT4     | ALT5 | ALT6          | ALT7      | EzPort |

|-------------|------------|-------------------|-----------|-----------|-------------------|-----------|-----------------|----------|------|---------------|-----------|--------|

| 97          | 61         | PTD4/<br>LLWU_P14 | DISABLED  |           | PTD4/<br>LLWU_P14 | SPI0_PCS1 | UART0_<br>RTS_b | FTM0_CH4 |      | EWM_IN        | SPI1_PCS0 |        |

| 98          | 62         | PTD5              | ADC0_SE6b | ADC0_SE6b | PTD5              | SPI0_PCS2 | UART0_<br>CTS_b | FTM0_CH5 |      | EWM_OUT_<br>b | SPI1_SCK  |        |

| 99          | 63         | PTD6/<br>LLWU_P15 | ADC0_SE7b | ADC0_SE7b | PTD6/<br>LLWU_P15 | SPI0_PCS3 | UART0_RX        | FTM0_CH6 |      | FTM0_FLT0     | SPI1_SOUT |        |

| 100         | 64         | PTD7              | DISABLED  |           | PTD7              |           | UART0_TX        | FTM0_CH7 |      | FTM0_FLT1     | SPI1_SIN  |        |

# 5.2 Recommended connection for unused analog and digital pins

The following table shows the recommended connections for analog interface pins if those analog interfaces are not used in the customer's application.

| Pin Type        |                | Short recommendation                     | Detailed recommendation                      |

|-----------------|----------------|------------------------------------------|----------------------------------------------|

| Analog/non GPIO | PGAx/ADCx      | Float                                    | Analog input - Float                         |

| Analog/non GPIO | ADCx/CMPx      | Float                                    | Analog input - Float                         |

| Analog/non GPIO | VREF_OUT       | Float                                    | Analog output - Float                        |

| Analog/non GPIO | DACx_OUT       | Float                                    | Analog output - Float                        |

| Analog/non GPIO | RTC_WAKEUP_B   | Float                                    | Analog output - Float                        |

| Analog/non GPIO | XTAL32         | Float                                    | Analog output - Float                        |

| Analog/non GPIO | EXTAL32        | Float                                    | Analog input - Float                         |

| GPIO/Analog     | PTA18/EXTAL0   | Float                                    | Analog input - Float                         |

| GPIO/Analog     | PTA19/XTAL0    | Float                                    | Analog output - Float                        |

| GPIO/Analog     | PTx/ADCx       | Float                                    | Float (default is analog input)              |

| GPIO/Analog     | PTx/CMPx       | Float                                    | Float (default is analog input)              |

| GPIO/Digital    | PTA0/JTAG_TCLK | Float                                    | Float (default is JTAG with pulldown)        |

| GPIO/Digital    | PTA1/JTAG_TDI  | Float                                    | Float (default is JTAG with pullup)          |

| GPIO/Digital    | PTA2/JTAG_TDO  | Float                                    | Float (default is JTAG with pullup)          |

| GPIO/Digital    | PTA3/JTAG_TMS  | Float                                    | Float (default is JTAG with pullup)          |

| GPIO/Digital    | PTA4/NMI_b     | 10k $\Omega$ pullup or disable and float | Pull high or disable in PCR & FOPT and float |

| GPIO/Digital    | PTx            | Float                                    | Float (default is disabled)                  |

| VDDA            | VDDA           | Always connect to VDD potential          | Always connect to VDD potential              |

Table 39.

Recommended connection for unused analog interfaces

## 6.4 Example

This is an example part number:

MKV31F256VLL12P

# 7 Terminology and guidelines

# 7.1 Definitions

Key terms are defined in the following table:

| Term                  | Definition                                                                                                                                                                                                                          |  |  |  |  |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Rating                | A minimum or maximum value of a technical characteristic that, if exceeded, may cause permanent chip failure:                                                                                                                       |  |  |  |  |

|                       | <ul> <li>Operating ratings apply during operation of the chip.</li> <li>Handling ratings apply when the chip is not powered.</li> </ul>                                                                                             |  |  |  |  |

|                       | <b>NOTE:</b> The likelihood of permanent chip failure increases rapidly as soon as a characteristic begins to exceed one of its operating ratings.                                                                                  |  |  |  |  |

| Operating requirement | A specified value or range of values for a technical characteristic that you must guarantee durin operation to avoid incorrect operation and possibly decreasing the useful life of the chip                                        |  |  |  |  |

| Operating behavior    | A specified value or range of values for a technical characteristic that are guaranteed during operation if you meet the operating requirements and any other specified conditions                                                  |  |  |  |  |

| Typical value         | A specified value for a technical characteristic that:                                                                                                                                                                              |  |  |  |  |

|                       | <ul> <li>Lies within the range of values specified by the operating behavior</li> <li>Is representative of that characteristic during operation when you meet the typical-value conditions or other specified conditions</li> </ul> |  |  |  |  |

|                       | <b>NOTE:</b> Typical values are provided as design guidelines and are neither tested nor guaranteed.                                                                                                                                |  |  |  |  |

# 7.2 Examples

## Operating rating:

| Symbol          | Description                  | Min. | Max. | Unit |

|-----------------|------------------------------|------|------|------|

| V <sub>DD</sub> | 1.0 V core supply<br>voltage | -0.3 | 1.2  | V    |

|                 |                              |      |      |      |

## Operating requirement:

| Operating require | ment:                        |      |      |      |

|-------------------|------------------------------|------|------|------|

| Symbol            | Description                  | Min. | Max. | Unit |

| V <sub>DD</sub>   | 1.0 V core supply<br>voltage | 0.9  | 1.1  | V    |

|                   |                              |      |      |      |

## Operating behavior that includes a typical value:

| Symbol          | Description                                    | Min.  | Тур. | Max. | Unit |

|-----------------|------------------------------------------------|-------|------|------|------|

| I <sub>WP</sub> | Digital I/O weak<br>pullup/pulldown<br>current | 10 AM | 70   | 130  | μA   |

#### **Typical-value conditions** 7.3

Typical values assume you meet the following conditions (or other conditions as specified):

| Symbol          | Description         | Value | Unit |

|-----------------|---------------------|-------|------|

| T <sub>A</sub>  | Ambient temperature | 25    | C°   |

| V <sub>DD</sub> | Supply voltage      | 3.3   | V    |