# E·XFL

#### NXP USA Inc. - MKV31F256VLL12 Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                        |

| Core Size                  | 32-Bit Single-Core                                                     |

| Speed                      | 120MHz                                                                 |

| Connectivity               | I²C, SPI, UART/USART                                                   |

| Peripherals                | DMA, PWM, WDT                                                          |

| Number of I/O              | 70                                                                     |

| Program Memory Size        | 256KB (256K x 8)                                                       |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 48K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                           |

| Data Converters            | A/D 2x16b; D/A 1x12b                                                   |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 100-LQFP                                                               |

| Supplier Device Package    | 100-LQFP (14x14)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mkv31f256vll12 |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

• Up to 70 general-purpose I/O (GPIO)

- Implements Field Orient Control (FOC) using Back EMF to improve motor efficiency

- Utilizes SpinTAC control theory that improves overall system performance and reliability

#### **Ordering Information**

| Part Number     | Mei        | mory      | Number of GPIOs |

|-----------------|------------|-----------|-----------------|

|                 | Flash (KB) | SRAM (KB) |                 |

| MKV31F256VLL12  | 256        | 48        | 70              |

| MKV31F256VLH12  | 256        | 48        | 46              |

| MKV31F256VLH12P | 248        | 48        | 46              |

#### **Related Resources**

| Туре                                                                                                       | Description                                                                                                                     | Resource                                                               |

|------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| Selector<br>Guide                                                                                          | The Freescale Solution Advisor is a web-based tool that features interactive application wizards and a dynamic product selector | Product Selector                                                       |

| Product Brief                                                                                              | The Product Brief contains concise overview/summary information to enable quick evaluation of a device for design suitability.  | KV30FKV31FPB                                                           |

| Reference<br>Manual                                                                                        | The Reference Manual contains a comprehensive description of the structure and function (operation) of a device.                | KV31P100M120SF8RM                                                      |

| Data Sheet The Data Sheet is this document. It includes electrical characteristics and signal connections. |                                                                                                                                 | KV31P100M120SF8                                                        |

| Chip Errata                                                                                                | The chip mask set Errata provides additional or corrective information for a particular device mask set.                        | KINETIS_xN51M <sup>1</sup>                                             |

| KMS User<br>Guide                                                                                          | The KMS User Guide provides a comprehensive description of the features and functions of the Kinetis Motor Suite solution.      | Kinetis Motor Suite User's Guide (KMS100UG) <sup>2</sup>               |

| KMS API<br>Reference<br>Manual                                                                             | The KMS API reference manual provides a comprehensive description of the API of the Kinetis Motor Suite function blocks.        | Kinetis Motor Suite API<br>Reference Manual<br>(KMS100RM) <sup>2</sup> |

| Package<br>drawing                                                                                         | Package dimensions are provided by part number:<br>• MKV31F256VLL12<br>• MKV31F256VLH12<br>• MKV31F256VLH12P                    | Package drawing:<br>• 98ASS23308W<br>• 98ASS23234W<br>• 98ASS23234W    |

1. To find the associated resource, go to freescale.com and perform a search using this term with the *x* replaced by the revision of the device you are using.

2. To find the associated resource, go to freescale.com and perform a search using Document ID

Figure 1 shows the functional modules in the chip.

| Symbol                | Description                                                                | Min. | Тур. | Max.   | Unit | Notes |

|-----------------------|----------------------------------------------------------------------------|------|------|--------|------|-------|

|                       | @ 1.8V                                                                     | _    |      |        | mA   | 11    |

|                       | @ 3.0V                                                                     | _    | 0.61 | 0.79   | mA   |       |

| I <sub>DD_VLPR</sub>  | Very-low-power run mode current at 3.0 V — all peripheral clocks disabled  | _    | 0.68 | 0.87   | mA   | 12    |

| I <sub>DD_VLPR</sub>  | Very-low-power run mode current at 3.0 V — all peripheral clocks enabled   | _    | 1.10 | 1.28   | mA   | 13    |

| I <sub>DD_VLPW</sub>  | Very-low-power wait mode current at 3.0 V — all peripheral clocks disabled | _    | 0.38 | 0.57   | mA   | 14    |

| I <sub>DD_STOP</sub>  | Stop mode current at 3.0 V                                                 |      |      |        |      |       |

|                       | @ -40°C to 25°C                                                            | _    | 0.27 | 0.35   | mA   |       |

|                       | @ 70°C                                                                     | _    | 0.32 | 0.47   | mA   |       |

|                       | @ 85°C                                                                     | _    | 0.32 | 0.51   | mA   |       |

|                       | @ 105°C                                                                    | _    | 0.45 | 0.77   | mA   |       |

| I <sub>DD_VLPS</sub>  | Very-low-power stop mode current at 3.0 V                                  |      |      |        |      |       |

|                       | @ -40°C to 25°C                                                            | _    | 4.5  | 12.00  | μA   |       |

|                       | @ 70°C                                                                     | _    | 16.8 | 42.40  | μA   |       |

|                       | @ 85°C                                                                     | _    | 28.9 | 73.45  | μA   |       |

|                       | @ 105°C                                                                    | _    | 60.8 | 141.90 | μA   |       |

| I <sub>DD_LLS3</sub>  | Low leakage stop mode 3 current at 3.0 V                                   |      |      |        |      |       |

|                       | @ -40°C to 25°C                                                            | _    | 2.6  | 3.75   | μA   |       |

|                       | @ 70°C                                                                     | _    | 6.6  | 12.00  | μA   |       |

|                       | @ 85°C                                                                     | _    | 10.5 | 17.25  | μA   |       |

|                       | @ 105°C                                                                    | _    | 21.0 | 40.70  | μA   |       |

| I <sub>DD_LLS2</sub>  | Low leakage stop mode 2 current at 3.0 V                                   |      |      |        |      |       |

|                       | @ -40°C to 25°C                                                            | _    | 2.4  | 3.40   | μA   |       |

|                       | @ 70°C                                                                     | _    | 5.3  | 8.90   | μA   |       |

|                       | @ 85°C                                                                     | _    | 5.1  | 10.05  | μA   |       |

|                       | @ 105°C                                                                    | _    | 15.9 | 28.85  | μA   |       |

| I <sub>DD_VLLS3</sub> | Very low-leakage stop mode 3 current at 3.0 V                              |      |      |        |      |       |

| 00_12200              | @ -40°C to 25°C                                                            | _    | 1.9  | 2.30   | μA   |       |

|                       | @ 70°C                                                                     | _    | 4.8  | 8.10   | μΑ   |       |

|                       | @ 85°C                                                                     | _    | 7.6  | 11.30  | μΑ   |       |

|                       | @ 105°C                                                                    | _    | 15.3 | 27.65  | μΑ   |       |

| IDD_VLLS2             | Very low-leakage stop mode 2 current at 3.0 V                              |      |      |        | •    |       |

| 20_1002               | @ -40°C to 25°C                                                            | _    | 1.7  | 2.10   | μA   |       |

|                       | @ 70°C                                                                     | _    | 3.4  | 4.85   | μΑ   |       |

|                       | @ 85°C                                                                     | _    | 5.1  | 8.80   | μΑ   |       |

|                       | @ 105°C                                                                    | _    | 9.8  | 15.70  | μA   |       |

| I <sub>DD_VLLS1</sub> | Very low-leakage stop mode 1 current at 3.0 V                              |      |      | -      | 1    |       |

|                       | @ -40°C to 25°C                                                            |      | 0.71 | 0.96   | μA   |       |

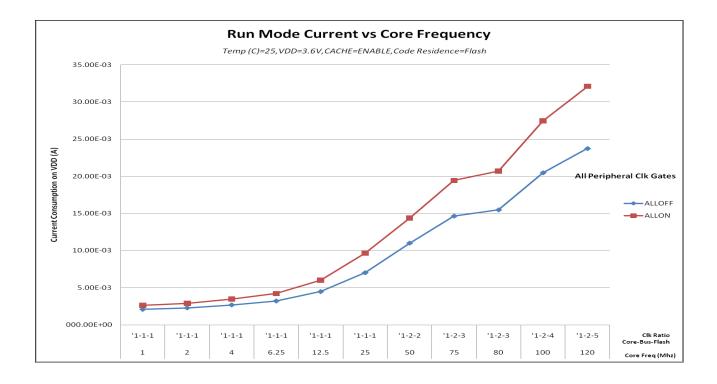

### 2.2.5.1 Diagram: Typical IDD\_RUN operating behavior

The following data was measured under these conditions:

- MCG in FBE mode for 50 MHz and lower frequencies. MCG in FEE mode at frequencies between 50 MHz and 100MHz. MCG in PEE mode at frequencies greater than 100 MHz.

- No GPIOs toggled

- Code execution from flash with cache enabled

- For the ALLOFF curve, all peripheral clocks are disabled except FTFA

Figure 3. Run mode supply current vs. core frequency

## 2.4 Thermal specifications

## 2.4.1 Thermal operating requirements

#### Table 11. Thermal operating requirements

| Syı | Symbol Description |                          | Min. | Max. | Unit | Notes |

|-----|--------------------|--------------------------|------|------|------|-------|

| -   | TJ                 | Die junction temperature | -40  | 125  | °C   |       |

| ٦   | T <sub>A</sub>     | Ambient temperature      | -40  | 105  | °C   | 1     |

1. Maximum  $T_A$  can be exceeded only if the user ensures that  $T_J$  does not exceed maximum  $T_J$ . The simplest method to determine  $T_J$  is:  $T_J = T_A + R_{\Theta JA} \times chip$  power dissipation.

### 2.4.2 Thermal attributes

| Board type           | Symbol            | Description                                                                     | 100 LQFP | 64 LQFP | Unit | Notes |

|----------------------|-------------------|---------------------------------------------------------------------------------|----------|---------|------|-------|

| Single-layer<br>(1s) | R <sub>0JA</sub>  | Thermal<br>resistance,<br>junction to<br>ambient<br>(natural<br>convection)     | 61       | 67      | °C/W | 1     |

| Four-layer<br>(2s2p) | R <sub>0JA</sub>  | Thermal<br>resistance,<br>junction to<br>ambient<br>(natural<br>convection)     | 48       | 48      | °C/W | 2     |

| Single-layer<br>(1s) | R <sub>eJMA</sub> | Thermal<br>resistance,<br>junction to<br>ambient (200<br>ft./min. air<br>speed) | 51       | 55      | °C/W | 3     |

| Four-layer<br>(2s2p) | R <sub>eJMA</sub> | Thermal<br>resistance,<br>junction to<br>ambient (200<br>ft./min. air<br>speed) | 42       | 42      | °C/W | 3     |

|                      | R <sub>θJB</sub>  | Thermal<br>resistance,<br>junction to<br>board                                  | 34       | 31      | °C/W | 4     |

|                      | R <sub>θJC</sub>  | Thermal<br>resistance,<br>junction to case                                      | 16       | 16      | °C/W | 5     |

#### Peripheral operating requirements and behaviors

| Board type | Symbol          | Description                                                                                                           | 100 LQFP | 64 LQFP | Unit | Notes |

|------------|-----------------|-----------------------------------------------------------------------------------------------------------------------|----------|---------|------|-------|

|            | Ψ <sub>JT</sub> | Thermal<br>characterizatio<br>n parameter,<br>junction to<br>package top<br>outside center<br>(natural<br>convection) | 3        | 3       | °C/W | 6     |

- 1. Determined according to JEDEC Standard JESD51-2, *Integrated Circuits Thermal Test Method Environmental Conditions—Natural Convection (Still Air)* with the single layer board horizontal. Board meets JESD51-9 specification.

- 2. Determined according to JEDEC Standard JESD51-2, Integrated Circuits Thermal Test Method Environmental Conditions—Natural Convection (Still Air).

- 3. Determined according to JEDEC Standard JESD51-6, Integrated Circuits Thermal Test Method Environmental Conditions—Forced Convection (Moving Air) with the board horizontal.

- 4. Determined according to JEDEC Standard JESD51-8, Integrated Circuit Thermal Test Method Environmental Conditions—Junction-to-Board.

- 5. Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1).

- 6. Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2.

## **3** Peripheral operating requirements and behaviors

## 3.1 Core modules

### 3.1.1 SWD electricals

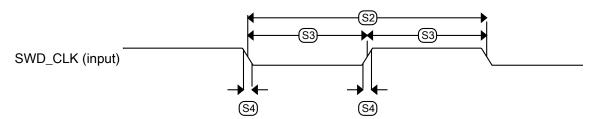

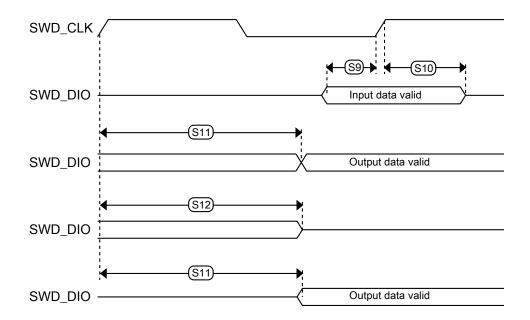

Table 12. SWD full voltage range electricals

| Symbol | Description                                     | Min. | Max. | Unit |

|--------|-------------------------------------------------|------|------|------|

|        | Operating voltage                               | 1.71 | 3.6  | V    |

| S1     | SWD_CLK frequency of operation                  |      |      |      |

|        | Serial wire debug                               | 0    | 33   | MHz  |

| S2     | SWD_CLK cycle period                            | 1/S1 |      | ns   |

| S3     | SWD_CLK clock pulse width                       |      |      |      |

|        | Serial wire debug                               | 15   | —    | ns   |

| S4     | SWD_CLK rise and fall times                     | —    | 3    | ns   |

| S9     | SWD_DIO input data setup time to SWD_CLK rise   | 8    | _    | ns   |

| S10    | SWD_DIO input data hold time after SWD_CLK rise | 1.4  | _    | ns   |

| S11    | SWD_CLK high to SWD_DIO data valid              | —    | 25   | ns   |

| S12    | SWD_CLK high to SWD_DIO high-Z                  | 5    |      | ns   |

20

Figure 5. Serial wire clock input timing

### 3.1.2 JTAG electricals

#### Table 13. JTAG limited voltage range electricals

| Symbol | Description                 | Min. | Max. | Unit |

|--------|-----------------------------|------|------|------|

|        | Operating voltage           | 2.7  | 3.6  | V    |

| J1     | TCLK frequency of operation |      |      | MHz  |

|        | Boundary Scan               | 0    | 10   |      |

|        | JTAG and CJTAG              | 0    | 20   |      |

| J2     | TCLK cycle period           | 1/J1 | _    | ns   |

| J3     | TCLK clock pulse width      |      |      |      |

|        |                             | 50   | _    | ns   |

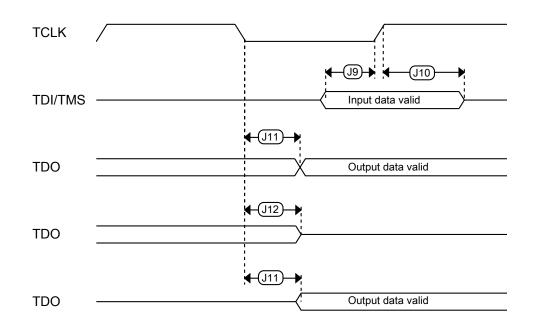

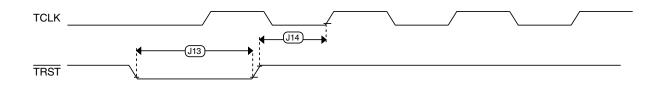

Figure 9. Test Access Port timing

## 3.2 System modules

There are no specifications necessary for the device's system modules.

## 3.3 Clock modules

## 3.3.1 MCG specifications

| Symbol                  | Description                                                                                                                                |                                                                  | Min.                            | Тур.      | Max.    | Unit                  | Notes |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|---------------------------------|-----------|---------|-----------------------|-------|

| f <sub>ints_ft</sub>    |                                                                                                                                            | frequency (slow clock) —<br>t nominal VDD and 25 °C              |                                 | 32.768    | —       | kHz                   |       |

| $\Delta f_{ints_t}$     |                                                                                                                                            | internal reference frequency voltage and temperature             | —                               | +0.5/-0.7 | ± 2     | %                     |       |

| $f_{ints\_t}$           | Internal reference<br>user trimmed                                                                                                         | frequency (slow clock) —                                         | 31.25                           | —         | 39.0625 | kHz                   |       |

| $\Delta_{fdco\_res\_t}$ |                                                                                                                                            | med average DCO output<br>voltage and temperature —<br>d SCFTRIM | _                               | ± 0.3     | ± 0.6   | %f <sub>dco</sub>     | 1     |

| $\Delta f_{dco_t}$      |                                                                                                                                            | trimmed average DCO output<br>Itage and temperature              | —                               | +0.5/-0.7 | ± 2     | %f <sub>dco</sub>     | 1, 2  |

| $\Delta f_{dco_t}$      |                                                                                                                                            | trimmed average DCO output<br>ed voltage and temperature         | _                               | ± 0.3     | ± 1.5   | %f <sub>dco</sub>     | 1     |

| f <sub>intf_ft</sub>    | Internal reference frequency (fast clock) — factory trimmed at nominal VDD and 25°C                                                        |                                                                  | _                               | 4         | —       | MHz                   |       |

| ∆f <sub>intf_ft</sub>   | Frequency deviation of internal reference clock<br>(fast clock) over temperature and voltage —<br>factory trimmed at nominal VDD and 25 °C |                                                                  | _                               | +1/-2     | ± 5     | %f <sub>intf_ft</sub> |       |

| f <sub>intf_t</sub>     | Internal reference frequency (fast clock) — user trimmed at nominal VDD and 25 °C                                                          |                                                                  | 3                               | —         | 5       | MHz                   |       |

| f <sub>loc_low</sub>    | Loss of external clock minimum frequency — RANGE = 00                                                                                      |                                                                  | (3/5) x<br>f <sub>ints_t</sub>  | —         | —       | kHz                   |       |

| f <sub>loc_high</sub>   | Loss of external c<br>RANGE = 01, 10,                                                                                                      | lock minimum frequency —<br>or 11                                | (16/5) x<br>f <sub>ints_t</sub> | —         | —       | kHz                   |       |

|                         |                                                                                                                                            | FL                                                               | L                               |           |         |                       |       |

| f <sub>fll_ref</sub>    | FLL reference free                                                                                                                         | quency range                                                     | 31.25                           | —         | 39.0625 | kHz                   |       |

| f <sub>dco</sub>        | DCO output<br>frequency range                                                                                                              | Low range (DRS=00)<br>640 × f <sub>fll_ref</sub>                 | 20                              | 20.97     | 25      | MHz                   | 3, 4  |

|                         |                                                                                                                                            | Mid range (DRS=01)<br>1280 × f <sub>fll_ref</sub>                | 40                              | 41.94     | 50      | MHz                   |       |

|                         |                                                                                                                                            | Mid-high range (DRS=10)<br>1920 × f <sub>fll_ref</sub>           | 60                              | 62.91     | 75      | MHz                   |       |

|                         |                                                                                                                                            | High range (DRS=11)<br>2560 × $f_{fil}$ ref                      | 80                              | 83.89     | 100     | MHz                   |       |

| dco_t_DMX3<br>2         | DCO output Low range (DRS=00) — 23.99 — frequency 732 × f <sub>fll_ref</sub>                                                               | MHz                                                              | 5, 6                            |           |         |                       |       |

|                         |                                                                                                                                            | Mid range (DRS=01)<br>1464 × f <sub>fll_ref</sub>                |                                 | 47.97     |         | MHz                   |       |

|                         | 1                                                                                                                                          |                                                                  |                                 | 1         |         |                       |       |

### Table 15. MCG specifications

| Symbol                   | Description                     |                                                                   | Min.   | Тур.  | Max.                                | Unit | Notes |

|--------------------------|---------------------------------|-------------------------------------------------------------------|--------|-------|-------------------------------------|------|-------|

|                          |                                 | $2197 \times f_{fll_{ref}}$                                       |        |       |                                     |      |       |

|                          |                                 | High range (DRS=11)                                               | —      | 95.98 | —                                   | MHz  |       |

|                          |                                 | $2929 \times f_{fll\_ref}$                                        |        |       |                                     |      |       |

| J <sub>cyc_fll</sub>     | FLL period jitter               | 1                                                                 | _      |       | _                                   | ps   |       |

|                          | • f <sub>VCO</sub> = 48 N       |                                                                   | _      | 180   |                                     |      |       |

|                          | • f <sub>VCO</sub> = 98 M       | 1Hz                                                               |        | 150   |                                     |      |       |

| t <sub>fll_acquire</sub> | FLL target freque               | ncy acquisition time                                              | —      |       | 1                                   | ms   | 7     |

|                          |                                 | Р                                                                 | ĹĹ     |       |                                     |      |       |

| f <sub>vco</sub>         | VCO operating fre               | CO operating frequency                                            |        | _     | 120                                 | MHz  |       |

| I <sub>pll</sub>         | PLL operating cur<br>PLL @ 96 N | rrent<br>MHz (f <sub>osc hi 1</sub> = 8 MHz, f <sub>oll ref</sub> | _      | 1060  | _                                   | μA   | 8     |

|                          |                                 | DIV multiplier = 48)                                              |        |       |                                     |      |       |

| I <sub>pll</sub>         | PLL operating cu                | rrent<br>MHz (f <sub>osc_hi_1</sub> = 8 MHz, f <sub>pll_ref</sub> | _      | 600   | _                                   | μA   | 8     |

|                          |                                 | DIV multiplier = 24)                                              |        |       |                                     |      |       |

| f <sub>pll_ref</sub>     | PLL reference fre               | quency range                                                      | 2.0    |       | 4.0                                 | MHz  |       |

| J <sub>cyc_pll</sub>     | PLL period jitter (             | RMS)                                                              | _      | 120   | _                                   | ps   | 9     |

|                          | • f <sub>vco</sub> = 48 MI      | Hz                                                                | _      | 75    | _                                   | ps   |       |

|                          | • f <sub>vco</sub> = 100 N      | 1Hz                                                               |        |       |                                     | F -  |       |

| J <sub>acc_pll</sub>     | PLL accumulated                 | jitter over 1µs (RMS)                                             | _      | 1350  | _                                   | ps   | 9     |

|                          | • f <sub>vco</sub> = 48 MI      | Hz                                                                | _      | 600   |                                     | ps   |       |

|                          | • f <sub>vco</sub> = 100 N      | 1Hz                                                               |        |       |                                     | F -  |       |

| D <sub>lock</sub>        | Lock entry freque               | ncy tolerance                                                     | ± 1.49 |       | ± 2.98                              | %    |       |

| D <sub>unl</sub>         | Lock exit frequen               | cy tolerance                                                      | ± 4.47 |       | ± 5.97                              | %    |       |

| t <sub>pll_lock</sub>    | Lock detector det               | ection time                                                       | —      |       | $150 \times 10^{-6}$                | S    | 10    |

|                          |                                 |                                                                   |        |       | + 1075(1/<br>f <sub>pll_ref</sub> ) |      |       |

| Table 15. | MCG specifications | (continued) |

|-----------|--------------------|-------------|

|-----------|--------------------|-------------|

- 1. This parameter is measured with the internal reference (slow clock) being used as a reference to the FLL (FEI clock mode).

- 2. 2.0 V <= VDD <= 3.6 V.

- 3. These typical values listed are with the slow internal reference clock (FEI) using factory trim and DMX32=0.

- The resulting system clock frequencies should not exceed their maximum specified values. The DCO frequency deviation (Δf<sub>dco\_t</sub>) over voltage and temperature should be considered.

- 5. These typical values listed are with the slow internal reference clock (FEI) using factory trim and DMX32=1.

- 6. The resulting clock frequency must not exceed the maximum specified clock frequency of the device.

- This specification applies to any time the FLL reference source or reference divider is changed, trim value is changed, DMX32 bit is changed, DRS bits are changed, or changing from FLL disabled (BLPE, BLPI) to FLL enabled (FEI, FEE, FBE, FBI). If a crystal/resonator is being used as the reference, this specification assumes it is already running.

- 8. Excludes any oscillator currents that are also consuming power while PLL is in operation.

- This specification was obtained using a Freescale developed PCB. PLL jitter is dependent on the noise characteristics of each PCB and results will vary.

- This specification applies to any time the PLL VCO divider or reference divider is changed, or changing from PLL disabled (BLPE, BLPI) to PLL enabled (PBE, PEE). If a crystal/resonator is being used as the reference, this specification assumes it is already running.

26

| Symbol                       | Description                                                                                            | Min. | Тур.            | Max. | Unit | Notes |

|------------------------------|--------------------------------------------------------------------------------------------------------|------|-----------------|------|------|-------|

|                              | • 32 kHz                                                                                               | _    | 25              | —    | μΑ   |       |

|                              | • 4 MHz                                                                                                | —    | 400             | _    | μA   |       |

|                              | • 8 MHz (RANGE=01)                                                                                     | _    | 500             | _    | μA   |       |

|                              | • 16 MHz                                                                                               | _    | 2.5             | _    | mA   |       |

|                              | • 24 MHz                                                                                               | —    | 3               | _    | mA   |       |

|                              | • 32 MHz                                                                                               | —    | 4               | _    | mA   |       |

| C <sub>x</sub>               | EXTAL load capacitance                                                                                 | _    | _               | _    |      | 2, 3  |

| Cy                           | XTAL load capacitance                                                                                  | _    | —               | _    |      | 2, 3  |

| R <sub>F</sub>               | Feedback resistor — low-frequency, low-power mode (HGO=0)                                              | _    |                 | _    | MΩ   | 2, 4  |

|                              | Feedback resistor — low-frequency, high-gain mode (HGO=1)                                              | —    | 10              | _    | ΜΩ   |       |

|                              | Feedback resistor — high-frequency, low-<br>power mode (HGO=0)                                         | —    | _               |      | MΩ   | -     |

|                              | Feedback resistor — high-frequency, high-gain mode (HGO=1)                                             | —    | 1               |      | MΩ   |       |

| R <sub>S</sub>               | Series resistor — low-frequency, low-power mode (HGO=0)                                                | —    | _               |      | kΩ   |       |

|                              | Series resistor — low-frequency, high-gain mode (HGO=1)                                                | _    | 200             |      | kΩ   |       |

|                              | Series resistor — high-frequency, low-power<br>mode (HGO=0)                                            | —    | _               | _    | kΩ   |       |

|                              | Series resistor — high-frequency, high-gain<br>mode (HGO=1)                                            |      |                 |      |      |       |

|                              |                                                                                                        | —    | 0               | _    | kΩ   |       |

| V <sub>pp</sub> <sup>5</sup> | Peak-to-peak amplitude of oscillation (oscillator<br>mode) — low-frequency, low-power mode<br>(HGO=0)  | _    | 0.6             | _    | V    |       |

|                              | Peak-to-peak amplitude of oscillation (oscillator<br>mode) — low-frequency, high-gain mode<br>(HGO=1)  | _    | V <sub>DD</sub> | _    | V    |       |

|                              | Peak-to-peak amplitude of oscillation (oscillator<br>mode) — high-frequency, low-power mode<br>(HGO=0) | _    | 0.6             | _    | V    |       |

|                              | Peak-to-peak amplitude of oscillation (oscillator<br>mode) — high-frequency, high-gain mode<br>(HGO=1) | _    | V <sub>DD</sub> | —    | V    |       |

Table 17. Oscillator DC electrical specifications (continued)

- 1.  $V_{DD}$ =3.3 V, Temperature =25 °C

- 2. See crystal or resonator manufacturer's recommendation

- 3.  $C_x$  and  $C_y$  can be provided by using either integrated capacitors or external components.

- 4. When low-power mode is selected,  $R_F$  is integrated and must not be attached externally.

- 5. The EXTAL and XTAL pins should only be connected to required oscillator components and must not be connected to any other device.

| Symbol                  | Description                            | Min. | Typ. <sup>1</sup> | Max. | Unit   | Notes |

|-------------------------|----------------------------------------|------|-------------------|------|--------|-------|

| t <sub>nvmretp10k</sub> | Data retention after up to 10 K cycles | 5    | 50                | —    | years  | —     |

| t <sub>nvmretp1k</sub>  | Data retention after up to 1 K cycles  | 20   | 100               | _    | years  | _     |

| n <sub>nvmcycp</sub>    | Cycling endurance                      | 10 K | 50 K              |      | cycles | 2     |

Table 22. NVM reliability specifications (continued)

Typical data retention values are based on measured response accelerated at high temperature and derated to a constant 25 °C use profile. Engineering Bulletin EB618 does not apply to this technology. Typical endurance defined in Engineering Bulletin EB619.

2. Cycling endurance represents number of program/erase cycles at -40 °C  $\leq$  T<sub>i</sub>  $\leq$  125 °C.

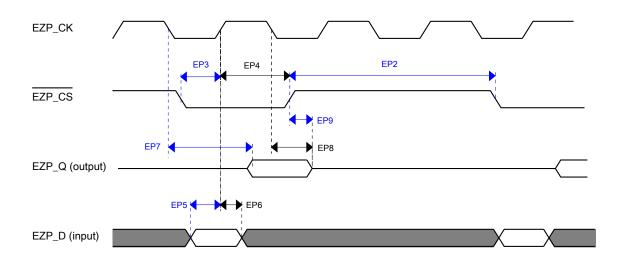

#### 3.4.2 EzPort switching specifications Table 23. EzPort switching specifications

| Num  | Description                                              | Min.                    | Max.                | Unit |

|------|----------------------------------------------------------|-------------------------|---------------------|------|

|      | Operating voltage                                        | 1.71                    | 3.6                 | V    |

| EP1  | EZP_CK frequency of operation (all commands except READ) | _                       | f <sub>SYS</sub> /2 | MHz  |

| EP1a | EZP_CK frequency of operation (READ command)             | _                       | f <sub>SYS</sub> /8 | MHz  |

| EP2  | EZP_CS negation to next EZP_CS assertion                 | 2 x t <sub>EZP_CK</sub> | _                   | ns   |

| EP3  | EZP_CS input valid to EZP_CK high (setup)                | 5                       | —                   | ns   |

| EP4  | EZP_CK high to EZP_CS input invalid (hold)               | 5                       | —                   | ns   |

| EP5  | EZP_D input valid to EZP_CK high (setup)                 | 2                       | _                   | ns   |

| EP6  | EZP_CK high to EZP_D input invalid (hold)                | 5                       | _                   | ns   |

| EP7  | EZP_CK low to EZP_Q output valid                         | —                       | 25                  | ns   |

| EP8  | EZP_CK low to EZP_Q output invalid (hold)                | 0                       | _                   | ns   |

| EP9  | EZP_CS negation to EZP_Q tri-state                       | _                       | 12                  | ns   |

Figure 11. EzPort Timing Diagram

### 3.5 Security and integrity modules

There are no specifications necessary for the device's security and integrity modules.

### 3.6 Analog

### 3.6.1 ADC electrical specifications

The 16-bit accuracy specifications listed in Table 24 and Table 25 are achievable on the differential pins ADCx\_DPx, ADCx\_DMx.

All other ADC channels meet the 13-bit differential/12-bit single-ended accuracy specifications.

|                   | Table 24. To-bit ADC operating conditions |                                                                |      |                   |      |      |       |  |  |

|-------------------|-------------------------------------------|----------------------------------------------------------------|------|-------------------|------|------|-------|--|--|

| Symbol            | Description                               | Conditions                                                     | Min. | Typ. <sup>1</sup> | Max. | Unit | Notes |  |  |

| V <sub>DDA</sub>  | Supply voltage                            | Absolute                                                       | 1.71 | _                 | 3.6  | V    |       |  |  |

| ΔV <sub>DDA</sub> | Supply voltage                            | Delta to V <sub>DD</sub> (V <sub>DD</sub> – V <sub>DDA</sub> ) | -100 | 0                 | +100 | mV   | 2     |  |  |

#### 3.6.1.1 16-bit ADC operating conditions Table 24. 16-bit ADC operating conditions

| Symbol            | Description                               | Conditions                                                       | Min.             | Typ. <sup>1</sup> | Max.             | Unit | Notes |

|-------------------|-------------------------------------------|------------------------------------------------------------------|------------------|-------------------|------------------|------|-------|

| $\Delta V_{SSA}$  | Ground voltage                            | Delta to $V_{SS}$ ( $V_{SS} - V_{SSA}$ )                         | -100             | 0                 | +100             | mV   | 2     |

| V <sub>REFH</sub> | ADC reference voltage high                |                                                                  | 1.13             | V <sub>DDA</sub>  | V <sub>DDA</sub> | V    |       |

| V <sub>REFL</sub> | ADC reference voltage low                 |                                                                  | V <sub>SSA</sub> | V <sub>SSA</sub>  | V <sub>SSA</sub> | V    |       |

| V <sub>ADIN</sub> | Input voltage                             | 16-bit differential mode                                         | VREFL            |                   | 31/32 *<br>VREFH | V    |       |

|                   |                                           | All other modes                                                  | VREFL            | _                 | VREFH            |      |       |

| C <sub>ADIN</sub> | Input                                     | 16-bit mode                                                      | _                | 8                 | 10               | pF   |       |

|                   | capacitance                               | <ul> <li>8-bit / 10-bit / 12-bit<br/>modes</li> </ul>            | _                | 4                 | 5                |      |       |

| R <sub>ADIN</sub> | Input series resistance                   |                                                                  | _                | 2                 | 5                | kΩ   |       |

| R <sub>AS</sub>   | Analog source<br>resistance<br>(external) | 13-bit / 12-bit modes<br>f <sub>ADCK</sub> < 4 MHz               | _                | _                 | 5                | kΩ   | 3     |

| f <sub>ADCK</sub> | ADC conversion<br>clock frequency         | ≤ 13-bit mode                                                    | 1.0              |                   | 24.0             | MHz  | 4     |

| f <sub>ADCK</sub> | ADC conversion<br>clock frequency         | 16-bit mode                                                      | 2.0              | _                 | 12.0             | MHz  | 4     |

| C <sub>rate</sub> | ADC conversion                            | ≤ 13-bit modes                                                   |                  |                   |                  |      | 5     |

|                   | rate                                      | No ADC hardware averaging                                        | 20               | _                 | 1200             | Ksps |       |

|                   |                                           | Continuous conversions<br>enabled, subsequent<br>conversion time |                  |                   |                  |      |       |

| C <sub>rate</sub> | ADC conversion                            | 16-bit mode                                                      |                  |                   |                  |      | 5     |

|                   | rate                                      | No ADC hardware averaging                                        | 37               | —                 | 461              | Ksps |       |

|                   |                                           | Continuous conversions<br>enabled, subsequent<br>conversion time |                  |                   |                  |      |       |

Table 24. 16-bit ADC operating conditions (continued)

- 1. Typical values assume V<sub>DDA</sub> = 3.0 V, Temp = 25 °C, f<sub>ADCK</sub> = 1.0 MHz, unless otherwise stated. Typical values are for reference only, and are not tested in production.

- 2. DC potential difference.

- 3. This resistance is external to MCU. To achieve the best results, the analog source resistance must be kept as low as possible. The results in this data sheet were derived from a system that had < 8  $\Omega$  analog source resistance. The R<sub>AS</sub>/C<sub>AS</sub> time constant should be kept to < 1 ns.

- 4. To use the maximum ADC conversion clock frequency, CFG2[ADHSC] must be set and CFG1[ADLPC] must be clear.

- 5. For guidelines and examples of conversion rate calculation, download the ADC calculator tool.

| Symbol              | Description                     | Conditions <sup>1</sup>                         | Min.   | Typ. <sup>2</sup>      | Max.            | Unit             | Notes                                                                  |

|---------------------|---------------------------------|-------------------------------------------------|--------|------------------------|-----------------|------------------|------------------------------------------------------------------------|

|                     |                                 | <ul> <li>&lt;12-bit modes</li> </ul>            | —      | ±0.5                   | -0.7 to<br>+0.5 |                  |                                                                        |

| E <sub>FS</sub>     | Full-scale error                | 12-bit modes                                    | _      | -4                     | -5.4            | LSB <sup>4</sup> | $V_{ADIN} = V_{DDA}^5$                                                 |

|                     |                                 | <ul> <li>&lt;12-bit modes</li> </ul>            | _      | -1.4                   | -1.8            |                  |                                                                        |

| EQ                  | Quantization error              | 16-bit modes                                    | _      | -1 to 0                | _               | LSB <sup>4</sup> |                                                                        |

|                     |                                 | <ul> <li>≤13-bit modes</li> </ul>               | _      | -                      | ±0.5            |                  |                                                                        |

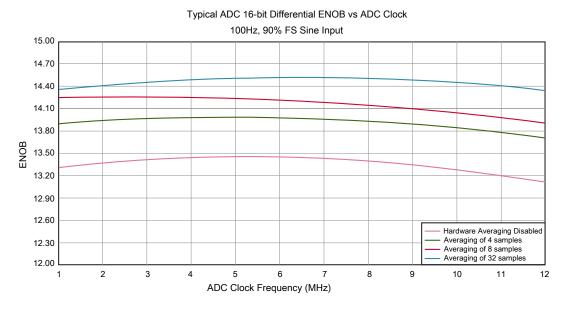

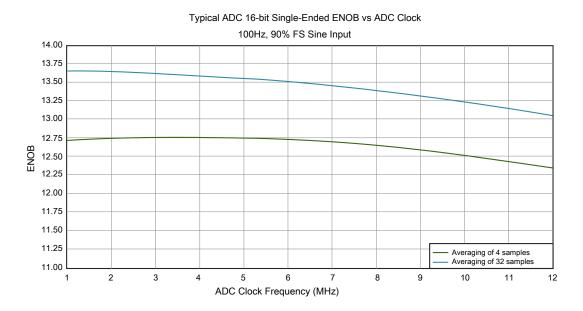

| ENOB                | Effective number of             | 16-bit differential mode                        |        |                        |                 |                  | 6                                                                      |

|                     | bits                            | • Avg = 32                                      | 12.8   | 14.5                   | _               | bits             |                                                                        |

|                     |                                 | • Avg = 4                                       | 11.9   | 13.8                   | _               | bits             |                                                                        |

|                     |                                 | 16-bit single-ended mode                        |        |                        |                 |                  |                                                                        |

|                     |                                 | • Avg = 32                                      | 12.2   | 13.9                   | _               |                  |                                                                        |

|                     |                                 | • Avg = 4                                       | 11.4   | 13.1                   |                 | bits             |                                                                        |

|                     |                                 |                                                 |        |                        |                 | bits             |                                                                        |

| SINAD               | Signal-to-noise plus distortion | See ENOB                                        | 6.02 × | 6.02 × ENOB + 1.76     |                 | dB               |                                                                        |

| THD                 | Total harmonic                  | 16-bit differential mode                        |        |                        |                 | dB               | 7                                                                      |

|                     | distortion                      | • Avg = 32                                      | _      | -94                    | —               |                  |                                                                        |

|                     |                                 | 16-bit single-ended mode                        |        |                        |                 | dB               |                                                                        |

|                     |                                 | <ul> <li>Avg = 32</li> </ul>                    | —      | -85                    | —               |                  |                                                                        |

| SFDR                | Spurious free                   | 16-bit differential mode                        |        |                        |                 | dB               | 7                                                                      |

|                     | dynamic range                   | • Avg = 32                                      | 82     | 95                     |                 |                  |                                                                        |

|                     |                                 |                                                 |        |                        |                 | dB               |                                                                        |

|                     |                                 | 16-bit single-ended mode                        | 78     | 90                     |                 |                  |                                                                        |

|                     |                                 | • Avg = 32                                      |        |                        |                 |                  |                                                                        |

| EIL                 | Input leakage error             |                                                 |        | $I_{In} \times R_{AS}$ |                 | mV               | I <sub>In</sub> = leakage<br>current                                   |

|                     |                                 |                                                 |        |                        |                 |                  | (refer to the<br>MCU's voltage<br>and current<br>operating<br>ratings) |

|                     | Temp sensor slope               | Across the full temperature range of the device | 1.55   | 1.62                   | 1.69            | mV/°C            | 8                                                                      |

| V <sub>TEMP25</sub> | Temp sensor voltage             | 25 °C                                           | 706    | 716                    | 726             | mV               | 8                                                                      |

Table 25. 16-bit ADC characteristics ( $V_{REFH} = V_{DDA}$ ,  $V_{REFL} = V_{SSA}$ ) (continued)

1. All accuracy numbers assume the ADC is calibrated with  $V_{\mathsf{REFH}}$  =  $V_{\mathsf{DDA}}$

Typical values assume V<sub>DDA</sub> = 3.0 V, Temp = 25 °C, f<sub>ADCK</sub> = 2.0 MHz unless otherwise stated. Typical values are for reference only and are not tested in production.

3. The ADC supply current depends on the ADC conversion clock speed, conversion rate and ADC\_CFG1[ADLPC] (low power). For lowest power operation, ADC\_CFG1[ADLPC] must be set, the ADC\_CFG2[ADHSC] bit must be clear with 1 MHz ADC conversion clock speed.

#### Peripheral operating requirements and behaviors

- 4. 1 LSB =  $(V_{REFH} V_{REFL})/2^N$

- 5. ADC conversion clock < 16 MHz, Max hardware averaging (AVGE = %1, AVGS = %11)

- 6. Input data is 100 Hz sine wave. ADC conversion clock < 12 MHz.

- 7. Input data is 1 kHz sine wave. ADC conversion clock < 12 MHz.

- 8. ADC conversion clock < 3 MHz

Figure 14. Typical ENOB vs. ADC\_CLK for 16-bit single-ended mode

### 3.6.2 CMP and 6-bit DAC electrical specifications Table 26. Comparator and 6-bit DAC electrical specifications

| Symbol             | Description                                         | Min.                  | Тур. | Max.            | Unit             |

|--------------------|-----------------------------------------------------|-----------------------|------|-----------------|------------------|

| V <sub>DD</sub>    | Supply voltage                                      | 1.71                  | _    | 3.6             | V                |

| IDDHS              | Supply current, High-speed mode (EN=1, PMODE=1)     |                       | _    | 200             | μA               |

| I <sub>DDLS</sub>  | Supply current, low-speed mode (EN=1, PMODE=0)      |                       | _    | 20              | μA               |

| V <sub>AIN</sub>   | Analog input voltage                                | V <sub>SS</sub> – 0.3 | _    | V <sub>DD</sub> | V                |

| V <sub>AIO</sub>   | Analog input offset voltage                         | _                     | _    | 20              | mV               |

| V <sub>H</sub>     | Analog comparator hysteresis <sup>1</sup>           |                       |      |                 |                  |

|                    | • CR0[HYSTCTR] = 00                                 | _                     | 5    | _               | mV               |

|                    | • CR0[HYSTCTR] = 01                                 | —                     | 10   | _               | mV               |

|                    | • CR0[HYSTCTR] = 10                                 | —                     | 20   | _               | mV               |

|                    | • CR0[HYSTCTR] = 11                                 | —                     | 30   | _               | mV               |

| V <sub>CMPOh</sub> | Output high                                         | V <sub>DD</sub> – 0.5 |      | _               | V                |

| V <sub>CMPOI</sub> | Output low                                          |                       |      | 0.5             | V                |

| t <sub>DHS</sub>   | Propagation delay, high-speed mode (EN=1, PMODE=1)  | 20                    | 50   | 200             | ns               |

| t <sub>DLS</sub>   | Propagation delay, low-speed mode (EN=1, PMODE=0)   | 80                    | 250  | 600             | ns               |

|                    | Analog comparator initialization delay <sup>2</sup> |                       | _    | 40              | μs               |

| I <sub>DAC6b</sub> | 6-bit DAC current adder (enabled)                   |                       | 7    | _               | μA               |

| INL                | 6-bit DAC integral non-linearity                    | -0.5                  |      | 0.5             | LSB <sup>3</sup> |

| DNL                | 6-bit DAC differential non-linearity                | -0.3                  | _    | 0.3             | LSB              |

1. Typical hysteresis is measured with input voltage range limited to 0.6 to  $V_{DD}$ -0.6 V.

Comparator initialization delay is defined as the time between software writes to change control inputs (Writes to CMP\_DACCR[DACEN], CMP\_DACCR[VRSEL], CMP\_DACCR[VOSEL], CMP\_MUXCR[PSEL], and CMP\_MUXCR[MSEL]) and the comparator output settling to a stable level.

3. 1 LSB =  $V_{reference}/64$

#### 3.6.3.2 12-bit DAC operating behaviors Table 28. 12-bit DAC operating behaviors

| Symbol                     | Description                                                                            | Min.                      | Тур.     | Max.              | Unit   | Notes |

|----------------------------|----------------------------------------------------------------------------------------|---------------------------|----------|-------------------|--------|-------|

| I <sub>DDA_DACL</sub><br>P | Supply current — low-power mode                                                        |                           | —        | 330               | μΑ     |       |

| I <sub>DDA_DACH</sub><br>P | Supply current — high-speed mode                                                       | —                         | —        | 1200              | μΑ     |       |

| t <sub>DACLP</sub>         | Full-scale settling time (0x080 to 0xF7F) — low-power mode                             | —                         | 100      | 200               | μs     | 1     |

| t <sub>DACHP</sub>         | Full-scale settling time (0x080 to 0xF7F) — high-power mode                            | _                         | 15       | 30                | μs     | 1     |

| t <sub>CCDACLP</sub>       | Code-to-code settling time (0xBF8 to<br>0xC08) — low-power mode and high-speed<br>mode | _                         | 0.7      | 1                 | μs     | 1     |

| V <sub>dacoutl</sub>       | DAC output voltage range low — high-<br>speed mode, no load, DAC set to 0x000          | —                         | —        | 100               | mV     |       |

| V <sub>dacouth</sub>       | DAC output voltage range high — high-<br>speed mode, no load, DAC set to 0xFFF         | V <sub>DACR</sub><br>-100 | —        | V <sub>DACR</sub> | mV     |       |

| INL                        | Integral non-linearity error — high speed mode                                         | _                         | —        | ±8                | LSB    | 2     |

| DNL                        | Differential non-linearity error — $V_{DACR} > 2$<br>V                                 | —                         | —        | ±1                | LSB    | 3     |

| DNL                        | Differential non-linearity error — V <sub>DACR</sub> = VREF_OUT                        | —                         | —        | ±1                | LSB    | 4     |

| V <sub>OFFSET</sub>        | Offset error                                                                           | _                         | ±0.4     | ±0.8              | %FSR   | 5     |

| E <sub>G</sub>             | Gain error                                                                             | _                         | ±0.1     | ±0.6              | %FSR   | 5     |

| PSRR                       | Power supply rejection ratio, $V_{DDA} \ge 2.4 \text{ V}$                              | 60                        | —        | 90                | dB     |       |

| T <sub>CO</sub>            | Temperature coefficient offset voltage                                                 | _                         | 3.7      | _                 | μV/C   | 6     |

| $T_{GE}$                   | Temperature coefficient gain error                                                     | _                         | 0.000421 | —                 | %FSR/C |       |

| Rop                        | Output resistance (load = $3 \text{ k}\Omega$ )                                        | —                         | —        | 250               | Ω      |       |

| SR                         | Slew rate -80h $\rightarrow$ F7Fh $\rightarrow$ 80h                                    |                           |          |                   | V/µs   |       |

|                            | <ul> <li>High power (SP<sub>HP</sub>)</li> </ul>                                       | 1.2                       | 1.7      | —                 |        |       |

|                            | <ul> <li>Low power (SP<sub>LP</sub>)</li> </ul>                                        | 0.05                      | 0.12     | —                 |        |       |

| BW                         | 3dB bandwidth                                                                          |                           |          |                   | kHz    |       |

|                            | <ul> <li>High power (SP<sub>HP</sub>)</li> </ul>                                       | 550                       | _        | _                 |        |       |

|                            | • Low power (SP <sub>LP</sub> )                                                        | 40                        | _        | _                 |        |       |

1. Settling within  $\pm 1$  LSB

2. The INL is measured for 0 + 100 mV to  $V_{DACR}$  –100 mV

3. The DNL is measured for 0 + 100 mV to  $V_{DACR}$  –100 mV

4. The DNL is measured for 0 + 100 mV to  $V_{DACR}$  –100 mV with  $V_{DDA}$  > 2.4 V 5. Calculated by a best fit curve from  $V_{SS}$  + 100 mV to  $V_{DACR}$  – 100 mV

6. V<sub>DDA</sub> = 3.0 V, reference select set for V<sub>DDA</sub> (DACx\_CO:DACRFS = 1), high power mode (DACx\_CO:LPEN = 0), DAC set to 0x800, temperature range is across the full range of the device

40

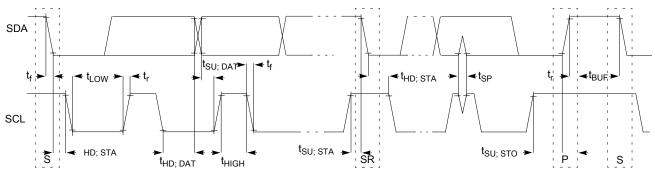

Figure 23. Timing definition for devices on the I<sup>2</sup>C bus

## 3.8.4 UART switching specifications

See General switching specifications.

## 3.9 Kinetis Motor Suite

Kinetis Motor Suite is a bundled software solution that enables the rapid configuration of motor drive systems, and accelerates development of the final motor drive application.

Several members of the KV3x family are enabled with Kinetis motor suite. The enabled devices can be identified within the orderable part numbers in this table. For more information refer to Kinetis Motor Suite User's Guide (KMS100UG) and Kinetis Motor Suite API Reference Manual (KMS100RM).

### NOTE

To find the associated resource, go to freescale.com and perform a search using Document ID.

## 4 Dimensions

## 4.1 Obtaining package dimensions

Package dimensions are provided in package drawings.

To find a package drawing, go to freescale.com and perform a keyword search for the drawing's document number:

| 100<br>LQFP | 64<br>LQFP | Pin Name           | Default                | ALT0                   | ALT1               | ALT2      | ALT3              | ALT4     | ALT5   | ALT6              | ALT7              | EzPort |

|-------------|------------|--------------------|------------------------|------------------------|--------------------|-----------|-------------------|----------|--------|-------------------|-------------------|--------|

| 70          | 43         | PTC0               | ADC0_SE14              | ADC0_SE14              | PTC0               | SPI0_PCS4 | PDB0_<br>EXTRG    |          |        | FTM0_FLT1         | SPI0_PCS0         |        |

| 71          | 44         | PTC1/<br>LLWU_P6   | ADC0_SE15              | ADC0_SE15              | PTC1/<br>LLWU_P6   | SPI0_PCS3 | UART1_<br>RTS_b   | FTM0_CH0 |        |                   | LPUART0_<br>RTS_b |        |

| 72          | 45         | PTC2               | ADC0_SE4b/<br>CMP1_IN0 | ADC0_SE4b/<br>CMP1_IN0 | PTC2               | SPI0_PCS2 | UART1_<br>CTS_b   | FTM0_CH1 |        |                   | LPUART0_<br>CTS_b |        |

| 73          | 46         | PTC3/<br>LLWU_P7   | CMP1_IN1               | CMP1_IN1               | PTC3/<br>LLWU_P7   | SPI0_PCS1 | UART1_RX          | FTM0_CH2 | CLKOUT |                   | LPUART0_<br>RX    |        |

| 74          | 47         | VSS                | VSS                    | VSS                    |                    |           |                   |          |        |                   |                   |        |

| 75          | 48         | VDD                | VDD                    | VDD                    |                    |           |                   |          |        |                   |                   |        |

| 76          | 49         | PTC4/<br>LLWU_P8   | DISABLED               |                        | PTC4/<br>LLWU_P8   | SPI0_PCS0 | UART1_TX          | FTM0_CH3 |        | CMP1_OUT          | LPUART0_<br>TX    |        |

| 77          | 50         | PTC5/<br>LLWU_P9   | DISABLED               |                        | PTC5/<br>LLWU_P9   | SPI0_SCK  | LPTMR0_<br>ALT2   |          |        | CMP0_OUT          | FTM0_CH2          |        |

| 78          | 51         | PTC6/<br>LLWU_P10  | CMP0_IN0               | CMP0_IN0               | PTC6/<br>LLWU_P10  | SPI0_SOUT | PDB0_<br>EXTRG    |          |        |                   | 12C0_SCL          |        |

| 79          | 52         | PTC7               | CMP0_IN1               | CMP0_IN1               | PTC7               | SPI0_SIN  |                   |          |        |                   | I2C0_SDA          |        |

| 80          | 53         | PTC8               | ADC1_SE4b/<br>CMP0_IN2 | ADC1_SE4b/<br>CMP0_IN2 | PTC8               |           |                   |          |        |                   |                   |        |

| 81          | 54         | PTC9               | ADC1_SE5b/<br>CMP0_IN3 | ADC1_SE5b/<br>CMP0_IN3 | PTC9               |           |                   |          |        | FTM2_FLT0         |                   |        |

| 82          | 55         | PTC10              | ADC1_SE6b              | ADC1_SE6b              | PTC10              | I2C1_SCL  |                   |          |        |                   |                   |        |

| 83          | 56         | PTC11/<br>LLWU_P11 | ADC1_SE7b              | ADC1_SE7b              | PTC11/<br>LLWU_P11 | I2C1_SDA  |                   |          |        |                   |                   |        |

| 84          | _          | PTC12              | DISABLED               |                        | PTC12              |           |                   |          |        |                   |                   |        |

| 85          | _          | PTC13              | DISABLED               |                        | PTC13              |           |                   |          |        |                   |                   |        |

| 86          | _          | PTC14              | DISABLED               |                        | PTC14              |           |                   |          |        |                   |                   |        |

| 87          | _          | PTC15              | DISABLED               |                        | PTC15              |           |                   |          |        |                   |                   |        |

| 88          | _          | VSS                | VSS                    | VSS                    |                    |           |                   |          |        |                   |                   |        |

| 89          | _          | VDD                | VDD                    | VDD                    |                    |           |                   |          |        |                   |                   |        |

| 90          | -          | PTC16              | DISABLED               |                        | PTC16              |           | LPUART0_<br>RX    |          |        |                   |                   |        |

| 91          | -          | PTC17              | DISABLED               |                        | PTC17              |           | LPUART0_<br>TX    |          |        |                   |                   |        |

| 92          | -          | PTC18              | DISABLED               |                        | PTC18              |           | LPUARTO_<br>RTS_b |          |        |                   |                   |        |

| 93          | 57         | PTD0/<br>LLWU_P12  | DISABLED               |                        | PTD0/<br>LLWU_P12  | SPI0_PCS0 | UART2_<br>RTS_b   | FTM0_CH0 |        | LPUART0_<br>RTS_b |                   |        |

| 94          | 58         | PTD1               | ADC0_SE5b              | ADC0_SE5b              | PTD1               | SPI0_SCK  | UART2_<br>CTS_b   | FTM0_CH1 |        | LPUARTO_<br>CTS_b |                   |        |

| 95          | 59         | PTD2/<br>LLWU_P13  | DISABLED               |                        | PTD2/<br>LLWU_P13  | SPI0_SOUT | UART2_RX          | FTM0_CH2 |        | LPUART0_<br>RX    | I2C0_SCL          |        |

| 96          | 60         | PTD3               | DISABLED               |                        | PTD3               | SPI0_SIN  | UART2_TX          | FTM0_CH3 |        | LPUART0_<br>TX    | I2C0_SDA          |        |

| Pin Type |       | Short recommendation            | Detailed recommendation         |

|----------|-------|---------------------------------|---------------------------------|

| VREFH    | VREFH | Always connect to VDD potential | Always connect to VDD potential |

| VREFL    | VREFL | Always connect to VSS potential | Always connect to VSS potential |

| VSSA     | VSSA  | Always connect to VSS potential | Always connect to VSS potential |

Table 39. Recommended connection for unused analog interfaces (continued)

## 5.3 KV31F Pinouts

The following figure shows the pinout diagram for the devices supported by this document. Many signals may be multiplexed onto a single pin. To determine what signals can be used on which pin, see the previous section.