Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | AVR                                                                             |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 66MHz                                                                           |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 123                                                                             |

| Program Memory Size        | 512KB (512K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 64K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                       |

| Data Converters            | A/D 16x12b; D/A 4x12b                                                           |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 144-LQFP                                                                        |

| Supplier Device Package    | 144-LQFP (20x20)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at32uc3c0512c-alur    |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 2-1. | Configuration Summary |

|------------|-----------------------|

|------------|-----------------------|

| Feature            | AT32UC3C0512C/<br>AT32UC3C0256C/<br>AT32UC3C0128C/<br>AT32UC3C064C | AT32UC3C1512C/<br>AT32UC3C1256C/<br>AT32UC3C1128C/<br>AT32UC3C164C | AT32UC3C2512C/<br>AT32UC3C2256C/<br>AT32UC3C2128C/<br>AT32UC3C264C |  |  |  |

|--------------------|--------------------------------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------|--|--|--|

| Analog Comparators | 4                                                                  | 4                                                                  | 2                                                                  |  |  |  |

| JTAG               |                                                                    | 1                                                                  |                                                                    |  |  |  |

| aWire              | 1                                                                  |                                                                    |                                                                    |  |  |  |

| Max Frequency      | 66 MHz                                                             |                                                                    |                                                                    |  |  |  |

| Package            | LQFP144                                                            | TQFP100                                                            | TQFP64/QFN64                                                       |  |  |  |

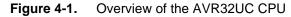

### 4.3.1 Pipeline Overview

AVR32UC has three pipeline stages, Instruction Fetch (IF), Instruction Decode (ID), and Instruction Execute (EX). The EX stage is split into three parallel subsections, one arithmetic/logic (ALU) section, one multiply (MUL) section, and one load/store (LS) section.

Instructions are issued and complete in order. Certain operations require several clock cycles to complete, and in this case, the instruction resides in the ID and EX stages for the required number of clock cycles. Since there is only three pipeline stages, no internal data forwarding is required, and no data dependencies can arise in the pipeline.

Figure 4-2 on page 28 shows an overview of the AVR32UC pipeline stages.

| Reg #   | Address  | Name      | Function                                        |

|---------|----------|-----------|-------------------------------------------------|

| 90      | 360      | MPUPSR2   | MPU Privilege Select Register region 2          |

| 91      | 364      | MPUPSR3   | MPU Privilege Select Register region 3          |

| 92      | 368      | MPUPSR4   | MPU Privilege Select Register region 4          |

| 93      | 372      | MPUPSR5   | MPU Privilege Select Register region 5          |

| 94      | 376      | MPUPSR6   | MPU Privilege Select Register region 6          |

| 95      | 380      | MPUPSR7   | MPU Privilege Select Register region 7          |

| 96      | 384      | MPUCRA    | Unused in this version of AVR32UC               |

| 97      | 388      | MPUCRB    | Unused in this version of AVR32UC               |

| 98      | 392      | MPUBRA    | Unused in this version of AVR32UC               |

| 99      | 396      | MPUBRB    | Unused in this version of AVR32UC               |

| 100     | 400      | MPUAPRA   | MPU Access Permission Register A                |

| 101     | 404      | MPUAPRB   | MPU Access Permission Register B                |

| 102     | 408      | MPUCR     | MPU Control Register                            |

| 103     | 412      | SS_STATUS | Secure State Status Register                    |

| 104     | 416      | SS_ADRF   | Secure State Address Flash Register             |

| 105     | 420      | SS_ADRR   | Secure State Address RAM Register               |

| 106     | 424      | SS_ADR0   | Secure State Address 0 Register                 |

| 107     | 428      | SS_ADR1   | Secure State Address 1 Register                 |

| 108     | 432      | SS_SP_SYS | Secure State Stack Pointer System Register      |

| 109     | 436      | SS_SP_APP | Secure State Stack Pointer Application Register |

| 110     | 440      | SS_RAR    | Secure State Return Address Register            |

| 111     | 444      | SS_RSR    | Secure State Return Status Register             |

| 112-191 | 448-764  | Reserved  | Reserved for future use                         |

| 192-255 | 768-1020 | IMPL      | IMPLEMENTATION DEFINED                          |

Table 4 9 m Deviatere (Centinued)

#### 4.5 **Exceptions and Interrupts**

In the AVR32 architecture, events are used as a common term for exceptions and interrupts. AVR32UC incorporates a powerful event handling scheme. The different event sources, like Illegal Op-code and interrupt requests, have different priority levels, ensuring a well-defined behavior when multiple events are received simultaneously. Additionally, pending events of a higher priority class may preempt handling of ongoing events of a lower priority class.

When an event occurs, the execution of the instruction stream is halted, and execution is passed to an event handler at an address specified in Table 4-4 on page 38. Most of the handlers are placed sequentially in the code space starting at the address specified by EVBA, with four bytes between each handler. This gives ample space for a jump instruction to be placed there, jumping to the event routine itself. A few critical handlers have larger spacing between them, allowing the entire event routine to be placed directly at the address specified by the EVBA-relative offset generated by hardware. All interrupt sources have autovectored interrupt service routine (ISR) addresses. This allows the interrupt controller to directly specify the ISR address as an address

relative to EVBA. The autovector offset has 14 address bits, giving an offset of maximum 16384 bytes. The target address of the event handler is calculated as (EVBA | event\_handler\_offset), not (EVBA + event\_handler\_offset), so EVBA and exception code segments must be set up appropriately. The same mechanisms are used to service all different types of events, including interrupt requests, yielding a uniform event handling scheme.

An interrupt controller does the priority handling of the interrupts and provides the autovector offset to the CPU.

### 4.5.1 System Stack Issues

Event handling in AVR32UC uses the system stack pointed to by the system stack pointer, SP\_SYS, for pushing and popping R8-R12, LR, status register, and return address. Since event code may be timing-critical, SP\_SYS should point to memory addresses in the IRAM section, since the timing of accesses to this memory section is both fast and deterministic.

The user must also make sure that the system stack is large enough so that any event is able to push the required registers to stack. If the system stack is full, and an event occurs, the system will enter an UNDEFINED state.

### 4.5.2 Exceptions and Interrupt Requests

When an event other than *scall* or debug request is received by the core, the following actions are performed atomically:

- 1. The pending event will not be accepted if it is masked. The I3M, I2M, I1M, I0M, EM, and GM bits in the Status Register are used to mask different events. Not all events can be masked. A few critical events (NMI, Unrecoverable Exception, TLB Multiple Hit, and Bus Error) can not be masked. When an event is accepted, hardware automatically sets the mask bits corresponding to all sources with equal or lower priority. This inhibits acceptance of other events of the same or lower priority, except for the critical events listed above. Software may choose to clear some or all of these bits after saving the necessary state if other priority schemes are desired. It is the event source's responsability to ensure that their events are left pending until accepted by the CPU.

- 2. When a request is accepted, the Status Register and Program Counter of the current context is stored to the system stack. If the event is an INT0, INT1, INT2, or INT3, registers R8-R12 and LR are also automatically stored to stack. Storing the Status Register ensures that the core is returned to the previous execution mode when the current event handling is completed. When exceptions occur, both the EM and GM bits are set, and the application may manually enable nested exceptions if desired by clearing the appropriate bit. Each exception handler has a dedicated handler address, and this address uniquely identifies the exception source.

- 3. The Mode bits are set to reflect the priority of the accepted event, and the correct register file bank is selected. The address of the event handler, as shown in Table 4-4 on page 38, is loaded into the Program Counter.

The execution of the event handler routine then continues from the effective address calculated.

The *rete* instruction signals the end of the event. When encountered, the Return Status Register and Return Address Register are popped from the system stack and restored to the Status Register and Program Counter. If the *rete* instruction returns from INT0, INT1, INT2, or INT3, registers R8-R12 and LR are also popped from the system stack. The restored Status Register contains information allowing the core to resume operation in the previous execution mode. This concludes the event handling.

### 4.5.3 Supervisor Calls

The AVR32 instruction set provides a supervisor mode call instruction. The *scall* instruction is designed so that privileged routines can be called from any context. This facilitates sharing of code between different execution modes. The *scall* mechanism is designed so that a minimal execution cycle overhead is experienced when performing supervisor routine calls from time-critical event handlers.

The *scall* instruction behaves differently depending on which mode it is called from. The behaviour is detailed in the instruction set reference. In order to allow the *scall* routine to return to the correct context, a return from supervisor call instruction, *rets*, is implemented. In the AVR32UC CPU, *scall* and *rets* uses the system stack to store the return address and the status register.

### 4.5.4 Debug Requests

The AVR32 architecture defines a dedicated Debug mode. When a debug request is received by the core, Debug mode is entered. Entry into Debug mode can be masked by the DM bit in the status register. Upon entry into Debug mode, hardware sets the SR.D bit and jumps to the Debug Exception handler. By default, Debug mode executes in the exception context, but with dedicated Return Address Register and Return Status Register. These dedicated registers remove the need for storing this data to the system stack, thereby improving debuggability. The Mode bits in the Status Register can freely be manipulated in Debug mode, to observe registers in all contexts, while retaining full privileges.

Debug mode is exited by executing the *retd* instruction. This returns to the previous context.

### 4.5.5 Entry Points for Events

Several different event handler entry points exist. In AVR32UC, the reset address is 0x80000000. This places the reset address in the boot flash memory area.

TLB miss exceptions and *scall* have a dedicated space relative to EVBA where their event handler can be placed. This speeds up execution by removing the need for a jump instruction placed at the program address jumped to by the event hardware. All other exceptions have a dedicated event routine entry point located relative to EVBA. The handler routine address identifies the exception source directly.

AVR32UC uses the ITLB and DTLB protection exceptions to signal a MPU protection violation. ITLB and DTLB miss exceptions are used to signal that an access address did not map to any of the entries in the MPU. TLB multiple hit exception indicates that an access address did map to multiple TLB entries, signalling an error.

All interrupt requests have entry points located at an offset relative to EVBA. This autovector offset is specified by an interrupt controller. The programmer must make sure that none of the autovector offsets interfere with the placement of other code. The autovector offset has 14 address bits, giving an offset of maximum 16384 bytes.

Special considerations should be made when loading EVBA with a pointer. Due to security considerations, the event handlers should be located in non-writeable flash memory, or optionally in a privileged memory protection region if an MPU is present.

If several events occur on the same instruction, they are handled in a prioritized way. The priority ordering is presented in Table 4-4 on page 38. If events occur on several instructions at different locations in the pipeline, the events on the oldest instruction are always handled before any events on any younger instruction, even if the younger instruction has events of higher priority

# AT32UC3C

| Priority | Handler Address        | Name                        | Event source   | Stored Return Address           |

|----------|------------------------|-----------------------------|----------------|---------------------------------|

| 1        | 0x80000000             | Reset                       | External input | Undefined                       |

| 2        | Provided by OCD system | OCD Stop CPU                | OCD system     | First non-completed instruction |

| 3        | EVBA+0x00              | Unrecoverable exception     | Internal       | PC of offending instruction     |

| 4        | EVBA+0x04              | TLB multiple hit            | MPU            | PC of offending instruction     |

| 5        | EVBA+0x08              | Bus error data fetch        | Data bus       | First non-completed instruction |

| 6        | EVBA+0x0C              | Bus error instruction fetch | Data bus       | First non-completed instruction |

| 7        | EVBA+0x10              | NMI                         | External input | First non-completed instruction |

| 8        | Autovectored           | Interrupt 3 request         | External input | First non-completed instruction |

| 9        | Autovectored           | Interrupt 2 request         | External input | First non-completed instruction |

| 10       | Autovectored           | Interrupt 1 request         | External input | First non-completed instruction |

| 11       | Autovectored           | Interrupt 0 request         | External input | First non-completed instruction |

| 12       | EVBA+0x14              | Instruction Address         | CPU            | PC of offending instruction     |

| 13       | EVBA+0x50              | ITLB Miss                   | MPU            | PC of offending instruction     |

| 14       | EVBA+0x18              | ITLB Protection             | MPU            | PC of offending instruction     |

| 15       | EVBA+0x1C              | Breakpoint                  | OCD system     | First non-completed instruction |

| 16       | EVBA+0x20              | Illegal Opcode              | Instruction    | PC of offending instruction     |

| 17       | EVBA+0x24              | Unimplemented instruction   | Instruction    | PC of offending instruction     |

| 18       | EVBA+0x28              | Privilege violation         | Instruction    | PC of offending instruction     |

| 19       | EVBA+0x2C              | Floating-point              | UNUSED         |                                 |

| 20       | EVBA+0x30              | Coprocessor absent          | Instruction    | PC of offending instruction     |

| 21       | EVBA+0x100             | Supervisor call             | Instruction    | PC(Supervisor Call) +2          |

| 22       | EVBA+0x34              | Data Address (Read)         | CPU            | PC of offending instruction     |

| 23       | EVBA+0x38              | Data Address (Write)        | CPU            | PC of offending instruction     |

| 24       | EVBA+0x60              | DTLB Miss (Read)            | MPU            | PC of offending instruction     |

| 25       | EVBA+0x70              | DTLB Miss (Write)           | MPU            | PC of offending instruction     |

| 26       | EVBA+0x3C              | DTLB Protection (Read)      | MPU            | PC of offending instruction     |

| 27       | EVBA+0x40              | DTLB Protection (Write)     | MPU            | PC of offending instruction     |

| 28       | EVBA+0x44              | DTLB Modified               | UNUSED         |                                 |

### Table 4-4. Priority and Handler Addresses for Events

The following GPIO registers are mapped on the local bus:

Table 5-4.

Local bus mapped GPIO registers

| Port | Register                             | Mode                     | Local Bus<br>Address | Access     |

|------|--------------------------------------|--------------------------|----------------------|------------|

| А    | Output Driver Enable Register (ODER) | WRITE                    | 0x40000040           | Write-only |

|      |                                      | Mode Address             | Write-only           |            |

|      |                                      | CLEAR                    | 0x40000048           | Write-only |

|      |                                      | TOGGLE                   | 0x4000004C           | Write-only |

|      | Output Value Register (OVR)          | WRITE                    | 0x40000050           | Write-only |

|      |                                      | SET                      | 0x40000054           | Write-only |

|      |                                      | CLEAR                    | 0x40000058           | Write-only |

|      |                                      | TOGGLE                   | 0x4000005C           | Write-only |

|      | Pin Value Register (PVR)             | -                        | 0x40000060           | Read-only  |

| В    | Output Driver Enable Register (ODER) | WRITE                    | 0x40000140           | Write-only |

|      |                                      | SET 0x400<br>CLEAR 0x400 | 0x40000144           | Write-only |

|      |                                      | CLEAR                    | 0x40000148           | Write-only |

|      |                                      | TOGGLE                   | 0x4000014C           | Write-only |

|      | Output Value Register (OVR)          | WRITE                    | 0x40000150           | Write-only |

|      |                                      | SET                      | 0x40000154           | Write-only |

|      |                                      | CLEAR                    | 0x40000158           | Write-only |

|      |                                      | TOGGLE                   | 0x4000015C           | Write-only |

|      | Pin Value Register (PVR)             | -                        | 0x40000160           | Read-only  |

| С    | Output Driver Enable Register (ODER) | WRITE                    | 0x40000240           | Write-only |

|      |                                      | SET                      | 0x40000244           | Write-only |

|      |                                      | CLEAR                    | 0x40000248           | Write-only |

|      |                                      | TOGGLE                   | 0x4000024C           | Write-only |

|      | Output Value Register (OVR)          | WRITE                    | 0x40000250           | Write-only |

|      |                                      | SET                      | 0x40000254           | Write-only |

|      |                                      | CLEAR                    | 0x40000258           | Write-only |

|      |                                      | TOGGLE                   | 0x4000025C           | Write-only |

|      | Pin Value Register (PVR)             | -                        | 0x40000260           | Read-only  |

## 6. Supply and Startup Considerations

### 6.1 Supply Considerations

### 6.1.1 Power Supplies

The AT32UC3C has several types of power supply pins:

- VDDIO pins (VDDIO1, VDDIO2, VDDIO3): Power I/O lines. Two voltage ranges are available: 5V or 3.3V nominal. The VDDIO pins should be connected together.

- VDDANA: Powers the Analog part of the device (Analog I/Os, ADC, ACs, DACs). 2 voltage ranges available: 5V or 3.3V nominal.

- VDDIN\_5: Input voltage for the 1.8V and 3.3V regulators. Two Voltage ranges are available: 5V or 3.3V nominal.

- VDDIN\_33:

- USB I/O power supply

- if the device is 3.3V powered: Input voltage, voltage is 3.3V nominal.

- if the device is 5V powered: stabilization for the 3.3V voltage regulator, requires external capacitors

- VDDCORE: Stabilization for the 1.8V voltage regulator, requires external capacitors.

- GNDCORE: Ground pins for the voltage regulators and the core.

- GNDANA: Ground pin for Analog part of the design

- GNDPLL: Ground pin for the PLLs

- GNDIO pins (GNDIO1, GNDIO2, GNDIO3): Ground pins for the I/O lines. The GNDIO pins should be connected together.

See "Electrical Characteristics" on page 50 for power consumption on the various supply pins.

For decoupling recommendations for the different power supplies, please refer to the schematic checklist.

### 6.1.2 Voltage Regulators

The AT32UC3C embeds two voltage regulators:

- One 1.8V internal regulator that converts from VDDIN\_5 to 1.8V. The regulator supplies the output voltage on VDDCORE.

- One 3.3V internal regulator that converts from VDDIN\_5 to 3.3V. The regulator supplies the USB pads on VDDIN\_33. If the USB is not used or if VDDIN\_5 is within the 3V range, the 3.3V regulator can be disabled through the VREG33CTL field of the VREGCTRL SCIF register.

### 6.1.3 Regulators Connection

The AT32UC3C supports two power supply configurations.

- 5V single supply mode

- 3.3V single supply mode

### 6.1.3.1 5V Single Supply Mode

In 5V single supply mode, the 1.8V internal regulator is connected to the 5V source (VDDIN\_5 pin) and its output feeds VDDCORE.

### 6.2 Startup Considerations

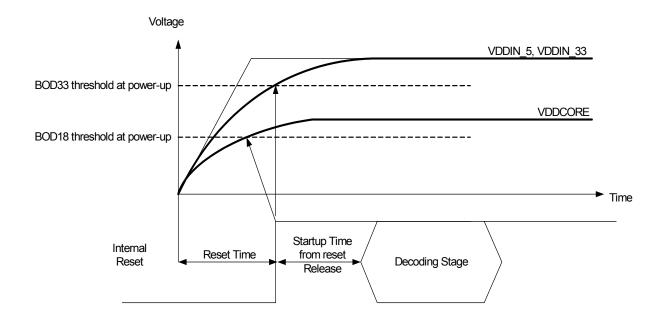

This chapter summarizes the boot sequence of the AT32UC3C. The behavior after power-up is controlled by the Power Manager. For specific details, refer to the Power Manager chapter.

### 6.2.1 Starting of clocks

At power-up, the BOD33 and the BOD18 are enabled. The device will be held in a reset state by the power-up circuitry, until the VDDIN\_33 (resp. VDDCORE) has reached the reset threshold of the BOD33 (resp BOD18). Refer to the Electrical Characteristics for the BOD thresholds. Once the power has stabilized, the device will use the System RC Oscillator (RCSYS, 115KHz typical frequency) as clock source. The BOD18 and BOD33 are kept enabled or are disabled according to the fuse settings (See the Fuse Setting section in the Flash Controller chapter).

On system start-up, the PLLs are disabled. All clocks to all modules are running. No clocks have a divided frequency, all parts of the system receive a clock with the same frequency as the internal RC Oscillator.

### 6.2.2 Fetching of initial instructions

After reset has been released, the AVR32UC CPU starts fetching instructions from the reset address, which is 0x8000\_0000. This address points to the first address in the internal Flash.

The internal Flash uses VDDIO voltage during read and write operations. It is recommended to use the BOD33 to monitor this voltage and make sure the VDDIO is above the minimum level (3.0V).

The code read from the internal Flash is free to configure the system to use for example the PLLs, to divide the frequency of the clock routed to some of the peripherals, and to gate the clocks to unused peripherals.

### 7.6 Oscillator Characteristics

### 7.6.1 Oscillator (OSC0 and OSC1) Characteristics

7.6.1.1 Digital Clock Characteristics

The following table describes the characteristics for the oscillator when a digital clock is applied on XIN0 or XIN1.

Table 7-7.

Digital Clock Characteristics

| Symbol             | Parameter                 | Conditions | Min                      | Тур | Мах                      | Units |

|--------------------|---------------------------|------------|--------------------------|-----|--------------------------|-------|

| f <sub>CPXIN</sub> | XIN clock frequency       |            |                          |     | 50                       | MHz   |

| t <sub>CPXIN</sub> | XIN clock period          |            | 20                       |     |                          | ns    |

| t <sub>CHXIN</sub> | XIN clock high half-priod |            | 0.4 x t <sub>CPXIN</sub> |     | 0.6 x t <sub>CPXIN</sub> | ns    |

| t <sub>CLXIN</sub> | XIN clock low half-priod  |            | 0.4 x t <sub>CPXIN</sub> |     | 0.6 x t <sub>CPXIN</sub> | ns    |

| C <sub>IN</sub>    | XIN input capacitance     |            |                          | 2   |                          | pF    |

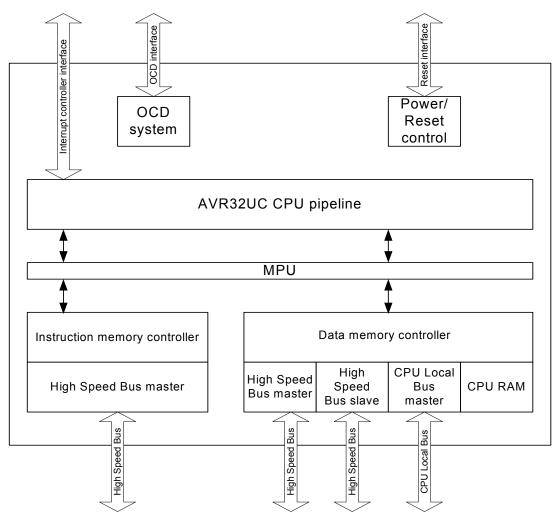

7.6.1.2 Crystal Oscillator Characteristics

The following table describes the characteristics for the oscillator when a crystal is connected between XIN and XOUT as shown in Figure 7-2. The user must choose a crystal oscillator where the crystal load capacitance  $C_L$  is within the range given in the table. The exact value of  $C_L$  can be found in the crystal datasheet. The capacitance of the external capacitors ( $C_{LEXT}$ ) can then be computed as follows:

$$C_{LEXT} = 2(C_L - C_i) - C_{PCB}$$

where  $C_{PCB}$  is the capacitance of the PCB and  $C_i$  is the internal equivalent load capacitance.

### Figure 7-2. Oscillator Connection

### 7.8.6 Analog to Digital Converter (ADC) and sample and hold (S/H) Characteristics

| Symbol               | Parameter        | Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Min                               | Тур                 | Max | Units     |

|----------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|---------------------|-----|-----------|

|                      |                  | 12-bit resolution mode, $V_{VDDANA} = 3V$                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                   |                     | 1.2 |           |

|                      |                  | 10-bit resolution mode, $V_{VDDANA} = 3V$                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                   |                     | 1.6 |           |

| £                    | ADC clock        | 8-bit resolution mode, $V_{VDDANA} = 3V$                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                   |                     | 2.2 | MHz       |

| f <sub>ADC</sub>     | frequency        | 12-bit resolution mode, $V_{VDDANA} = 4.5V$                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                   |                     | 1.5 |           |

|                      |                  | 10-bit resolution mode, $V_{VDDANA} = 4.5V$                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                   |                     | 2   | _         |

|                      |                  | 8-bit resolution mode, $V_{VDDANA} = 4.5V$                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                   |                     | 2.4 |           |

|                      |                  | ADC cold start-up                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                   |                     | 1   | ms        |

| t <sub>STARTUP</sub> | Startup time     | ADC hot start-up                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | = 4.5V 2.4<br>1<br>24<br>+ 2, 6 8 | ADC clock<br>cycles |     |           |

|                      | Conversion time  | (ADCIFA.SEQCFGn.SRES)/2 + 2,<br>ADCIFA.CFG.SHD = 1                                                                                                                                                                                                                                                                                                                                                                                                                                       | 6                                 |                     | 8   | ADC clock |

| t <sub>CONV</sub>    | (latency)        | InductionInduction (V_VDDANA = 100 C)10-bit resolution mode, V_VDDANA = 4.5V8-bit resolution mode, V_VDDANA = 4.5VADC cold start-upADC hot start-upADC hot start-up(ADCIFA.SEQCFGn.SRES)/2 + 2,<br>ADCIFA.CFG.SHD = 1(ADCIFA.SEQCFGn.SRES)/2 + 3,<br>ADCIFA.CFG.SHD = 0(ADCIFA.SEQCFGn.SRES)/2 + 3,<br>ADCIFA.CFG.SHD = 012-bit resolution,<br>ADC clock = 1.2 MHz, V_VDDANA = 3Vnoughput rateADC clock = 1.6 MHz, V_VDDANA = 3V12-bit resolution,<br>ADC clock = 1.6 MHz, V_VDDANA = 3V | 9                                 | cycles              |     |           |

|                      |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                   |                     | 1.2 |           |

|                      |                  | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                   |                     | 1.6 | MODO      |

|                      | i nrougnput rate | 12-bit resolution,<br>ADC clock = 1.5 MHz, V <sub>VDDANA</sub> = 4.5V                                                                                                                                                                                                                                                                                                                                                                                                                    |                                   |                     | 1.5 | – MSPS    |

|                      |                  | 10-bit resolution,<br>ADC clock = 2 MHz, V <sub>VDDANA</sub> = 4.5V                                                                                                                                                                                                                                                                                                                                                                                                                      |                                   |                     | 2   |           |

### Table 7-27. ADC and S/H characteristics

### Table 7-28. ADC Reference Voltage

| Symbol                                     | Parameter                     | Conditions                                      | Min | Тур                     | Max                             | Unit<br>s |

|--------------------------------------------|-------------------------------|-------------------------------------------------|-----|-------------------------|---------------------------------|-----------|

| N/                                         | ADCREF0 input voltage range   | 5V Range                                        | 1   |                         | 3.5                             | V         |

| V <sub>ADCREF0</sub>                       | ADCREFO Input voltage lange   | 3V Range                                        | 1   |                         | V <sub>VDDANA</sub> -0.7        | v         |

| M                                          |                               | 5V Range                                        | 1   |                         | 3.5                             | V         |

| V <sub>ADCREF1</sub> ADCREF1 input voltage | ADCREFT Input voltage lange   | 3V Range                                        | 1   |                         | V <sub>VDDANA</sub> -0.7        | v         |

|                                            |                               | 5V Range - Voltage reference applied on ADCREFP | 1   |                         | 3.5                             | - V       |

| V <sub>ADCREFP</sub>                       | ADCREFP input voltage         | 3V Range - Voltage reference applied on ADCREFP | 1   |                         | 3.5<br>V <sub>VDDANA</sub> -0.7 | V         |

| V <sub>ADCREFN</sub>                       | ADCREFN input voltage         | Voltage reference applied on<br>ADCREFN         |     | GNDANA                  |                                 | V         |

|                                            | Internal 1V reference         |                                                 |     | 1.0                     |                                 | V         |

|                                            | Internal 0.6*VDDANA reference |                                                 |     | 0.6*V <sub>VDDANA</sub> |                                 | V         |

| Symbol | Parameter                  | Conditions                                        | Min | Тур | Max | Units |

|--------|----------------------------|---------------------------------------------------|-----|-----|-----|-------|

| RES    | Resolution                 | Differential mode,                                |     |     | 10  | Bit   |

| INL    | Integral Non-Linearity     | $V_{VDDANA} = 5V,$                                |     |     | 1.5 | LSB   |

| DNL    | Differential Non-Linearity | $V_{ADCREF0} = 3V,$                               |     |     | 1.5 | LSB   |

|        | Offset error               | ADCFIA.SEQCFGn.SRES = 1,<br>S/H gain from 1 to 16 | -25 |     | 25  | mV    |

|        | Gain error                 | $(F_{adc} = 1.5MHz)$                              | -15 |     | 15  | mV    |

Table 7-36. ADC and S/H Transfer Characteristics (Continued)10-bit Resolution Mode and S/H gain from 1 to 16<sup>(1)</sup>

Note: 1. The measures are done without any I/O activity on VDDANA/GNDANA power domain.

### 7.8.7 Digital to Analog Converter (DAC) Characteristics

Table 7-37.

Channel Conversion Time and DAC Clock

| Symbol               | Parameter                 | Conditions                   | Min | Тур | Max                 | Units |

|----------------------|---------------------------|------------------------------|-----|-----|---------------------|-------|

| f <sub>DAC</sub>     | DAC clock frequency       |                              |     |     | 1                   | MHz   |

| t <sub>STARTUP</sub> | Startup time              |                              |     |     | 3                   | μs    |

| t <sub>CONV</sub>    | Conversion time (latency) | No S/H enabled, internal DAC |     |     | 1                   | μs    |

|                      |                           | One S/H                      |     |     | 1.5                 | μs    |

|                      |                           | Two S/H                      |     |     | 2                   | μs    |

|                      | Throughput rate           |                              |     |     | 1/t <sub>CONV</sub> | MSPS  |

### Table 7-38. External Voltage Reference Input

| Symbol  | Parameter                  | Conditions | Min | Тур | Мах                      | Units |

|---------|----------------------------|------------|-----|-----|--------------------------|-------|

| VDACREF | DACREF input voltage range |            | 1.2 |     | V <sub>VDDANA</sub> -0.7 | V     |

### Table 7-39. DAC Outputs

| Symbol            | Parameter          | Conditions                  | Min | Тур | Max                      | Units |  |

|-------------------|--------------------|-----------------------------|-----|-----|--------------------------|-------|--|

|                   | Output range       | with external DAC reference | 0.2 |     | VDACREF                  | V     |  |

|                   | Oulput lange       | with internal DAC reference | 0.2 |     | V <sub>VDDANA</sub> -0.7 |       |  |

| C <sub>LOAD</sub> | Output capacitance |                             | 0   |     | 100                      | pF    |  |

| R <sub>LOAD</sub> | Output resitance   |                             | 2   |     |                          | kΩ    |  |

### 7.9 Timing Characteristics

### 7.9.1 Startup, Reset, and Wake-up Timing

The startup, reset, and wake-up timings are calculated using the following formula:

$$t = t_{CONST} + N_{CPU} \times t_{CPU}$$

Where  $t_{CONST}$  and  $N_{CPU}$  are found in Table 7-44.  $t_{CONST}$  is the delay relative to RCSYS,  $t_{CPU}$  is the period of the CPU clock. If another clock source than RCSYS is selected as CPU clock the startup time of the oscillator,  $t_{OSCSTART}$ , must be added to the wake-up time in the stop, deepstop, and static sleep modes. Please refer to the source for the CPU clock in the "Oscillator Characteristics" on page 57 for more details about oscillator startup times.

Table 7-44. Maximum Reset and Wake-up Timing

| Parameter                                   |                   | Measuring                                                                                                                                                               | Max <i>t<sub>CONST</sub></i> (in µs) | ${\rm Max}\; N_{CPU}$ |

|---------------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-----------------------|

| Startup time from power-up, using regulator |                   | VDDIN_5 rising (10 mV/ms)<br>Time from $V_{VDDIN_5}$ =0 to the first instruction entering<br>the decode stage of CPU. VDDCORE is supplied by<br>the internal regulator. | 2600                                 | 0                     |

| Startup time fr                             | rom reset release | Time from releasing a reset source (except POR,<br>BOD18, and BOD33) to the first instruction entering<br>the decode stage of CPU.1240                                  |                                      | 0                     |

|                                             | Idle              |                                                                                                                                                                         | 0                                    | 19                    |

|                                             | Frozen            |                                                                                                                                                                         | 268                                  | 209                   |

|                                             | Standby           | From wake-up event to the first instruction entering                                                                                                                    | 268                                  | 209                   |

| Wake-up                                     | Stop              | the decode stage of the CPU.                                                                                                                                            | 268+ t <sub>OSCSTART</sub>           | 212                   |

|                                             | Deepstop          |                                                                                                                                                                         | 268+ t <sub>OSCSTART</sub>           | 212                   |

|                                             | Static            |                                                                                                                                                                         | 268+ t <sub>OSCSTART</sub>           | 212                   |

AT32UC3C

Figure 7-5. Startup and Reset Time

### 7.9.2 RESET\_N characteristics

| Symbol             | Parameter                    | Condition | Min.                   | Тур. | Max. | Units        |

|--------------------|------------------------------|-----------|------------------------|------|------|--------------|

| t <sub>RESET</sub> | RESET_N minimum pulse length |           | 2 * T <sub>RCSYS</sub> |      |      | clock cycles |

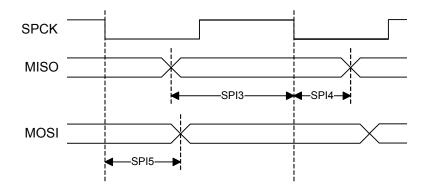

Figure 7-12. SPI Master Mode With (CPOL= 0 and NCPHA= 1) or (CPOL= 1 and NCPHA= 0)

### Table 7-48. SPI Timing, Master Mode<sup>(1)</sup>

| Symbol | Parameter                         | Conditions          | Min                              | Мах  | Units |

|--------|-----------------------------------|---------------------|----------------------------------|------|-------|

| SPI0   | MISO setup time before SPCK rises |                     | 28.5+ (t <sub>CLK_SPI</sub> )/2  |      | ns    |

| SPI1   | MISO hold time after SPCK rises   |                     | 0                                |      | ns    |

| SPI2   | SPCK rising to MOSI delay         | external            |                                  | 10.5 | ns    |

| SPI3   | MISO setup time before SPCK falls | capacitor =<br>40pF | 28.5 + (t <sub>CLK_SPI</sub> )/2 |      | ns    |

| SPI4   | MISO hold time after SPCK falls   |                     | 0                                |      | ns    |

| SPI5   | SPCK falling to MOSI delay        |                     |                                  | 10.5 | ns    |

Note: 1. These values are based on simulation and characterization of other AVR microcontrollers manufactured in the same process technology. These values are not covered by test limits in production.

### Maximum SPI Frequency, Master Output

The maximum SPI master output frequency is given by the following formula:

$$f_{SPCKMAX} = MIN(f_{PINMAX}, \frac{1}{SPIn})$$

Where *SPIn* is the MOSI delay, SPI2 or SPI5 depending on CPOL and NCPHA.  $f_{PINMAX}$  is the maximum frequency of the SPI pins. Please refer to the I/O Pin Characteristics section for the maximum frequency of the pins.

### Maximum SPI Frequency, Master Input

The maximum SPI master input frequency is given by the following formula:

$$f_{SPCKMAX} = \frac{1}{SPIn + t_{VALID}}$$

Where *SPIn* is the MISO setup and hold time, SPI0 + SPI1 or SPI3 + SPI4 depending on CPOL and NCPHA.  $t_{VALID}$  is the SPI slave response time. Please refer to the SPI slave datasheet for  $t_{VALID}$ .

TWIM and TWIS user interface registers. Please refer to the TWIM and TWIS sections for more information.

Table 7-50. **TWI-Bus Timing Requirements**

|                         |                              |                         | Minimum                                    |                     | Maxir       | num                  |       |  |

|-------------------------|------------------------------|-------------------------|--------------------------------------------|---------------------|-------------|----------------------|-------|--|

| Symbol                  | Parameter                    | Mode                    | Requirement                                | Device              | Requirement | Device               | Unit  |  |

|                         | TWOK and TWD rise time       | Standard <sup>(1)</sup> | -                                          |                     | 1000        |                      | 20    |  |

| t <sub>r</sub>          | TWCK and TWD rise time       | Fast <sup>(1)</sup>     | 20 + 0                                     | .1 C <sub>b</sub>   | 30          | 0                    | ns    |  |

|                         |                              | Standard <sup>(1)</sup> | -                                          |                     | 300         |                      |       |  |

| t <sub>f</sub>          | TWCK and TWD fall time       | Fast <sup>(1)</sup>     | 20 + 0                                     | .1 C <sub>b</sub>   | 30          | 0                    | ns    |  |

|                         |                              | Standard <sup>(1)</sup> | 4.0                                        | 4                   |             |                      |       |  |

| t <sub>HD-STA</sub>     | (Repeated) START hold time   | Fast <sup>(1)</sup>     | 0.6                                        | t <sub>clkpb</sub>  | -           | μs                   |       |  |

|                         |                              | Standard <sup>(1)</sup> | 4.7                                        |                     |             |                      |       |  |

| t <sub>SU-STA</sub>     | (Repeated) START set-up time | Fast <sup>(1)</sup>     | 0.6                                        | t <sub>clkpb</sub>  | -           |                      | μS    |  |

| t <sub>SU-STO</sub>     | STOP set-up time             | Standard <sup>(1)</sup> | 4.0                                        |                     | -           |                      | μs    |  |

|                         |                              | Fast <sup>(1)</sup>     | 0.6                                        | 4t <sub>clkpb</sub> |             |                      |       |  |

|                         | Data hold time               | Standard <sup>(1)</sup> | - 0.3 <sup>(2)</sup> 2t <sub>clkpb</sub> - | 01                  | 3.45        | 22                   |       |  |

| t <sub>HD-DAT</sub>     |                              | Fast <sup>(1)</sup>     |                                            | 0.9                 | ??          | μS                   |       |  |

|                         | Data act un time             | Standard <sup>(1)</sup> | 250                                        | 01                  | -           |                      | ns    |  |

| t <sub>SU-DAT-I2C</sub> | Data set-up time             | Fast <sup>(1)</sup>     | 100                                        | 2t <sub>clkpb</sub> |             |                      |       |  |

| t <sub>SU-DAT</sub>     |                              | -                       | -                                          | t <sub>clkpb</sub>  | -           |                      | -     |  |

|                         | TWOK LOW period              | Standard <sup>(1)</sup> | 4.7                                        | 44                  |             |                      |       |  |

| t <sub>LOW-I2C</sub>    | TWCK LOW period              | Fast <sup>(1)</sup>     | 1.3                                        | 4t <sub>clkpb</sub> | -           |                      | μs    |  |

| t <sub>LOW</sub>        |                              | -                       | -                                          | t <sub>clkpb</sub>  | -           |                      | -     |  |

|                         | TWCK LICH paried             | Standard <sup>(1)</sup> | 4.0                                        |                     | -           |                      |       |  |

| t <sub>HIGH</sub>       | TWCK HIGH period             | Fast <sup>(1)</sup>     | 0.6                                        | 8t <sub>clkpb</sub> |             |                      | μS    |  |

| £                       |                              | Standard <sup>(1)</sup> |                                            | 1                   | 100         | 1                    | ld le |  |

| f <sub>TWCK</sub>       | TWCK frequency               | Fast <sup>(1)</sup>     | -                                          |                     | 400         | <sup>12t</sup> clkpb | kHz   |  |

Notes: 1. Standard mode:  $f_{TWCK} \le 100 \text{ kHz}$ ; fast mode:  $f_{TWCK} > 100 \text{ kHz}$ . 2. A device must internally provide a hold time of at least 300 ns for TWD with reference to the falling edge of TWCK.

Notations:

C<sub>b</sub> = total capacitance of one bus line in pF

$t_{clkpb}$  = period of TWI peripheral bus clock

$t_{prescaled}$  = period of TWI internal prescaled clock (see chapters on TWIM and TWIS)

The maximum  $t_{HD;DAT}$  has only to be met if the device does not stretch the LOW period ( $t_{LOW-I2C}$ ) of TWCK.

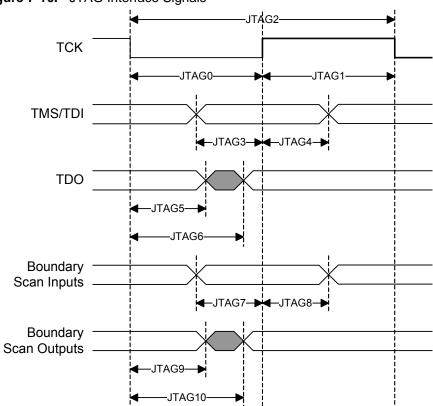

### 7.9.6 JTAG Timing

Figure 7-16. JTAG Interface Signals

| Table 7 | 7-51. | JTAG | Timings <sup>(1)</sup> |

|---------|-------|------|------------------------|

|---------|-------|------|------------------------|

| Symbol | Parameter                          | Conditions  | Min  | Max  | Units |

|--------|------------------------------------|-------------|------|------|-------|

| JTAG0  | TCK Low Half-period                |             | 21.5 |      | ns    |

| JTAG1  | TCK High Half-period               |             | 8.5  |      | ns    |

| JTAG2  | TCK Period                         |             | 29   |      | ns    |

| JTAG3  | TDI, TMS Setup before TCK High     |             | 6.5  |      | ns    |

| JTAG4  | TDI, TMS Hold after TCK High       | external    | 0    |      | ns    |

| JTAG5  | TDO Hold Time                      | capacitor = | 12.5 |      | ns    |

| JTAG6  | TCK Low to TDO Valid               | 40pF        |      | 21.5 | ns    |

| JTAG7  | Boundary Scan Inputs Setup Time    |             | 0    |      | ns    |

| JTAG8  | Boundary Scan Inputs Hold Time     |             | 4.5  |      | ns    |

| JTAG9  | Boundary Scan Outputs Hold Time    |             | 11   |      | ns    |

| JTAG10 | TCK to Boundary Scan Outputs Valid |             |      | 18   | ns    |

Note: 1. These values are based on simulation and characterization of other AVR microcontrollers manufactured in the same process technology. These values are not covered by test limits in production.

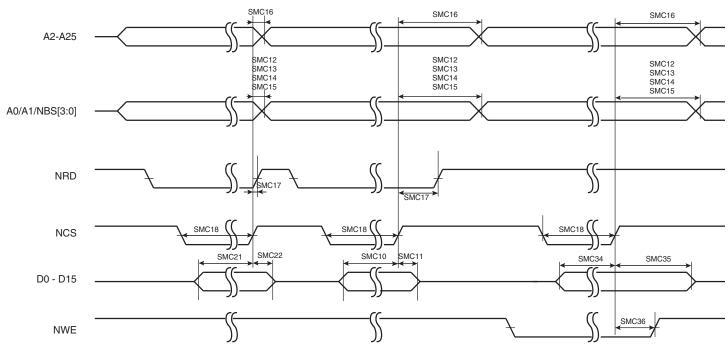

| Symbol            | Parameter                        | Conditions                                                                   | Min                                   | Units |

|-------------------|----------------------------------|------------------------------------------------------------------------------|---------------------------------------|-------|

| SMC <sub>37</sub> | NWE rising to A2-A25 valid       |                                                                              | 8.7                                   |       |

| SMC <sub>38</sub> | NWE rising to NBS0/A0 valid      | V <sub>VDD</sub> = 3.0V,<br>drive strength of the pads<br>set to the lowest, | 7.6                                   |       |

| SMC <sub>40</sub> | NWE rising to A1/NBS2 change     |                                                                              | 8.7                                   |       |

| SMC <sub>42</sub> | NWE rising to NCS rising         |                                                                              | 8.4                                   | ns    |

| SMC <sub>43</sub> | Data Out valid before NWE rising | external capacitor = 40pF                                                    | (nwe pulse length - 1) * tcpsмc - 1.2 |       |

| SMC <sub>44</sub> | Data Out valid after NWE rising  |                                                                              | 8.4                                   |       |

| SMC <sub>45</sub> | NWE pulse width                  |                                                                              | nwe pulse length * tcpsmc - 0         |       |

Table 7-56.

SMC Write Signals with No Hold Settings (NWE Controlled only)<sup>(1)</sup>

Note: 1. These values are based on simulation and characterization of other AVR microcontrollers manufactured in the same process technology. These values are not covered by test limits in production.

Figure 7-17. SMC Signals for NCS Controlled Accesses

### 10.2.10 TWIS

10.2.11 USBC

### 1 Clearing the NAK bit before the BTF bit is set locks up the TWI bus

When the TWIS is in transmit mode, clearing the NAK Received (NAK) bit of the Status Register (SR) before the end of the Acknowledge/Not Acknowledge cycle will cause the TWIS to attempt to continue transmitting data, thus locking up the bus. **Fix/Workaround**

Clear SR.NAK only after the Byte Transfer Finished (BTF) bit of the same register has been set.

### 2 TWIS stretch on Address match error

When the TWIS stretches TWCK due to a slave address match, it also holds TWD low for the same duration if it is to be receiving data. When TWIS releases TWCK, it releases TWD at the same time. This can cause a TWI timing violation. **Fix/Workaround**

None.

### 3 TWALM forced to GND

The TWALM pin is forced to GND when the alternate function is selected and the TWIS module is enabled.

### Fix/Workaround

None.

### 1 UPINRQx.INRQ field is limited to 8-bits

In Host mode, when using the UPINRQx.INRQ feature together with the multi-packet mode to launch a finite number of packet among multi-packet, the multi-packet size (located in the descriptor table) is limited to the UPINRQx.INRQ value multiply by the pipe size. **Fix/Workaround**

UPINRQx.INRQ value shall be less than the number of configured multi-packet.

2 In USB host mode, downstream resume feature does not work (UHCON.RESUME=1). Fix/Workaround

None.

3 In host mode, the disconnection during OUT transition is not supported In USB host mode, a pipe can not work if the previous USB device disconnection has occurred during a USB transfer. Fix/Workaround

Reset the USBC (USBCON.USB=0 and =1) after a device disconnection (UHINT.DDISCI).

### 4 In USB host mode, entering suspend mode can fail

In USB host mode, entering suspend mode can fail when UHCON.SOFE=0 is done just after a SOF reception (UHINT.HSOFI).

### Fix/Workaround

Check that UHNUM.FLENHIGH is below 185 in Full speed and below 21 in Low speed before clearing UHCON.SOFE.

5 In USB host mode, entering suspend mode for low speed device can fail when the USB freeze (USBCON.FRZCLK=1) is done just after UHCON.SOFE=0. Fix/Workaround

When entering suspend mode (UHCON.SOFE is cleared), check that USBFSM.DRDSTATE is not equal to three before freezing the clock (USBCON.FRZCLK=1).

#### Headquarters

Atmel Corporation 2325 Orchard Parkway San Jose, CA 95131 USA Tel: 1(408) 441-0311 Fax: 1(408) 487-2600

### International

Atmel Asia Unit 1-5 & 16, 19/F BEA Tower, Millennium City 5 418 Kwun Tong Road Kwun Tong, Kowloon Hong Kong Tel: (852) 2245-6100 Fax: (852) 2722-1369 Atmel Europe Le Krebs 8, Rue Jean-Pierre Timbaud BP 309 78054 Saint-Quentin-en-Yvelines Cedex France Tel: (33) 1-30-60-70-00 Fax: (33) 1-30-60-71-11

#### Atmel Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan Tel: (81) 3-3523-3551 Fax: (81) 3-3523-7581

#### **Product Contact**

Web Site www.atmel.com Technical Support avr32@atmel.com Sales Contact www.atmel.com/contacts

Literature Requests www.atmel.com/literature

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL'S TERMS AND CONDI-TIONS OF SALE LOCATED ON ATMEL'S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDEN-TAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel's products are not intended, or warranted for use as components in applications intended to support or sustain life.

© 2012 Atmel Corporation. All rights reserved. Atmel<sup>®</sup>, Atmel logo and combinations thereof, AVR<sup>®</sup> and others are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.