#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | AVR                                                                         |

| Core Size                  | 32-Bit Single-Core                                                          |

| Speed                      | 66MHz                                                                       |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB      |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                |

| Number of I/O              | 81                                                                          |

| Program Memory Size        | 512KB (512K x 8)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 64K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                   |

| Data Converters            | A/D 16x12b; D/A 4x12b                                                       |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 100-TQFP                                                                    |

| Supplier Device Package    | 100-TQFP (14x14)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at32uc3c1512c-aur |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The Full-Speed USB 2.0 Device interface supports several USB Classes at the same time thanks to the rich End-Point configuration. The On-The-GO (OTG) Host interface allows device like a USB Flash disk or a USB printer to be directly connected to the processor.

The media-independent interface (MII) and reduced MII (RMII) 10/100 Ethernet MAC module provides on-chip solutions for network-connected devices.

The Peripheral Event Controller (PEVC) allows to redirect events from one peripheral or from input pins to another peripheral. It can then trigger, in a deterministic time, an action inside a peripheral without the need of CPU. For instance a PWM waveform can directly trigger an ADC capture, hence avoiding delays due to software interrupt processing.

The AT32UC3C features analog functions like ADC, DAC, Analog comparators. The ADC interface is built around a 12-bit pipelined ADC core and is able to control two independent 8-channel or one 16-channel. The ADC block is able to measure two different voltages sampled at the same time. The analog comparators can be paired to detect when the sensing voltage is within or outside the defined reference window.

Atmel offers the QTouch library for embedding capacitive touch buttons, sliders, and wheels functionality into AVR microcontrollers. The patented charge-transfer signal acquisition offers robust sensing and included fully debounced reporting of touch keys and includes Adjacent Key Suppression<sup>®</sup> (AKS<sup>®</sup>) technology for unambiguous detection of key events. The easy-to-use QTouch Suite toolchain allows you to explore, develop, and debug your own touch applications.

AT32UC3C integrates a class 2+ Nexus 2.0 On-Chip Debug (OCD) System, with non-intrusive real-time trace, full-speed read/write memory access in addition to basic runtime control. The Nanotrace interface enables trace feature for aWire- or JTAG-based debuggers. The single-pin aWire interface allows all features available through the JTAG interface to be accessed through the RESET pin, allowing the JTAG pins to be used for GPIO or peripherals.

# 2. Overview

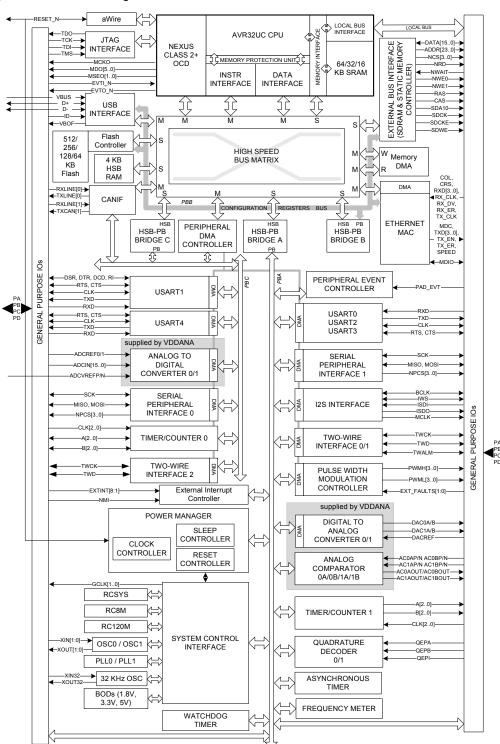

# 2.1 Block diagram

### Figure 2-1. Block diagram

Table 3-1.

GPIO Controller Function Multiplexing

| TQFP           |             |             |      | G   |        |                    | -               |                   | GPIO fu                    | unction            |                      |   |

|----------------|-------------|-------------|------|-----|--------|--------------------|-----------------|-------------------|----------------------------|--------------------|----------------------|---|

| /<br>QFN<br>64 | TQFP<br>100 | LQFP<br>144 | PIN  | ΡΙΟ | Supply | Pin<br>Type<br>(1) | А               | в                 | с                          | D                  | E                    | F |

|                |             | 14          | PB11 | 43  | VDDIO1 | x1/x2              | USART1 -<br>DSR | SPI0 -<br>MISO    | PWM -<br>PWMH[1]           |                    |                      |   |

|                |             | 15          | PB12 | 44  | VDDIO1 | x1/x2              | USART1 -<br>DCD | SPI0 -<br>SCK     | PWM -<br>PWML[2]           |                    |                      |   |

|                |             | 16          | PB13 | 45  | VDDIO1 | x1/x2              | USART1 -<br>RI  | SPI0 -<br>NPCS[0] | PWM -<br>PWMH[2]           |                    | MACB -<br>RX_ER      |   |

|                |             | 17          | PB14 | 46  | VDDIO1 | x1/x2              | USART1 -<br>RTS | SPI0 -<br>NPCS[1] | PWM -<br>PWML[3]           |                    | MACB -<br>MDC        |   |

|                |             | 18          | PB15 | 47  | VDDIO1 | x1/x2              | USART1 -<br>CTS | USART1 -<br>CLK   | PWM -<br>PWMH[3]           |                    | MACB -<br>MDIO       |   |

|                |             | 19          | PB16 | 48  | VDDIO1 | x1/x2              | USART1 -<br>RXD | SPI0 -<br>NPCS[2] | PWM -<br>EXT_<br>FAULTS[0] |                    | CANIF -<br>RXLINE[0] |   |

|                |             | 20          | PB17 | 49  | VDDIO1 | x1/x2              | USART1 -<br>TXD | SPIO -<br>NPCS[3] | PWM -<br>EXT_<br>FAULTS[1] |                    | CANIF -<br>TXLINE[0] |   |

|                |             | 57          | PB18 | 50  | VDDIO2 | x1/x2              | TC0 -<br>CLK2   |                   | EIC -<br>EXTINT[4]         |                    |                      |   |

|                | 42          | 58          | PB19 | 51  | VDDIO2 | x1/x2              | TC0 - A0        | SPI1 -<br>MOSI    | IISC -<br>ISDO             |                    | MACB -<br>CRS        |   |

|                | 43          | 59          | PB20 | 52  | VDDIO2 | x1/x2              | TC0 - B0        | SPI1 -<br>MISO    | IISC - ISDI                | ACIFA1 -<br>ACAOUT | MACB -<br>COL        |   |

|                | 44          | 60          | PB21 | 53  | VDDIO2 | x2/x4              | TC0 -<br>CLK1   | SPI1 -<br>SCK     | IISC -<br>IMCK             | ACIFA1 -<br>ACBOUT | MACB -<br>RXD[2]     |   |

|                | 45          | 61          | PB22 | 54  | VDDIO2 | x1/x2              | TC0 - A1        | SPI1 -<br>NPCS[3] | IISC -<br>ISCK             | SCIF -<br>GCLK[0]  | MACB -<br>RXD[3]     |   |

|                | 46          | 62          | PB23 | 55  | VDDIO2 | x1/x2              | TC0 - B1        | SPI1 -<br>NPCS[2] | IISC - IWS                 | SCIF -<br>GCLK[1]  | MACB -<br>RX_CLK     |   |

|                |             | 63          | PB24 | 56  | VDDIO2 | x1/x2              | TC0 -<br>CLK0   | SPI1 -<br>NPCS[1] |                            |                    |                      |   |

|                |             | 64          | PB25 | 57  | VDDIO2 | x1/x2              | TC0 - A2        | SPI1 -<br>NPCS[0] | PEVC -<br>PAD_EVT<br>[8]   |                    |                      |   |

|                |             | 65          | PB26 | 58  | VDDIO2 | x2/x4              | TC0 - B2        | SPI1 -<br>SCK     | PEVC -<br>PAD_EVT<br>[9]   |                    | MACB -<br>TX_EN      |   |

|                |             | 66          | PB27 | 59  | VDDIO2 | x1/x2              | QDEC0 -<br>QEPA | SPI1 -<br>MISO    | PEVC -<br>PAD_EVT<br>[10]  | TC1 -<br>CLK0      | MACB -<br>TXD[0]     |   |

|                |             | 67          | PB28 | 60  | VDDIO2 | x1/x2              | QDEC0 -<br>QEPB | SPI1 -<br>MOSI    | PEVC -<br>PAD_EVT<br>[11]  | TC1 - B0           | MACB -<br>TXD[1]     |   |

|                |             | 68          | PB29 | 61  | VDDIO2 | x1/x2              | QDEC0 -<br>QEPI | SPI0 -<br>NPCS[0] | PEVC -<br>PAD_EVT<br>[12]  | TC1 - A0           |                      |   |

| 31             | 47          | 69          | PB30 | 62  | VDDIO2 | x1                 |                 |                   |                            |                    |                      |   |

| 32             | 48          | 70          | PB31 | 63  | VDDIO2 | x1                 |                 |                   |                            |                    |                      |   |

|                | 49          | 71          | PC00 | 64  | VDDIO2 | x1/x2              | USBC - ID       | SPI0 -<br>NPCS[1] | USART2 -<br>CTS            | TC1 - B2           | CANIF -<br>TXLINE[1] |   |

|                | 50          | 72          | PC01 | 65  | VDDIO2 | x1/x2              | USBC -<br>VBOF  | SPI0 -<br>NPCS[2] | USART2 -<br>RTS            | TC1 - A2           | CANIF -<br>RXLINE[1] |   |

### Table 3-2.Peripheral Functions

| Function              | Description                  |

|-----------------------|------------------------------|

| aWire DATAOUT         | aWire output in two-pin mode |

| JTAG port connections | JTAG debug port              |

| Oscillators           | OSC0, OSC32                  |

#### 3.2.3 Oscillator Pinout

The oscillators are not mapped to the normal GPIO functions and their muxings are controlled by registers in the System Control Interface (SCIF). Please refer to the SCIF chapter for more information about this.

| Table 3-3. | Oscillator pinout |

|------------|-------------------|

|------------|-------------------|

| QFN64/<br>TQFP64 pin | TQFP100 pin | LQFP144 pin | Pad  | Oscillator pin |

|----------------------|-------------|-------------|------|----------------|

| 31                   | 47          | 69          | PB30 | xin0           |

|                      | 99          | 143         | PB02 | xin1           |

| 62                   | 96          | 140         | PB00 | xin32          |

| 32                   | 48          | 70          | PB31 | xout0          |

|                      | 100         | 144         | PB03 | xout1          |

| 63                   | 97          | 141         | PB01 | xout32         |

### 3.2.4 JTAG port connections

If the JTAG is enabled, the JTAG will take control over a number of pins, irrespectively of the I/O Controller configuration.

| QFN64/<br>TQFP64 pin | TQFP100 pin | LQFP144 pin | Pin name | JTAG pin |

|----------------------|-------------|-------------|----------|----------|

| 2                    | 2           | 2           | PA01     | TDI      |

| 3                    | 3           | 3           | PA02     | TDO      |

| 4                    | 4           | 4           | PA03     | TMS      |

| 1                    | 1           | 1           | PA00     | тск      |

### 3.2.5 Nexus OCD AUX port connections

If the OCD trace system is enabled, the trace system will take control over a number of pins, irrespectively of the GPIO configuration. Three different OCD trace pin mappings are possible,

# Table 3-7.Signal Description List

| Signal Name                | Function                                                  | Туре                      | Active<br>Level | Comments                                                                                    |

|----------------------------|-----------------------------------------------------------|---------------------------|-----------------|---------------------------------------------------------------------------------------------|

| VDDIN_5                    | 1.8V Voltage Regulator Input                              | Power<br>Input            |                 | Power Supply:<br>4.5V to 5.5V<br>or<br>3.0V to 3.6 V                                        |

| VDDIN_33                   | USB I/O power supply                                      | Power<br>Output/<br>Input |                 | Capacitor Connection for the 3.3V<br>voltage regulator<br>or power supply:<br>3.0V to 3.6 V |

| VDDCORE                    | 1.8V Voltage Regulator Output                             | Power<br>output           |                 | Capacitor Connection for the 1.8V voltage regulator                                         |

| GNDIO1<br>GNDIO2<br>GNDIO3 | I/O Ground                                                | Ground                    |                 |                                                                                             |

| GNDANA                     | Analog Ground                                             | Ground                    |                 |                                                                                             |

| GNDCORE                    | Ground of the core                                        | Ground                    |                 |                                                                                             |

| GNDPLL                     | Ground of the PLLs                                        | Ground                    |                 |                                                                                             |

|                            | Analog Comparator Interfa                                 | ace - ACIFA               | 0/1             | 1                                                                                           |

| AC0AN1/AC0AN0              | Negative inputs for comparator AC0A                       | Analog                    |                 |                                                                                             |

| AC0AP1/AC0AP0              | Positive inputs for comparator AC0A                       | Analog                    |                 |                                                                                             |

| AC0BN1/AC0BN0              | Negative inputs for comparator AC0B                       | Analog                    |                 |                                                                                             |

| AC0BP1/AC0BP0              | Positive inputs for comparator AC0B                       | Analog                    |                 |                                                                                             |

| AC1AN1/AC1AN0              | Negative inputs for comparator AC1A                       | Analog                    |                 |                                                                                             |

| AC1AP1/AC1AP0              | Positive inputs for comparator AC1A                       | Analog                    |                 |                                                                                             |

| AC1BN1/AC1BN0              | Negative inputs for comparator AC1B                       | Analog                    |                 |                                                                                             |

| AC1BP1/AC1BP0              | Positive inputs for comparator AC1B                       | Analog                    |                 |                                                                                             |

| ACAOUT/ACBOUT              | analog comparator outputs                                 | output                    |                 |                                                                                             |

|                            | ADC Interface - A                                         | DCIFA                     |                 |                                                                                             |

| ADCIN[15:0]                | ADC input pins                                            | Analog                    |                 |                                                                                             |

| ADCREF0                    | Analog positive reference 0 voltage input                 | Analog                    |                 |                                                                                             |

| ADCREF1                    | Analog positive reference 1 voltage input                 | Analog                    |                 |                                                                                             |

| ADCVREFP                   | Analog positive reference connected to external capacitor | Analog                    |                 |                                                                                             |

than the oldest instruction. An instruction B is younger than an instruction A if it was sent down the pipeline later than A.

The addresses and priority of simultaneous events are shown in Table 4-4 on page 38. Some of the exceptions are unused in AVR32UC since it has no MMU, coprocessor interface, or floating-point unit.

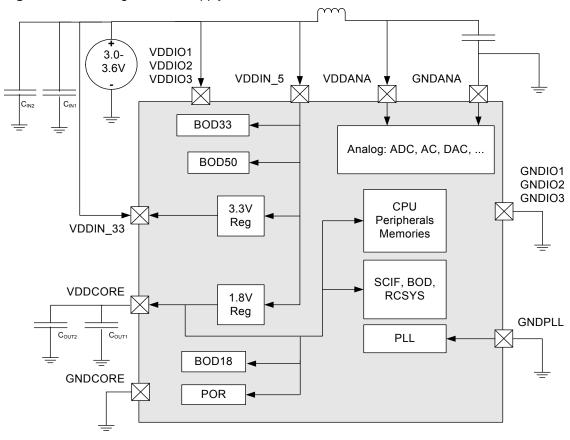

Figure 6-2. 3 Single Power Supply Mode

### 6.1.4 Power-up Sequence

#### 6.1.4.1 Maximum Rise Rate

To avoid risk of latch-up, the rise rate of the power supplies must not exceed the values described in Table 7-2 on page 51.

Recommended order for power supplies is also described in this table.

#### 6.1.4.2 Minimum Rise Rate

The integrated Power-Reset circuitry monitoring the powering supply requires a minimum rise rate for the VDDIN\_5 power supply.

See Table 7-2 on page 51 for the minimum rise rate value.

If the application can not ensure that the minimum rise rate condition for the VDDIN power supply is met, the following configuration can be used:

- A logic "0" value is applied during power-up on pin RESET\_N until:

- VDDIN\_5 rises above 4.5V in 5V single supply mode.

- VDDIN\_33 rises above 3V in 3.3V single supply mode.

**Table 7-8.**Crystal Oscillator Characteristics

| Symbol               | Parameter                            | Conditions                                                       | Min | Тур  | Max | Unit |

|----------------------|--------------------------------------|------------------------------------------------------------------|-----|------|-----|------|

| f <sub>OUT</sub>     | Crystal oscillator frequency         |                                                                  | 0.4 |      | 20  | MHz  |

| C <sub>i</sub>       | Internal equivalent load capacitance |                                                                  |     | 1.7  |     | pF   |

| t <sub>STARTUP</sub> |                                      | f <sub>OUT</sub> = 8MHz<br>SCIF.OSCCTRL.GAIN = 1 <sup>(1)</sup>  |     | 975  |     | us   |

|                      | Startup time                         | f <sub>OUT</sub> = 16MHz<br>SCIF.OSCCTRL.GAIN = 2 <sup>(1)</sup> |     | 1100 |     | us   |

Notes: 1. Please refer to the SCIF chapter for details.

### 7.6.2 32KHz Crystal Oscillator (OSC32K) Characteristics

7.6.2.1 Digital Clock Characteristics

The following table describes the characteristics for the oscillator when a digital clock is applied on XIN32.

### Table 7-9. Digital 32KHz Clock Characteristics

| Symbol             | Parameter                   | Conditions | Min                      | Тур    | Max                      | Units |

|--------------------|-----------------------------|------------|--------------------------|--------|--------------------------|-------|

| f <sub>CPXIN</sub> | XIN32 clock frequency       |            |                          | 32.768 | 5000                     | KHz   |

| t <sub>CPXIN</sub> | XIN32 clock period          |            | 200                      |        |                          | ns    |

| t <sub>CHXIN</sub> | XIN32 clock high half-priod |            | 0.4 x t <sub>CPXIN</sub> |        | 0.6 x t <sub>CPXIN</sub> | ns    |

| t <sub>CLXIN</sub> | XIN32 clock low half-priod  |            | 0.4 x t <sub>CPXIN</sub> |        | 0.6 x t <sub>CPXIN</sub> | ns    |

| C <sub>IN</sub>    | XIN32 input capacitance     |            |                          | 2      |                          | pF    |

7.6.2.2 Crystal Oscillator Characteristics

Figure 7-2 and the equation above also applies to the 32KHz oscillator connection. The user must choose a crystal oscillator where the crystal load capacitance  $C_L$  is within the range given in the table. The exact value of  $C_L$  can then be found in the crystal datasheet.

Table 7-10.

32 KHz Crystal Oscillator Characteristics

| Symbol               | Parameter                            | Conditions                                        | Min | Тур    | Max | Unit |

|----------------------|--------------------------------------|---------------------------------------------------|-----|--------|-----|------|

| f <sub>OUT</sub>     | Crystal oscillator frequency         |                                                   |     | 32 768 |     | Hz   |

| t <sub>STARTUP</sub> | Startup time                         | $R_{S} = 50 \text{ kOhm}, C_{L} = 12.5 \text{pF}$ |     | 2      |     | S    |

| CL                   | Crystal load capacitance             |                                                   | 6   |        | 15  | pF   |

| C <sub>i</sub>       | Internal equivalent load capacitance |                                                   |     | 1.4    |     | pF   |

# 7.9 Timing Characteristics

### 7.9.1 Startup, Reset, and Wake-up Timing

The startup, reset, and wake-up timings are calculated using the following formula:

$$t = t_{CONST} + N_{CPU} \times t_{CPU}$$

Where  $t_{CONST}$  and  $N_{CPU}$  are found in Table 7-44.  $t_{CONST}$  is the delay relative to RCSYS,  $t_{CPU}$  is the period of the CPU clock. If another clock source than RCSYS is selected as CPU clock the startup time of the oscillator,  $t_{OSCSTART}$ , must be added to the wake-up time in the stop, deepstop, and static sleep modes. Please refer to the source for the CPU clock in the "Oscillator Characteristics" on page 57 for more details about oscillator startup times.

Table 7-44. Maximum Reset and Wake-up Timing

| Parameter                                   |          | Measuring                                                                                                                                                               | Max <i>t<sub>CONST</sub></i> (in µs) | Max N <sub>CPU</sub> |

|---------------------------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|----------------------|

| Startup time from power-up, using regulator |          | VDDIN_5 rising (10 mV/ms)<br>Time from $V_{VDDIN_5}$ =0 to the first instruction entering<br>the decode stage of CPU. VDDCORE is supplied by<br>the internal regulator. | 2600                                 | 0                    |

| Startup time from reset release             |          | Time from releasing a reset source (except POR,<br>BOD18, and BOD33) to the first instruction entering<br>the decode stage of CPU.                                      | 1240                                 | 0                    |

|                                             | Idle     |                                                                                                                                                                         | 0                                    | 19                   |

|                                             | Frozen   |                                                                                                                                                                         | 268                                  | 209                  |

|                                             | Standby  | From wake-up event to the first instruction entering                                                                                                                    | 268                                  | 209                  |

| Wake-up                                     | Stop     | the decode stage of the CPU.                                                                                                                                            | 268+ t <sub>OSCSTART</sub>           | 212                  |

|                                             | Deepstop |                                                                                                                                                                         | 268+ t <sub>OSCSTART</sub>           | 212                  |

|                                             | Static   |                                                                                                                                                                         | 268+ t <sub>OSCSTART</sub>           | 212                  |

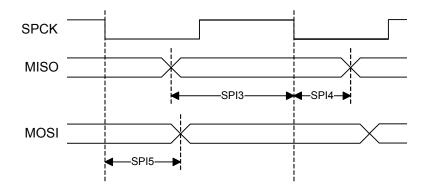

### Maximum SPI Frequency, Master Output

The maximum SPI master output frequency is given by the following formula:

$$f_{SPCKMAX} = MIN(f_{PINMAX}, \frac{1}{SPIn}, \frac{f_{CLKSPI} \times 2}{9})$$

Where *SPIn* is the MOSI delay, USPI2 or USPI5 depending on CPOL and NCPHA.  $f_{PINMAX}$  is the maximum frequency of the SPI pins. Please refer to the I/O Pin Characteristics section for the maximum frequency of the pins.  $f_{CLKSPI}$  is the maximum frequency of the CLK\_SPI. Refer to the SPI chapter for a description of this clock.

### Maximum SPI Frequency, Master Input

The maximum SPI master input frequency is given by the following formula:

$$f_{SPCKMAX} = MIN(\frac{1}{SPIn + t_{VALID}}, \frac{f_{CLKSPI} \times 2}{9})$$

Where *SPIn* is the MISO setup and hold time, USPI0 + USPI1 or USPI3 + USPI4 depending on CPOL and NCPHA.  $T_{VALID}$  is the SPI slave response time. Please refer to the SPI slave datasheet for  $T_{VALID}$ .  $f_{CLKSPI}$  is the maximum frequency of the CLK\_SPI. Refer to the SPI chapter for a description of this clock.

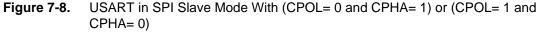

7.9.3.2 Slave mode

Figure 7-12. SPI Master Mode With (CPOL= 0 and NCPHA= 1) or (CPOL= 1 and NCPHA= 0)

### Table 7-48. SPI Timing, Master Mode<sup>(1)</sup>

| Symbol | Parameter                         | Conditions          | Min                              | Max  | Units |

|--------|-----------------------------------|---------------------|----------------------------------|------|-------|

| SPI0   | MISO setup time before SPCK rises |                     | 28.5+ (t <sub>CLK_SPI</sub> )/2  |      | ns    |

| SPI1   | MISO hold time after SPCK rises   |                     | 0                                |      | ns    |

| SPI2   | SPCK rising to MOSI delay         | external            |                                  | 10.5 | ns    |

| SPI3   | MISO setup time before SPCK falls | capacitor =<br>40pF | 28.5 + (t <sub>CLK_SPI</sub> )/2 |      | ns    |

| SPI4   | MISO hold time after SPCK falls   |                     | 0                                |      | ns    |

| SPI5   | SPCK falling to MOSI delay        |                     |                                  | 10.5 | ns    |

Note: 1. These values are based on simulation and characterization of other AVR microcontrollers manufactured in the same process technology. These values are not covered by test limits in production.

### Maximum SPI Frequency, Master Output

The maximum SPI master output frequency is given by the following formula:

$$f_{SPCKMAX} = MIN(f_{PINMAX}, \frac{1}{SPIn})$$

Where *SPIn* is the MOSI delay, SPI2 or SPI5 depending on CPOL and NCPHA.  $f_{PINMAX}$  is the maximum frequency of the SPI pins. Please refer to the I/O Pin Characteristics section for the maximum frequency of the pins.

### Maximum SPI Frequency, Master Input

The maximum SPI master input frequency is given by the following formula:

$$f_{SPCKMAX} = \frac{1}{SPIn + t_{VALID}}$$

Where *SPIn* is the MISO setup and hold time, SPI0 + SPI1 or SPI3 + SPI4 depending on CPOL and NCPHA.  $t_{VALID}$  is the SPI slave response time. Please refer to the SPI slave datasheet for  $t_{VALID}$ .

### 7.9.7 EBI Timings

See EBI I/O lines description for more details.

Table 7-52.SMC Clock Signal.

| Symbol                  | Parameter                      | Max <sup>(1)</sup> | Units |

|-------------------------|--------------------------------|--------------------|-------|

| 1/(t <sub>CPSMC</sub> ) | SMC Controller clock frequency | f <sub>cpu</sub>   | MHz   |

Note: 1. The maximum frequency of the SMC interface is the same as the max frequency for the HSB.

### Table 7-53. SMC Read Signals with Hold Settings<sup>(1)</sup>

| Symbol            | Parameter                                  | Conditions                                     | Min                                                      | Units |

|-------------------|--------------------------------------------|------------------------------------------------|----------------------------------------------------------|-------|

|                   | NR                                         | D Controlled (READ_MODE                        | = 1)                                                     |       |

| SMC <sub>1</sub>  | Data setup before NRD high                 |                                                | 32.5                                                     |       |

| SMC <sub>2</sub>  | Data hold after NRD high                   |                                                | 0                                                        |       |

| SMC <sub>3</sub>  | NRD high to NBS0/A0 change <sup>(2)</sup>  | V <sub>VDD</sub> = 3.0V,                       | nrd hold length * tcpsmc - 1.5                           |       |

| SMC <sub>4</sub>  | NRD high to NBS1 change <sup>(2)</sup>     | drive strength of the pads set to the lowest,  | nrd hold length * tcpsмc - 0                             |       |

| SMC <sub>5</sub>  | NRD high to NBS2/A1 change <sup>(2)</sup>  | external capacitor =                           | nrd hold length * tсрѕмс - 0                             | ns    |

| SMC <sub>7</sub>  | NRD high to A2 - A25 change <sup>(2)</sup> | 40pF                                           | nrd hold length * tcpsmc - 5.6                           | -     |

| SMC <sub>8</sub>  | NRD high to NCS inactive <sup>(2)</sup>    |                                                | (nrd hold length - ncs rd hold length) *<br>tcpsmc - 1.3 |       |

| SMC <sub>9</sub>  | NRD pulse width                            |                                                | nrd pulse length * tcpsmc - 0.6                          |       |

|                   | NR                                         | D Controlled (READ_MODE                        | = 0)                                                     |       |

| SMC <sub>10</sub> | Data setup before NCS high                 |                                                | 34.1                                                     |       |

| SMC <sub>11</sub> | Data hold after NCS high                   |                                                | 0                                                        |       |

| SMC <sub>12</sub> | NCS high to NBS0/A0 change <sup>(2)</sup>  | V <sub>VDD</sub> = 3.0V,                       | ncs rd hold length * tcpsмc - 3                          |       |

| SMC <sub>13</sub> | NCS high to NBS0/A0 change <sup>(2)</sup>  | $v_{VDD} = 3.0 v_{,}$<br>drive strength of the | ncs rd hold length * tcpsmc - 2                          |       |

| SMC <sub>14</sub> | NCS high to NBS2/A1 change <sup>(2)</sup>  | pads set to the lowest,                        | ncs rd hold length * tcpsmc - 1.1                        | ns    |

| SMC <sub>16</sub> | NCS high to A2 - A25 change <sup>(2)</sup> | external capacitor =<br>40pF                   | ncs rd hold length * tcpsмc - 7.2                        |       |

| SMC <sub>17</sub> | NCS high to NRD inactive <sup>(2)</sup>    |                                                | (ncs rd hold length - nrd hold length) *<br>tcPSMc - 2.2 |       |

| SMC <sub>18</sub> | NCS pulse width                            |                                                | ncs rd pulse length * tcpsmc - 3                         |       |

Note: 1. These values are based on simulation and characterization of other AVR microcontrollers manufactured in the same process technology. These values are not covered by test limits in production.

2. hold length = total cycle duration - setup duration - pulse duration. "hold length" is for "ncs rd hold length" or "nrd hold length".

| Symbol               | Parameter                                | Conditions                                     | Min | Units |

|----------------------|------------------------------------------|------------------------------------------------|-----|-------|

| SDRAMC <sub>1</sub>  | SDCKE high before SDCK rising edge       |                                                | 5.6 |       |

| SDRAMC <sub>2</sub>  | SDCKE low after SDCK rising edge         |                                                | 7.3 |       |

| SDRAMC <sub>3</sub>  | SDCKE low before SDCK rising edge        |                                                | 6.8 |       |

| SDRAMC <sub>4</sub>  | SDCKE high after SDCK rising edge        |                                                | 8.3 |       |

| SDRAMC <sub>5</sub>  | SDCS low before SDCK rising edge         |                                                | 6.1 | 1     |

| SDRAMC <sub>6</sub>  | SDCS high after SDCK rising edge         |                                                | 8.4 |       |

| SDRAMC <sub>7</sub>  | RAS low before SDCK rising edge          |                                                | 7   |       |

| SDRAMC <sub>8</sub>  | RAS high after SDCK rising edge          |                                                | 7.7 | ns    |

| SDRAMC <sub>9</sub>  | SDA10 change before SDCK rising edge     |                                                | 6.4 |       |

| SDRAMC <sub>10</sub> | SDA10 change after SDCK rising edge      |                                                | 7.1 |       |

| SDRAMC <sub>11</sub> | Address change before SDCK rising edge   | $V_{VDD} = 3.0V,$                              | 4.7 |       |

| SDRAMC <sub>12</sub> | Address change after SDCK rising edge    | drive strength of the pads set to the highest, | 4.4 |       |

| SDRAMC <sub>13</sub> | Bank change before SDCK rising edge      | external capacitor = 40pF on                   | 6.2 |       |

| SDRAMC <sub>14</sub> | Bank change after SDCK rising edge       | SDRAM pins<br>except 8 pF on SDCK pins         | 6.9 |       |

| SDRAMC <sub>15</sub> | CAS low before SDCK rising edge          |                                                | 6.6 |       |

| SDRAMC <sub>16</sub> | CAS high after SDCK rising edge          |                                                | 7.8 |       |

| SDRAMC <sub>17</sub> | DQM change before SDCK rising edge       |                                                | 6   | -     |

| SDRAMC <sub>18</sub> | DQM change after SDCK rising edge        |                                                | 6.7 | -     |

| SDRAMC <sub>19</sub> | D0-D15 in setup before SDCK rising edge  |                                                | 6.4 | -     |

| SDRAMC <sub>20</sub> | D0-D15 in hold after SDCK rising edge    |                                                | 0   | -     |

| SDRAMC <sub>23</sub> | SDWE low before SDCK rising edge         |                                                | 7   |       |

| SDRAMC <sub>24</sub> | SDWE high after SDCK rising edge         |                                                | 7.4 |       |

| SDRAMC <sub>25</sub> | D0-D15 Out valid before SDCK rising edge |                                                | 5.2 |       |

| SDRAMC <sub>26</sub> | D0-D15 Out valid after SDCK rising edge  |                                                | 5.6 | 1     |

Note: 1. These values are based on simulation and characterization of other AVR microcontrollers manufactured in the same process technology. These values are not covered by test limits in production.

# 8. Mechanical Characteristics

# 8.1 Thermal Considerations

### 8.1.1 Thermal Data

Table 8-1 summarizes the thermal resistance data depending on the package.

| Symbol               | Parameter                              | Condition   | Package | Тур  | Unit   |

|----------------------|----------------------------------------|-------------|---------|------|--------|

| $\theta_{JA}$        | Junction-to-ambient thermal resistance | No air flow | QFN64   | 20.0 | °C/M   |

| $\theta_{JC}$        | Junction-to-case thermal resistance    |             | QFN64   | 0.8  | °C/W   |

| $\theta_{JA}$        | Junction-to-ambient thermal resistance | No air flow | TQFP64  | 40.5 | 0000   |

| $\theta_{JC}$        | Junction-to-case thermal resistance    |             | TQFP64  | 8.7  | °C/W   |

| $\theta_{JA}$        | Junction-to-ambient thermal resistance | No air flow | TQFP100 | 39.3 | °C /// |

| $\theta_{\text{JC}}$ | Junction-to-case thermal resistance    |             | TQFP100 | 8.5  | °C/W   |

| $\theta_{JA}$        | Junction-to-ambient thermal resistance | No air flow | LQFP144 | 38.1 | 0000   |

| $\theta_{JC}$        | Junction-to-case thermal resistance    |             | LQFP144 | 8.4  | °C/W   |

Table 8-1.

Thermal Resistance Data

### 8.1.2 Junction Temperature

The average chip-junction temperature, T<sub>J</sub>, in °C can be obtained from the following:

1.

$$T_J = T_A + (P_D \times \theta_{JA})$$

2.  $T_J = T_A + (P_D \times (\theta_{HEATSINK} + \theta_{JC}))$

where:

- θ<sub>JA</sub> = package thermal resistance, Junction-to-ambient (°C/W), provided in Table 8-1 on page 90.

- $\theta_{JC}$  = package thermal resistance, Junction-to-case thermal resistance (°C/W), provided in Table 8-1 on page 90.

- $\theta_{HEAT SINK}$  = cooling device thermal resistance (°C/W), provided in the device datasheet.

- P<sub>D</sub> = device power consumption (W) estimated from data provided in the section "Power Consumption" on page 51.

- T<sub>A</sub> = ambient temperature (°C).

From the first equation, the user can derive the estimated lifetime of the chip and decide if a cooling device is necessary or not. If a cooling device is to be fitted on the chip, the second equation should be used to compute the resulting average chip-junction temperature  $T_J$  in °C.

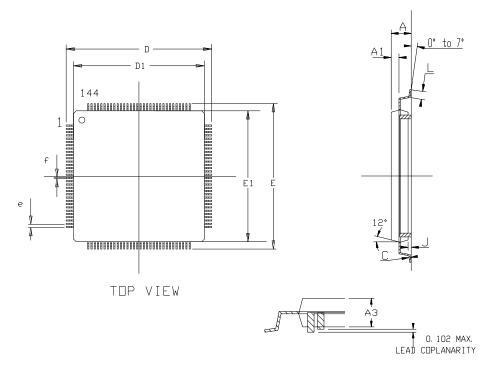

# Figure 8-4. LQFP-144 package drawing

|    | Min   | MM<br>Nom | Ma×    | Min   | INCH<br>Nom | Ma×   |

|----|-------|-----------|--------|-------|-------------|-------|

| A  | -     | -         | 1.60   | -     | -           | . 063 |

| С  | 0, 09 | -         | 0, 20  | , 004 | -           | . 008 |

| A3 | 1. 35 | 1.40      | 1.45   | , 053 | . 055       | . 057 |

| D  | 21.90 | 22. 00    | 22.10  | , 862 | . 866       | . 870 |

| D1 | 19.90 | 20, 00    | 20.10  | , 783 | . 787       | . 791 |

| E  | 21.90 | 22. 00    | 22. 10 | . 862 | . 866       | . 870 |

| E1 | 19.90 | 20. 00    | 20.10  | . 783 | . 787       | . 791 |

| J  | 0. 05 | -         | 0.15   | . 002 | -           | . 006 |

| L  | 0.45  | 0. 60     | 0. 75  | . 018 | . 024       | . 030 |

| e  |       | 0.50 BSC  |        |       | .0197 BSC   |       |

| f  |       | 0.22 BSC  |        |       | .009 BSC    |       |

### Table 8-11. Device and Package Maximum Weight

| 1300                       |                         | mg                      |  |

|----------------------------|-------------------------|-------------------------|--|

| Table 8-12.                | Package Characteristics |                         |  |

| Moisture Sensitivity Level |                         | Jdec J-STD0-20D - MSL 3 |  |

| Table 8-13.                | Package Reference       |                         |  |

| IEDEC Drowing Deference    |                         | MS 026                  |  |

| JEDEC Drawing Reference | MS-026 |

|-------------------------|--------|

| JESD97 Classification   | E3     |

# 8.3 Soldering Profile

Table 8-14 gives the recommended soldering profile from J-STD-20.

| Table 8-14. | Soldering Profile |

|-------------|-------------------|

|-------------|-------------------|

| Profile Feature                            | Green Package            |

|--------------------------------------------|--------------------------|

| Average Ramp-up Rate (217°C to Peak)       | 3°C/sec                  |

| Preheat Temperature 175°C ±25°C            | Min. 150 °C, Max. 200 °C |

| Temperature Maintained Above 217°C         | 60-150 sec               |

| Time within 5.C of Actual Peak Temperature | 30 sec                   |

| Peak Temperature Range                     | 260 °C                   |

| Ramp-down Rate                             | 6 °C/sec                 |

| Time 25 C to Peak Temperature              | Max. 8 minutes           |

Note: It is recommended to apply a soldering temperature higher than 250°C. A maximum of three reflow passes is allowed per component.

# 2 Requesting clocks in idle sleep modes will mask all other PB clocks than the requested

In idle or frozen sleep mode, all the PB clocks will be frozen if the TWIS or the AST need to wake the cpu up.

#### **Fix/Workaround**

Disable the TWIS or the AST before entering idle or frozen sleep mode.

### 3 TWIS may not wake the device from sleep mode

If the CPU is put to a sleep mode (except Idle and Frozen) directly after a TWI Start condition, the CPU may not wake upon a TWIS address match. The request is NACKed. **Fix/Workaround**

When using the TWI address match to wake the device from sleep, do not switch to sleep modes deeper than Frozen. Another solution is to enable asynchronous EIC wake on the TWIS clock (TWCK) or TWIS data (TWD) pins, in order to wake the system up on bus events.

### 10.2.6 SCIF

### 1 PLLCOUNT value larger than zero can cause PLLEN glitch

Initializing the PLLCOUNT with a value greater than zero creates a glitch on the PLLEN signal during asynchronous wake up.

### Fix/Workaround

The lock-masking mechanism for the PLL should not be used. The PLLCOUNT field of the PLL Control Register should always be written to zero.

### 2 PLL lock might not clear after disable

Under certain circumstances, the lock signal from the Phase Locked Loop (PLL) oscillator may not go back to zero after the PLL oscillator has been disabled. This can cause the propagation of clock signals with the wrong frequency to parts of the system that use the PLL clock.

### Fix/Workaround

PLL must be turned off before entering STOP, DEEPSTOP or STATIC sleep modes. If PLL has been turned off, a delay of 30us must be observed after the PLL has been enabled again before the SCIF.PLL0LOCK bit can be used as a valid indication that the PLL is locked.

### 3 BOD33 reset locks the device

If BOD33 is enabled as a reset source (SCIF.BOD33.CTRL=0x1) and when VDDIN\_33 power supply voltage falls below the BOD33 voltage (SCIF.BOD33.LEVEL), the device is locked permanently under reset even if the power supply goes back above BOD33 reset level. In order to unlock the device, an external reset event should be applied on RESET\_N. **Fix/Workaround**

Use an external BOD on VDDIN\_33 or an external reset source.

### 1 SPI data transfer hangs with CSR0.CSAAT==1 and MR.MODFDIS==0

When CSR0.CSAAT==1 and mode fault detection is enabled (MR.MODFDIS==0), the SPI module will not start a data transfer.

### Fix/Workaround

Disable mode fault detection by writing a one to MR.MODFDIS.

# **11. Datasheet Revision History**

Please note that the referring page numbers in this section are referred to this document. The referring revision in this section are referring to the document revision.

## 11.1 Rev. D - 01/12

- 1 Errata: Updated

- 2 PM: Clock Mask Table Updated

- 3 Fixed PLLOPT field description in SCIF chapter

- 4 MDMA: Swapped bit descriptions for IER and IDR

- 5 MACB: USRIO register description and bit descriptions for IMR/IDR/IER Updated

- 6 USBC: UPCON.PFREEZE and UPINRQn description Updated

- 7 ACIFA: Updated

- 8 ADCIFA: CFG.MUXSET, SSMQ description and conversion results section Updated

- 9 DACIFB: Calibration section Updated

- 10 Electrical Characteristics: ADCREFP/ADCREFN added

## 11.2 Rev. C – 08/11

Electrical Characteristics Updated:

- I/O Pins characteristics

- 8MHz/1MHz RC Oscillator (RC8M) characteristics

- 1.8V Voltage Regulator characteristics

- 3.3V Voltage Regulator characteristics

- 1.8VBrown Out Detector (BOD18) characteristics

- 3.3VBrown Out Detector (BOD33) characteristics

- 5VBrown Out Detector (BOD50) characteristics

- Analog to Digital Converter (ADC) and sample and hold (S/DH) Characteristics

- Analog Comparator characteristics

- 2 Errata: Updated

1

3 TWIS: Updated

# 11.3 Rev. B - 03/11

- 1 Package and pinout: Added supply column. Updated peripheral functions

- 2 Supply and Startup Considerations: Updated I/O lines power

- 3 PM: Added AWEN description

- 4 SCIF: Added VREGCR register

- 5 AST: Updated digital tuner formula

- 6 SDRAMC: cleaned-up SDCS/NCS names. Added VERSION register

- 7 SAU: Updated SR.IDLE

- 8 USART: Updated

- 9 CANIF: Updated address map figure

- 10 USBC: Updated

- 11 DACIFB: Updated

- 12 Programming and Debugging: Added JTAG Data Registers section

- 13 Electrical Characteristics: Updated

- 14 Ordering Information: Updated

- 15 Errata: Updated

# 11.4 Rev. A - 10/10

1 Initial revision

# AT32UC3C

| 7.9    | Timing Characteristics                                                                 | 70                                                                                          |

|--------|----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| Mecha  | nical Characteristics                                                                  | 90                                                                                          |

| 8.1    | Thermal Considerations                                                                 | 90                                                                                          |

| 8.2    | Package Drawings                                                                       | 91                                                                                          |

| 8.3    | Soldering Profile                                                                      | 95                                                                                          |

| Orderi | ng Information                                                                         | 96                                                                                          |

| Errata |                                                                                        | 97                                                                                          |

| 10.1   | rev E                                                                                  | 97                                                                                          |

| 10.2   | rev D                                                                                  | 101                                                                                         |

| Datash | eet Revision History                                                                   | 106                                                                                         |

| 11.1   | Rev. D – 01/12                                                                         | 106                                                                                         |

| 11.2   | Rev. C – 08/11                                                                         | 106                                                                                         |

|        | Dev D 02/44                                                                            | 400                                                                                         |

| 11.3   | Rev. B – 03/11                                                                         | 106                                                                                         |

|        | 8.1<br>8.2<br>8.3<br><b>Orderin</b><br>Errata<br>10.1<br>10.2<br><b>Datash</b><br>11.1 | 8.2       Package Drawings         8.3       Soldering Profile         Ordering Information |