#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

ĿXF

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | AVR                                                                          |

| Core Size                  | 32-Bit Single-Core                                                           |

| Speed                      | 66MHz                                                                        |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB       |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                 |

| Number of I/O              | 45                                                                           |

| Program Memory Size        | 128KB (128K x 8)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | · ·                                                                          |

| RAM Size                   | 32K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                    |

| Data Converters            | A/D 11x12b; D/A 2x12b                                                        |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 64-VFQFN Exposed Pad                                                         |

| Supplier Device Package    | 64-QFN (9x9)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at32uc3c2128c-z2ur |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The Full-Speed USB 2.0 Device interface supports several USB Classes at the same time thanks to the rich End-Point configuration. The On-The-GO (OTG) Host interface allows device like a USB Flash disk or a USB printer to be directly connected to the processor.

The media-independent interface (MII) and reduced MII (RMII) 10/100 Ethernet MAC module provides on-chip solutions for network-connected devices.

The Peripheral Event Controller (PEVC) allows to redirect events from one peripheral or from input pins to another peripheral. It can then trigger, in a deterministic time, an action inside a peripheral without the need of CPU. For instance a PWM waveform can directly trigger an ADC capture, hence avoiding delays due to software interrupt processing.

The AT32UC3C features analog functions like ADC, DAC, Analog comparators. The ADC interface is built around a 12-bit pipelined ADC core and is able to control two independent 8-channel or one 16-channel. The ADC block is able to measure two different voltages sampled at the same time. The analog comparators can be paired to detect when the sensing voltage is within or outside the defined reference window.

Atmel offers the QTouch library for embedding capacitive touch buttons, sliders, and wheels functionality into AVR microcontrollers. The patented charge-transfer signal acquisition offers robust sensing and included fully debounced reporting of touch keys and includes Adjacent Key Suppression<sup>®</sup> (AKS<sup>®</sup>) technology for unambiguous detection of key events. The easy-to-use QTouch Suite toolchain allows you to explore, develop, and debug your own touch applications.

AT32UC3C integrates a class 2+ Nexus 2.0 On-Chip Debug (OCD) System, with non-intrusive real-time trace, full-speed read/write memory access in addition to basic runtime control. The Nanotrace interface enables trace feature for aWire- or JTAG-based debuggers. The single-pin aWire interface allows all features available through the JTAG interface to be accessed through the RESET pin, allowing the JTAG pins to be used for GPIO or peripherals.

# 2.2 Configuration Summary

| Table 2-1. | Configuration Summary |

|------------|-----------------------|

| Feature                          | AT32UC3C0512C/<br>AT32UC3C0256C/<br>AT32UC3C0128C/<br>AT32UC3C064C                                                                                                                                        | AT32UC3C1512C/<br>AT32UC3C1256C/<br>AT32UC3C1128C/<br>AT32UC3C164C | AT32UC3C2512C/<br>AT32UC3C2256C/<br>AT32UC3C2128C/<br>AT32UC3C264C |  |  |

|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------|--|--|

| Flash                            | 512/256/128/64 KB                                                                                                                                                                                         | 512/256/128/64 KB                                                  | 512/256/128/64 KB                                                  |  |  |

| SRAM                             | 64/64/32/16KB                                                                                                                                                                                             | 64/64/32/16KB                                                      | 64/64/32/16KB                                                      |  |  |

| HSB RAM                          |                                                                                                                                                                                                           | 4 KB                                                               |                                                                    |  |  |

| EBI                              | 1                                                                                                                                                                                                         | 0                                                                  | 0                                                                  |  |  |

| GPIO                             | 123                                                                                                                                                                                                       | 81                                                                 | 45                                                                 |  |  |

| External Interrupts              | 8                                                                                                                                                                                                         | 8                                                                  | 8                                                                  |  |  |

| TWI                              | 3                                                                                                                                                                                                         | 3                                                                  | 2                                                                  |  |  |

| USART                            | 5                                                                                                                                                                                                         | 5                                                                  | 4                                                                  |  |  |

| Peripheral DMA Channels          | 16                                                                                                                                                                                                        | 16                                                                 | 16                                                                 |  |  |

| Peripheral Event System          | 1                                                                                                                                                                                                         | 1                                                                  | 1                                                                  |  |  |

| SPI                              | 2                                                                                                                                                                                                         | 2                                                                  | 1                                                                  |  |  |

| CAN channels                     | 2                                                                                                                                                                                                         | 2                                                                  | 2                                                                  |  |  |

| USB                              | 1                                                                                                                                                                                                         | 1                                                                  | 1                                                                  |  |  |

| Ethernet MAC 10/100              | 1<br>RMII/MII                                                                                                                                                                                             | 1<br>RMII/MII                                                      | 1<br>RMII only                                                     |  |  |

| I2S                              | 1                                                                                                                                                                                                         | 1                                                                  | 1                                                                  |  |  |

| Asynchronous Timers              | 1                                                                                                                                                                                                         | 1                                                                  | 1                                                                  |  |  |

| Timer/Counter Channels           | 6                                                                                                                                                                                                         | 6                                                                  | 3                                                                  |  |  |

| PWM channels                     |                                                                                                                                                                                                           | 4x2                                                                |                                                                    |  |  |

| QDEC                             | 2                                                                                                                                                                                                         | 2                                                                  | 1                                                                  |  |  |

| Frequency Meter                  |                                                                                                                                                                                                           | 1                                                                  |                                                                    |  |  |

| Watchdog Timer                   |                                                                                                                                                                                                           | 1                                                                  |                                                                    |  |  |

| Power Manager                    |                                                                                                                                                                                                           | 1                                                                  |                                                                    |  |  |

| Oscillators                      | PLL 80-240 MHz (PLL0/PLL1)<br>Crystal Oscillator 0.4-20 MHz (OSC0)<br>Crystal Oscillator 32 KHz (OSC32K)<br>RC Oscillator 115 kHz (RCSYS)<br>RC Oscillator 8 MHz (RC8M)<br>RC Oscillator 120 MHz (RC120M) |                                                                    |                                                                    |  |  |

|                                  |                                                                                                                                                                                                           | Hz (OSC1)                                                          | -                                                                  |  |  |

| 12-bit ADC<br>number of channels | 1<br>16                                                                                                                                                                                                   | 1<br>16                                                            | 1                                                                  |  |  |

| 12-bit DAC<br>number of channels | 1 4                                                                                                                                                                                                       | 1 4                                                                | 1 2                                                                |  |  |

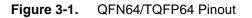

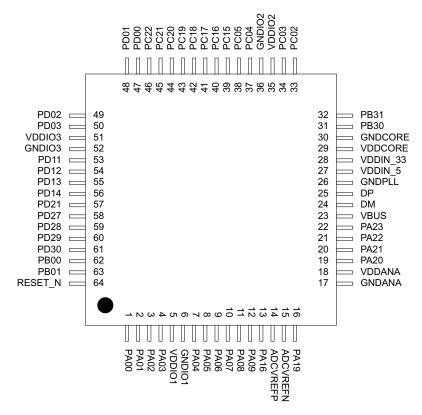

# 3. Package and Pinout

## 3.1 Package

The device pins are multiplexed with peripheral functions as described in Table 3-1 on page 11.

Note: on QFN packages, the exposed pad is unconnected.

#### Figure 3-3. LQFP144 Pinout

| Table 3-1. | GPIO Controller Function Multiplexing |

|------------|---------------------------------------|

|------------|---------------------------------------|

| TQFP           |             |             |      | G           |        |                    |                   |                          | GPIO fu                   | unction                   |                  |   |

|----------------|-------------|-------------|------|-------------|--------|--------------------|-------------------|--------------------------|---------------------------|---------------------------|------------------|---|

| /<br>QFN<br>64 | TQFP<br>100 | LQFP<br>144 | PIN  | P<br>I<br>O | Supply | Pin<br>Type<br>(1) | А                 | в                        | С                         | D                         | E                | F |

| 16             | 25          | 36          | PA19 | 19          | VDDANA | x1/x2              | ADCIN8            | EIC -<br>EXTINT[1]       |                           |                           |                  |   |

| 19             | 28          | 39          | PA20 | 20          | VDDANA | x1/x2              | ADCIN9            | AC0AP0                   | AC0AP0 or<br>DAC0A        |                           |                  |   |

| 20             | 29          | 40          | PA21 | 21          | VDDANA | x1/x2              | ADCIN10           | AC0BN0                   | AC0BN0 or<br>DAC0B        |                           |                  |   |

| 21             | 30          | 41          | PA22 | 22          | VDDANA | x1/x2              | ADCIN11           | AC0AN0                   | PEVC -<br>PAD_EVT<br>[4]  |                           | MACB -<br>SPEED  |   |

| 22             | 31          | 42          | PA23 | 23          | VDDANA | x1/x2              | ADCIN12           | AC0BP0                   | PEVC -<br>PAD_EVT<br>[5]  |                           | MACB -<br>WOL    |   |

|                | 32          | 43          | PA24 | 24          | VDDANA | x1/x2              | ADCIN13           | SPI1 -<br>NPCS[2]        |                           |                           |                  |   |

|                | 33          | 44          | PA25 | 25          | VDDANA | x1/x2              | ADCIN14           | SPI1 -<br>NPCS[3]        | EIC -<br>EXTINT[0]        |                           |                  |   |

|                |             | 45          | PA26 | 26          | VDDANA | x1/x2              | AC0AP1            | EIC -<br>EXTINT[1]       |                           |                           |                  |   |

|                |             | 46          | PA27 | 27          | VDDANA | x1/x2              | AC0AN1            | EIC -<br>EXTINT[2]       |                           |                           |                  |   |

|                |             | 47          | PA28 | 28          | VDDANA | x1/x2              | AC0BP1            | EIC -<br>EXTINT[3]       |                           |                           |                  |   |

|                |             | 48          | PA29 | 29          | VDDANA | x1/x2              | AC0BN1            | EIC -<br>EXTINT[0]       |                           |                           |                  |   |

| 62             | 96          | 140         | PB00 | 32          | VDDIO1 | x1                 | USART0 -<br>CLK   | CANIF -<br>RXLINE[1]     | EIC -<br>EXTINT[8]        | PEVC -<br>PAD_EVT<br>[10] |                  |   |

| 63             | 97          | 141         | PB01 | 33          | VDDIO1 | x1                 |                   | CANIF -<br>TXLINE[1]     |                           | PEVC -<br>PAD_EVT<br>[11] |                  |   |

|                | 99          | 143         | PB02 | 34          | VDDIO1 | x1                 |                   | USBC - ID                | PEVC -<br>PAD_EVT<br>[6]  | TC1 - A1                  |                  |   |

|                | 100         | 144         | PB03 | 35          | VDDIO1 | x1                 |                   | USBC -<br>VBOF           | PEVC -<br>PAD_EVT<br>[7]  |                           |                  |   |

|                | 7           | 7           | PB04 | 36          | VDDIO1 | x1/x2              | SPI1 -<br>MOSI    | CANIF -<br>RXLINE[0]     | QDEC1 -<br>QEPI           |                           | MACB -<br>TXD[2] |   |

|                | 8           | 8           | PB05 | 37          | VDDIO1 | x1/x2              | SPI1 -<br>MISO    | CANIF -<br>TXLINE[0]     | PEVC -<br>PAD_EVT<br>[12] | USART3 -<br>CLK           | MACB -<br>TXD[3] |   |

|                | 9           | 9           | PB06 | 38          | VDDIO1 | x2/x4              | SPI1 -<br>SCK     |                          | QDEC1 -<br>QEPA           | USART1-<br>CLK            | MACB -<br>TX_ER  |   |

|                |             | 10          | PB07 | 39          | VDDIO1 | x1/x2              | SPI1 -<br>NPCS[0] | EIC -<br>EXTINT[2]       | QDEC1 -<br>QEPB           |                           | MACB -<br>RX_DV  |   |

|                |             | 11          | PB08 | 40          | VDDIO1 | x1/x2              | SPI1 -<br>NPCS[1] | PEVC -<br>PAD_EVT<br>[1] | PWM -<br>PWML[0]          |                           | MACB -<br>RXD[0] |   |

|                |             | 12          | PB09 | 41          | VDDIO1 | x1/x2              | SPI1 -<br>NPCS[2] |                          | PWM -<br>PWMH[0]          |                           | MACB -<br>RXD[1] |   |

|                |             | 13          | PB10 | 42          | VDDIO1 | x1/x2              | USART1 -<br>DTR   | SPI0 -<br>MOSI           | PWM -<br>PWML[1]          |                           |                  |   |

Table 3-1.

GPIO Controller Function Multiplexing

| TQFP           |             |             |      | G   |        |                    | -               |                   | GPIO fu                    | unction            |                      |   |

|----------------|-------------|-------------|------|-----|--------|--------------------|-----------------|-------------------|----------------------------|--------------------|----------------------|---|

| /<br>QFN<br>64 | TQFP<br>100 | LQFP<br>144 | PIN  | ΡΙΟ | Supply | Pin<br>Type<br>(1) | А               | в                 | с                          | D                  | E                    | F |

|                |             | 14          | PB11 | 43  | VDDIO1 | x1/x2              | USART1 -<br>DSR | SPI0 -<br>MISO    | PWM -<br>PWMH[1]           |                    |                      |   |

|                |             | 15          | PB12 | 44  | VDDIO1 | x1/x2              | USART1 -<br>DCD | SPI0 -<br>SCK     | PWM -<br>PWML[2]           |                    |                      |   |

|                |             | 16          | PB13 | 45  | VDDIO1 | x1/x2              | USART1 -<br>RI  | SPI0 -<br>NPCS[0] | PWM -<br>PWMH[2]           |                    | MACB -<br>RX_ER      |   |

|                |             | 17          | PB14 | 46  | VDDIO1 | x1/x2              | USART1 -<br>RTS | SPI0 -<br>NPCS[1] | PWM -<br>PWML[3]           |                    | MACB -<br>MDC        |   |

|                |             | 18          | PB15 | 47  | VDDIO1 | x1/x2              | USART1 -<br>CTS | USART1 -<br>CLK   | PWM -<br>PWMH[3]           |                    | MACB -<br>MDIO       |   |

|                |             | 19          | PB16 | 48  | VDDIO1 | x1/x2              | USART1 -<br>RXD | SPI0 -<br>NPCS[2] | PWM -<br>EXT_<br>FAULTS[0] |                    | CANIF -<br>RXLINE[0] |   |

|                |             | 20          | PB17 | 49  | VDDIO1 | x1/x2              | USART1 -<br>TXD | SPIO -<br>NPCS[3] | PWM -<br>EXT_<br>FAULTS[1] |                    | CANIF -<br>TXLINE[0] |   |

|                |             | 57          | PB18 | 50  | VDDIO2 | x1/x2              | TC0 -<br>CLK2   |                   | EIC -<br>EXTINT[4]         |                    |                      |   |

|                | 42          | 58          | PB19 | 51  | VDDIO2 | x1/x2              | TC0 - A0        | SPI1 -<br>MOSI    | IISC -<br>ISDO             |                    | MACB -<br>CRS        |   |

|                | 43          | 59          | PB20 | 52  | VDDIO2 | x1/x2              | TC0 - B0        | SPI1 -<br>MISO    | IISC - ISDI                | ACIFA1 -<br>ACAOUT | MACB -<br>COL        |   |

|                | 44          | 60          | PB21 | 53  | VDDIO2 | x2/x4              | TC0 -<br>CLK1   | SPI1 -<br>SCK     | IISC -<br>IMCK             | ACIFA1 -<br>ACBOUT | MACB -<br>RXD[2]     |   |

|                | 45          | 61          | PB22 | 54  | VDDIO2 | x1/x2              | TC0 - A1        | SPI1 -<br>NPCS[3] | IISC -<br>ISCK             | SCIF -<br>GCLK[0]  | MACB -<br>RXD[3]     |   |

|                | 46          | 62          | PB23 | 55  | VDDIO2 | x1/x2              | TC0 - B1        | SPI1 -<br>NPCS[2] | IISC - IWS                 | SCIF -<br>GCLK[1]  | MACB -<br>RX_CLK     |   |

|                |             | 63          | PB24 | 56  | VDDIO2 | x1/x2              | TC0 -<br>CLK0   | SPI1 -<br>NPCS[1] |                            |                    |                      |   |

|                |             | 64          | PB25 | 57  | VDDIO2 | x1/x2              | TC0 - A2        | SPI1 -<br>NPCS[0] | PEVC -<br>PAD_EVT<br>[8]   |                    |                      |   |

|                |             | 65          | PB26 | 58  | VDDIO2 | x2/x4              | TC0 - B2        | SPI1 -<br>SCK     | PEVC -<br>PAD_EVT<br>[9]   |                    | MACB -<br>TX_EN      |   |

|                |             | 66          | PB27 | 59  | VDDIO2 | x1/x2              | QDEC0 -<br>QEPA | SPI1 -<br>MISO    | PEVC -<br>PAD_EVT<br>[10]  | TC1 -<br>CLK0      | MACB -<br>TXD[0]     |   |

|                |             | 67          | PB28 | 60  | VDDIO2 | x1/x2              | QDEC0 -<br>QEPB | SPI1 -<br>MOSI    | PEVC -<br>PAD_EVT<br>[11]  | TC1 - B0           | MACB -<br>TXD[1]     |   |

|                |             | 68          | PB29 | 61  | VDDIO2 | x1/x2              | QDEC0 -<br>QEPI | SPI0 -<br>NPCS[0] | PEVC -<br>PAD_EVT<br>[12]  | TC1 - A0           |                      |   |

| 31             | 47          | 69          | PB30 | 62  | VDDIO2 | x1                 |                 |                   |                            |                    |                      |   |

| 32             | 48          | 70          | PB31 | 63  | VDDIO2 | x1                 |                 |                   |                            |                    |                      |   |

|                | 49          | 71          | PC00 | 64  | VDDIO2 | x1/x2              | USBC - ID       | SPI0 -<br>NPCS[1] | USART2 -<br>CTS            | TC1 - B2           | CANIF -<br>TXLINE[1] |   |

|                | 50          | 72          | PC01 | 65  | VDDIO2 | x1/x2              | USBC -<br>VBOF  | SPI0 -<br>NPCS[2] | USART2 -<br>RTS            | TC1 - A2           | CANIF -<br>RXLINE[1] |   |

## 4. Processor and Architecture

Rev: 2.1.2.0

This chapter gives an overview of the AVR32UC CPU. AVR32UC is an implementation of the AVR32 architecture. A summary of the programming model, instruction set, and MPU is presented. For further details, see the *AVR32 Architecture Manual* and the *AVR32UC Technical Reference Manual*.

## 4.1 Features

- 32-bit load/store AVR32A RISC architecture

- 15 general-purpose 32-bit registers

- 32-bit Stack Pointer, Program Counter and Link Register reside in register file

- Fully orthogonal instruction set

- Privileged and unprivileged modes enabling efficient and secure operating systems

- Innovative instruction set together with variable instruction length ensuring industry leading code density

- DSP extension with saturating arithmetic, and a wide variety of multiply instructions

- 3-stage pipeline allowing one instruction per clock cycle for most instructions

- Byte, halfword, word, and double word memory access

- Multiple interrupt priority levels

- MPU allows for operating systems with memory protection

- FPU enables hardware accelerated floating point calculations

- Secure State for supporting FlashVault technology

## 4.2 AVR32 Architecture

AVR32 is a new, high-performance 32-bit RISC microprocessor architecture, designed for costsensitive embedded applications, with particular emphasis on low power consumption and high code density. In addition, the instruction set architecture has been tuned to allow a variety of microarchitectures, enabling the AVR32 to be implemented as low-, mid-, or high-performance processors. AVR32 extends the AVR family into the world of 32- and 64-bit applications.

Through a quantitative approach, a large set of industry recognized benchmarks has been compiled and analyzed to achieve the best code density in its class. In addition to lowering the memory requirements, a compact code size also contributes to the core's low power characteristics. The processor supports byte and halfword data types without penalty in code size and performance.

Memory load and store operations are provided for byte, halfword, word, and double word data with automatic sign- or zero extension of halfword and byte data. The C-compiler is closely linked to the architecture and is able to exploit code optimization features, both for size and speed.

In order to reduce code size to a minimum, some instructions have multiple addressing modes. As an example, instructions with immediates often have a compact format with a smaller immediate, and an extended format with a larger immediate. In this way, the compiler is able to use the format giving the smallest code size.

Another feature of the instruction set is that frequently used instructions, like add, have a compact format with two operands as well as an extended format with three operands. The larger format increases performance, allowing an addition and a data move in the same instruction in a

single cycle. Load and store instructions have several different formats in order to reduce code size and speed up execution.

The register file is organized as sixteen 32-bit registers and includes the Program Counter, the Link Register, and the Stack Pointer. In addition, register R12 is designed to hold return values from function calls and is used implicitly by some instructions.

## 4.3 The AVR32UC CPU

The AVR32UC CPU targets low- and medium-performance applications, and provides an advanced On-Chip Debug (OCD) system, no caches, and a Memory Protection Unit (MPU). A hardware Floating Point Unit (FPU) is also provided through the coprocessor instruction space. Java acceleration hardware is not implemented.

AVR32UC provides three memory interfaces, one High Speed Bus master for instruction fetch, one High Speed Bus master for data access, and one High Speed Bus slave interface allowing other bus masters to access data RAMs internal to the CPU. Keeping data RAMs internal to the CPU allows fast access to the RAMs, reduces latency, and guarantees deterministic timing. Also, power consumption is reduced by not needing a full High Speed Bus access for memory accesses. A dedicated data RAM interface is provided for communicating with the internal data RAMs.

A local bus interface is provided for connecting the CPU to device-specific high-speed systems, such as floating-point units and I/O controller ports. This local bus has to be enabled by writing a one to the LOCEN bit in the CPUCR system register. The local bus is able to transfer data between the CPU and the local bus slave in a single clock cycle. The local bus has a dedicated memory range allocated to it, and data transfers are performed using regular load and store instructions. Details on which devices that are mapped into the local bus space is given in the CPU Local Bus section in the Memories chapter.

Figure 4-1 on page 27 displays the contents of AVR32UC.

| Part Number                                     | Flash Size<br>(FLASH_PW) | Number of<br>pages<br>(FLASH_P) | Page size<br>(FLASH_W) |

|-------------------------------------------------|--------------------------|---------------------------------|------------------------|

| AT32UC3C0512C<br>AT32UC3C1512C<br>AT32UC3C2512C | 512 Kbytes               | 1024                            | 128 words              |

| AT32UC3C0256C<br>AT32UC3C1256C<br>AT32UC3C2256C | 256 Kbytes               | 512                             | 128 words              |

| AT32UC3C0128C<br>AT32UC3C1128C<br>AT32UC3C2128C | 128 Kbytes               | 256                             | 128 words              |

| AT32UC3C064C<br>AT32UC3C164C<br>AT32UC3C264C    | 64 Kbytes                | 128                             | 128 words              |

**Table 5-2.**Flash Memory Parameters

## 5.3 Peripheral Address Map

## **Table 5-3.**Peripheral Address Mapping

| Address    |        | Peripheral Name                                                      |

|------------|--------|----------------------------------------------------------------------|

| 0xFFFD0000 | PDCA   | Peripheral DMA Controller - PDCA                                     |

| 0xFFFD1000 | MDMA   | Memory DMA - MDMA                                                    |

|            |        | Universal Synchronous/Asynchronous<br>Receiver/Transmitter - USART1  |

| 0xFFFD1800 | SPI0   | Serial Peripheral Interface - SPI0                                   |

| 0xFFFD1C00 | CANIF  | Control Area Network interface - CANIF                               |

| 0xFFFD2000 | TC0    | Timer/Counter - TC0                                                  |

| 0xFFFD2400 | ADCIFA | ADC controller interface with Touch Screen functionality<br>- ADCIFA |

| 0xFFFD2800 | USART4 | Universal Synchronous/Asynchronous<br>Receiver/Transmitter - USART4  |

| 0xFFFD2C00 | TWIM2  | Two-wire Master Interface - TWIM2                                    |

| 0xFFFD3000 | TWIS2  | Two-wire Slave Interface - TWIS2                                     |

| Port | Register                             | Mode   | Local Bus<br>Address | Access     |

|------|--------------------------------------|--------|----------------------|------------|

| D    | Output Driver Enable Register (ODER) | WRITE  | 0x40000340           | Write-only |

|      |                                      | SET    | 0x40000344           | Write-only |

|      |                                      | CLEAR  | 0x40000348           | Write-only |

|      |                                      | TOGGLE | 0x4000034C           | Write-only |

|      | Output Value Register (OVR)          | WRITE  | 0x40000350           | Write-only |

|      |                                      | SET    | 0x40000354           | Write-only |

|      |                                      | CLEAR  | 0x40000358           | Write-only |

|      |                                      | TOGGLE | 0x4000035C           | Write-only |

|      | Pin Value Register (PVR)             | -      | 0x40000360           | Read-only  |

| Table 5-4. | Local bus mapped GPIO registers |

|------------|---------------------------------|

|------------|---------------------------------|

# 7. Electrical Characteristics

## 7.1 Absolute Maximum Ratings\*

| Operating temperature40°C to +85°C                                                       |

|------------------------------------------------------------------------------------------|

| Storage temperature60°C to +150°C                                                        |

| Voltage on any pin except DM/DP/VBUS with respect to ground0.3V to $V_{VDD}^{(1)}$ +0.3V |

| Voltage on DM/DP with respect to ground0.3V to +3.6V                                     |

| Voltage on VBUS with respect to ground0.3V to +5.5V                                      |

| Maximum operating voltage (VDDIN_5)                                                      |

| Maximum operating voltage (VDDIO1, VDDIO2, VDDIO3, VDDANA)                               |

| Maximum operating voltage (VDDIN_33)                                                     |

| Total DC output current on all I/O pins- VDDIO1 120 mA                                   |

| Total DC output current on all I/O pins- VDDIO2 120 mA                                   |

| Total DC output current on all I/O pins- VDDIO3 120 mA                                   |

| Total DC output current on all I/O pins- VDDANA 120 mA                                   |

\*NOTICE: Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Notes: 1. V<sub>VDD</sub> corresponds to either V<sub>VDDIO1</sub>, V<sub>VDDIO2</sub>, V<sub>VDDIO3</sub>, or V<sub>VDDANA</sub>, depending on the supply for the pin. Refer to Section 3-1 on page 11 for details.

## 7.2 Supply Characteristics

The following characteristics are applicable to the operating temperature range:  $T_A = -40$  °C to 85 °C, unless otherwise specified and are valid for a junction temperature up to  $T_J = 100$  °C. Please refer to Section 6. "Supply and Startup Considerations" on page 46.

| Symbol                                     | Parameter                     | Condition        | Min | Мах | Unit |

|--------------------------------------------|-------------------------------|------------------|-----|-----|------|

| M                                          |                               | 3V range         | 3.0 | 3.6 | V    |

| $V_{VDDIN_5}$                              | DC supply internal regulators | 5V range         | 4.5 | 5.5 | v    |

| V <sub>VDDIN_33</sub>                      | DC supply USB I/O             | only in 3V range | 3.0 | 3.6 | V    |

| M                                          | DC supply peripheral I/O and  | 3V range         | 3.0 | 3.6 |      |

| V <sub>VDDANA</sub>                        | analog part                   | 5V range         | 4.5 | 5.5 | V    |

| V <sub>VDDIO1</sub>                        |                               | 3V range         | 3.0 | 3.6 |      |

| V <sub>VDDIO2</sub><br>V <sub>VDDIO2</sub> | DC supply peripheral I/O      | 5V range         | 4.5 | 5.5 | V    |

Table 7-1.

Supply Characteristics

- Internal 3.3V regulator is off

- TA = 25°C

- I/Os are configured as inputs, with internal pull-up enabled.

- Oscillators

- OSC0/1 (crystal oscillator) stopped

- OSC32K (32KHz crystal oscillator) stopped

- PLL0 running

- PLL1 stopped

- Clocks

- External clock on XIN0 as main clock source (10MHz)

- CPU, HSB, and PBB clocks undivided

- PBA, PBC clock divided by 4

- All peripheral clocks running

Table 7-4.

Power Consumption for Different Operating Modes

| Mode                   | Conditions                                  | Measured on | Consumption Typ | Unit                |

|------------------------|---------------------------------------------|-------------|-----------------|---------------------|

| Active <sup>(1)</sup>  | CPU running a recursive Fibonacci algorithm |             | 512             |                     |

| Idle <sup>(1)</sup>    |                                             |             | 258             | . ( <b>b</b> . 4) 1 |

| Frozen <sup>(1)</sup>  |                                             |             | 106             | µA/MHz              |

| Standby <sup>(1)</sup> |                                             |             | 48              | -                   |

| Stop                   |                                             | Amp         | 73              |                     |

| DeepStop               |                                             |             | 43              |                     |

| Ctatia                 | OSC32K and AST running                      |             | 32              | μA                  |

| Static                 | AST and OSC32K stopped                      |             | 31              |                     |

Note: 1. These numbers are valid for the measured condition only and must not be extrapolated to other frequencies.

- PLL1 stopped

- Clocks

- External clock on XIN0 as main clock source.

- CPU, HSB, and PB clocks undivided

Consumption active is the added current consumption when the module clock is turned on and when the module is doing a typical set of operations.

| Peripheral            | Typ Consumption Active | Unit   |

|-----------------------|------------------------|--------|

| ACIFA <sup>(1)</sup>  | 3                      |        |

| ADCIFA <sup>(1)</sup> | 7                      |        |

| AST                   | 3                      | -      |

| CANIF                 | 25                     | -      |

| DACIFB <sup>(1)</sup> | 3                      | -      |

| EBI                   | 23                     | -      |

| EIC                   | 0.5                    |        |

| FREQM                 | 0.5                    | _      |

| GPIO                  | 37                     | -      |

| INTC                  | 3                      | -      |

| MDMA                  | 4                      | -      |

| PDCA                  | 24                     | -      |

| PEVC                  | 15                     | -      |

| PWM                   | 40                     | -      |

| QDEC                  | 3                      | µA/MHz |

| SAU                   | 3                      |        |

| SDRAMC                | 2                      |        |

| SMC                   | 9                      |        |

| SPI                   | 5                      |        |

| тс                    | 8                      |        |

| ТШМ                   | 2                      |        |

| TWIS                  | 2                      |        |

| USART                 | 10                     |        |

| USBC                  | 5                      |        |

| WDT                   | 2                      |        |

Table 7-5.

Typical Current Consumption by Peripheral<sup>(2)</sup>

Notes: 1. Includes the current consumption on VDDANA.

2. These numbers are valid for the measured condition only and must not be extrapolated to other frequencies.

Table 7-8.

Crystal Oscillator Characteristics

| Symbol               | Parameter                            | Conditions                                                      | Min | Тур  | Max | Unit |

|----------------------|--------------------------------------|-----------------------------------------------------------------|-----|------|-----|------|

| f <sub>OUT</sub>     | Crystal oscillator frequency         |                                                                 | 0.4 |      | 20  | MHz  |

| C <sub>i</sub>       | Internal equivalent load capacitance |                                                                 |     | 1.7  |     | pF   |

| t <sub>STARTUP</sub> |                                      | f <sub>OUT</sub> = 8MHz<br>SCIF.OSCCTRL.GAIN = 1 <sup>(1)</sup> |     | 975  |     | us   |

|                      | Startup time                         | $f_{OUT} = 16MHz$<br>SCIF.OSCCTRL.GAIN = 2 <sup>(1)</sup>       |     | 1100 |     | us   |

Notes: 1. Please refer to the SCIF chapter for details.

## 7.6.2 32KHz Crystal Oscillator (OSC32K) Characteristics

7.6.2.1 Digital Clock Characteristics

The following table describes the characteristics for the oscillator when a digital clock is applied on XIN32.

## Table 7-9. Digital 32KHz Clock Characteristics

| Symbol             | Parameter                   | Conditions | Min                      | Тур    | Max                      | Units |

|--------------------|-----------------------------|------------|--------------------------|--------|--------------------------|-------|

| f <sub>CPXIN</sub> | XIN32 clock frequency       |            |                          | 32.768 | 5000                     | KHz   |

| t <sub>CPXIN</sub> | XIN32 clock period          |            | 200                      |        |                          | ns    |

| t <sub>CHXIN</sub> | XIN32 clock high half-priod |            | 0.4 x t <sub>CPXIN</sub> |        | 0.6 x t <sub>CPXIN</sub> | ns    |

| t <sub>CLXIN</sub> | XIN32 clock low half-priod  |            | 0.4 x t <sub>CPXIN</sub> |        | 0.6 x t <sub>CPXIN</sub> | ns    |

| C <sub>IN</sub>    | XIN32 input capacitance     |            |                          | 2      |                          | pF    |

7.6.2.2 Crystal Oscillator Characteristics

Figure 7-2 and the equation above also applies to the 32KHz oscillator connection. The user must choose a crystal oscillator where the crystal load capacitance  $C_L$  is within the range given in the table. The exact value of  $C_L$  can then be found in the crystal datasheet.

Table 7-10.

32 KHz Crystal Oscillator Characteristics

| Symbol               | Parameter                            | Conditions                                         | Min | Тур    | Max | Unit |

|----------------------|--------------------------------------|----------------------------------------------------|-----|--------|-----|------|

| f <sub>OUT</sub>     | Crystal oscillator frequency         |                                                    |     | 32 768 |     | Hz   |

| t <sub>STARTUP</sub> | Startup time                         | $R_{S} = 50 \text{ kOhm}, C_{L} = 12.5 \text{ pF}$ |     | 2      |     | S    |

| CL                   | Crystal load capacitance             |                                                    | 6   |        | 15  | pF   |

| C <sub>i</sub>       | Internal equivalent load capacitance |                                                    |     | 1.4    |     | pF   |

## 7.9.4.2 Slave mode

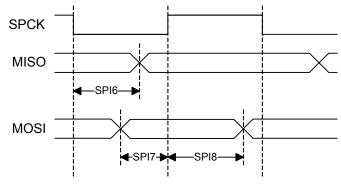

Figure 7-13. SPI Slave Mode With (CPOL= 0 and NCPHA= 1) or (CPOL= 1 and NCPHA= 0)

Figure 7-14. SPI Slave Mode With (CPOL= NCPHA= 0) or (CPOL= NCPHA= 1)

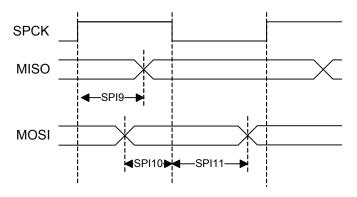

Figure 7-15. SPI Slave Mode NPCS Timing

TWIM and TWIS user interface registers. Please refer to the TWIM and TWIS sections for more information.

Table 7-50. **TWI-Bus Timing Requirements**

|                         |                              |                         | Minin              | num                 | Maxir       | num                  |       |

|-------------------------|------------------------------|-------------------------|--------------------|---------------------|-------------|----------------------|-------|

| Symbol                  | Parameter                    | Mode                    | Requirement        | Device              | Requirement | Device               | Unit  |

|                         | TWOK and TWD rise time       | Standard <sup>(1)</sup> | -                  |                     | 1000        |                      |       |

| t <sub>r</sub>          | TWCK and TWD rise time       | Fast <sup>(1)</sup>     | 20 + 0             | .1 C <sub>b</sub>   | 30          | 0                    | ns    |

|                         |                              | Standard <sup>(1)</sup> | -                  |                     | 30          | 0                    |       |

| t <sub>f</sub>          | TWCK and TWD fall time       | Fast <sup>(1)</sup>     | 20 + 0             | .1 C <sub>b</sub>   | 30          | 0                    | ns ns |

|                         |                              | Standard <sup>(1)</sup> | 4.0                | 4                   |             |                      |       |

| t <sub>HD-STA</sub>     | (Repeated) START hold time   | Fast <sup>(1)</sup>     | 0.6                | t <sub>clkpb</sub>  | -           |                      | μs    |

|                         |                              | Standard <sup>(1)</sup> | 4.7                |                     |             |                      | μs    |

| t <sub>SU-STA</sub>     | (Repeated) START set-up time | Fast <sup>(1)</sup>     | 0.6                | t <sub>clkpb</sub>  | -           |                      |       |

|                         |                              | Standard <sup>(1)</sup> | 4.0                | 4                   |             |                      |       |

| t <sub>SU-STO</sub>     | STOP set-up time             | Fast <sup>(1)</sup>     | 0.6                | 4t <sub>clkpb</sub> | -           |                      | μS    |

|                         | Dete held time               | Standard <sup>(1)</sup> | 0.3 <sup>(2)</sup> | 01                  | 3.45        | 22                   |       |

| t <sub>HD-DAT</sub>     | Data hold time               | Fast <sup>(1)</sup>     | 0.3                | 2t <sub>clkpb</sub> | 0.9         | ??                   | μS    |

|                         | Data act un time             | Standard <sup>(1)</sup> | 250                | 01                  |             |                      |       |

| t <sub>SU-DAT-I2C</sub> | Data set-up time             | Fast <sup>(1)</sup>     | 100                | 2t <sub>clkpb</sub> | -           |                      | ns    |

| t <sub>SU-DAT</sub>     |                              | -                       | -                  | t <sub>clkpb</sub>  | -           |                      | -     |

|                         | TWOK LOW period              | Standard <sup>(1)</sup> | 4.7                | 44                  |             |                      |       |

| t <sub>LOW-I2C</sub>    | TWCK LOW period              | Fast <sup>(1)</sup>     | 1.3                | 4t <sub>clkpb</sub> | -           |                      | μS    |

| t <sub>LOW</sub>        |                              | -                       | -                  | t <sub>clkpb</sub>  | -           |                      | -     |

|                         | TWCK LICH paried             | Standard <sup>(1)</sup> | 4.0                | 04                  |             |                      |       |

| t <sub>HIGH</sub>       | TWCK HIGH period             | Fast <sup>(1)</sup>     | 0.6                | 8t <sub>clkpb</sub> | -           |                      | μS    |

| £                       |                              | Standard <sup>(1)</sup> |                    | 1                   | 100         | 1                    | ld le |

| f <sub>TWCK</sub>       | TWCK frequency               | Fast <sup>(1)</sup>     | -                  |                     | 400         | <sup>12t</sup> clkpb | kHz   |

Notes: 1. Standard mode:  $f_{TWCK} \le 100 \text{ kHz}$ ; fast mode:  $f_{TWCK} > 100 \text{ kHz}$ . 2. A device must internally provide a hold time of at least 300 ns for TWD with reference to the falling edge of TWCK.

Notations:

C<sub>b</sub> = total capacitance of one bus line in pF

$t_{clkpb}$  = period of TWI peripheral bus clock

$t_{prescaled}$  = period of TWI internal prescaled clock (see chapters on TWIM and TWIS)

The maximum  $t_{HD;DAT}$  has only to be met if the device does not stretch the LOW period ( $t_{LOW-I2C}$ ) of TWCK.

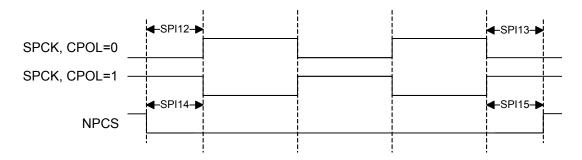

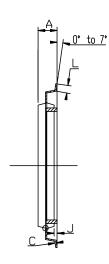

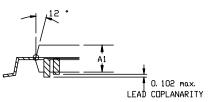

## Figure 8-2. TQFP-64 package drawing

| COMMON DIMENSIONS IN N | ЛМ |

|------------------------|----|

|                        |    |

| SYMBOL | Min   | Max   | NDTES |

|--------|-------|-------|-------|

| A      |       | 1, 20 |       |

| A1     | 0, 95 | 1. 05 |       |

| С      | 0. 09 | 0. 20 |       |

| D      | 12. 0 | O BSC |       |

| D1     | 10, 0 | O BSC |       |

| E      | 12. 0 | O BSC |       |

| E1     | 10. 0 | O BSC |       |

| J      | 0. 05 | 0.15  |       |

| L      | 0, 45 | 0, 75 |       |

| e      | 0, 5  |       |       |

| f      | 0.17  | 0, 27 |       |

## Table 8-5. Device and Package Maximum Weight

|             | Bottoo alla Paokago Maximalii Polgik |                         |

|-------------|--------------------------------------|-------------------------|

| 300         |                                      | mg                      |

| Table 8-6.  | Package Characteristics              |                         |

| Moisture Se | nsitivity Level                      | Jdec J-STD0-20D - MSL 3 |

| Table 8-7.  | Package Reference                    |                         |

# JEDEC Drawing Reference MS-026 JESD97 Classification E3

## 8.3 Soldering Profile

Table 8-14 gives the recommended soldering profile from J-STD-20.

| Table 8-14. | Soldering Profile |

|-------------|-------------------|

|-------------|-------------------|

| Profile Feature                            | Green Package            |

|--------------------------------------------|--------------------------|

| Average Ramp-up Rate (217°C to Peak)       | 3°C/sec                  |

| Preheat Temperature 175°C ±25°C            | Min. 150 °C, Max. 200 °C |

| Temperature Maintained Above 217°C         | 60-150 sec               |

| Time within 5.C of Actual Peak Temperature | 30 sec                   |

| Peak Temperature Range                     | 260 °C                   |

| Ramp-down Rate                             | 6 °C/sec                 |

| Time 25 C to Peak Temperature              | Max. 8 minutes           |

Note: It is recommended to apply a soldering temperature higher than 250°C. A maximum of three reflow passes is allowed per component.

## 10.1.5 SCIF

## 1 PLLCOUNT value larger than zero can cause PLLEN glitch

Initializing the PLLCOUNT with a value greater than zero creates a glitch on the PLLEN signal during asynchronous wake up.

#### Fix/Workaround

The lock-masking mechanism for the PLL should not be used.

The PLLCOUNT field of the PLL Control Register should always be written to zero.

#### 2 PLL lock might not clear after disable

Under certain circumstances, the lock signal from the Phase Locked Loop (PLL) oscillator may not go back to zero after the PLL oscillator has been disabled. This can cause the propagation of clock signals with the wrong frequency to parts of the system that use the PLL clock.

## Fix/Workaround

PLL must be turned off before entering STOP, DEEPSTOP or STATIC sleep modes. If PLL has been turned off, a delay of 30us must be observed after the PLL has been enabled again before the SCIF.PLL0LOCK bit can be used as a valid indication that the PLL is locked.

## 3 BOD33 reset locks the device

If BOD33 is enabled as a reset source (SCIF.BOD33.CTRL=0x1) and when VDDIN\_33 power supply voltage falls below the BOD33 voltage (SCIF.BOD33.LEVEL), the device is locked permanently under reset even if the power supply goes back above BOD33 reset level. In order to unlock the device, an external reset event should be applied on RESET\_N. **Fix/Workaround**

Use an external BOD on VDDIN\_33 or an external reset source.

#### 10.1.6 SPI

## 1 SPI data transfer hangs with CSR0.CSAAT==1 and MR.MODFDIS==0

When CSR0.CSAAT==1 and mode fault detection is enabled (MR.MODFDIS==0), the SPI module will not start a data transfer. **Fix/Workaround**

#### Fix/Workaround

Disable mode fault detection by writing a one to MR.MODFDIS.

#### 2 Disabling SPI has no effect on the SR.TDRE bit

Disabling SPI has no effect on the SR.TDRE bit whereas the write data command is filtered when SPI is disabled. Writing to TDR when SPI is disabled will not clear SR.TDRE. If SPI is disabled during a PDCA transfer, the PDCA will continue to write data to TDR until its buffer is empty, and this data will be lost.

#### Fix/Workaround

Disable the PDCA, add two NOPs, and disable the SPI. To continue the transfer, enable the SPI and PDCA.

## 3 SPI disable does not work in SLAVE mode

SPI disable does not work in SLAVE mode.

## Fix/Workaround

Read the last received data, then perform a software reset by writing a one to the Software Reset bit in the Control Register (CR.SWRST).

# **Table of Contents**

| 1 | Descr  | ription                              | 3  |

|---|--------|--------------------------------------|----|

| 2 | Overv  | /iew                                 | 5  |

|   | 2.1    | Block diagram                        | 5  |

|   | 2.2    | Configuration Summary                | 6  |

| 3 | Packa  | age and Pinout                       | 8  |

|   | 3.1    | Package                              | 8  |

|   | 3.2    | Peripheral Multiplexing on I/O lines | 11 |

|   | 3.3    | Signals Description                  | 18 |

|   | 3.4    | I/O Line Considerations              | 24 |

| 4 | Proce  | essor and Architecture               | 25 |

|   | 4.1    | Features                             | 25 |

|   | 4.2    | AVR32 Architecture                   | 25 |

|   | 4.3    | The AVR32UC CPU                      | 26 |

|   | 4.4    | Programming Model                    | 30 |

|   | 4.5    | Exceptions and Interrupts            | 34 |

| 5 | Memo   | ories                                | 39 |

|   | 5.1    | Embedded Memories                    | 39 |

|   | 5.2    | Physical Memory Map                  | 40 |

|   | 5.3    | Peripheral Address Map               | 41 |

|   | 5.4    | CPU Local Bus Mapping                | 43 |

| 6 | Suppl  | ly and Startup Considerations        | 46 |

|   | 6.1    | Supply Considerations                | 46 |

|   | 6.2    | Startup Considerations               | 49 |

| 7 | Electr | rical Characteristics                | 50 |

|   | 7.1    | Absolute Maximum Ratings*            | 50 |

|   | 7.2    | Supply Characteristics               | 50 |

|   | 7.3    | Maximum Clock Frequencies            | 51 |

|   | 7.4    | Power Consumption                    | 51 |

|   | 7.5    | I/O Pin Characteristics              | 55 |

|   | 7.6    | Oscillator Characteristics           | 57 |

|   | 7.7    | Flash Characteristics                | 60 |

|   | 7.8    | Analog Characteristics               | 61 |