#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | AVR                                                                         |

| Core Size                  | 32-Bit Single-Core                                                          |

| Speed                      | 66MHz                                                                       |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB      |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                |

| Number of I/O              | 45                                                                          |

| Program Memory Size        | 64KB (64K x 8)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 16K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                   |

| Data Converters            | A/D 11x12b; D/A 2x12b                                                       |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 64-VFQFN Exposed Pad                                                        |

| Supplier Device Package    | 64-QFN (9x9)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at32uc3c264c-z2ut |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

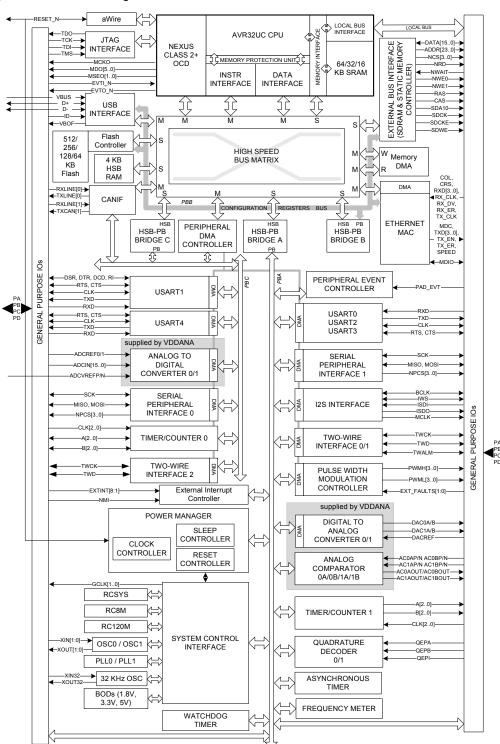

# 2. Overview

# 2.1 Block diagram

# Figure 2-1. Block diagram

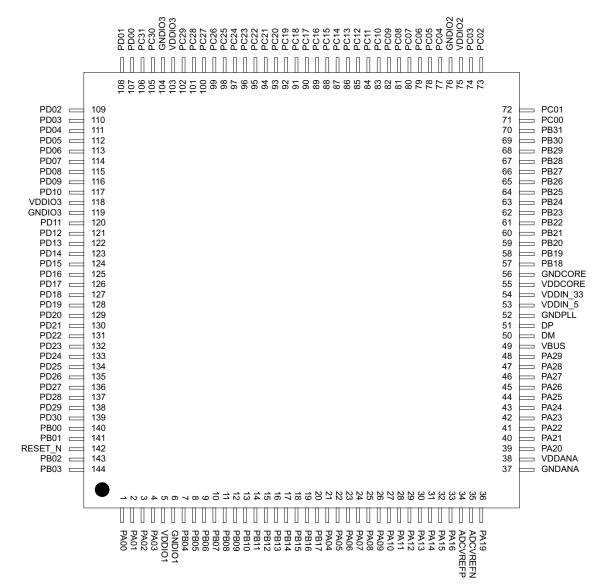

# Figure 3-3. LQFP144 Pinout

| Table 3-1. | GPIO Controller Function Multiplexing |

|------------|---------------------------------------|

|------------|---------------------------------------|

| TQFP           |             |             |      | G           |        |                    |                 |                      | GPIO fu           | unction           |                  |   |

|----------------|-------------|-------------|------|-------------|--------|--------------------|-----------------|----------------------|-------------------|-------------------|------------------|---|

| /<br>QFN<br>64 | TQFP<br>100 | LQFP<br>144 | PIN  | P<br>I<br>O | Supply | Pin<br>Type<br>(1) | А               | В                    | с                 | D                 | E                | F |

|                |             | 124         | PD15 | 111         | VDDIO3 | x1/x2              | TC0 - A0        | USART3 -<br>TXD      | EBI -<br>ADDR[11] |                   |                  |   |

|                |             | 125         | PD16 | 112         | VDDIO3 | x1/x2              | TC0 - B0        | USART3 -<br>RXD      | EBI -<br>ADDR[12] |                   |                  |   |

|                |             | 126         | PD17 | 113         | VDDIO3 | x1/x2              | TC0 - A1        | USART3 -<br>CTS      | EBI -<br>ADDR[13] | USART3-<br>CLK    |                  |   |

|                |             | 127         | PD18 | 114         | VDDIO3 | x1/x2              | TC0 - B1        | USART3 -<br>RTS      | EBI -<br>ADDR[14] |                   |                  |   |

|                |             | 128         | PD19 | 115         | VDDIO3 | x1/x2              | TC0 - A2        |                      | EBI -<br>ADDR[15] |                   |                  |   |

|                |             | 129         | PD20 | 116         | VDDIO3 | x1/x2              | TC0 - B2        |                      | EBI -<br>ADDR[16] |                   |                  |   |

| 57             | 88          | 130         | PD21 | 117         | VDDIO3 | x1/x2              | USART3 -<br>TXD | EIC -<br>EXTINT[0]   | EBI -<br>ADDR[17] | QDEC1 -<br>QEPI   |                  |   |

|                | 89          | 131         | PD22 | 118         | VDDIO1 | x1/x2              | USART3 -<br>RXD | TC0 - A2             | EBI -<br>ADDR[18] | SCIF -<br>GCLK[0] |                  |   |

|                | 90          | 132         | PD23 | 119         | VDDIO1 | x1/x2              | USART3 -<br>CTS | USART3 -<br>CLK      | EBI -<br>ADDR[19] | QDEC1 -<br>QEPA   |                  |   |

|                | 91          | 133         | PD24 | 120         | VDDIO1 | x1/x2              | USART3 -<br>RTS | EIC -<br>EXTINT[8]   | EBI -<br>NWE1     | QDEC1 -<br>QEPB   |                  |   |

|                |             | 134         | PD25 | 121         | VDDIO1 | x1/x2              | TC0 -<br>CLK0   | USBC - ID            | EBI -<br>NWE0     |                   | USART4 -<br>CLK  |   |

|                |             | 135         | PD26 | 122         | VDDIO1 | x1/x2              | TC0 -<br>CLK1   | USBC -<br>VBOF       | EBI - NRD         |                   |                  |   |

| 58             | 92          | 136         | PD27 | 123         | VDDIO1 | x1/x2              | USART0 -<br>TXD | CANIF -<br>RXLINE[0] | EBI -<br>NCS[1]   | TC0 - A0          | MACB -<br>RX_ER  |   |

| 59             | 93          | 137         | PD28 | 124         | VDDIO1 | x1/x2              | USART0 -<br>RXD | CANIF -<br>TXLINE[0] | EBI -<br>NCS[2]   | TC0 - B0          | MACB -<br>RX_DV  |   |

| 60             | 94          | 138         | PD29 | 125         | VDDIO1 | x1/x2              | USART0 -<br>CTS | EIC -<br>EXTINT[6]   | USART0 -<br>CLK   | TC0 -<br>CLK0     | MACB -<br>TX_CLK |   |

| 61             | 95          | 139         | PD30 | 126         | VDDIO1 | x1/x2              | USART0 -<br>RTS | EIC -<br>EXTINT[3]   | EBI -<br>NWAIT    | TC0 - A1          | MACB -<br>TX_EN  |   |

Note: 1. Refer to "Electrical Characteristics" on page 50 for a description of the electrical properties of the pin types used. See Section 3.3 for a description of the various peripheral signals.

# 3.2.2 Peripheral Functions

Each GPIO line can be assigned to one of several peripheral functions. The following table describes how the various peripheral functions are selected. The last listed function has priority in case multiple functions are enabled on the same pin.

| Table 3-2. | Peripheral Functions |

|------------|----------------------|

|------------|----------------------|

| Function                              | Description                               |

|---------------------------------------|-------------------------------------------|

| GPIO Controller Function multiplexing | GPIO and GPIO peripheral selection A to F |

| Nexus OCD AUX port connections        | OCD trace system                          |

# Table 3-7.Signal Description List

| Signal Name          | Function                          | Туре            | Active<br>Level | Comments |

|----------------------|-----------------------------------|-----------------|-----------------|----------|

| SDCK                 | SDRAM Clock                       | Output          |                 |          |

| SDCKE                | SDRAM Clock Enable                | Output          |                 |          |

| SDWE                 | SDRAM Write Enable                | Output          | Low             |          |

|                      | External Interrupt Co             | ntroller - EIC  |                 |          |

| EXTINT[8:1]          | External Interrupt Pins           | Input           |                 |          |

| NMI_N = EXTINT[0]    | Non-Maskable Interrupt Pin        | Input           | Low             |          |

|                      | General Purpose Input/Output - GP | IOA, GPIOB,     | GPIOC, GPI      | OD       |

| PA[29:19] - PA[16:0] | Parallel I/O Controller GPIOA     | I/O             |                 |          |

| PB[31:0]             | Parallel I/O Controller GPIOB     | I/O             |                 |          |

| PC[31:0]             | Parallel I/O Controller GPIOC     | I/O             |                 |          |

| PD[30:0]             | Parallel I/O Controller GPIOD     | I/O             |                 |          |

|                      | Inter-IC Sound (I2S) C            | ontroller - IIS | С               |          |

| IMCK                 | I2S Master Clock                  | Output          |                 |          |

| ISCK                 | I2S Serial Clock                  | I/O             |                 |          |

| ISDI                 | I2S Serial Data In                | Input           |                 |          |

| ISDO                 | I2S Serial Data Out               | Output          |                 |          |

| IWS                  | I2S Word Select                   | I/O             |                 |          |

|                      | JTAG                              |                 |                 |          |

| тск                  | Test Clock                        | Input           |                 |          |

| TDI                  | Test Data In                      | Input           |                 |          |

| TDO                  | Test Data Out                     | Output          |                 |          |

| TMS                  | Test Mode Select                  | Input           |                 |          |

|                      | Ethernet MAC -                    | МАСВ            |                 | •        |

| COL                  | Collision Detect                  | Input           |                 |          |

| CRS                  | Carrier Sense and Data Valid      | Input           |                 |          |

| MDC                  | Management Data Clock             | Output          |                 |          |

| MDIO                 | Management Data Input/Output      | I/O             |                 |          |

| RXD[3:0]             | Receive Data                      | Input           |                 |          |

# 5. Memories

# 5.1 Embedded Memories

- Internal High-Speed Flash (See Table 5-1 on page 40)

- 512 Kbytes

- 256 Kbytes

- 128 Kbytes

- 64 Kbytes

- 0 Wait State Access at up to 33 MHz in Worst Case Conditions

- 1 Wait State Access at up to 66 MHz in Worst Case Conditions

- Pipelined Flash Architecture, allowing burst reads from sequential Flash locations, hiding penalty of 1 wait state access

- Pipelined Flash Architecture typically reduces the cycle penalty of 1 wait state operation to only 15% compared to 0 wait state operation

- 100 000 Write Cycles, 15-year Data Retention Capability

- Sector Lock Capabilities, Bootloader Protection, Security Bit

- 32 Fuses, Erased During Chip Erase

- User Page For Data To Be Preserved During Chip Erase

- Internal High-Speed SRAM, Single-cycle access at full speed (See Table 5-1 on page 40)

- 64 Kbytes

- 32 Kbytes

- 16 Kbytes

- Supplementary Internal High-Speed System SRAM (HSB RAM), Single-cycle access at full speed

- Memory space available on System Bus for peripherals data.

- 4 Kbytes

| Symbol | Parameter                  | Conditions                                        | Min | Тур | Max | Units |

|--------|----------------------------|---------------------------------------------------|-----|-----|-----|-------|

| RES    | Resolution                 | Differential mode,                                |     |     | 10  | Bit   |

| INL    | Integral Non-Linearity     | $V_{VDDANA} = 5V,$                                |     |     | 1.5 | LSB   |

| DNL    | Differential Non-Linearity | $V_{ADCREF0} = 3V,$                               |     |     | 1.5 | LSB   |

|        | Offset error               | ADCFIA.SEQCFGn.SRES = 1,<br>S/H gain from 1 to 16 | -25 |     | 25  | mV    |

|        | Gain error                 | $(F_{adc} = 1.5MHz)$                              | -15 |     | 15  | mV    |

Table 7-36. ADC and S/H Transfer Characteristics (Continued)10-bit Resolution Mode and S/H gain from 1 to 16<sup>(1)</sup>

Note: 1. The measures are done without any I/O activity on VDDANA/GNDANA power domain.

# 7.8.7 Digital to Analog Converter (DAC) Characteristics

Table 7-37.

Channel Conversion Time and DAC Clock

| Symbol               | Parameter                 | Conditions                   | Min | Тур | Max                 | Units |

|----------------------|---------------------------|------------------------------|-----|-----|---------------------|-------|

| f <sub>DAC</sub>     | DAC clock frequency       |                              |     |     | 1                   | MHz   |

| t <sub>STARTUP</sub> | Startup time              |                              |     |     | 3                   | μs    |

|                      | Conversion time (latency) | No S/H enabled, internal DAC |     |     | 1                   | μs    |

| t <sub>CONV</sub>    |                           | One S/H                      |     |     | 1.5                 | μs    |

|                      |                           | Two S/H                      |     |     | 2                   | μs    |

|                      | Throughput rate           |                              |     |     | 1/t <sub>CONV</sub> | MSPS  |

# Table 7-38. External Voltage Reference Input

| Symbol  | Parameter                  | Conditions | Min | Тур | Мах                      | Units |

|---------|----------------------------|------------|-----|-----|--------------------------|-------|

| VDACREF | DACREF input voltage range |            | 1.2 |     | V <sub>VDDANA</sub> -0.7 | V     |

# Table 7-39. DAC Outputs

| Symbol            | Parameter          | Conditions                  | Min | Тур | Max                      | Units |

|-------------------|--------------------|-----------------------------|-----|-----|--------------------------|-------|

|                   | Output range       | with external DAC reference | 0.2 |     | VDACREF                  | V     |

|                   | Output range       | with internal DAC reference | 0.2 |     | V <sub>VDDANA</sub> -0.7 | v     |

| C <sub>LOAD</sub> | Output capacitance |                             | 0   |     | 100                      | pF    |

| R <sub>LOAD</sub> | Output resitance   |                             | 2   |     |                          | kΩ    |

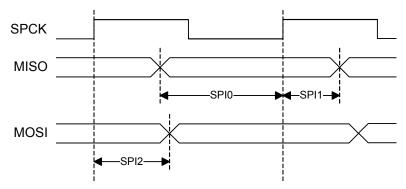

# Maximum SPI Frequency, Master Output

The maximum SPI master output frequency is given by the following formula:

$$f_{SPCKMAX} = MIN(f_{PINMAX}, \frac{1}{SPIn}, \frac{f_{CLKSPI} \times 2}{9})$$

Where *SPIn* is the MOSI delay, USPI2 or USPI5 depending on CPOL and NCPHA.  $f_{PINMAX}$  is the maximum frequency of the SPI pins. Please refer to the I/O Pin Characteristics section for the maximum frequency of the pins.  $f_{CLKSPI}$  is the maximum frequency of the CLK\_SPI. Refer to the SPI chapter for a description of this clock.

# Maximum SPI Frequency, Master Input

The maximum SPI master input frequency is given by the following formula:

$$f_{SPCKMAX} = MIN(\frac{1}{SPIn + t_{VALID}}, \frac{f_{CLKSPI} \times 2}{9})$$

Where *SPIn* is the MISO setup and hold time, USPI0 + USPI1 or USPI3 + USPI4 depending on CPOL and NCPHA.  $T_{VALID}$  is the SPI slave response time. Please refer to the SPI slave datasheet for  $T_{VALID}$ .  $f_{CLKSPI}$  is the maximum frequency of the CLK\_SPI. Refer to the SPI chapter for a description of this clock.

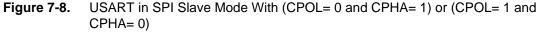

7.9.3.2 Slave mode

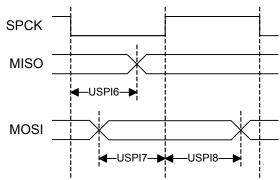

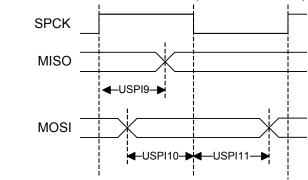

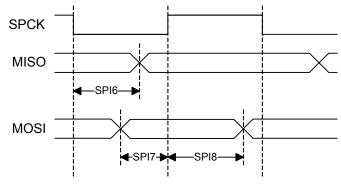

**Figure 7-9.** USART in SPI Slave Mode With (CPOL= CPHA= 0) or (CPOL= CPHA= 1)

Table 7-47.

USART in SPI mode Timing, Slave Mode<sup>(1)</sup>

| Symbol | Parameter                         | Conditions       | Min                                | Max | Units |

|--------|-----------------------------------|------------------|------------------------------------|-----|-------|

| USPI6  | SPCK falling to MISO delay        |                  |                                    | 27  | ns    |

| USPI7  | MOSI setup time before SPCK rises |                  | $t_{SAMPLE}^{(2)} + t_{CLK_USART}$ |     | ns    |

| USPI8  | MOSI hold time after SPCK rises   |                  | 0                                  |     | ns    |

| USPI9  | SPCK rising to MISO delay         |                  |                                    | 28  | ns    |

| USPI10 | MOSI setup time before SPCK falls | external         | $t_{SAMPLE}^{(2)} + t_{CLK_USART}$ |     | ns    |

| USPI11 | MOSI hold time after SPCK falls   | capacitor = 40pF | 0                                  |     | ns    |

| USPI12 | NSS setup time before SPCK rises  |                  | 33                                 |     | ns    |

| USPI13 | NSS hold time after SPCK falls    |                  | 0                                  |     | ns    |

| USPI14 | NSS setup time before SPCK falls  |                  | 33                                 |     | ns    |

| USPI15 | NSS hold time after SPCK rises    |                  | 0                                  |     | ns    |

Note: 1. These values are based on simulation and characterization of other AVR microcontrollers manufactured in the same process technology. These values are not covered by test limits in production.

2. Where:

$$t_{SAMPLE} = t_{SPCK} - \left( \left\lfloor \frac{t_{SPCK}}{2 \times t_{CLKUSART}} \right\rfloor + \frac{1}{2} \right) \times t_{CLKUSART}$$

# Maximum SPI Frequency, Slave Input Mode

The maximum SPI slave input frequency is given by the following formula:

$$f_{SPCKMAX} = MIN(\frac{f_{CLKSPI} \times 2}{9}, \frac{1}{SPIn})$$

Where *SPIn* is the MOSI setup and hold time, USPI7 + USPI8 or USPI10 + USPI11 depending on CPOL and NCPHA.  $f_{CLKSPI}$  is the maximum frequency of the CLK\_SPI. Refer to the SPI chapter for a description of this clock.

# Maximum SPI Frequency, Slave Output Mode

The maximum SPI slave output frequency is given by the following formula:

$$f_{SPCKMAX} = MIN(\frac{f_{CLKSPI} \times 2}{9}, f_{PINMAX}, \frac{1}{SPIn + t_{SETUP}})$$

Where *SPIn* is the MISO delay, USPI6 or USPI9 depending on CPOL and NCPHA.  $T_{SETUP}$  is the SPI master setup time. Please refer to the SPI masterdatasheet for  $T_{SETUP}$ .  $f_{CLKSPI}$  is the maximum frequency of the CLK\_SPI. Refer to the SPI chapter for a description of this clock.  $f_{PINMAX}$  is the maximum frequency of the SPI pins. Please refer to the I/O Pin Characteristics section for the maximum frequency of the pins.

# 7.9.4 SPI Timing

7.9.4.1 Master mode

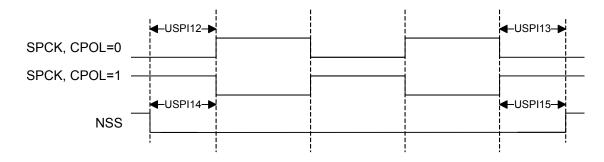

Figure 7-11. SPI Master Mode With (CPOL= NCPHA= 0) or (CPOL= NCPHA= 1)

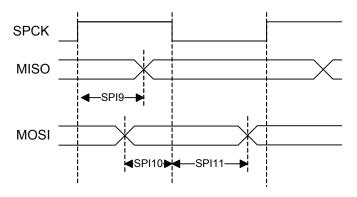

# 7.9.4.2 Slave mode

Figure 7-13. SPI Slave Mode With (CPOL= 0 and NCPHA= 1) or (CPOL= 1 and NCPHA= 0)

Figure 7-14. SPI Slave Mode With (CPOL= NCPHA= 0) or (CPOL= NCPHA= 1)

Figure 7-15. SPI Slave Mode NPCS Timing

| Symbol | Parameter                         | Conditions       | Min | Max | Units |

|--------|-----------------------------------|------------------|-----|-----|-------|

| SPI6   | SPCK falling to MISO delay        |                  |     | 29  | ns    |

| SPI7   | MOSI setup time before SPCK rises | _                | 0   |     | ns    |

| SPI8   | MOSI hold time after SPCK rises   |                  | 6.5 |     | ns    |

| SPI9   | SPCK rising to MISO delay         |                  |     | 30  | ns    |

| SPI10  | MOSI setup time before SPCK falls | external         | 0   |     | ns    |

| SPI11  | MOSI hold time after SPCK falls   | capacitor = 40pF | 5   |     | ns    |

| SPI12  | NPCS setup time before SPCK rises |                  | 0   |     | ns    |

| SPI13  | NPCS hold time after SPCK falls   |                  | 1.5 |     | ns    |

| SPI14  | NPCS setup time before SPCK falls |                  | 0   |     | ns    |

| SPI15  | NPCS hold time after SPCK rises   |                  | 1.5 |     | ns    |

**Table 7-49.**SPI Timing, Slave Mode<sup>(1)</sup>

Note: 1. These values are based on simulation and characterization of other AVR microcontrollers manufactured in the same process technology. These values are not covered by test limits in production.

## Maximum SPI Frequency, Slave Input Mode

The maximum SPI slave input frequency is given by the following formula:

$$f_{SPCKMAX} = MIN(f_{CLKSPI}, \frac{1}{SPIn})$$

Where *SPIn* is the MOSI setup and hold time, SPI7 + SPI8 or SPI10 + SPI11 depending on CPOL and NCPHA. $f_{CLKSPI}$  is the maximum frequency of the CLK\_SPI. Refer to the SPI chapter for a description of this clock.

# Maximum SPI Frequency, Slave Output Mode

The maximum SPI slave output frequency is given by the following formula:

$$f_{SPCKMAX} = MIN(f_{PINMAX}, \frac{1}{SPIn + t_{SETUP}})$$

Where *SPIn* is the MISO delay, SPI6 or SPI9 depending on CPOL and NCPHA.  $t_{SETUP}$  is the SPI master setup time. Please refer to the SPI masterdatasheet for  $t_{SETUP}$ .  $f_{PINMAX}$  is the maximum frequency of the SPI pins. Please refer to the I/O Pin Characteristics section for the maximum frequency of the pins.

# 7.9.5 TWIM/TWIS Timing

Figure 7-50 shows the TWI-bus timing requirements and the compliance of the device with them. Some of these requirements ( $t_r$  and  $t_f$ ) are met by the device without requiring user intervention. Compliance with the other requirements ( $t_{HD-STA}$ ,  $t_{SU-STA}$ ,  $t_{SU-STO}$ ,  $t_{HD-DAT}$ ,  $t_{SU-DAT-I2C}$ ,  $t_{LOW-I2C}$ ,  $t_{HIGH}$ , and  $f_{TWCK}$ ) requires user intervention through appropriate programming of the relevant

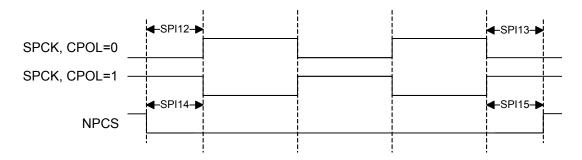

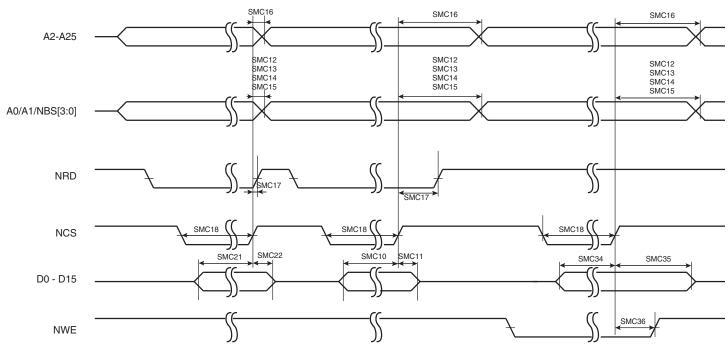

# 7.9.7 EBI Timings

See EBI I/O lines description for more details.

Table 7-52.SMC Clock Signal.

| Symbol                  | Parameter                      | Max <sup>(1)</sup> | Units |

|-------------------------|--------------------------------|--------------------|-------|

| 1/(t <sub>CPSMC</sub> ) | SMC Controller clock frequency | f <sub>cpu</sub>   | MHz   |

Note: 1. The maximum frequency of the SMC interface is the same as the max frequency for the HSB.

# Table 7-53. SMC Read Signals with Hold Settings<sup>(1)</sup>

| Symbol            | Parameter                                  | Conditions                                     | Min                                                      | Units |  |

|-------------------|--------------------------------------------|------------------------------------------------|----------------------------------------------------------|-------|--|

|                   | NR                                         | D Controlled (READ_MODE                        | = 1)                                                     |       |  |

| SMC <sub>1</sub>  | Data setup before NRD high                 |                                                | 32.5                                                     |       |  |

| SMC <sub>2</sub>  | Data hold after NRD high                   |                                                | 0                                                        |       |  |

| SMC <sub>3</sub>  | NRD high to NBS0/A0 change <sup>(2)</sup>  | V <sub>VDD</sub> = 3.0V,                       | nrd hold length * tcpsmc - 1.5                           |       |  |

| SMC <sub>4</sub>  | NRD high to NBS1 change <sup>(2)</sup>     | drive strength of the pads set to the lowest,  | nrd hold length * tcpsмc - 0                             | ns    |  |

| SMC <sub>5</sub>  | NRD high to NBS2/A1 change <sup>(2)</sup>  | external capacitor =                           | nrd hold length * tсрѕмс - 0                             |       |  |

| SMC <sub>7</sub>  | NRD high to A2 - A25 change <sup>(2)</sup> | 40pF                                           | nrd hold length * tcpsmc - 5.6                           |       |  |

| SMC <sub>8</sub>  | NRD high to NCS inactive <sup>(2)</sup>    |                                                | (nrd hold length - ncs rd hold length) *<br>tcpsmc - 1.3 | _     |  |

| SMC <sub>9</sub>  | NRD pulse width                            |                                                | nrd pulse length * tcpsmc - 0.6                          |       |  |

|                   | NR                                         | D Controlled (READ_MODE                        | = 0)                                                     |       |  |

| SMC <sub>10</sub> | Data setup before NCS high                 |                                                | 34.1                                                     |       |  |

| SMC <sub>11</sub> | Data hold after NCS high                   |                                                | 0                                                        |       |  |

| SMC <sub>12</sub> | NCS high to NBS0/A0 change <sup>(2)</sup>  | V <sub>VDD</sub> = 3.0V,                       | ncs rd hold length * tcpsмc - 3                          |       |  |

| SMC <sub>13</sub> | NCS high to NBS0/A0 change <sup>(2)</sup>  | $v_{VDD} = 3.0 v_{,}$<br>drive strength of the | ncs rd hold length * tcpsmc - 2                          |       |  |

| SMC <sub>14</sub> | NCS high to NBS2/A1 change <sup>(2)</sup>  | pads set to the lowest,                        | ncs rd hold length * tcpsmc - 1.1                        | ns    |  |

| SMC <sub>16</sub> | NCS high to A2 - A25 change <sup>(2)</sup> | external capacitor =<br>40pF                   | ncs rd hold length * tcpsмc - 7.2                        |       |  |

| SMC <sub>17</sub> | NCS high to NRD inactive <sup>(2)</sup>    |                                                | (ncs rd hold length - nrd hold length) *<br>tcPSMc - 2.2 |       |  |

| SMC <sub>18</sub> | NCS pulse width                            |                                                | ncs rd pulse length * tcpsmc - 3                         |       |  |

Note: 1. These values are based on simulation and characterization of other AVR microcontrollers manufactured in the same process technology. These values are not covered by test limits in production.

2. hold length = total cycle duration - setup duration - pulse duration. "hold length" is for "ncs rd hold length" or "nrd hold length".

| Symbol            | Parameter                        | Conditions                                       | Min                                   | Units |

|-------------------|----------------------------------|--------------------------------------------------|---------------------------------------|-------|

| SMC <sub>37</sub> | NWE rising to A2-A25 valid       |                                                  | 8.7                                   |       |

| SMC <sub>38</sub> | NWE rising to NBS0/A0 valid      | _                                                | 7.6                                   |       |

| SMC <sub>40</sub> | NWE rising to A1/NBS2 change     | $V_{VDD} = 3.0V,$                                | 8.7                                   |       |

| SMC <sub>42</sub> | NWE rising to NCS rising         | drive strength of the pads<br>set to the lowest, | 8.4                                   | ns    |

| SMC <sub>43</sub> | Data Out valid before NWE rising | external capacitor = 40pF                        | (nwe pulse length - 1) * tcpsмc - 1.2 |       |

| SMC <sub>44</sub> | Data Out valid after NWE rising  |                                                  | 8.4                                   |       |

| SMC <sub>45</sub> | NWE pulse width                  |                                                  | nwe pulse length * tcpsмc - 0         |       |

Table 7-56.

SMC Write Signals with No Hold Settings (NWE Controlled only)<sup>(1)</sup>

Note: 1. These values are based on simulation and characterization of other AVR microcontrollers manufactured in the same process technology. These values are not covered by test limits in production.

Figure 7-17. SMC Signals for NCS Controlled Accesses

| Symbol               | Parameter                                | Conditions                                                                                                                  | Min | Units          |

|----------------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-----|----------------|

| SDRAMC <sub>1</sub>  | SDCKE high before SDCK rising edge       |                                                                                                                             | 5.6 |                |

| SDRAMC <sub>2</sub>  | SDCKE low after SDCK rising edge         |                                                                                                                             | 7.3 |                |

| SDRAMC <sub>3</sub>  | SDCKE low before SDCK rising edge        |                                                                                                                             | 6.8 |                |

| SDRAMC <sub>4</sub>  | SDCKE high after SDCK rising edge        |                                                                                                                             | 8.3 |                |

| SDRAMC <sub>5</sub>  | SDCS low before SDCK rising edge         |                                                                                                                             | 6.1 |                |

| SDRAMC <sub>6</sub>  | SDCS high after SDCK rising edge         |                                                                                                                             | 8.4 |                |

| SDRAMC <sub>7</sub>  | RAS low before SDCK rising edge          |                                                                                                                             | 7   |                |

| SDRAMC <sub>8</sub>  | RAS high after SDCK rising edge          |                                                                                                                             | 7.7 |                |

| SDRAMC <sub>9</sub>  | SDA10 change before SDCK rising edge     |                                                                                                                             | 6.4 | -<br>-<br>- ns |

| SDRAMC <sub>10</sub> | SDA10 change after SDCK rising edge      |                                                                                                                             | 7.1 |                |

| SDRAMC <sub>11</sub> | Address change before SDCK rising edge   | $V_{VDD} = 3.0V,$                                                                                                           | 4.7 |                |

| SDRAMC <sub>12</sub> | Address change after SDCK rising edge    | drive strength of the pads set to<br>the highest,<br>external capacitor = 40pF on<br>SDRAM pins<br>except 8 pF on SDCK pins | 4.4 |                |

| SDRAMC <sub>13</sub> | Bank change before SDCK rising edge      |                                                                                                                             | 6.2 |                |

| SDRAMC <sub>14</sub> | Bank change after SDCK rising edge       |                                                                                                                             | 6.9 | -              |

| SDRAMC <sub>15</sub> | CAS low before SDCK rising edge          |                                                                                                                             | 6.6 |                |

| SDRAMC <sub>16</sub> | CAS high after SDCK rising edge          |                                                                                                                             | 7.8 |                |

| SDRAMC <sub>17</sub> | DQM change before SDCK rising edge       |                                                                                                                             | 6   | -              |

| SDRAMC <sub>18</sub> | DQM change after SDCK rising edge        |                                                                                                                             | 6.7 | -              |

| SDRAMC <sub>19</sub> | D0-D15 in setup before SDCK rising edge  |                                                                                                                             | 6.4 | -              |

| SDRAMC <sub>20</sub> | D0-D15 in hold after SDCK rising edge    | _                                                                                                                           | 0   | -              |

| SDRAMC <sub>23</sub> | SDWE low before SDCK rising edge         |                                                                                                                             | 7   |                |

| SDRAMC <sub>24</sub> | SDWE high after SDCK rising edge         |                                                                                                                             | 7.4 |                |

| SDRAMC <sub>25</sub> | D0-D15 Out valid before SDCK rising edge |                                                                                                                             | 5.2 |                |

| SDRAMC <sub>26</sub> | D0-D15 Out valid after SDCK rising edge  |                                                                                                                             | 5.6 | 1              |

Note: 1. These values are based on simulation and characterization of other AVR microcontrollers manufactured in the same process technology. These values are not covered by test limits in production.

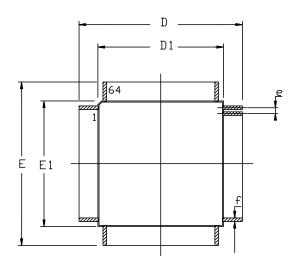

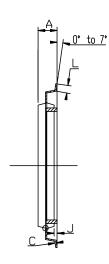

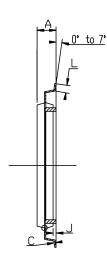

# Figure 8-2. TQFP-64 package drawing

| COMMON DIMENSIONS IN N | ЛМ |

|------------------------|----|

|                        |    |

| SYMBOL | Min       | Max   | NDTES |

|--------|-----------|-------|-------|

| A      |           | 1, 20 |       |

| A1     | 0, 95     | 1. 05 |       |

| С      | 0. 09     | 0. 20 |       |

| D      | 12. 0     | O BSC |       |

| D1     | 10,00 BSC |       |       |

| E      | 12.00 BSC |       |       |

| E1     | 10.00 BSC |       |       |

| J      | 0. 05     | 0.15  |       |

| L      | 0, 45     | 0, 75 |       |

| e      | 0, 50 BSC |       |       |

| f      | 0.17      | 0, 27 |       |

# Table 8-5. Device and Package Maximum Weight

|             | Bottoo alla Paokago Maximalii Polgik |                         |

|-------------|--------------------------------------|-------------------------|

| 300         |                                      | mg                      |

| Table 8-6.  | Package Characteristics              |                         |

| Moisture Se | nsitivity Level                      | Jdec J-STD0-20D - MSL 3 |

| Table 8-7.  | Package Reference                    |                         |

# JEDEC Drawing Reference MS-026 JESD97 Classification E3

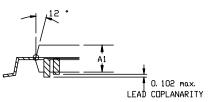

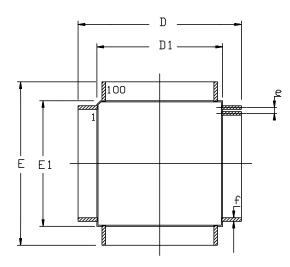

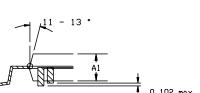

# Figure 8-3. TQFP-100 package drawing

| COMMON DIMENSIONS IN MM |           |       |       |  |

|-------------------------|-----------|-------|-------|--|

| SYMBOL                  | Min       | Max   | NDTES |  |

| А                       |           | 1. 20 |       |  |

| A1                      | 0, 95     | 1. 05 |       |  |

| С                       | 0. 09     | 0, 20 |       |  |

| D                       | 16. 0     |       |       |  |

| D1                      | 14.00 BSC |       |       |  |

| E                       | 16.00 BSC |       |       |  |

| E1                      | 14.00 BSC |       |       |  |

| J                       | 0. 05     | 0.15  |       |  |

| L                       | 0.45      | 0, 75 |       |  |

| e                       | 0, 50 BSC |       |       |  |

| f                       | 0.17      | 0. 27 |       |  |

0. 102 max. LEAD COPLANARITY

# Table 8-8. Device and Package Maximum Weight

| 500 | mg |

|-----|----|

|     |    |

# Table 8-9. Package Characteristics

| loisture Sensitivity Level | Jdec J-STD0-20D - MSL 3 |

|----------------------------|-------------------------|

|----------------------------|-------------------------|

# Table 8-10. Package Reference

| JEDEC Drawing Reference | MS-026 |

|-------------------------|--------|

| JESD97 Classification   | E3     |

|         |      | 4 | SPI bad serial clock generation on 2nd chip_select when SCBR=1, CPOL=1, and NCPHA=0                                                                                                                                                                                                                                                                |

|---------|------|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |      |   | When multiple chip selects (CS) are in use, if one of the baudrates equal 1 while one (CSRn.SCBR=1) of the others do not equal 1, and CSRn.CPOL=1 and CSRn.NCPHA=0, then an additional pulse will be generated on SCK.<br><b>Fix/Workaround</b>                                                                                                    |

|         |      |   | When multiple CS are in use, if one of the baudrates equals 1, the others must also equal 1 if CSRn.CPOL=1 and CSRn.NCPHA=0.                                                                                                                                                                                                                       |

| 10.1.7  | тс   |   |                                                                                                                                                                                                                                                                                                                                                    |

|         |      | 1 | <ul> <li>Channel chaining skips first pulse for upper channel</li> <li>When chaining two channels using the Block Mode Register, the first pulse of the clock between the channels is skipped.</li> <li>Fix/Workaround</li> <li>Configure the lower channel with RA = 0x1 and RC = 0x2 to produce a dummy clock cycle</li> </ul>                   |

|         |      |   | for the upper channel. After the dummy cycle has been generated, indicated by the SR.CPCS bit, reconfigure the RA and RC registers for the lower channel with the real values.                                                                                                                                                                     |

| 10.1.8  | тwiм |   |                                                                                                                                                                                                                                                                                                                                                    |

|         |      | 1 | SMBALERT bit may be set after reset<br>For TWIM0 and TWIM1 modules, the SMBus Alert (SMBALERT) bit in the Status Register<br>(SR) might be erroneously set after system reset.<br>Fix/Workaround                                                                                                                                                   |

|         |      |   | After system reset, clear the SR.SMBALERT bit before commencing any TWI transfer.                                                                                                                                                                                                                                                                  |

|         |      |   | For TWIM2 module, the SMBus Alert (SMBALERT) is not implemented but the bit in the Sta-<br>tus Register (SR) is erroneously set once TWIM2 is enabled.<br><b>Fix/Workaround</b><br>None.                                                                                                                                                           |

| 10.1.9  | TWIS |   |                                                                                                                                                                                                                                                                                                                                                    |

|         |      | 1 | Clearing the NAK bit before the BTF bit is set locks up the TWI bus<br>When the TWIS is in transmit mode, clearing the NAK Received (NAK) bit of the Status Reg-<br>ister (SR) before the end of the Acknowledge/Not Acknowledge cycle will cause the TWIS to<br>attempt to continue transmitting data, thus locking up the bus.<br>Fix/Workaround |

|         |      |   | Clear SR.NAK only after the Byte Transfer Finished (BTF) bit of the same register has been set.                                                                                                                                                                                                                                                    |

| 10.1.10 | USBC |   |                                                                                                                                                                                                                                                                                                                                                    |

|         |      | 1 | UPINRQx.INRQ field is limited to 8-bits<br>In Host mode, when using the UPINRQx.INRQ feature together with the multi-packet mode<br>to launch a finite number of packet among multi-packet, the multi-packet size (located in the<br>descriptor table) is limited to the UPINRQx.INRQ value multiply by the pipe size.<br>Fix/Workaround           |

|         |      |   | UPINRQx.INRQ value shall be less than the number of configured multi-packet.                                                                                                                                                                                                                                                                       |

2 In USB host mode, downstream resume feature does not work (UHCON.RESUME=1).

# 10.2 rev D

10.2.1 ADCIFA

## 1 ADCREFP/ADCREFN can not be selected as an external ADC reference by setting the ADCIFA.CFG.EXREF bit to one Fix/Workaround

A voltage reference can be applied on ADCREFP/ADCREFN pins if the ADCIFA.CFG.EXREF bit is set to zero, the ADCIFA.CFG.RS bit is set to zero and the voltage reference applied on ADCREFP/ADCREFN pins is higher than the internal 1V reference.

# 10.2.2 AST

1 AST wake signal is released one AST clock cycle after the BUSY bit is cleared After writing to the Status Clear Register (SCR) the wake signal is released one AST clock cycle after the BUSY bit in the Status Register (SR.BUSY) is cleared. If entering sleep mode directly after the BUSY bit is cleared the part will wake up immediately. Fix/Workaround Read the Wake Enable Register (WER) and write this value back to the same register. Wait

Read the Wake Enable Register (WER) and write this value back to the same register. Wait for BUSY to clear before entering sleep mode.

# 10.2.3 aWire

# 1 aWire MEMORY\_SPEED\_REQUEST command does not return correct CV The aWire MEMORY\_SPEED\_REQUEST command does not return a CV corresponding to

the formula in the aWire Debug Interface chapter.

# Fix/Workaround

Issue a dummy read to address 0x10000000 before issuing the MEMORY\_SPEED\_REQUEST command and use this formula instead:

$$f_{sab} = \frac{7f_{aw}}{CV-3}$$

10.2.4 GPIO

# 1 Clearing Interrupt flags can mask other interrupts

When clearing interrupt flags in a GPIO port, interrupts on other pins of that port, happening in the same clock cycle will not be registered.

# Fix/Workaround

Read the PVR register of the port before and after clearing the interrupt to see if any pin change has happened while clearing the interrupt. If any change occurred in the PVR between the reads, they must be treated as an interrupt.

# 10.2.5 Power Manager

# 1 Clock Failure Detector (CFD) can be issued while turning off the CFD

While turning off the CFD, the CFD bit in the Status Register (SR) can be set. This will change the main clock source to RCSYS.

# Fix/Workaround

Solution 1: Enable CFD interrupt. If CFD interrupt is issues after turning off the CFD, switch back to original main clock source.

Solution 2: Only turn off the CFD while running the main clock on RCSYS.

# 2 Disabling SPI has no effect on the SR.TDRE bit

Disabling SPI has no effect on the SR.TDRE bit whereas the write data command is filtered when SPI is disabled. Writing to TDR when SPI is disabled will not clear SR.TDRE. If SPI is disabled during a PDCA transfer, the PDCA will continue to write data to TDR until its buffer is empty, and this data will be lost.

#### Fix/Workaround

Disable the PDCA, add two NOPs, and disable the SPI. To continue the transfer, enable the SPI and PDCA.

# 3 SPI disable does not work in SLAVE mode

SPI disable does not work in SLAVE mode.

# Fix/Workaround

Read the last received data, then perform a software reset by writing a one to the Software Reset bit in the Control Register (CR.SWRST).

# 4 SPI bad serial clock generation on 2nd chip select when SCBR=1, CPOL=1, and NCPHA=0

When multiple chip selects (CS) are in use, if one of the baudrates equal 1 while one (CSRn.SCBR=1) of the others do not equal 1, and CSRn.CPOL=1 and CSRn.NCPHA=0, then an additional pulse will be generated on SCK.

#### Fix/Workaround

When multiple CS are in use, if one of the baudrates equals 1, the others must also equal 1 if CSRn.CPOL=1 and CSRn.NCPHA=0.

#### 10.2.8 TC

# 1 Channel chaining skips first pulse for upper channel

When chaining two channels using the Block Mode Register, the first pulse of the clock between the channels is skipped.

# Fix/Workaround

Configure the lower channel with RA = 0x1 and RC = 0x2 to produce a dummy clock cycle for the upper channel. After the dummy cycle has been generated, indicated by the SR.CPCS bit, reconfigure the RA and RC registers for the lower channel with the real values.

#### 10.2.9 TWIM

#### 1 SMBALERT bit may be set after reset

For TWIM0 and TWIM1 modules, the SMBus Alert (SMBALERT) bit in the Status Register (SR) might be erroneously set after system reset. Fix/Workaround

After system reset, clear the SR.SMBALERT bit before commencing any TWI transfer.

For TWIM2 module, the SMBus Alert (SMBALERT) is not implemented but the bit in the Status Register (SR) is erroneously set once TWIM2 is enabled. Fix/Workaround None.

# 2 TWIM TWALM polarity is wrong

The TWALM signal in the TWIM is active high instead of active low. Fix/Workaround

Use an external inverter to invert the signal going into the TWIM. When using both TWIM and TWIS on the same pins, the TWALM cannot be used.

## Headquarters

Atmel Corporation 2325 Orchard Parkway San Jose, CA 95131 USA Tel: 1(408) 441-0311 Fax: 1(408) 487-2600

# International

Atmel Asia Unit 1-5 & 16, 19/F BEA Tower, Millennium City 5 418 Kwun Tong Road Kwun Tong, Kowloon Hong Kong Tel: (852) 2245-6100 Fax: (852) 2722-1369 Atmel Europe Le Krebs 8, Rue Jean-Pierre Timbaud BP 309 78054 Saint-Quentin-en-Yvelines Cedex France Tel: (33) 1-30-60-70-00 Fax: (33) 1-30-60-71-11

#### Atmel Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan Tel: (81) 3-3523-3551 Fax: (81) 3-3523-7581

#### **Product Contact**

Web Site www.atmel.com Technical Support avr32@atmel.com Sales Contact www.atmel.com/contacts

Literature Requests www.atmel.com/literature

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL'S TERMS AND CONDI-TIONS OF SALE LOCATED ON ATMEL'S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDEN-TAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel's products are not intended, or warranted for use as components in applications intended to support or sustain life.

© 2012 Atmel Corporation. All rights reserved. Atmel<sup>®</sup>, Atmel logo and combinations thereof, AVR<sup>®</sup> and others are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.