Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 72MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB          |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                  |

| Number of I/O              | 37                                                                    |

| Program Memory Size        | 128KB (128K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 32K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                             |

| Data Converters            | A/D 9x12b; D/A 1x12b                                                  |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 48-LQFP                                                               |

| Supplier Device Package    | 48-LQFP (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f302cbt6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### List of tables

| Table 1.  | Device summary                                                                                                                                                                        | . 1 |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 2.  | STM32F302xx family device features and peripheral counts                                                                                                                              | 11  |

| Table 3.  | External analog supply values for analog peripherals                                                                                                                                  | 15  |

| Table 4.  | STM32F302xB/STM32F302xC peripheral interconnect matrix                                                                                                                                |     |

| Table 5.  | Timer feature comparison                                                                                                                                                              | 22  |

| Table 6.  | Comparison of I2C analog and digital filters                                                                                                                                          |     |

| Table 7.  | STM32F302xB/STM32F302xC I <sup>2</sup> C implementation                                                                                                                               | 25  |

| Table 8.  | USART features                                                                                                                                                                        |     |

| Table 9.  | STM32F302xB/STM32F302xC SPI/I2S implementation                                                                                                                                        | 27  |

| Table 10. | Capacitive sensing GPIOs available on STM32F302xB/STM32F302xC devices                                                                                                                 |     |

| Table 11. | No. of capacitive sensing channels available on STM32F302xB/STM32F302xC devices.                                                                                                      |     |

| Table 12. | Legend/abbreviations used in the pinout table                                                                                                                                         |     |

| Table 13. | STM32F302xB/STM32F302xC pin definitions                                                                                                                                               |     |

| Table 14. | Alternate functions for port A                                                                                                                                                        |     |

| Table 15. | Alternate functions for port B                                                                                                                                                        |     |

| Table 16. | Alternate functions for port C                                                                                                                                                        |     |

| Table 17. | Alternate functions for port D                                                                                                                                                        |     |

| Table 18. | Alternate functions for port E                                                                                                                                                        |     |

| Table 19. | Alternate functions for port F                                                                                                                                                        |     |

| Table 20. | STM32F302xB/STM32F302xC memory map, peripheral register boundary addresses                                                                                                            |     |

| Table 21. | Voltage characteristics                                                                                                                                                               |     |

| Table 22. | Current characteristics                                                                                                                                                               |     |

| Table 23. | Thermal characteristics.                                                                                                                                                              |     |

| Table 24. | General operating conditions                                                                                                                                                          |     |

| Table 25. | Operating conditions at power-up / power-down                                                                                                                                         |     |

| Table 26. | Embedded reset and power control block characteristics.                                                                                                                               |     |

| Table 27. | Programmable voltage detector characteristics                                                                                                                                         |     |

| Table 28. | Embedded internal reference voltage.                                                                                                                                                  |     |

| Table 29. | Internal reference voltage calibration values                                                                                                                                         |     |

| Table 30. | Typical and maximum current consumption from $V_{DD}$ supply at $V_{DD}$ = 3.6V                                                                                                       |     |

| Table 31. | Typical and maximum current consumption from the $V_{DDA}$ supply $\dots \dots \dots$ |     |

| Table 32. | Typical and maximum $V_{DD}$ consumption in Stop and Standby modes.                                                                                                                   |     |

| Table 33. | Typical and maximum $V_{DDA}$ consumption in Stop and Standby modes                                                                                                                   |     |

| Table 34. | Typical and maximum current consumption from V <sub>BAT</sub> supply.                                                                                                                 |     |

| Table 35. | Typical current consumption in Run mode, code with data processing running from Flash                                                                                                 |     |

| Table 36. | Typical current consumption in Sleep mode, code running from Flash or RAM                                                                                                             |     |

| Table 37. | Switching output I/O current consumption                                                                                                                                              |     |

| Table 38. | Peripheral current consumption                                                                                                                                                        |     |

| Table 39. | Low-power mode wakeup timings                                                                                                                                                         |     |

| Table 40. | High-speed external user clock characteristics.                                                                                                                                       | 73  |

| Table 41. | Low-speed external user clock characteristics                                                                                                                                         |     |

| Table 42. | HSE oscillator characteristics                                                                                                                                                        |     |

| Table 43. | LSE oscillator characteristics (f <sub>LSE</sub> = 32.768 kHz)                                                                                                                        |     |

| Table 44. | HSI oscillator characteristics.                                                                                                                                                       |     |

| Table 45. | LSI oscillator characteristics                                                                                                                                                        |     |

| Table 46. | PLL characteristics                                                                                                                                                                   |     |

| Table 47. | Flash memory characteristics                                                                                                                                                          |     |

| Table 48. | Flash memory endurance and data retention                                                                                                                                             |     |

|           |                                                                                                                                                                                       |     |

### 2 Description

The STM32F302xB/STM32F302xC family is based on the high-performance ARM<sup>®</sup> Cortex<sup>®</sup>-M4 32-bit RISC core with FPU operating at a frequency of up to 72 MHz, and embedding a floating point unit (FPU), a memory protection unit (MPU) and an embedded trace macrocell (ETM). The family incorporates high-speed embedded memories (up to 256 Kbytes of Flash memory, up to 40 Kbytes of SRAM) and an extensive range of enhanced I/Os and peripherals connected to two APB buses.

The devices offer up to two fast 12-bit ADCs (5 Msps), four comparators, two operational amplifiers, up to one DAC channel, a low-power RTC, up to five general-purpose 16-bit timers, one general-purpose 32-bit timer, and one timer dedicated to motor control. They also feature standard and advanced communication interfaces: up to two I<sup>2</sup>Cs, up to three SPIs (two SPIs are with multiplexed full-duplex I2Ss), three USARTs, up to two UARTs, CAN and USB. To achieve audio class accuracy, the I2S peripherals can be clocked via an external PLL.

The STM32F302xB/STM32F302xC family operates in the -40 to +85 °C and -40 to +105 °C temperature ranges from a 2.0 to 3.6 V power supply. A comprehensive set of power-saving mode allows the design of low-power applications.

The STM32F302xB/STM32F302xC family offers devices in four packages ranging from 48 pins to 100 pins.

The set of included peripherals changes with the device chosen.

### 3.4 Embedded SRAM

STM32F302xB/STM32F302xC devices feature up to 40 Kbytes of embedded SRAM with hardware parity check on first 16 Kbytes of SRAM. The memory can be accessed in read/write at CPU clock speed with 0 wait states.

### 3.5 Boot modes

At startup, Boot0 pin and Boot1 option bit are used to select one of three boot options:

- Boot from user Flash

- Boot from system memory

- Boot from embedded SRAM

The boot loader is located in the system memory. It is used to reprogram the Flash memory by using USART1 (PA9/PA10), USART2 (PD5/PD6) or USB (PA11/PA12) through DFU (device firmware upgrade).

### 3.6 Cyclic redundancy check (CRC)

The CRC (cyclic redundancy check) calculation unit is used to get a CRC code using a configurable generator polynomial value and size.

Among other applications, CRC-based techniques are used to verify data transmission or storage integrity. In the scope of the EN/IEC 60335-1 standard, they offer a means of verifying the Flash memory integrity. The CRC calculation unit helps compute a signature of the software during runtime, to be compared with a reference signature generated at linktime and stored at a given memory location.

### 3.7.4 Low-power modes

The STM32F302xB/STM32F302xC supports three low-power modes to achieve the best compromise between low-power consumption, short startup time and available wakeup sources:

Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs.

• Stop mode

Stop mode achieves the lowest power consumption while retaining the content of SRAM and registers. All clocks in the 1.8 V domain are stopped, the PLL, the HSI RC and the HSE crystal oscillators are disabled. The voltage regulator can also be put either in normal or in low-power mode.

The device can be woken up from Stop mode by any of the EXTI line. The EXTI line source can be one of the 16 external lines, the PVD output, the USB wakeup, the RTC alarm, COMPx, I2Cx or U(S)ARTx.

Standby mode

The Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire 1.8 V domain is powered off. The PLL, the HSI RC and the HSE crystal oscillators are also switched off. After entering Standby mode, SRAM and register contents are lost except for registers in the Backup domain and Standby circuitry.

The device exits Standby mode when an external reset (NRST pin), an IWDG reset, a rising edge on the WKUP pin or an RTC alarm occurs.

*Note:* The RTC, the IWDG and the corresponding clock sources are not stopped by entering Stop or Standby mode.

### 3.8 Interconnect matrix

Several peripherals have direct connections between them. This allows autonomous communication between peripherals, saving CPU resources thus power supply consumption. In addition, these hardware connections allow fast and predictable latency.

| Interconnect source | Interconnect<br>destination | Interconnect action                         |

|---------------------|-----------------------------|---------------------------------------------|

|                     | TIMx                        | Timers synchronization or chaining          |

| TIMx                | ADCx<br>DAC1                | Conversion triggers                         |

|                     | DMA                         | Memory to memory transfer trigger           |

|                     | Compx                       | Comparator output blanking                  |

| COMPx               | TIMx                        | Timer input: OCREF_CLR input, input capture |

| ADCx                | TIMx                        | Timer triggered by analog watchdog          |

Table 4. STM32F302xB/STM32F302xC peripheral interconnect matrix

### 3.17.1 Advanced timer (TIM1)

The advanced-control timer, TIM1, can be seen as a three-phase PWM multiplexed on six channels. It has a complementary PWM output with programmable inserted dead-times. It can also be seen as a complete general-purpose timer. The four independent channels can be used for:

- Input capture

- Output compare

- PWM generation (edge or center-aligned modes) with full modulation capability (0-100%)

- One-pulse mode output

In debug mode, the advanced-control timer counter can be frozen and the PWM outputs disabled to turn off any power switches driven by these outputs.

Many features are shared with those of the general-purpose TIM timers (described in *Section 3.17.2* using the same architecture, so the advanced-control timers can work together with the TIM timers via the Timer Link feature for synchronization or event chaining.

### 3.17.2 General-purpose timers (TIM2, TIM3, TIM4, TIM15, TIM16, TIM17)

There are up to six synchronizable general-purpose timers embedded in the STM32F302xB/STM32F302xC (see *Table 5* for differences). Each general-purpose timer can be used to generate PWM outputs, or act as a simple time base.

• TIM2, 3, and TIM4

These are full-featured general-purpose timers:

- TIM2 has a 32-bit auto-reload up/downcounter and 32-bit prescaler

- TIM3 and 4 have 16-bit auto-reload up/downcounters and 16-bit prescalers.

These timers all feature 4 independent channels for input capture/output compare, PWM or one-pulse mode output. They can work together, or with the other general-purpose timers via the Timer Link feature for synchronization or event chaining.

The counters can be frozen in debug mode.

All have independent DMA request generation and support quadrature encoders.

• TIM15, 16 and 17

These three timers general-purpose timers with mid-range features:

- They have 16-bit auto-reload upcounters and 16-bit prescalers.

- TIM15 has 2 channels and 1 complementary channel

- TIM16 and TIM17 have 1 channel and 1 complementary channel

All channels can be used for input capture/output compare, PWM or one-pulse mode output.

The timers can work together via the Timer Link feature for synchronization or event chaining. The timers have independent DMA request generation.

The counters can be frozen in debug mode.

### 3.17.3 Basic timer (TIM6)

This timer is mainly used for DAC trigger generation. It can also be used as a generic 16-bit time base.

DocID025186 Rev 7

| I2C features <sup>(1)</sup> | I2C1 | I2C2 |

|-----------------------------|------|------|

| SMBus                       | Х    | Х    |

| Wakeup from STOP            | Х    | х    |

| Table 7. STM32F302xB/STM32F302xC I <sup>2</sup> C implementation (continued) | ) |

|------------------------------------------------------------------------------|---|

|------------------------------------------------------------------------------|---|

1. X = supported.

# 3.20 Universal synchronous/asynchronous receiver transmitter (USART)

The STM32F302xB/STM32F302xC devices have three embedded universal synchronous/asynchronous receiver transmitters (USART1, USART2 and USART3).

The USART interfaces are able to communicate at speeds of up to 9 Mbits/s.

They provide hardware management of the CTS and RTS signals, they support IrDA SIR ENDEC, the multiprocessor communication mode, the single-wire half-duplex communication mode and have LIN Master/Slave capability. The USART interfaces can be served by the DMA controller.

### 3.21 Universal asynchronous receiver transmitter (UART)

The STM32F302xB/STM32F302xC devices have 2 embedded universal asynchronous receiver transmitters (UART4, and UART5). The UART interfaces support IrDA SIR ENDEC, multiprocessor communication mode and single-wire half-duplex communication mode. The UART4 interface can be served by the DMA controller.

Refer to Table 8 for the features available in all U(S)ART interfaces.

| USART modes/features <sup>(1)</sup>         | USART1 | USART2 | USART3 | UART4 | UART5 |

|---------------------------------------------|--------|--------|--------|-------|-------|

| Hardware flow control for modem             | Х      | Х      | Х      | -     | -     |

| Continuous communication using DMA          | Х      | Х      | Х      | Х     | -     |

| Multiprocessor communication                | Х      | Х      | Х      | Х     | Х     |

| Synchronous mode                            | Х      | Х      | Х      | -     | -     |

| Smartcard mode                              | Х      | Х      | Х      | -     | -     |

| Single-wire half-duplex communication       | Х      | Х      | Х      | Х     | Х     |

| IrDA SIR ENDEC block                        | Х      | Х      | Х      | Х     | Х     |

| LIN mode                                    | Х      | Х      | Х      | Х     | Х     |

| Dual clock domain and wakeup from Stop mode | Х      | Х      | Х      | Х     | Х     |

| Receiver timeout interrupt                  | Х      | Х      | Х      | Х     | Х     |

| Modbus communication                        | Х      | Х      | Х      | Х     | х     |

| Auto baud rate detection                    | Х      | Х      | Х      | -     | -     |

| Driver Enable                               | Х      | Х      | Х      | -     | -     |

#### Table 8. USART features

1. X = supported.

| Group | Capacitive sensing signal name | Pin<br>name | Group | Capacitive sensing signal name | Pin<br>name |

|-------|--------------------------------|-------------|-------|--------------------------------|-------------|

|       | TSC_G1_IO1                     | PA0         |       | TSC_G5_IO1                     | PB3         |

| 1     | TSC_G1_IO2                     | PA1         | 5     | TSC_G5_IO2                     | PB4         |

|       | TSC_G1_IO3                     | PA2         | 5     | TSC_G5_IO3                     | PB6         |

|       | TSC_G1_IO4                     | PA3         |       | TSC_G5_IO4                     | PB7         |

|       | TSC_G2_IO1                     | PA4         |       | TSC_G6_IO1                     | PB11        |

| 2     | TSC_G2_IO2                     | PA5         | 6     | TSC_G6_IO2                     | PB12        |

| 2     | TSC_G2_IO3                     | PA6         | 0     | TSC_G6_IO3                     | PB13        |

|       | TSC_G2_IO4                     | PA7         |       | TSC_G6_IO4                     | PB14        |

|       | TSC_G3_IO1                     | PC5         |       | TSC_G7_IO1                     | PE2         |

| 3     | TSC_G3_IO2                     | PB0         | 7     | TSC_G7_IO2                     | PE3         |

| 3     | TSC_G3_IO3                     | PB1         | 1     | TSC_G7_IO3                     | PE4         |

|       | TSC_G3_IO4                     | PB2         |       | TSC_G7_IO4                     | PE5         |

|       | TSC_G4_IO1                     | PA9         |       | TSC_G8_IO1                     | PD12        |

| 4     | TSC_G4_IO2                     | PA10        | 8     | TSC_G8_IO2                     | PD13        |

| -+    | TSC_G4_IO3                     | PA13        | 0     | TSC_G8_IO3                     | PD14        |

|       | TSC_G4_IO4                     | PA14        |       | TSC_G8_IO4                     | PD15        |

## Table 10. Capacitive sensing GPIOs available on STM32F302xB/STM32F302xC devices

Table 11. No. of capacitive sensing channels available on STM32F302xB/STM32F302xC devices

|                                       | Number of capacitive sensing channels |             |             |  |  |  |  |  |

|---------------------------------------|---------------------------------------|-------------|-------------|--|--|--|--|--|

| Analog I/O group                      | STM32F302Vx                           | STM32F302Rx | STM32F302Cx |  |  |  |  |  |

| G1                                    | 3                                     | 3           | 3           |  |  |  |  |  |

| G2                                    | 3                                     | 3           | 3           |  |  |  |  |  |

| G3                                    | 3                                     | 3           | 2           |  |  |  |  |  |

| G4                                    | 3                                     | 3           | 3           |  |  |  |  |  |

| G5                                    | 3                                     | 3           | 3           |  |  |  |  |  |

| G6                                    | 3                                     | 3           | 3           |  |  |  |  |  |

| G7                                    | 3                                     | 0           | 0           |  |  |  |  |  |

| G8                                    | 3                                     | 0           | 0           |  |  |  |  |  |

| Number of capacitive sensing channels | 24                                    | 18          | 17          |  |  |  |  |  |

### 3.27 Development support

### 3.27.1 Serial wire JTAG debug port (SWJ-DP)

The ARM SWJ-DP Interface is embedded, and is a combined JTAG and serial wire debug port that enables either a serial wire debug or a JTAG probe to be connected to the target.

The JTAG TMS and TCK pins are shared respectively with SWDIO and SWCLK and a specific sequence on the TMS pin is used to switch between JTAG-DP and SW-DP.

### 3.27.2 Embedded trace macrocell<sup>™</sup>

The ARM embedded trace macrocell provides a greater visibility of the instruction and data flow inside the CPU core by streaming compressed data at a very high rate from the STM32F302xB/STM32F302xC through a small number of ETM pins to an external hardware trace port analyzer (TPA) device. The TPA is connected to a host computer using a high-speed channel. Real-time instruction and data flow activity can be recorded and then formatted for display on the host computer running debugger software. TPA hardware is commercially available from common development tool vendors. It operates with third party debugger software tools.

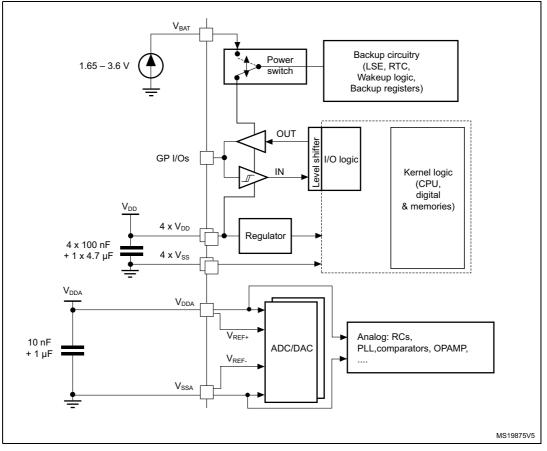

### 6.1.6 Power supply scheme

Figure 11. Power supply scheme

1. Dotted lines represent the internal connections on low pin count packages, joining the dedicated supply pins.

**Caution:** Each power supply pair (V<sub>DD</sub>/V<sub>SS</sub>, V<sub>DDA</sub>/V<sub>SSA</sub> etc..) must be decoupled with filtering ceramic capacitors as shown above. These capacitors must be placed as close as possible to, or below the appropriate pins on the underside of the PCB to ensure the good functionality of the device.

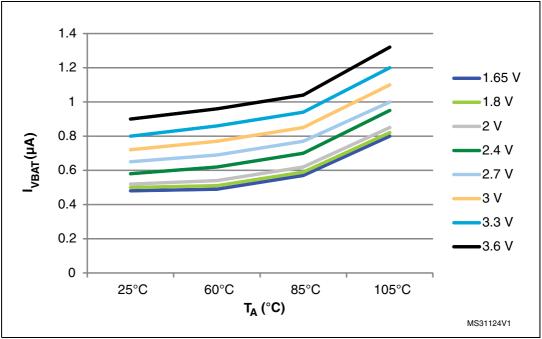

| Symbol                  | Para              | Conditions                                                                                    | Typ @V <sub>BAT</sub> |      |      |      |      |      | Max<br>@V <sub>BAT</sub> = 3.6 V <sup>(2)</sup> |      |                          | Unit                     |                           |      |

|-------------------------|-------------------|-----------------------------------------------------------------------------------------------|-----------------------|------|------|------|------|------|-------------------------------------------------|------|--------------------------|--------------------------|---------------------------|------|

|                         | meter             | (1)                                                                                           | 1.65V                 | 1.8V | 2V   | 2.4V | 2.7V | 3V   | 3.3V                                            | 3.6V | T <sub>A</sub> =<br>25°C | T <sub>A</sub> =<br>85°C | T <sub>A</sub> =<br>105°C | Unit |

|                         | Backup<br>domain  | LSE & RTC<br>ON; "Xtal<br>mode"<br>lower<br>driving<br>capability;<br>LSEDRV[1:<br>0] = '00'  | 0.48                  | 0.50 | 0.52 | 0.58 | 0.65 | 0.72 | 0.80                                            | 0.90 | 1.1                      | 1.5                      | 2.0                       |      |

| I <sub>DD_VBAT</sub> su | supply<br>current | LSE & RTC<br>ON; "Xtal<br>mode"<br>higher<br>driving<br>capability;<br>LSEDRV[1:<br>0] = '11' | 0.83                  | 0.86 | 0.90 | 0.98 | 1.03 | 1.10 | 1.20                                            | 1.30 | 1.5                      | 2.2                      | 2.9                       | -μA  |

Table 34. Typical and maximum current consumption from  $V_{\text{BAT}}$  supply

1. Crystal used: Abracon ABS07-120-32.768 kHz-T with a CL of 6 pF for typical values.

2. Guaranteed by characterization results.

Figure 13. Typical V<sub>BAT</sub> current consumption (LSE and RTC ON/LSEDRV[1:0] = '00')

#### Typical current consumption

The MCU is placed under the following conditions:

- V<sub>DD</sub> = V<sub>DDA</sub> = 3.3 V

- All I/O pins available on each package are in analog input configuration

- The Flash access time is adjusted to f<sub>HCLK</sub> frequency (0 wait states from 0 to 24 MHz, 1 wait state from 24 to 48 MHz and 2 wait states from 48 MHz to 72 MHz), and Flash prefetch is ON

- When the peripherals are enabled,  $f_{APB1} = f_{AHB/2}$ ,  $f_{APB2} = f_{AHB}$

- PLL is used for frequencies greater than 8 MHz

- AHB prescaler of 2, 4, 8,16 and 64 is used for the frequencies 4 MHz, 2 MHz, 1 MHz, 500 kHz and 125 kHz respectively.

#### Table 35. Typical current consumption in Run mode, code with data processing running from Flash

|                                     |                                 |                                       |                   | Т                      | Тур                     |        |  |  |

|-------------------------------------|---------------------------------|---------------------------------------|-------------------|------------------------|-------------------------|--------|--|--|

| Symbol                              | Parameter                       | Conditions                            | f <sub>HCLK</sub> | Peripherals<br>enabled | Peripherals<br>disabled | Unit   |  |  |

|                                     |                                 |                                       | 72 MHz            | 61.3                   | 28.0                    |        |  |  |

| I <sub>DD</sub>                     |                                 |                                       | 64 MHz            | 54.8                   | 25.4                    |        |  |  |

|                                     |                                 |                                       | 48 MHz            | 41.9                   | 19.3                    |        |  |  |

|                                     |                                 |                                       | 32 MHz            | 28.5                   | 13.3                    |        |  |  |

|                                     |                                 |                                       | 24 MHz            | 21.8                   | 10.4                    |        |  |  |

|                                     | Supply current in Run mode from |                                       | 16 MHz            | 14.9                   | 7.2                     | mA     |  |  |

| 'DD                                 | V <sub>DD</sub> supply          |                                       | 8 MHz             | 7.7                    | 3.9                     | - IIIA |  |  |

|                                     |                                 |                                       | 4 MHz             | 4.5                    | 2.5                     |        |  |  |

|                                     |                                 |                                       | 2 MHz             | 2.8                    | 1.7                     |        |  |  |

|                                     |                                 | Running from HSE crystal clock 8 MHz, | 1 MHz             | 1.9                    | 1.3                     |        |  |  |

|                                     |                                 |                                       | 500 kHz           | 1.4                    | 1.1                     |        |  |  |

|                                     |                                 |                                       | 125 kHz           | 1.1                    | 0.9                     |        |  |  |

|                                     |                                 | code executing from                   | 239.5             |                        |                         |        |  |  |

|                                     |                                 | Flash                                 | 64 MHz 210.9 2    | 210.3                  |                         |        |  |  |

|                                     |                                 |                                       | 48 MHz            | 155.8                  | 155.6                   |        |  |  |

|                                     |                                 |                                       | 32 MHz            | 105.7                  | 105.6                   |        |  |  |

|                                     |                                 |                                       | 24 MHz            | 82.1                   | 82.0                    |        |  |  |

| I <sub>DDA</sub> <sup>(1) (2)</sup> | Supply current in Run mode from |                                       | 16 MHz            | 58.8                   | 58.8                    | μA     |  |  |

| 'DDA`´``                            | V <sub>DDA</sub> supply         |                                       | 8 MHz             | 2.4                    | 2.4                     | μΑ     |  |  |

|                                     | DDA                             |                                       | 4 MHz             | 2.4                    | 2.4                     |        |  |  |

|                                     |                                 |                                       | 2 MHz             | 2.4                    | 2.4                     | 1      |  |  |

|                                     |                                 |                                       | 1 MHz             | 2.4                    | 2.4                     | 1      |  |  |

|                                     |                                 |                                       | 500 kHz           | 2.4                    | 2.4                     |        |  |  |

|                                     |                                 |                                       | 125 kHz           | 2.4                    | 2.4                     | ]      |  |  |

1. V<sub>DDA</sub> monitoring is ON.

2. When peripherals are enabled, the power consumption of the analog part of peripherals such as ADC, DAC, Comparators, OpAmp etc. is not included. Refer to the tables of characteristics in the subsequent sections.

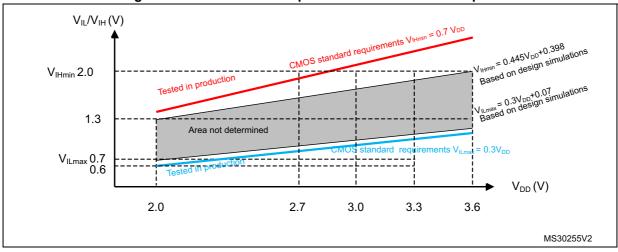

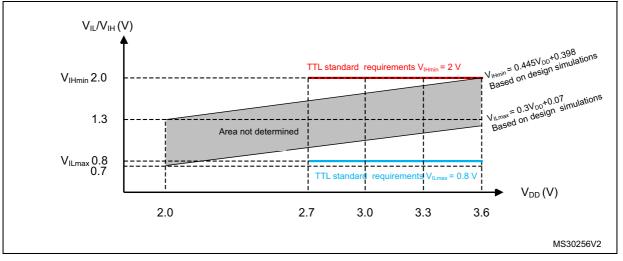

All I/Os are CMOS and TTL compliant (no software configuration required). Their characteristics cover more than the strict CMOS-technology or TTL parameters. The coverage of these requirements is shown in *Figure 19* and *Figure 20* for standard I/Os.

Figure 19. TC and TTa I/O input characteristics - CMOS port

#### Figure 20. TC and TTa I/O input characteristics - TTL port

| Table 64. I <sup>2</sup> S characteristics <sup>(1)</sup> Symbol     Parameter     Conditions     Min     Max     U |                                                  |                                            |       |        |      |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|--------------------------------------------|-------|--------|------|--|--|--|--|--|

| Symbol                                                                                                              | Parameter                                        | Conditions                                 | Min   | Max    | Unit |  |  |  |  |  |

| f <sub>CK</sub>                                                                                                     | I <sup>2</sup> S clock frequency                 | Master data: 16 bits,<br>audio freq=48 kHz | 1.496 | 1.503  | MHz  |  |  |  |  |  |

| 1/t <sub>c(CK)</sub>                                                                                                |                                                  | Slave                                      | 0     | 12.288 |      |  |  |  |  |  |

| t <sub>r(CK)</sub><br>t <sub>f(CK)</sub>                                                                            | I <sup>2</sup> S clock rise and fall time        | Capacitive load<br>C <sub>L</sub> = 30 pF  | -     | 8      |      |  |  |  |  |  |

| t <sub>w(CKH)</sub>                                                                                                 | I <sup>2</sup> S clock high time                 | Master f <sub>PCLK</sub> = 36 MHz,         | 331   | -      |      |  |  |  |  |  |

| t <sub>w(CKL)</sub>                                                                                                 | I <sup>2</sup> S clock low time                  | audio frequency =<br>48 kHz                | 332   | -      | ns   |  |  |  |  |  |

| t <sub>v(WS)</sub>                                                                                                  | WS valid time                                    | Master mode                                | 4     | -      | 115  |  |  |  |  |  |

| t <sub>h(WS)</sub>                                                                                                  | WS hold time                                     | Master mode                                | 4     | -      |      |  |  |  |  |  |

| t <sub>su(WS)</sub>                                                                                                 | WS setup time                                    |                                            |       | -      |      |  |  |  |  |  |

| t <sub>h(WS)</sub>                                                                                                  | WS hold time                                     | Slave mode                                 | 0     | -      |      |  |  |  |  |  |

| Duty Cycle                                                                                                          | I <sup>2</sup> S slave input clock<br>duty cycle | Slave mode                                 | 30    | 70     | %    |  |  |  |  |  |

| $t_{su(SD_MR)}$                                                                                                     | Data input setup time                            | Master receiver                            | 9     | -      |      |  |  |  |  |  |

| t <sub>su(SD_SR)</sub>                                                                                              | Data input setup time                            | Slave receiver                             | 2     | -      |      |  |  |  |  |  |

| t <sub>h(SD_MR)</sub>                                                                                               | Data input hold time                             | Master receiver                            | 0     | -      |      |  |  |  |  |  |

| t <sub>h(SD_SR)</sub>                                                                                               |                                                  | Slave receiver                             | 0     | -      |      |  |  |  |  |  |

| $t_{v(SD\_ST)}$                                                                                                     | Data output valid time                           | Slave transmitter (after enable edge)      | -     | 29     | ns   |  |  |  |  |  |

| $t_{h(SD\_ST)}$                                                                                                     | Data output hold time                            | Slave transmitter (after enable edge)      | 12    | -      |      |  |  |  |  |  |

| $t_{v(SD_MT)}$                                                                                                      | Data output valid time                           | Master transmitter (after enable edge)     | -     | 3      |      |  |  |  |  |  |

| t <sub>h(SD_MT)</sub>                                                                                               | Data output hold time                            | Master transmitter (after enable edge)     | 2     | -      |      |  |  |  |  |  |

|                                                                                                                     | •                                                |                                            |       |        | ·    |  |  |  |  |  |

Table 64. I<sup>2</sup>S characteristics<sup>(1)</sup>

1. Guaranteed by characterization results.

104/144

#### Table 68. ADC characteristics (continued) Symbol Parameter Мах Conditions Min Тур Unit 0.021 f<sub>ADC</sub> = 72 MHz 8.35 μs $t_{s}^{(1)}$ Sampling time 1.5 601.5 1/f<sub>ADC</sub> --T<sub>ADCVREG\_STUP</sub><sup>(1)</sup> ADC Voltage Regulator Start-up time -10 -μs f<sub>ADC</sub> = 72 MHz Resolution = 12 bits 0.19 8.52 μs Total conversion time (including $t_{CONV}^{(1)}$ sampling time) 14 to 614 (t<sub>S</sub> for sampling + 12.5 for successive Resolution = 12 bits 1/f<sub>ADC</sub> approximation) (V<sub>SSA</sub>+V<sub>REF+</sub>)/2 -10% (V<sub>SSA</sub>+V<sub>REF+</sub>)/2 + 10% CMIR<sup>(1)</sup> ADC differential mode V Common Mode Input signal Range $(V_{SSA}+V_{REF+})/2$

1. Data guaranteed by design.

2. V<sub>REF+</sub> can be internally connected to V<sub>DDA</sub> and V<sub>REF-</sub> can be internally connected to V<sub>SSA</sub>, depending on the package. Refer to Section 4: Pinouts and pin description for further details.

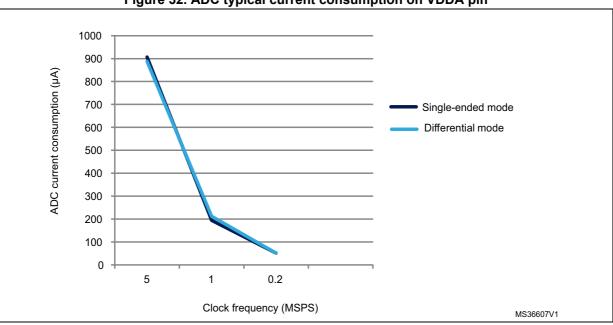

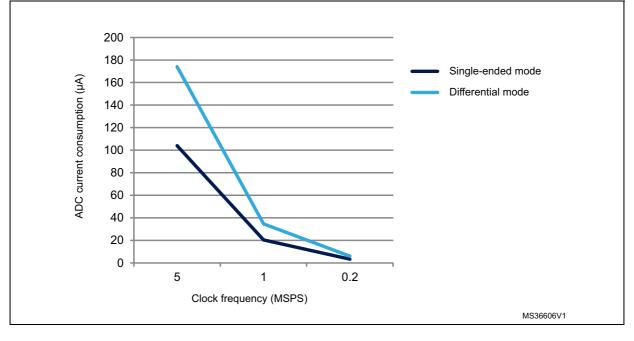

Figure 32. ADC typical current consumption on VDDA pin

#### Figure 33. ADC typical current consumption on VREF+ pin

### 6.3.19 DAC electrical specifications

| Symbol                               | Parameter                                                                                                                                                          | с                                                            | onditions                                                                           | Min | Тур | Мах                     | Unit |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|-------------------------------------------------------------------------------------|-----|-----|-------------------------|------|

| V <sub>DDA</sub>                     | Analog supply voltage                                                                                                                                              |                                                              | -                                                                                   | 2.4 | -   | 3.6                     | V    |

| R <sub>LOAD</sub> <sup>(1)</sup>     | Resistive load                                                                                                                                                     | DAC output                                                   | Connected to $V_{SSA}$                                                              | 5   | 5   |                         | kΩ   |

| INLOAD                               |                                                                                                                                                                    | buffer ON                                                    | Connected to $V_{DDA}$                                                              | 25  | -   | -                       | K22  |

| $R_0^{(1)}$                          | Output impedance                                                                                                                                                   | DAC output                                                   | buffer OFF                                                                          | -   | -   | 15                      | kΩ   |

| C <sub>LOAD</sub> <sup>(1)</sup>     | Capacitive load                                                                                                                                                    | DAC output                                                   | buffer ON                                                                           | -   | -   | 50                      | pF   |

| V <sub>DAC_OUT</sub> <sup>(1)</sup>  | Voltage on DAC_OUT<br>output                                                                                                                                       | code (0x0E)<br>V <sub>DDA</sub> = 3.6<br>and (0x155)         | s to 12-bit input<br>0) to (0xF1C) at<br>V<br>and (0xEAB) at<br>V DAC output buffer | 0.2 | -   | V <sub>DDA</sub> – 0.2  | V    |

|                                      |                                                                                                                                                                    | DAC output                                                   | buffer OFF                                                                          | -   | 0.5 | V <sub>DDA</sub> - 1LSB | mV   |

| I (3)                                | DAC DC current                                                                                                                                                     | With no load<br>(0x800) on t                                 | d, middle code<br>he input.                                                         | -   | -   | 380                     | μΑ   |

| 'DDA'                                | I <sub>DDA</sub> <sup>(3)</sup> consumption in quiescent<br>mode (Standby mode) <sup>(2)</sup>                                                                     |                                                              | With no load, worst code<br>(0xF1C) on the input.                                   |     | -   | 480                     | μA   |

| <b>-</b> (3)                         | Differential non linearity                                                                                                                                         | Given for a 10-bit input code                                |                                                                                     | -   | -   | ±0.5                    | LSB  |

|                                      | Difference between two<br>consecutive code-1LSB)                                                                                                                   | Given for a 12-bit input code                                |                                                                                     | -   | -   | ±2                      | LSB  |

|                                      | Integral non linearity                                                                                                                                             |                                                              | 10-bit input code                                                                   | -   | -   | ±1                      | LSB  |

| INL <sup>(3)</sup>                   | (difference between<br>measured value at Code i<br>and the value at Code i on a<br>line drawn between Code 0<br>and last Code 4095)                                | Given for a 12-bit input code                                |                                                                                     | _   | -   | ±4                      | LSB  |

|                                      |                                                                                                                                                                    |                                                              | -                                                                                   | -   | -   | ±10                     | mV   |

| Offset <sup>(3)</sup>                | Offset error (difference<br>between measured value at<br>Code (0x800) and the ideal                                                                                | Given for a 10-bit input code at<br>V <sub>DDA</sub> = 3.6 V |                                                                                     | -   | -   | ±3                      | LSB  |

|                                      | value = $V_{DDA}/2$ )                                                                                                                                              | Given for a 12-bit input code at<br>V <sub>DDA</sub> = 3.6 V |                                                                                     | -   | -   | ±12                     | LSB  |

| Gain error <sup>(3)</sup>            | Gain error                                                                                                                                                         | Given for a 12-bit input code                                |                                                                                     | -   | -   | ±0.5                    | %    |

| t <sub>SETTLING</sub> <sup>(3)</sup> | Settling time (full scale: for a<br>12-bit input code transition<br>between the lowest and the<br>highest input codes when<br>DAC_OUT reaches final<br>value ±1LSB | C <sub>LOAD</sub> ≰50 pF,<br>R <sub>LOAD</sub> ≥ 5 kΩ        |                                                                                     | -   | 3   | 4                       | μs   |

| Update<br>rate <sup>(3)</sup>        | Max frequency for a correct<br>DAC_OUT change when<br>small variation in the input<br>code (from code i to i+1LSB)                                                 | C <sub>LOAD</sub>                                            |                                                                                     | -   | -   | 1                       | MS/s |

#### Table 75. DAC characteristics

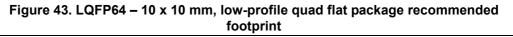

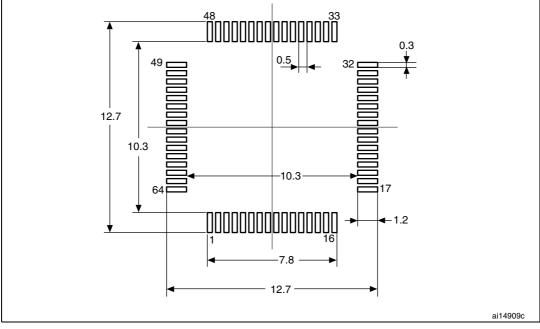

### 7 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

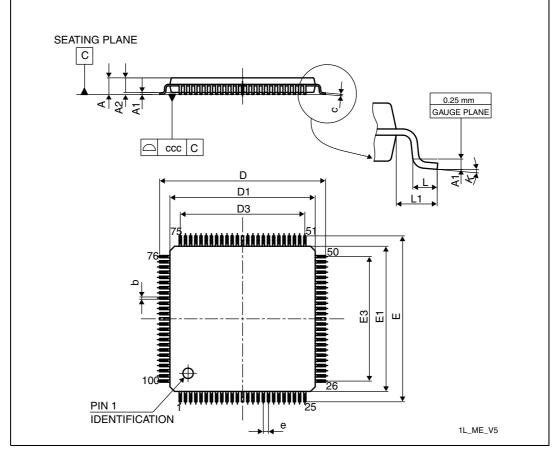

## 7.1 LQFP100 – 14 x 14 mm, low-profile quad flat package information

Figure 39. LQFP100 – 14 x 14 mm, low-profile quad flat package outline

1. Drawing is not to scale.

Table 81. LQPF100 – 14 x 14 mm, low-profile quad flat package mechanical data

| e      | Symbol | millimeters |     |      | inches <sup>(1)</sup> |     |        |

|--------|--------|-------------|-----|------|-----------------------|-----|--------|

| Symbol | ymbol  | Min         | Тур | Max  | Min                   | Тур | Max    |

|        | А      | -           | -   | 1.60 | -                     | -   | 0.063  |

|        | A1     | 0.05        | -   | 0.15 | 0.002                 | -   | 0.0059 |

DocID025186 Rev 7

| (continued) |      |             |      |                       |        |        |  |  |

|-------------|------|-------------|------|-----------------------|--------|--------|--|--|

| Cumb al     |      | millimeters |      | inches <sup>(1)</sup> |        |        |  |  |

| Symbol      | Min  | Тур         | Max  | Min                   | Тур    | Мах    |  |  |

| E1          | -    | 10.00       | -    | -                     | 0.3937 | -      |  |  |

| E3          | -    | 7.50        | -    | -                     | 0.2953 | -      |  |  |

| е           | -    | 0.50        | -    | -                     | 0.0197 | -      |  |  |

| К           | 0°   | 3.5°        | 7°   | 0°                    | 3.5°   | 7°     |  |  |

| L           | 0.45 | 0.60        | 0.75 | 0.0177                | 0.0236 | 0.0295 |  |  |

| L1          | -    | 1.00        | -    | -                     | 0.0394 | -      |  |  |

| CCC         | -    | -           | 0.08 | -                     | -      | 0.0031 |  |  |

Table 82. LQFP64 – 10 x 10 mm, low-profile quad flat package mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

1. Dimensions are in millimeters.

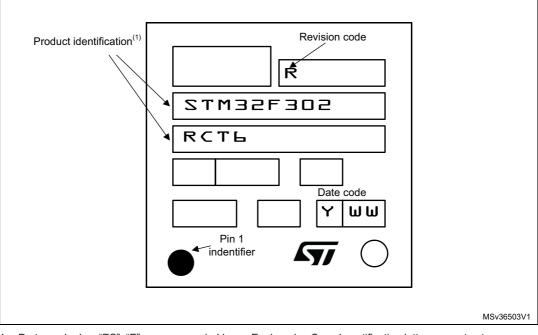

#### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 06-May-2016 | 7        | <ul> <li>Updated <i>Figure 5: STM32F302xB/STM32F302xC LQFP64 pinout</i><br/>replacing VSS by PF4.</li> <li>Updated <i>Table 13: STM32F302xB/STM32F302xC pin definitions</i>: <ul> <li>Adding 'digital power supply' in the Pin function column at the line corresponding to K8/28/19 pins.</li> <li>Adding VSS digital ground line with WLCSP100 K9 and K10 pins connected.</li> <li>Replacing in VDD line for WLCSP100: 'A10, B10' by 'A9, A10, B10, B8'.</li> <li>Updated <i>Figure 21: Five volt tolerant (FT and FTf) I/O input characteristics - CMOS port.</i></li> <li>Updated <i>Table 77: Operational amplifier characteristics</i> high saturation and low saturation voltages.</li> <li>Updated <i>Table 13: STM32F302xB/STM32F302xC pin definitions</i> adding note 'Fast ADC channel' for ADCx_IN15.</li> <li>Updated <i>Table 75: DAC characteristics</i> adding CMIR parameter and modifying tSTAB parameter characteristics.</li> </ul> </li> </ul> |

Table 88. Document revision history (continued)