Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 72MHz                                                                   |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB            |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                    |

| Number of I/O              | 37                                                                      |

| Program Memory Size        | 128KB (128K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 32K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                               |

| Data Converters            | A/D 9x12b; D/A 1x12b                                                    |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 48-LQFP                                                                 |

| Supplier Device Package    | 48-LQFP (7x7)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f302cbt6tr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1 Introduction

This datasheet provides the ordering information and mechanical device characteristics of the STM32F302xB/STM32F302xC microcontrollers.

This STM32F302xB/STM32F302xC datasheet should be read in conjunction with the STM32F302xx reference manual (RM0365). The reference manual is available from the STMicroelectronics website *www.st.com*.

For information on the Cortex<sup>®</sup>-M4 core with FPU, please refer to:

- **Cortex<sup>®</sup>-M4 with FPU Technical Reference Manual**, available from ARM website www.arm.com.

- STM32F3xxx and STM32F4xxx Cortex<sup>®</sup>-M4 programming manual (PM0214) available from our website *www.st.com*.

| Interconnect source                             | Interconnect<br>destination | Interconnect action                                            |

|-------------------------------------------------|-----------------------------|----------------------------------------------------------------|

| GPIO<br>RTCCLK<br>HSE/32<br>MC0                 | TIM16                       | Clock source used as input channel for HSI and LSI calibration |

| CSS<br>CPU (hard fault)<br>COMPx<br>PVD<br>GPIO | TIM1,<br>TIM15, 16, 17      | Timer break                                                    |

|                                                 | TIMx                        | External trigger, timer break                                  |

| GPIO                                            | ADCx<br>DAC1                | Conversion external trigger                                    |

| DAC1                                            | COMPx                       | Comparator inverting input                                     |

#### Table 4. STM32F302xB/STM32F302xC peripheral interconnect matrix (continued)

*Note:* For more details about the interconnect actions, please refer to the corresponding sections in the reference manual (RM0365.

## 3.9 Clocks and startup

System clock selection is performed on startup, however the internal RC 8 MHz oscillator is selected as default CPU clock on reset. An external 4-32 MHz clock can be selected, in which case it is monitored for failure. If failure is detected, the system automatically switches back to the internal RC oscillator. A software interrupt is generated if enabled. Similarly, full interrupt management of the PLL clock entry is available when necessary (for example with failure of an indirectly used external oscillator).

Several prescalers allow to configure the AHB frequency, the high speed APB (APB2) and the low speed APB (APB1) domains. The maximum frequency of the AHB and the high speed APB domains is 72 MHz, while the maximum allowed frequency of the low speed APB domain is 36 MHz.

| I2C features <sup>(1)</sup> | I2C1 | I2C2 |

|-----------------------------|------|------|

| SMBus                       | Х    | Х    |

| Wakeup from STOP            | Х    | х    |

| Table 7. STM32F302xB/STM32F302xC I <sup>2</sup> C implementation (continued) | ) |

|------------------------------------------------------------------------------|---|

|------------------------------------------------------------------------------|---|

1. X = supported.

## 3.20 Universal synchronous/asynchronous receiver transmitter (USART)

The STM32F302xB/STM32F302xC devices have three embedded universal synchronous/asynchronous receiver transmitters (USART1, USART2 and USART3).

The USART interfaces are able to communicate at speeds of up to 9 Mbits/s.

They provide hardware management of the CTS and RTS signals, they support IrDA SIR ENDEC, the multiprocessor communication mode, the single-wire half-duplex communication mode and have LIN Master/Slave capability. The USART interfaces can be served by the DMA controller.

## 3.21 Universal asynchronous receiver transmitter (UART)

The STM32F302xB/STM32F302xC devices have 2 embedded universal asynchronous receiver transmitters (UART4, and UART5). The UART interfaces support IrDA SIR ENDEC, multiprocessor communication mode and single-wire half-duplex communication mode. The UART4 interface can be served by the DMA controller.

Refer to Table 8 for the features available in all U(S)ART interfaces.

| USART modes/features <sup>(1)</sup>         | USART1 | USART2 | USART3 | UART4 | UART5 |

|---------------------------------------------|--------|--------|--------|-------|-------|

| Hardware flow control for modem             | Х      | Х      | Х      | -     | -     |

| Continuous communication using DMA          | Х      | Х      | Х      | Х     | -     |

| Multiprocessor communication                | Х      | Х      | Х      | Х     | Х     |

| Synchronous mode                            | Х      | Х      | Х      | -     | -     |

| Smartcard mode                              | Х      | Х      | Х      | -     | -     |

| Single-wire half-duplex communication       | Х      | Х      | Х      | Х     | Х     |

| IrDA SIR ENDEC block                        | Х      | Х      | Х      | Х     | Х     |

| LIN mode                                    | Х      | Х      | Х      | Х     | Х     |

| Dual clock domain and wakeup from Stop mode | Х      | Х      | Х      | Х     | Х     |

| Receiver timeout interrupt                  | Х      | Х      | Х      | Х     | Х     |

| Modbus communication                        | Х      | Х      | Х      | Х     | х     |

| Auto baud rate detection                    | Х      | Х      | Х      | -     | -     |

| Driver Enable                               | Х      | Х      | Х      | -     | -     |

#### Table 8. USART features

1. X = supported.

|                  | Pin nu  | umber  |        | 13. 51 WI32                              |          |               |       | Pin functions                                                                                            |                      |  |  |

|------------------|---------|--------|--------|------------------------------------------|----------|---------------|-------|----------------------------------------------------------------------------------------------------------|----------------------|--|--|

| WLCSP100         | LQFP100 | LQFP64 | LQFP48 | Pin name<br>(function<br>after<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                                                                      | Additional functions |  |  |

| E2               | 70      | 44     | 32     | PA11                                     | I/O      | FT            | -     | USART1_CTS, USB_DM,<br>CAN_RX, TIM1_CH1N,<br>TIM1_CH4, TIM1_BKIN2,<br>TIM4_CH1, COMP1_OUT,<br>EVENTOUT   | -                    |  |  |

| D1               | 71      | 45     | 33     | PA12                                     | I/O      | FT            | -     | USART1_RTS_DE, USB_DP,<br>CAN_TX, TIM1_CH2N,<br>TIM1_ETR, TIM4_CH2,<br>TIM16_CH1, COMP2_OUT,<br>EVENTOUT | -                    |  |  |

| E3               | 72      | 46     | 34     | PA13                                     | I/O      | FT            | -     | USART3_CTS, TIM4_CH3,<br>TIM16_CH1N, TSC_G4_IO3,<br>IR_OUT, SWDIO-JTMS,<br>EVENTOUT                      | -                    |  |  |

| C1               | 73      | -      | -      | PF6                                      | I/O      | FTf           | (1)   | I2C2_SCL,<br>USART3_RTS_DE,<br>TIM4_CH4, EVENTOUT                                                        | -                    |  |  |

| A1,<br>A2,<br>B1 | 74      | 47     | 35     | VSS                                      | S        | -             | -     | Gro                                                                                                      | und                  |  |  |

| D2               | 75      | 48     | 36     | VDD                                      | S        | -             | -     | Digital pov                                                                                              | wer supply           |  |  |

| C2               | 76      | 49     | 37     | PA14                                     | I/O      | FTf           | -     | I2C1_SDA,<br>USART2_TXTIM1_BKIN,<br>TSC_G4_IO4, SWCLK-JTCK,<br>EVENTOUT                                  | -                    |  |  |

| B2               | 77      | 50     | 38     | PA15                                     | I/O      | FTf           | -     | I2C1_SCL, SPI1_NSS,<br>SPI3_NSS, I2S3_WS, JTDI,<br>USART2_RX, TIM1_BKIN,<br>TIM2_CH1_ETR,<br>EVENTOUT    | -                    |  |  |

| E4               | 78      | 51     | -      | PC10                                     | I/O      | FT            | (1)   | SPI3_SCK, I2S3_CK,<br>USART3_TX, UART4_TX,<br>EVENTOUT                                                   | -                    |  |  |

| D3               | 79      | 52     | -      | PC11                                     | I/O      | FT            | (1)   | SPI3_MISO, I2S3ext_SD,<br>USART3_RX, UART4_RX,<br>EVENTOUT                                               | -                    |  |  |

| A3               | 80      | 53     | -      | PC12                                     | I/O      | FT            | (1)   | EVENTOUT                                                                                                 | -                    |  |  |

| B3               | 81      | -      | -      | PD0                                      | I/O      | FT            | (1)   | CAN_RX, EVENTOUT                                                                                         | -                    |  |  |

50/144

| Table 19. Alternate functions for port F |          |           |           |          |          |           |               |  |  |

|------------------------------------------|----------|-----------|-----------|----------|----------|-----------|---------------|--|--|

| Port &<br>Pin Name                       | AF1      | AF2       | AF3       | AF4      | AF5      | AF6       | AF7           |  |  |

| PF0                                      | -        | -         | -         | I2C2_SDA | -        | TIM1_CH3N | -             |  |  |

| PF1                                      | -        | -         | -         | I2C2_SCL | -        | -         | -             |  |  |

| PF2                                      | EVENTOUT | -         | -         | -        | -        | -         | -             |  |  |

| PF4                                      | EVENTOUT | COMP1_OUT | -         | -        | -        | -         | -             |  |  |

| PF6                                      | EVENTOUT | TIM4_CH4  | -         | I2C2_SCL | -        | -         | USART3_RTS_DE |  |  |

| PF9                                      | EVENTOUT | -         | TIM15_CH1 | -        | SPI2_SCK | -         | -             |  |  |

| PF10                                     | EVENTOUT | -         | TIM15_CH2 | -        | SPI2_SCK | -         | -             |  |  |

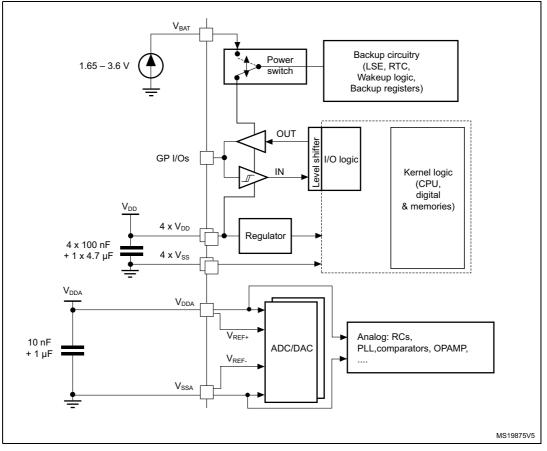

#### 6.1.6 Power supply scheme

Figure 11. Power supply scheme

1. Dotted lines represent the internal connections on low pin count packages, joining the dedicated supply pins.

**Caution:** Each power supply pair (V<sub>DD</sub>/V<sub>SS</sub>, V<sub>DDA</sub>/V<sub>SSA</sub> etc..) must be decoupled with filtering ceramic capacitors as shown above. These capacitors must be placed as close as possible to, or below the appropriate pins on the underside of the PCB to ensure the good functionality of the device.

## 6.3 Operating conditions

### 6.3.1 General operating conditions

| Table 24. | General | operating | conditions |

|-----------|---------|-----------|------------|

|-----------|---------|-----------|------------|

| Symbol             | Parameter                                                                                           | Conditions                                 | Min  | Max                   | Unit |

|--------------------|-----------------------------------------------------------------------------------------------------|--------------------------------------------|------|-----------------------|------|

| f <sub>HCLK</sub>  | Internal AHB clock frequency                                                                        | -                                          | 0    | 72                    |      |

| f <sub>PCLK1</sub> | Internal APB1 clock frequency                                                                       | -                                          | 0    | 36                    | MHz  |

| f <sub>PCLK2</sub> | Internal APB2 clock frequency                                                                       | -                                          | 0    | 72                    |      |

| V <sub>DD</sub>    | Standard operating voltage                                                                          | -                                          | 2    | 3.6                   | V    |

|                    | Analog operating voltage<br>(OPAMP and DAC not used)                                                | Must have a potential                      | 2    | 3.6                   | V    |

| V <sub>DDA</sub>   | Analog operating voltage (OPAMP and DAC used)                                                       | equal to or higher than<br>V <sub>DD</sub> | 2.4  | 3.6                   | V    |

| V <sub>BAT</sub>   | Backup operating voltage                                                                            | -                                          | 1.65 | 3.6                   | V    |

|                    | I/O input voltage                                                                                   | TC I/O                                     | -0.3 | V <sub>DD</sub> +0.3  | V    |

| V <sub>IN</sub>    |                                                                                                     | TTa I/O                                    | -0.3 | V <sub>DDA</sub> +0.3 |      |

|                    |                                                                                                     | FT and FTf I/O <sup>(1)</sup>              | -0.3 | 5.5                   |      |

|                    |                                                                                                     | BOOT0                                      | 0    | 5.5                   |      |

|                    |                                                                                                     | WLCSP100                                   | -    | 500                   | mW   |

| Р                  | Power dissipation at $T_A =$<br>85 °C for suffix 6 or $T_A =$<br>105 °C for suffix 7 <sup>(2)</sup> | LQFP100                                    | -    | 488                   |      |

| $P_{D}$            |                                                                                                     | LQFP64                                     | -    | 444                   |      |

|                    |                                                                                                     | LQFP48                                     | -    | 364                   |      |

|                    | Ambient temperature for 6 Maximum power dissipation                                                 |                                            | -40  | 85                    | °C   |

| т.                 | suffix version                                                                                      | Low-power dissipation <sup>(3)</sup>       | -40  | 105                   |      |

| TA                 | Ambient temperature for 7                                                                           | Maximum power<br>dissipation               | -40  | 105                   | °C   |

|                    | suffix version                                                                                      | Low-power dissipation <sup>(3)</sup>       | -40  | 125                   |      |

| т.                 | lunction tomporature range                                                                          | 6 suffix version                           | -40  | 105                   | °C   |

| TJ                 | Junction temperature range                                                                          | 7 suffix version                           | -40  | 125                   | U    |

1. To sustain a voltage higher than  $V_{DD}$ +0.3 V, the internal pull-up/pull-down resistors must be disabled.

If T<sub>A</sub> is lower, higher P<sub>D</sub> values are allowed as long as T<sub>J</sub> does not exceed T<sub>Jmax</sub> (see Section 7.5: Thermal characteristics).

In low-power dissipation state, T<sub>A</sub> can be extended to this range as long as T<sub>J</sub> does not exceed T<sub>Jmax</sub> (see Section 7.5: Thermal characteristics).

#### On-chip peripheral current consumption

The MCU is placed under the following conditions:

- all I/O pins are in analog input configuration

- all peripherals are disabled unless otherwise mentioned

- the given value is calculated by measuring the current consumption

- with all peripherals clocked off

- with only one peripheral clocked on

- ambient operating temperature at 25°C and  $V_{DD} = V_{DDA} = 3.3$  V.

#### Table 38. Peripheral current consumption

| Derinherol                 | Typical consumption <sup>(1)</sup> | Unit   |

|----------------------------|------------------------------------|--------|

| Peripheral                 | I <sub>DD</sub>                    | Onit   |

| BusMatrix <sup>(2)</sup>   | 12.6                               |        |

| DMA1                       | 7.6                                |        |

| DMA2                       | 6.1                                |        |

| CRC                        | 2.1                                |        |

| GPIOA                      | 10.0                               |        |

| GPIOB                      | 10.3                               |        |

| GPIOC                      | 2.2                                |        |

| GPIOD                      | 8.8                                |        |

| GPIOE                      | 3.3                                |        |

| GPIOF                      | 3.0                                |        |

| TSC                        | 5.5                                |        |

| ADC1&2                     | 17.3                               |        |

| APB2-Bridge <sup>(3)</sup> | 3.6                                |        |

| SYSCFG                     | 7.3                                | μA/MHz |

| TIM1                       | 40.0                               |        |

| SPI1                       | 8.8                                |        |

| USART1                     | 23.3                               |        |

| TIM15                      | 17.1                               |        |

| TIM16                      | 10.1                               |        |

| TIM17                      | 11.0                               |        |

| APB1-Bridge <sup>(3)</sup> | 6.1                                |        |

| TIM2                       | 49.1                               |        |

| TIM3                       | 38.8                               |        |

| TIM4                       | 38.3                               |        |

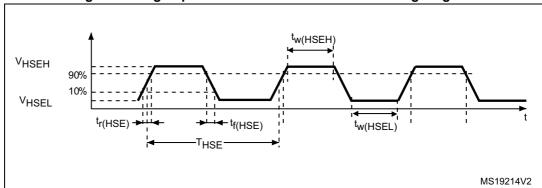

### 6.3.7 External clock source characteristics

#### High-speed external user clock generated from an external source

In bypass mode the HSE oscillator is switched off and the input pin is a standard GPIO. The external clock signal has to respect the I/O characteristics in *Section 6.3.14*. However, the recommended clock input waveform is shown in *Figure 14*.

| Symbol                                       | Parameter                                           | Conditions | Min                | Тур | Max             | Unit |

|----------------------------------------------|-----------------------------------------------------|------------|--------------------|-----|-----------------|------|

| f <sub>HSE_ext</sub>                         | User external clock source frequency <sup>(1)</sup> |            | 1                  | 8   | 32              | MHz  |

| V <sub>HSEH</sub>                            | OSC_IN input pin high level voltage                 |            | 0.7V <sub>DD</sub> | -   | V <sub>DD</sub> | V    |

| V <sub>HSEL</sub>                            | OSC_IN input pin low level voltage                  | -          | V <sub>SS</sub>    | -   | $0.3V_{DD}$     |      |

| t <sub>w(HSEH)</sub><br>t <sub>w(HSEL)</sub> | OSC_IN high or low time <sup>(1)</sup>              |            | 15                 | -   | -               | 20   |

| t <sub>r(HSE)</sub><br>t <sub>f(HSE)</sub>   | OSC_IN rise or fall time <sup>(1)</sup>             |            | -                  | -   | 20              | ns   |

1. Guaranteed by design.

#### Figure 14. High-speed external clock source AC timing diagram

#### Static latch-up

Two complementary static tests are required on six parts to assess the latch-up performance:

- A supply overvoltage is applied to each power supply pin

- A current injection is applied to each input, output and configurable I/O pin

These tests are compliant with EIA/JESD 78A IC latch-up standard.

| Symbol | Parameter             | Conditions                            | Class      |

|--------|-----------------------|---------------------------------------|------------|

| LU     | Static latch-up class | $T_A = +105$ °C conforming to JESD78A | II level A |

#### 6.3.13 I/O current injection characteristics

As a general rule, current injection to the I/O pins, due to external voltage below  $V_{SS}$  or above  $V_{DD}$  (for standard, 3 V-capable I/O pins) should be avoided during normal product operation. However, in order to give an indication of the robustness of the microcontroller in cases when abnormal injection accidentally happens, susceptibility tests are performed on a sample basis during device characterization.

#### Functional susceptibility to I/O current injection

While a simple application is executed on the device, the device is stressed by injecting current into the I/O pins programmed in floating input mode. While current is injected into the I/O pin, one at a time, the device is checked for functional failures.

The failure is indicated by an out of range parameter: ADC error above a certain limit (higher than 5 LSB TUE), out of conventional limits of induced leakage current on adjacent pins (out of  $-5 \mu$ A/+0  $\mu$ A range), or other functional failure (for example reset occurrence or oscillator frequency deviation).

The test results are given in Table 53.

| Symbol                                    | Parameter                       | Conditions                     | Min | Тур | Max | Unit |  |  |  |

|-------------------------------------------|---------------------------------|--------------------------------|-----|-----|-----|------|--|--|--|

| Driver characteristics                    |                                 |                                |     |     |     |      |  |  |  |

| t <sub>r</sub>                            | Rise time <sup>(2)</sup>        | C <sub>L</sub> = 50 pF         | 4   | -   | 20  | ns   |  |  |  |

| t <sub>f</sub>                            | Fall time <sup>(2)</sup>        | C <sub>L</sub> = 50 pF         | 4   | -   | 20  | ns   |  |  |  |

| t <sub>rfm</sub>                          | Rise/ fall time matching        | t <sub>r</sub> /t <sub>f</sub> | 90  | -   | 110 | %    |  |  |  |

| V <sub>CRS</sub>                          | Output signal crossover voltage | -                              | 1.3 | -   | 2.0 | V    |  |  |  |

| Output driver<br>Impedance <sup>(3)</sup> | Z <sub>DRV</sub>                | driving high and low           | 28  | 40  | 44  | Ω    |  |  |  |

Table 67. USB: Full-speed electrical characteristics<sup>(1)</sup>

1. Guaranteed by design.

Measured from 10% to 90% of the data signal. For more detailed informations, please refer to USB Specification - Chapter 7 (version 2.0).

3. No external termination series resistors are required on USB\_DP (D+) and USB\_DM (D-), the matching impedance is already included in the embedded driver.

#### CAN (controller area network) interface

Refer to Section 6.3.14: I/O port characteristics for more details on the input/output alternate function characteristics (CAN\_TX and CAN\_RX).

| S                       |

|-------------------------|

| TM                      |

| 132                     |

| Ξ                       |

| 02                      |

| Ň                       |

| ŝ                       |

| T                       |

| 13:                     |

| 2F                      |

| 30                      |

| STM32F302xB STM32F302xC |

| C                       |

| Symbol                             | Parameter                                                          | Conditions                                        | Min    | Тур | Мах               | U   |  |

|------------------------------------|--------------------------------------------------------------------|---------------------------------------------------|--------|-----|-------------------|-----|--|

| f <sub>ADC</sub>                   | ADC clock frequency                                                | -                                                 | 0.14   | -   | 72                | Ν   |  |

|                                    |                                                                    | Resolution = 12 bits,<br>Fast Channel             | 0.01   | -   | 5.14              |     |  |

| f <sub>S</sub> <sup>(1)</sup>      | Sampling rate                                                      | Resolution = 10 bits,<br>Fast Channel             | 0.012  | -   | 6                 | MSI |  |

| IS' '                              | Sampling rate                                                      | Resolution = 8 bits,<br>Fast Channel              | 0.014  | -   | 7.2               |     |  |

|                                    |                                                                    | Resolution = 6 bits,<br>Fast Channel              | 0.0175 | -   | 9                 |     |  |

| f <sub>TRIG</sub> <sup>(1)</sup> E | External trigger frequency                                         | f <sub>ADC</sub> = 72 MHz<br>Resolution = 12 bits | -      | -   | 5.14              | N   |  |

|                                    |                                                                    | Resolution = 12 bits                              | -      | -   | 14                | 1/  |  |

| V <sub>AIN</sub>                   | Conversion voltage range <sup>(2)</sup>                            | -                                                 | 0      | -   | V <sub>REF+</sub> |     |  |

| R <sub>AIN</sub> <sup>(1)</sup>    | External input impedance                                           | -                                                 | -      | -   | 100               |     |  |

| C <sub>ADC</sub> <sup>(1)</sup>    | Internal sample and hold capacitor                                 | -                                                 | -      | 5   | -                 |     |  |

| t <sub>STAB</sub> <sup>(1)</sup>   | Power-up time                                                      | -                                                 | · · ·  | 1   |                   |     |  |

| t <sub>CAL</sub> (1)               | Calibration time                                                   | f <sub>ADC</sub> = 72 MHz                         | 1.56   |     |                   |     |  |

| <sup>I</sup> CAL`′                 |                                                                    | -                                                 | 112    |     |                   | 1/  |  |

|                                    |                                                                    | CKMODE = 00                                       | 1.5    | 2   | 2.5               | 1/  |  |

| t <sub>latr</sub> (1)              | Trigger conversion latency<br>Regular and injected channels        | CKMODE = 01                                       | -      | -   | 2                 | 1/  |  |

| 'latr` '                           | without conversion abort                                           | CKMODE = 10                                       | -      | -   | 2.25              | 1/  |  |

|                                    |                                                                    | CKMODE = 11                                       | -      | -   | 2.125             | 1/  |  |

|                                    |                                                                    | CKMODE = 00                                       | 2.5    | 3   | 3.5               | 1/  |  |

| t <sub>latrinj</sub> (1)           | Trigger conversion latency<br>Injected channels aborting a regular | CKMODE = 01                                       | -      | -   | 3                 | 1/  |  |

| "Hatrinj`                          | conversion                                                         | CKMODE = 10                                       | -      | -   | 3.25              | 1/  |  |

|                                    |                                                                    | CKMODE = 11                                       | -      | -   | 3.125             | 1/  |  |

103/144

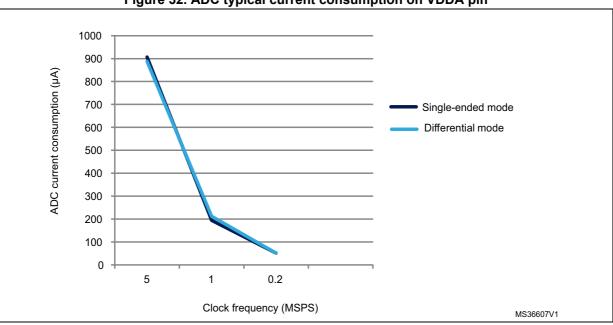

Figure 32. ADC typical current consumption on VDDA pin

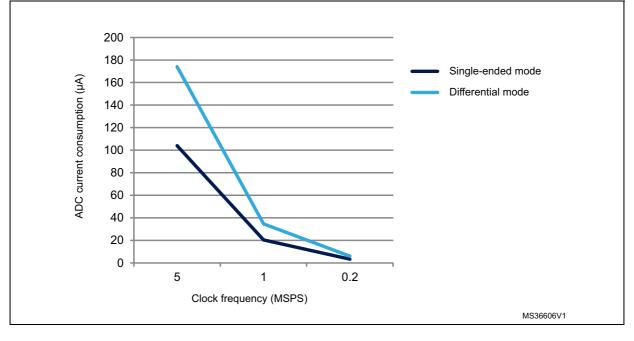

#### Figure 33. ADC typical current consumption on VREF+ pin

#### **Electrical characteristics**

|                | Sampling          | Sampling              |                              | R <sub>AIN</sub> max (kΩ) |                                  |  |

|----------------|-------------------|-----------------------|------------------------------|---------------------------|----------------------------------|--|

| Resolution     | cycle @<br>72 MHz | time [ns] @<br>72 MHz | Fast channels <sup>(2)</sup> | Slow<br>channels          | Other<br>channels <sup>(3)</sup> |  |

|                | 1.5               | 20.83                 | 0.018                        | NA                        | NA                               |  |

|                | 2.5               | 34.72                 | 0.150                        | NA                        | 0.022                            |  |

|                | 4.5               | 62.50                 | 0.470                        | 0.220                     | 0.180                            |  |

| 10 hite        | 7.5               | 104.17                | 0.820                        | 0.560                     | 0.470                            |  |

| 12 bits        | 19.5              | 270.83                | 2.70                         | 1.80                      | 1.50                             |  |

|                | 61.5              | 854.17                | 8.20                         | 6.80                      | 4.70                             |  |

|                | 181.5             | 2520.83               | 22.0                         | 18.0                      | 15.0                             |  |

|                | 601.5             | 8354.17               | 82.0                         | 68.0                      | 47.0                             |  |

|                | 1.5               | 20.83                 | 0.082                        | NA                        | NA                               |  |

|                | 2.5               | 34.72                 | 0.270                        | 0.082                     | 0.100                            |  |

|                | 4.5               | 62.50                 | 0.560                        | 0.390                     | 0.330                            |  |

|                | 7.5               | 104.17                | 1.20                         | 0.82                      | 0.68                             |  |

| 10 bits        | 19.5              | 270.83                | 3.30                         | 2.70                      | 2.20                             |  |

|                | 61.5              | 854.17                | 10.0                         | 8.2                       | 6.8                              |  |

|                | 181.5             | 2520.83               | 33.0                         | 27.0                      | 22.0                             |  |

|                | 601.5             | 8354.17               | 100.0                        | 82.0                      | 68.0                             |  |

|                | 1.5               | 20.83                 | 0.150                        | NA                        | 0.039                            |  |

|                | 2.5               | 34.72                 | 0.390                        | 0.180                     | 0.180                            |  |

|                | 4.5               | 62.50                 | 0.820                        | 0.560                     | 0.470                            |  |

| <b>•</b> • • • | 7.5               | 104.17                | 1.50                         | 1.20                      | 1.00                             |  |

| 8 bits         | 19.5              | 270.83                | 3.90                         | 3.30                      | 2.70                             |  |

|                | 61.5              | 854.17                | 12.00                        | 12.00                     | 8.20                             |  |

|                | 181.5             | 2520.83               | 39.00                        | 33.00                     | 27.00                            |  |

|                | 601.5             | 8354.17               | 100.00                       | 100.00                    | 82.00                            |  |

|                | 1.5               | 20.83                 | 0.270                        | 0.100                     | 0.150                            |  |

|                | 2.5               | 34.72                 | 0.560                        | 0.390                     | 0.330                            |  |

|                | 4.5               | 62.50                 | 1.200                        | 0.820                     | 0.820                            |  |

| 0.1.11         | 7.5               | 104.17                | 2.20                         | 1.80                      | 1.50                             |  |

| 6 bits         | 19.5              | 270.83                | 5.60                         | 4.70                      | 3.90                             |  |

|                | 61.5              | 854.17                | 18.0                         | 15.0                      | 12.0                             |  |

|                | 181.5             | 2520.83               | 56.0                         | 47.0                      | 39.0                             |  |

|                | 601.5             | 8354.17               | 100.00                       | 100.0                     | 100.0                            |  |

Table 69. Maximum ADC R<sub>AIN</sub> <sup>(1)</sup>

1. Guaranteed by characterization results.

2. All fast channels, expect channels on PA2, PA6.

#### STM32F302xB STM32F302xC

#### 3. Channels available on PA2, PA6.

| Symbol               | Parameter                          | Conditions                             |                |                     |                     | Тур        | Max<br>(3) | Unit   |  |

|----------------------|------------------------------------|----------------------------------------|----------------|---------------------|---------------------|------------|------------|--------|--|

|                      |                                    | 0                                      | Cingle ended   | Fast channel 5.1 Ms | -                   | ±3.5       | ±4.5       |        |  |

| ET                   | Total                              | adjusted                               | Single ended - | Slow channel 4.8 Ms | -                   | <u>+</u> 4 | ±4.5       |        |  |

|                      | error                              |                                        | Differential   | Fast channel 5.1 Ms | -                   | ±3         | ±3         |        |  |

|                      |                                    |                                        | Dillerential   | Slow channel 4.8 Ms | -                   | ±3         | ±3         |        |  |

|                      |                                    |                                        | Single ended   | Fast channel 5.1 Ms | -                   | ±1         | ±1.5       |        |  |

| EO                   | Offset error                       |                                        | Single ended   | Slow channel 4.8 Ms | -                   | ±1         | ±2.5       |        |  |

| LO                   | Olisetenoi                         |                                        | Differential   | Fast channel 5.1 Ms | -                   | ±1         | ±1.5       |        |  |

|                      |                                    |                                        | Dillerential   | Slow channel 4.8 Ms | -                   | ±1         | ±1.5       |        |  |

|                      |                                    |                                        | Single ended   | Fast channel 5.1 Ms | -                   | ±3         | ±4         | _      |  |

| EG                   | Gain error                         | or                                     | Single ended   | Slow channel 4.8 Ms | -                   | ±3.5       | ±4         |        |  |

| EG                   |                                    |                                        | Differential   | Fast channel 5.1 Ms | -                   | ±1.5       | ±2.5       |        |  |

|                      |                                    |                                        |                | Slow channel 4.8 Ms | -                   | ±2         | ±2.5       |        |  |

|                      | Differential<br>linearity<br>error | linearity $V_{DDA} = V_{REF+} = 3.3 V$ | Single ended   | Fast channel 5.1 Ms | -                   | ±1         | ±1.5       |        |  |

| ED                   |                                    |                                        |                | Slow channel 4.8 Ms | -                   | ±1         | ±1.5       |        |  |

| ED                   |                                    |                                        | Differential   | Fast channel 5.1 Ms | -                   | ±1         | ±1         |        |  |

|                      |                                    |                                        |                | Slow channel 4.8 Ms | -                   | ±1         | ±1         |        |  |

|                      |                                    |                                        |                | Single ended        | Fast channel 5.1 Ms | -          | ±1.5       | ±2     |  |

| EL                   | Integral                           | Integral<br>linearity<br>error         | Silligie endeu | Slow channel 4.8 Ms | -                   | ±1.5       | ±3         | -      |  |

| LL                   |                                    |                                        | Differential   | Fast channel 5.1 Ms | -                   | ±1         | ±1.5       |        |  |

|                      |                                    |                                        |                | Slow channel 4.8 Ms | -                   | ±1         | ±1.5       |        |  |

|                      |                                    |                                        | Single ended   | Fast channel 5.1 Ms | 10.7                | 10.8       | -          |        |  |

| ENOB <sup>(4)</sup>  | Effective<br>number of             |                                        | Single ended   | Slow channel 4.8 Ms | 10.7                | 10.8       | -          | hite   |  |

| ENOB.                | bits                               |                                        | Differential   | Fast channel 5.1 Ms | 11.2                | 11.3       | -          | - bits |  |

|                      |                                    |                                        | Dillerential   | Slow channel 4.8 Ms | 11.1                | 11.3       | -          |        |  |

|                      | Signal-to-                         |                                        | Single ended   | Fast channel 5.1 Ms | 66                  | 67         | -          |        |  |

| SINAD <sup>(4)</sup> | noise and                          |                                        | Single ended   | Slow channel 4.8 Ms | 66                  | 67         | -          | dB     |  |

| SINAD: /             | distortion<br>ratio                |                                        | Differential   | Fast channel 5.1 Ms | 69                  | 70         | -          |        |  |

|                      | 1000                               |                                        | Differential   | Slow channel 4.8 Ms | 69                  | 70         | -          |        |  |

| Table 70. ADC accuracy - limited test conditions, 100-pin pac | kages <sup>(1)(2)</sup> |

|---------------------------------------------------------------|-------------------------|

|---------------------------------------------------------------|-------------------------|

| Symbol | Parameter                          | Conditions                |                     |                     |      | Тур  | Max<br>(3) | Unit  |

|--------|------------------------------------|---------------------------|---------------------|---------------------|------|------|------------|-------|

|        |                                    |                           | Cingle ended        | Fast channel 5.1 Ms | -    | ±4   | ±4.5       |       |

| CT.    | Total                              | unadjusted                | Single ended        | Slow channel 4.8 Ms | -    | ±5.5 | ±6         |       |

| ET     | error                              |                           | Differential        | Fast channel 5.1 Ms | -    | ±3.5 | ±4         |       |

|        |                                    |                           | Differential        | Slow channel 4.8 Ms | -    | ±3.5 | ±4         |       |

|        |                                    |                           |                     | Fast channel 5.1 Ms | -    | ±2   | ±2         |       |

| 50     | Offeet error                       |                           | Single ended        | Slow channel 4.8 Ms | -    | ±1.5 | ±2         |       |

| EO     | Offset error                       |                           | Differential        | Fast channel 5.1 Ms | -    | ±1.5 | ±2         |       |

|        |                                    |                           | Differential        | Slow channel 4.8 Ms | -    | ±1.5 | ±2         |       |

|        |                                    |                           |                     | Fast channel 5.1 Ms | -    | ±3   | ±4         |       |

| 50     | Gain error                         | ain error -               | Single ended        | Slow channel 4.8 Ms | -    | ±5   | ±5.5       | - LSB |

| EG     |                                    |                           | Differential        | Fast channel 5.1 Ms | -    | ±3   | ±3         |       |

|        |                                    |                           |                     | Slow channel 4.8 Ms | -    | ±3   | ±3.5       |       |

|        | Differential<br>linearity<br>error | ADC clock freq. ≤72 MHz   | Single ended        | Fast channel 5.1 Ms | -    | ±1   | ±1         |       |

|        |                                    | nearity $V_{DDA} = 3.3 V$ |                     | Slow channel 4.8 Ms | -    | ±1   | ±1         |       |

| ED     |                                    |                           | Differential        | Fast channel 5.1 Ms | -    | ±1   | ±1         |       |

|        |                                    |                           |                     | Slow channel 4.8 Ms | -    | ±1   | ±1         |       |

|        | Integral                           |                           | Oin als surds d     | Fast channel 5.1 Ms | -    | ±1.5 | ±2         |       |

| -      |                                    | Single ended              | Slow channel 4.8 Ms | -                   | ±2   | ±3   | 1          |       |

| EL     | error                              | linearity<br>error        |                     | Fast channel 5.1 Ms | -    | ±1.5 | ±1.5       | -     |

|        |                                    |                           | Differential        | Slow channel 4.8 Ms | -    | ±1.5 | ±2         |       |

|        |                                    |                           | Cingle and d        | Fast channel 5.1 Ms | 10.8 | 10.8 | -          |       |

| ENOB   | Effective                          |                           | Single ended        | Slow channel 4.8 Ms | 10.8 | 10.8 | -          | L. 14 |

| (4)    | number of bits                     |                           | Differential        | Fast channel 5.1 Ms | 11.2 | 11.3 | -          | bit   |

|        |                                    |                           | Differential        | Slow channel 4.8 Ms | 11.2 | 11.3 | -          |       |

|        | Circul to                          |                           |                     | Fast channel 5.1 Ms | 66   | 67   | -          |       |

| SINAD  | Signal-to-<br>noise and            |                           | Single ended        | Slow channel 4.8 Ms | 66   | 67   | -          | d٦    |

| (4)    | distortion                         |                           | Differential        | Fast channel 5.1 Ms | 69   | 70   | -          | dB    |

|        | ratio                              |                           | Differential        | Slow channel 4.8 Ms | 69   | 70   | -          |       |

Table 72. ADC accuracy - limited test conditions, 64-pin packages<sup>(1)(2)</sup>

## 6.3.19 DAC electrical specifications

| Symbol                               | Parameter                                                                                                                                                          | с                                                         | onditions                                                                           | Min | Тур | Мах                     | Unit |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|-------------------------------------------------------------------------------------|-----|-----|-------------------------|------|

| V <sub>DDA</sub>                     | Analog supply voltage                                                                                                                                              |                                                           | -                                                                                   | 2.4 | -   | 3.6                     | V    |

| R <sub>LOAD</sub> <sup>(1)</sup>     | Resistive load                                                                                                                                                     | DAC output Connected to V <sub>SSA</sub>                  |                                                                                     | 5   | 5   |                         | kΩ   |

| INLOAD                               |                                                                                                                                                                    | buffer ON                                                 | Connected to $V_{DDA}$                                                              | 25  | -   | -                       | K22  |

| $R_0^{(1)}$                          | Output impedance                                                                                                                                                   | DAC output                                                | buffer OFF                                                                          | -   | -   | 15                      | kΩ   |

| C <sub>LOAD</sub> <sup>(1)</sup>     | Capacitive load                                                                                                                                                    | DAC output                                                | buffer ON                                                                           | -   | -   | 50                      | pF   |

| V <sub>DAC_OUT</sub> <sup>(1)</sup>  | Voltage on DAC_OUT<br>output                                                                                                                                       | code (0x0E)<br>V <sub>DDA</sub> = 3.6<br>and (0x155)      | s to 12-bit input<br>0) to (0xF1C) at<br>V<br>and (0xEAB) at<br>V DAC output buffer | 0.2 | -   | V <sub>DDA</sub> – 0.2  | V    |

|                                      |                                                                                                                                                                    | DAC output                                                | buffer OFF                                                                          | -   | 0.5 | V <sub>DDA</sub> - 1LSB | mV   |

| I <sub>DDA</sub> <sup>(3)</sup>      | DAC DC current<br>consumption in quiescent                                                                                                                         | With no load<br>(0x800) on t                              | d, middle code<br>he input.                                                         | -   | -   | 380                     | μA   |

| 'DDA'                                | mode (Standby mode) <sup>(2)</sup>                                                                                                                                 | With no load, worst code<br>(0xF1C) on the input.         |                                                                                     | -   | -   | 480                     | μA   |

| <b>-</b> (3)                         | Differential non linearity                                                                                                                                         | Given for a 10-bit input code                             |                                                                                     | -   | -   | ±0.5                    | LSB  |

| DNL <sup>(3)</sup>                   | Difference between two<br>consecutive code-1LSB)                                                                                                                   | Given for a 12-bit input code                             |                                                                                     | -   | -   | ±2                      | LSB  |

|                                      | Integral non linearity                                                                                                                                             | Given for a                                               | 10-bit input code                                                                   | -   | -   | ±1                      | LSB  |

| INL <sup>(3)</sup>                   | (difference between<br>measured value at Code i<br>and the value at Code i on a<br>line drawn between Code 0<br>and last Code 4095)                                | Given for a 12-bit input code                             |                                                                                     | _   | -   | ±4                      | LSB  |

|                                      |                                                                                                                                                                    | -                                                         |                                                                                     | -   | -   | ±10                     | mV   |

| Offset <sup>(3)</sup>                | Offset error (difference<br>between measured value at<br>Code (0x800) and the ideal                                                                                | Given for a 10-bit input code at V <sub>DDA</sub> = 3.6 V |                                                                                     | -   | -   | ±3                      | LSB  |

|                                      | value = $V_{DDA}/2$ )                                                                                                                                              | Given for a<br>V <sub>DDA</sub> = 3.6                     | 12-bit input code at<br>V                                                           | -   | -   | ±12                     | LSB  |

| Gain error <sup>(3)</sup>            | Gain error                                                                                                                                                         | Given for a                                               | 12-bit input code                                                                   | -   | -   | ±0.5                    | %    |

| t <sub>SETTLING</sub> <sup>(3)</sup> | Settling time (full scale: for a<br>12-bit input code transition<br>between the lowest and the<br>highest input codes when<br>DAC_OUT reaches final<br>value ±1LSB | C <sub>LOAD</sub> ≤50 pF,<br>R <sub>LOAD</sub> ≥ 5 kΩ     |                                                                                     | -   | 3   | 4                       | μs   |

| Update<br>rate <sup>(3)</sup>        | Max frequency for a correct<br>DAC_OUT change when<br>small variation in the input<br>code (from code i to i+1LSB)                                                 | C <sub>LOAD</sub>                                         |                                                                                     | -   | -   | 1                       | MS/s |

#### Table 75. DAC characteristics

| Symbol           | Parameter                                                      | Conditio                                 | Min                   | Тур | Max | Unit |    |

|------------------|----------------------------------------------------------------|------------------------------------------|-----------------------|-----|-----|------|----|

|                  |                                                                | No hysteresis<br>(COMPxHYST[1:0]=00)     | -                     | -   | 0   | -    |    |

|                  |                                                                |                                          | High speed mode       | 3   |     | 13   |    |

|                  | Nys Comparator hysteresis Medium hysteresis (COMPxHYST[1:0]=10 | (COMPxHYST[1:0]=01)                      | All other power modes | 5   | 8   | 10   | mV |

| V <sub>hys</sub> |                                                                | Medium hysteresis<br>(COMPxHYST[1:0]=10) | High speed mode       | 7   | 15  | 26   |    |

|                  |                                                                |                                          | All other power modes | 9   |     | 19   |    |

|                  |                                                                | High hystoropia                          | High speed mode       | 18  |     | 49   |    |

|                  |                                                                | (COMPxHYST[1:0]=11)                      | All other power modes | 19  | 31  | 40   |    |

| Table 76. Comparator characteristics <sup>(1)</sup> ( | (continued) |

|-------------------------------------------------------|-------------|

|-------------------------------------------------------|-------------|

1. Data guaranteed by design.

2. For more details and conditions, see Figure 37 Maximum V\_{REFINT} scaler startup time from power down.

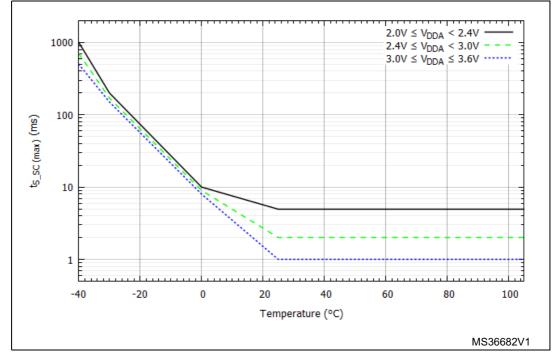

#### Figure 37. Maximum $V_{REFINT}$ scaler startup time from power down

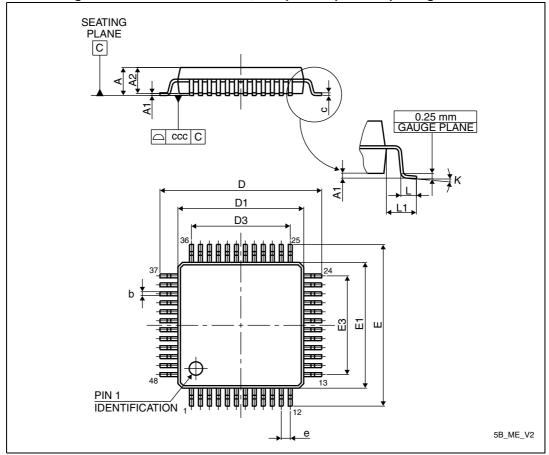

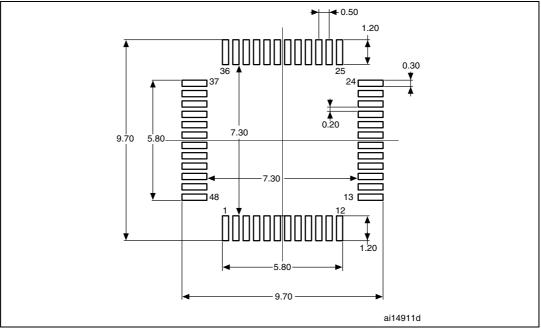

# 7.3 LQFP48 – 7 x 7 mm, low-profile quad flat package information

Figure 45. LQFP48 – 7 x 7 mm, low-profile quad flat package outline

1. Drawing is not to scale.

| Symbol | millimeters |      |      | inches <sup>(1)</sup> |        |        |

|--------|-------------|------|------|-----------------------|--------|--------|

|        | Min         | Тур  | Мах  | Min                   | Тур    | Мах    |

| А      | -           | -    | 1.60 | -                     | -      | 0.0630 |

| A1     | 0.05        | -    | 0.15 | 0.0020                | -      | 0.0059 |

| A2     | 1.35        | 1.40 | 1.45 | 0.0531                | 0.0551 | 0.0571 |

| b      | 0.17        | 0.22 | 0.27 | 0.0067                | 0.0087 | 0.0106 |

| С      | 0.09        | -    | 0.20 | 0.0035                | -      | 0.0079 |

| D      | 8.80        | 9.00 | 9.20 | 0.3465                | 0.3543 | 0.3622 |

| D1     | 6.80        | 7.00 | 7.20 | 0.2677                | 0.2756 | 0.2835 |

| D3     | -           | 5.50 | -    | -                     | 0.2165 | -      |

| Е      | 8.80        | 9.00 | 9.20 | 0.3465                | 0.3543 | 0.3622 |

| (••••••••) |             |      |      |                       |        |        |

|------------|-------------|------|------|-----------------------|--------|--------|

| Symbol     | millimeters |      |      | inches <sup>(1)</sup> |        |        |

|            | Min         | Тур  | Мах  | Min                   | Тур    | Max    |

| E1         | 6.80        | 7.00 | 7.20 | 0.2677                | 0.2756 | 0.2835 |

| E3         | -           | 5.50 | -    | -                     | 0.2165 | -      |

| е          | -           | 0.50 | -    | -                     | 0.0197 | -      |

| L          | 0.45        | 0.60 | 0.75 | 0.0177                | 0.0236 | 0.0295 |

| L1         | -           | 1.00 | -    | -                     | 0.0394 | -      |

| K          | 0°          | 3.5° | 7°   | 0°                    | 3.5°   | 7°     |

| CCC        | -           | -    | 0.08 | -                     | -      | 0.0031 |

## Table 83. LQFP48 – 7 x 7 mm, low-profile quad flat package mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

1. Dimensions are in millimeters.