Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Operating Temperature<br>Mounting Type | -40°C ~ 85°C (TA)<br>Surface Mount                           |

|----------------------------------------|--------------------------------------------------------------|

| Oscillator Type                        |                                                              |

| Data Converters                        | A/D 9x12b; D/A 1x12b                                         |

| Voltage - Supply (Vcc/Vdd)             | 2V ~ 3.6V                                                    |

| RAM Size                               | 40K x 8                                                      |

| EEPROM Size                            |                                                              |

| Program Memory Type                    | FLASH                                                        |

| Program Memory Size                    | 256KB (256K x 8)                                             |

| Number of I/O                          | 37                                                           |

| Peripherals                            | DMA, I <sup>2</sup> S, POR, PWM, WDT                         |

| Connectivity                           | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB |

| Speed                                  | 72MHz                                                        |

| Core Size                              | 32-Bit Single-Core                                           |

| Core Processor                         | ARM® Cortex®-M4                                              |

| Product Status                         | Active                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Contents

| 1 | Intro | luction                                                                                                                          |

|---|-------|----------------------------------------------------------------------------------------------------------------------------------|

| 2 | Desc  | ription                                                                                                                          |

| 3 | Func  | tional overview                                                                                                                  |

|   | 3.1   | $\text{ARM}^{\textcircled{\text{B}}}$ Cortex $\textcircled{\text{B}}$ -M4 core with FPU with embedded Flash and SRAM $\ldots$ 13 |

|   | 3.2   | Memory protection unit (MPU) 13                                                                                                  |

|   | 3.3   | Embedded Flash memory                                                                                                            |

|   | 3.4   | Embedded SRAM                                                                                                                    |

|   | 3.5   | Boot modes                                                                                                                       |

|   | 3.6   | Cyclic redundancy check (CRC) 14                                                                                                 |

|   | 3.7   | Power management                                                                                                                 |

|   |       | 3.7.1 Power supply schemes                                                                                                       |

|   |       | 3.7.2 Power supply supervision                                                                                                   |

|   |       | 3.7.3 Voltage regulator                                                                                                          |

|   |       | 3.7.4 Low-power modes                                                                                                            |

|   | 3.8   | Interconnect matrix                                                                                                              |

|   | 3.9   | Clocks and startup                                                                                                               |

|   | 3.10  | General-purpose input/outputs (GPIOs) 19                                                                                         |

|   | 3.11  | Direct memory access (DMA) 19                                                                                                    |

|   | 3.12  | Interrupts and events                                                                                                            |

|   |       | 3.12.1 Nested vectored interrupt controller (NVIC)                                                                               |

|   | 3.13  | Fast analog-to-digital converter (ADC) 20                                                                                        |

|   |       | 3.13.1 Temperature sensor                                                                                                        |

|   |       | 3.13.2 Internal voltage reference (V <sub>REFINT</sub> )                                                                         |

|   |       | 3.13.3 V <sub>BAT</sub> battery voltage monitoring                                                                               |

|   |       | 3.13.4 OPAMP reference voltage (VREFOPAMP)                                                                                       |

|   | 3.14  | Digital-to-analog converter (DAC) 21                                                                                             |

|   | 3.15  | Operational amplifier (OPAMP) 21                                                                                                 |

|   | 3.16  | Fast comparators (COMP) 21                                                                                                       |

|   | 3.17  | Timers and watchdogs 22                                                                                                          |

|   |       | 3.17.1 Advanced timer (TIM1)                                                                                                     |

| Perip                            | heral                             | STM32                                                                                                 | F302Cx | STM32   | F302Rx | STM32F                          | 302Vx |  |  |

|----------------------------------|-----------------------------------|-------------------------------------------------------------------------------------------------------|--------|---------|--------|---------------------------------|-------|--|--|

| Flash (Kbytes)                   |                                   | 128                                                                                                   | 256    | 128     | 256    | 128                             | 256   |  |  |

| SRAM (Kbytes)                    | on data bus                       | 32                                                                                                    | 40     | 32      | 40     | 32                              | 40    |  |  |

|                                  | Advanced control                  | 1 (16-bit)                                                                                            |        |         |        |                                 |       |  |  |

| Timers                           | General<br>purpose                | 5 (16-bit)<br>1 (32-bit)                                                                              |        |         |        |                                 |       |  |  |

|                                  | Basic                             |                                                                                                       |        | 1 (16-t | oit)   |                                 |       |  |  |

| PWM channels (                   | all) <sup>(1)</sup>               |                                                                                                       |        | 26      |        |                                 |       |  |  |

| PWM channels (<br>complementary) | except                            |                                                                                                       |        | 20      |        |                                 |       |  |  |

| SPI (I2S) <sup>(2)</sup>         |                                   |                                                                                                       |        | 3 (2)   |        |                                 |       |  |  |

| l <sup>2</sup> C                 |                                   |                                                                                                       |        | 2       |        |                                 |       |  |  |

| Communication                    | USART                             |                                                                                                       |        |         |        |                                 |       |  |  |

| interfaces                       | UART                              |                                                                                                       | 0      | 2       |        |                                 |       |  |  |

|                                  | CAN                               | 1                                                                                                     |        |         |        |                                 |       |  |  |

|                                  | USB                               | 1                                                                                                     |        |         |        |                                 |       |  |  |

|                                  | Normal I/Os<br>(TC, TTa)          | 20                                                                                                    |        | 27      |        | 45 in LQ<br>37 in WLC           |       |  |  |

| GPIOs                            | 5-volt tolerant<br>I/Os (FT, FTf) | 17                                                                                                    |        | 25      |        | 42 in LQFP100<br>40 in WLCSP100 |       |  |  |

| DMA channels                     |                                   | 12                                                                                                    |        |         |        |                                 |       |  |  |

| Capacitive sensi                 | ng channels                       | 1                                                                                                     | 7      | 18 24   |        |                                 |       |  |  |

| 12-bit ADCs                      |                                   |                                                                                                       |        | 2       |        |                                 |       |  |  |

| Number of chanr                  | nels                              |                                                                                                       | 9      | 16      |        | 17                              |       |  |  |

| 12-bit DAC chan                  | nels                              | 1                                                                                                     |        |         |        |                                 |       |  |  |

| Analog comparat                  | tor                               | 4                                                                                                     |        |         |        |                                 |       |  |  |

| Operational amp                  | lifiers                           | 2                                                                                                     |        |         |        |                                 |       |  |  |

| CPU frequency                    |                                   | 72 MHz                                                                                                |        |         |        |                                 |       |  |  |

| Operating voltage                |                                   | 2.0 to 3.6 V                                                                                          |        |         |        |                                 |       |  |  |

| Operating temperature            |                                   | Ambient operating temperature: - 40 to 85 °C / - 40 to 105 °C<br>Junction temperature: - 40 to 125 °C |        |         |        |                                 | 05 °C |  |  |

| Packages                         |                                   | LQF                                                                                                   | -P48   | LQF     | P64    | LQFP<br>WLCSI                   |       |  |  |

Table 2. STM32F302xx family device features and peripheral counts

1. This total number considers also the PWMs generated on the complementary output channels

2. The SPI interfaces can work in an exclusive way in either the SPI mode or the I<sup>2</sup>S audio mode.

# 3.7 **Power management**

# 3.7.1 **Power supply schemes**

- $V_{SS}$ ,  $V_{DD}$  = 2.0 to 3.6 V: external power supply for I/Os and the internal regulator. It is provided externally through  $V_{DD}$  pins.

- V<sub>SSA</sub>, V<sub>DDA</sub> = 2.0 to 3.6 V: external analog power supply for ADC, DAC, comparators operational amplifiers, reset blocks, RCs and PLL. The minimum voltage to be applied to V<sub>DDA</sub> differs from one analog peripheral to another. *Table 3* provides the summary of the V<sub>DDA</sub> ranges for analog peripherals. The V<sub>DDA</sub> voltage level must be always greater or equal to the V<sub>DD</sub> voltage level and must be provided first.

- V<sub>BAT</sub> = 1.65 to 3.6 V: power supply for RTC, external clock 32 kHz oscillator and backup registers (through power switch) when V<sub>DD</sub> is not present.

|                   |                          | ••••                            |

|-------------------|--------------------------|---------------------------------|

| Analog peripheral | Minimum $V_{DDA}$ supply | Maximum V <sub>DDA</sub> supply |

| ADC / COMP        | 2.0 V                    | 3.6 V                           |

| DAC / OPAMP       | 2.4 V                    | 3.6V                            |

Table 3. External analog supply values for analog peripherals

# 3.7.2 Power supply supervision

The device has an integrated power-on reset (POR) and power-down reset (PDR) circuits. They are always active, and ensure proper operation above a threshold of 2 V. The device remains in reset mode when the monitored supply voltage is below a specified threshold, VPOR/PDR, without the need for an external reset circuit.

- The POR monitors only the V<sub>DD</sub> supply voltage. During the startup phase it is required that V<sub>DDA</sub> should arrive first and be greater than or equal to V<sub>DD</sub>.

- The PDR monitors both the V<sub>DD</sub> and V<sub>DDA</sub> supply voltages, however the V<sub>DDA</sub> power supply supervisor can be disabled (by programming a dedicated Option bit) to reduce the power consumption if the application design ensures that V<sub>DDA</sub> is higher than or equal to V<sub>DD</sub>.

The device features an embedded programmable voltage detector (PVD) that monitors the  $V_{DD}$  power supply and compares it to the VPVD threshold. An interrupt can be generated when  $V_{DD}$  drops below the  $V_{PVD}$  threshold and/or when  $V_{DD}$  is higher than the  $V_{PVD}$  threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software.

# 3.7.3 Voltage regulator

The regulator has three operation modes: main (MR), low-power (LPR), and power-down.

- The MR mode is used in the nominal regulation mode (Run)

- The LPR mode is used in Stop mode.

- The power-down mode is used in Standby mode: the regulator output is in high impedance, and the kernel circuitry is powered down thus inducing zero consumption.

The voltage regulator is always enabled after reset. It is disabled in Standby mode.

• 17-bit Auto-reload counter for periodic interrupt with wakeup from STOP/STANDBY capability.

The RTC clock sources can be:

- A 32.768 kHz external crystal

- A resonator or oscillator

- The internal low-power RC oscillator (typical frequency of 40 kHz)

- The high-speed external clock divided by 32.

# 3.19 Inter-integrated circuit interface (I<sup>2</sup>C)

Up to two  $I^2C$  bus interfaces can operate in multimaster and slave modes. They can support standard (up to 100 KHz), fast (up to 400 KHz) and fast mode + (up to 1 MHz) modes.

Both support 7-bit and 10-bit addressing modes, multiple 7-bit slave addresses (2 addresses, 1 with configurable mask). They also include programmable analog and digital noise filters.

|                                     | Analog filter                                         | Digital filter                                                                                       |

|-------------------------------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| Pulse width of<br>suppressed spikes | 50 ns                                                 | Programmable length from 1 to 15<br>I2C peripheral clocks                                            |

| Benefits                            | Available in Stop mode                                | <ol> <li>Extra filtering capability vs.<br/>standard requirements.</li> <li>Stable length</li> </ol> |

| Drawbacks                           | Variations depending on temperature, voltage, process | Wakeup from Stop on address<br>match is not available when digital<br>filter is enabled.             |

#### Table 6. Comparison of I2C analog and digital filters

In addition, they provide hardware support for SMBUS 2.0 and PMBUS 1.1: ARP capability, Host notify protocol, hardware CRC (PEC) generation/verification, timeouts verifications and ALERT protocol management. They also have a clock domain independent from the CPU clock, allowing the I2Cx (x=1,2) to wake up the MCU from Stop mode on address match.

The I2C interfaces can be served by the DMA controller.

Refer to *Table 7* for the features available in I2C1 and I2C2.

| Table 7. STM32F302xB/STM32F302xC I <sup>2</sup> C | c implem | nentation |

|---------------------------------------------------|----------|-----------|

|---------------------------------------------------|----------|-----------|

| I2C features <sup>(1)</sup>                                 | I2C1 | I2C2 |

|-------------------------------------------------------------|------|------|

| 7-bit addressing mode                                       | Х    | Х    |

| 10-bit addressing mode                                      | Х    | Х    |

| Standard mode (up to 100 kbit/s)                            | х    | Х    |

| Fast mode (up to 400 kbit/s)                                | Х    | Х    |

| Fast Mode Plus with 20mA output drive I/Os (up to 1 Mbit/s) | Х    | Х    |

| Independent clock                                           | Х    | Х    |

# 3.22 Serial peripheral interface (SPI)/Inter-integrated sound interfaces (I2S)

Up to three SPIs are able to communicate up to 18 Mbits/s in slave and master modes in full-duplex and half-duplex communication modes. The 3-bit prescaler gives 8 master mode frequencies and the frame size is configurable from 4 bits to 16 bits.

Two standard I2S interfaces (multiplexed with SPI2 and SPI3) supporting four different audio standards can operate as master or slave at half-duplex and full duplex communication modes. They can be configured to transfer 16 and 24 or 32 bits with 16-bit or 32-bit data resolution and synchronized by a specific signal. Audio sampling frequency from 8 kHz up to 192 kHz can be set by 8-bit programmable linear prescaler. When operating in master mode it can output a clock for an external audio component at 256 times the sampling frequency.

Refer to Table 9 for the features available in SPI1, SPI2 and SPI3.

| SPI features <sup>(1)</sup> | SPI1 | SPI2 | SPI3 |

|-----------------------------|------|------|------|

| Hardware CRC calculation    | Х    | Х    | Х    |

| Rx/Tx FIFO                  | Х    | Х    | Х    |

| NSS pulse mode              | Х    | Х    | Х    |

| I2S mode                    | -    | Х    | Х    |

| TI mode                     | Х    | Х    | Х    |

Table 9. STM32F302xB/STM32F302xC SPI/I2S implementation

1. X = supported.

# 3.23 Controller area network (CAN)

The CAN is compliant with specifications 2.0A and B (active) with a bit rate up to 1 Mbit/s. It can receive and transmit standard frames with 11-bit identifiers as well as extended frames with 29-bit identifiers. It has three transmit mailboxes, two receive FIFOs with 3 stages and 14 scalable filter banks.

# 3.24 Universal serial bus (USB)

The STM32F302xB/STM32F302xC devices embed an USB device peripheral compatible with the USB full-speed 12 Mbs. The USB interface implements a full-speed (12 Mbit/s) function interface. It has software-configurable endpoint setting and suspend/resume support. The dedicated 48 MHz clock is generated from the internal main PLL (the clock source must use a HSE crystal oscillator). The USB has a dedicated 512-bytes SRAM memory for data transmission and reception.

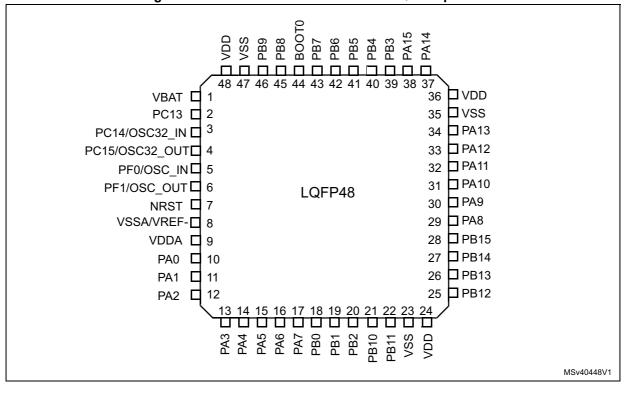

# 4 Pinouts and pin description

STM32F302xB STM32F302xC

Pinouts and pin description

| Port<br>&<br>Pin<br>Name | AF0           | AF1                  | AF2          | AF3            | AF4           | AF5           | AF6                  | AF7               | AF8           | AF9            | AF10         | AF11     | AF12           | AF14       | AF1                    |

|--------------------------|---------------|----------------------|--------------|----------------|---------------|---------------|----------------------|-------------------|---------------|----------------|--------------|----------|----------------|------------|------------------------|

| PA0                      | -             | TIM2_<br>CH1_<br>ETR | -            | TSC_<br>G1_IO1 | -             | -             | -                    | USART2_<br>CTS    | COMP1<br>_OUT |                |              | -        | -              | -          | EVEI<br>OUT            |

| PA1                      | RTC_<br>REFIN | TIM2_<br>CH2         | -            | TSC_<br>G1_IO2 | -             | -             | -                    | USART2_<br>RTS_DE |               | TIM15_<br>CH1N | -            | -        | -              | -          | EVE<br>OUT             |

| PA2                      | -             | TIM2_<br>CH3         | -            | TSC_<br>G1_IO3 | -             | -             | -                    | USART2_<br>TX     | COMP2<br>_OUT | TIM15_<br>CH1  | -            | -        | -              | -          | EVE<br>OUT             |

| PA3                      | -             | TIM2_<br>CH4         | -            | TSC_<br>G1_IO4 | -             | -             | -                    | USART2_<br>RX     | -             | TIM15_<br>CH2  | -            | -        | -              | -          | EVE<br>OU1             |

| PA4                      | -             | -                    | TIM3_<br>CH2 | TSC_<br>G2_IO1 | -             | SPI1_<br>NSS  | SPI3_NSS,<br>I2S3_WS | USART2_<br>CK     | -             | -              | -            | -        | -              | -          | EVE<br>OU1             |

| PA5                      | -             | TIM2_<br>CH1_<br>ETR | -            | TSC_<br>G2_IO2 | -             | SPI1_<br>SCK  | -                    | -                 | -             | -              | -            | -        | -              | -          | EVE<br>OU1             |

| PA6                      | -             | TIM16_<br>CH1        | TIM3_<br>CH1 | TSC_<br>G2_IO3 |               | SPI1_<br>MISO | TIM1_BKIN            | -                 | COMP1<br>_OUT | -              | -            | -        | -              | -          | EVE<br>OU <sup>-</sup> |

| PA7                      | -             | TIM17_<br>CH1        | TIM3_<br>CH2 | TSC_<br>G2_IO4 |               | SPI1_<br>MOSI | TIM1_CH1N            | -                 | COMP2<br>_OUT | -              | -            | -        | -              | -          | EVE<br>OU1             |

| PA8                      | МСО           | -                    | -            | -              | I2C2_<br>SMBA | I2S2_<br>MCK  | TIM1_CH1             | USART1_<br>CK     |               | -              | TIM4_<br>ETR | -        | -              | -          | EVE<br>OU1             |

| PA9                      | -             | -                    | -            | TSC_<br>G4_IO1 | I2C2_<br>SCL  | I2S3_<br>MCK  | TIM1_CH2             | USART1_<br>TX     |               | TIM15_<br>BKIN | TIM2_<br>CH3 | -        | -              | -          | EVE<br>OU1             |

| PA10                     | -             | TIM17_<br>BKIN       | -            | TSC_<br>G4_IO2 | I2C2_<br>SDA  | -             | TIM1_CH3             | USART1_<br>RX     | COMP6<br>_OUT | -              | TIM2_<br>CH4 |          | -              | -          | EVE<br>OU1             |

| PA11                     | -             | -                    | -            | -              | -             | -             | TIM1_CH1N            | USART1_<br>CTS    | COMP1<br>OUT  | CAN_RX         | TIM4_<br>CH1 | TIM1_CH4 | TIM1_<br>BKIN2 | USB_<br>DM | EVE<br>OU1             |

DocID025186 Rev 7

43/144

নি

# 6.3 Operating conditions

# 6.3.1 General operating conditions

| Table 24. | General | operating | conditions |

|-----------|---------|-----------|------------|

|-----------|---------|-----------|------------|

| Symbol             | Parameter                                                     | Conditions                                 | Min  | Max                   | Unit |  |

|--------------------|---------------------------------------------------------------|--------------------------------------------|------|-----------------------|------|--|

| f <sub>HCLK</sub>  | Internal AHB clock frequency                                  | -                                          | 0    | 72                    |      |  |

| f <sub>PCLK1</sub> | Internal APB1 clock frequency                                 | -                                          | 0    | 36                    | MHz  |  |

| f <sub>PCLK2</sub> | Internal APB2 clock frequency                                 | -                                          | 0    | 72                    |      |  |

| V <sub>DD</sub>    | Standard operating voltage                                    | -                                          | 2    | 3.6                   | V    |  |

|                    | Analog operating voltage<br>(OPAMP and DAC not used)          | Must have a potential                      | 2    | 3.6                   | V    |  |

| V <sub>DDA</sub>   | Analog operating voltage (OPAMP and DAC used)                 | equal to or higher than<br>V <sub>DD</sub> | 2.4  | 3.6                   | V    |  |

| V <sub>BAT</sub>   | Backup operating voltage                                      | -                                          | 1.65 | 3.6                   | V    |  |

|                    |                                                               | TC I/O                                     | -0.3 | V <sub>DD</sub> +0.3  | v    |  |

| V                  | I/O input voltage                                             | TTa I/O                                    | -0.3 | V <sub>DDA</sub> +0.3 |      |  |

| V <sub>IN</sub>    |                                                               | FT and FTf I/O <sup>(1)</sup>              | -0.3 | 5.5                   |      |  |

|                    |                                                               | BOOT0                                      | 0    | 5.5                   |      |  |

|                    |                                                               | WLCSP100                                   | -    | 500                   |      |  |

| Р                  | Power dissipation at $T_A =$<br>85 °C for suffix 6 or $T_A =$ | LQFP100                                    | -    | 488                   |      |  |

| $P_{D}$            | 105 °C for suffix $7^{(2)}$                                   | LQFP64                                     | -    | 444                   | mW   |  |

|                    |                                                               | LQFP48                                     | -    | 364                   |      |  |

|                    | Ambient temperature for 6 dissipation                         | Maximum power<br>dissipation               | -40  | 85                    | °C   |  |

| т.                 | suffix version                                                | Low-power dissipation <sup>(3)</sup>       | -40  | 105                   |      |  |

|                    | Ambient temperature for 7                                     | Maximum power<br>dissipation               | -40  | 105                   | °C   |  |

|                    | suffix version                                                | Low-power dissipation <sup>(3)</sup>       | -40  | 125                   |      |  |

| т.                 | lunction tomporature range                                    | 6 suffix version                           | -40  | 105                   | °C   |  |

| TJ                 | Junction temperature range                                    | 7 suffix version                           | -40  | 125                   | U    |  |

1. To sustain a voltage higher than  $V_{DD}$ +0.3 V, the internal pull-up/pull-down resistors must be disabled.

If T<sub>A</sub> is lower, higher P<sub>D</sub> values are allowed as long as T<sub>J</sub> does not exceed T<sub>Jmax</sub> (see Section 7.5: Thermal characteristics).

In low-power dissipation state, T<sub>A</sub> can be extended to this range as long as T<sub>J</sub> does not exceed T<sub>Jmax</sub> (see Section 7.5: Thermal characteristics).

| Symbol                              | Parameter               | Conditions   | Min <sup>(1)</sup> | Тур  | Max <sup>(1)</sup> | Unit |  |

|-------------------------------------|-------------------------|--------------|--------------------|------|--------------------|------|--|

| N/                                  | DVD three hold 0        | Rising edge  | 2.1                | 2.18 | 2.26               |      |  |

| V <sub>PVD0</sub>                   | PVD threshold 0         | Falling edge | 2                  | 2.08 | 2.16               |      |  |

| M                                   | PVD threshold 1         | Rising edge  | 2.19               | 2.28 | 2.37               |      |  |

| V <sub>PVD1</sub>                   | PVD theshold 1          | Falling edge | 2.09               | 2.18 | 2.27               |      |  |

| V                                   | PVD threshold 2         | Rising edge  | 2.28               | 2.38 | 2.48               |      |  |

| V <sub>PVD2</sub>                   | PVD threshold 2         | Falling edge | 2.18               | 2.28 | 2.38               |      |  |

| V                                   | PVD threshold 3         | Rising edge  | 2.38               | 2.48 | 2.58               |      |  |

| V <sub>PVD3</sub>                   |                         | Falling edge | 2.28               | 2.38 | 2.48               | V    |  |

| V                                   | PVD threshold 4         | Rising edge  | 2.47               | 2.58 | 2.69               | v    |  |

| V <sub>PVD4</sub>                   |                         | Falling edge | 2.37               | 2.48 | 2.59               |      |  |

| N/                                  | PVD threshold 5         | Rising edge  | 2.57               | 2.68 | 2.79               |      |  |

| V <sub>PVD5</sub>                   |                         | Falling edge | 2.47               | 2.58 | 2.69               |      |  |

| M                                   | PVD threshold 6         | Rising edge  | 2.66               | 2.78 | 2.9                |      |  |

| V <sub>PVD6</sub>                   | PVD threshold 6         | Falling edge | 2.56               | 2.68 | 2.8                |      |  |

| M                                   | PVD threshold 7         | Rising edge  | 2.76               | 2.88 | 3                  |      |  |

| V <sub>PVD7</sub>                   |                         | Falling edge | 2.66               | 2.78 | 2.9                |      |  |

| V <sub>PVDhyst</sub> <sup>(2)</sup> | PVD hysteresis          | -            | -                  | 100  | -                  | mV   |  |

| IDD(PVD)                            | PVD current consumption | -            | -                  | 0.15 | 0.26               | μA   |  |

Table 27. Programmable voltage detector characteristics

1. Guaranteed by characterization results.

2. Guaranteed by design.

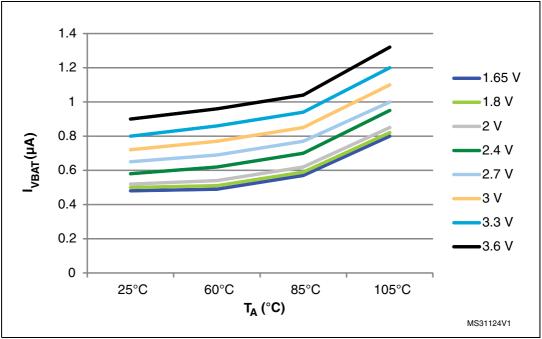

| Symbol   | Para<br>meter     | Conditions<br>(1)                                                                             | Typ @V <sub>BAT</sub> |      |      |      |      |      |      |      | Max<br>@V <sub>BAT</sub> = 3.6 V <sup>(2)</sup> |                          |                           | Unit |

|----------|-------------------|-----------------------------------------------------------------------------------------------|-----------------------|------|------|------|------|------|------|------|-------------------------------------------------|--------------------------|---------------------------|------|

| Symbol   |                   |                                                                                               | 1.65V                 | 1.8V | 2V   | 2.4V | 2.7V | 3V   | 3.3V | 3.6V | T <sub>A</sub> =<br>25°C                        | T <sub>A</sub> =<br>85°C | T <sub>A</sub> =<br>105°C |      |

|          | Backup<br>domain  | LSE & RTC<br>ON; "Xtal<br>mode"<br>lower<br>driving<br>capability;<br>LSEDRV[1:<br>0] = '00'  | 0.48                  | 0.50 | 0.52 | 0.58 | 0.65 | 0.72 | 0.80 | 0.90 | 1.1                                             | 1.5                      | 2.0                       |      |

| IDD_VBAT | supply<br>current | LSE & RTC<br>ON; "Xtal<br>mode"<br>higher<br>driving<br>capability;<br>LSEDRV[1:<br>0] = '11' | 0.83                  | 0.86 | 0.90 | 0.98 | 1.03 | 1.10 | 1.20 | 1.30 | 1.5                                             | 2.2                      | 2.9                       | μΑ   |

Table 34. Typical and maximum current consumption from  $V_{\text{BAT}}$  supply

1. Crystal used: Abracon ABS07-120-32.768 kHz-T with a CL of 6 pF for typical values.

2. Guaranteed by characterization results.

Figure 13. Typical V<sub>BAT</sub> current consumption (LSE and RTC ON/LSEDRV[1:0] = '00')

# On-chip peripheral current consumption

The MCU is placed under the following conditions:

- all I/O pins are in analog input configuration

- all peripherals are disabled unless otherwise mentioned

- the given value is calculated by measuring the current consumption

- with all peripherals clocked off

- with only one peripheral clocked on

- ambient operating temperature at 25°C and  $V_{DD} = V_{DDA} = 3.3$  V.

## Table 38. Peripheral current consumption

| Derinherol                 | Typical consumption <sup>(1)</sup> | Unit   |

|----------------------------|------------------------------------|--------|

| Peripheral                 | I <sub>DD</sub>                    | Onit   |

| BusMatrix <sup>(2)</sup>   | 12.6                               |        |

| DMA1                       | 7.6                                |        |

| DMA2                       | 6.1                                |        |

| CRC                        | 2.1                                |        |

| GPIOA                      | 10.0                               |        |

| GPIOB                      | 10.3                               |        |

| GPIOC                      | 2.2                                |        |

| GPIOD                      | 8.8                                |        |

| GPIOE                      | 3.3                                |        |

| GPIOF                      | 3.0                                |        |

| TSC                        | 5.5                                |        |

| ADC1&2                     | 17.3                               |        |

| APB2-Bridge <sup>(3)</sup> | 3.6                                |        |

| SYSCFG                     | 7.3                                | μA/MHz |

| TIM1                       | 40.0                               |        |

| SPI1                       | 8.8                                |        |

| USART1                     | 23.3                               |        |

| TIM15                      | 17.1                               |        |

| TIM16                      | 10.1                               |        |

| TIM17                      | 11.0                               |        |

| APB1-Bridge <sup>(3)</sup> | 6.1                                |        |

| TIM2                       | 49.1                               |        |

| TIM3                       | 38.8                               |        |

| TIM4                       | 38.3                               |        |

# 6.3.6 Wakeup time from low-power mode

The wakeup times given in *Table 39* are measured starting from the wakeup event trigger up to the first instruction executed by the CPU:

- For Stop or Sleep mode: the wakeup event is WFE.

- WKUP1 (PA0) pin is used to wakeup from Standby, Stop and Sleep modes.

All timings are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 24*.

| Symbol                | Parameter                   | Conditions                        | Typ @Vdd, V <sub>DD</sub> = V <sub>DDA</sub> |       |       |      |       |       |     | Unit                   |

|-----------------------|-----------------------------|-----------------------------------|----------------------------------------------|-------|-------|------|-------|-------|-----|------------------------|

| Symbol                |                             | Conditions                        | 2.0 V                                        | 2.4 V | 2.7 V | 3 V  | 3.3 V | 3.6 V | Мах | onit                   |

|                       | Wakoup from                 | Regulator in run mode             | 4.1                                          | 3.9   | 3.8   | 3.7  | 3.6   | 3.5   | 4.5 |                        |

| <sup>t</sup> wustop   | Wakeup from<br>Stop mode    | Regulator in<br>low-power<br>mode | 7.9                                          | 6.7   | 6.1   | 5.7  | 5.4   | 5.2   | 9   | μs                     |

| $t_{WUSTANDBY}^{(1)}$ | Wakeup from<br>Standby mode | LSI and<br>IWDG OFF               | 69.2                                         | 60.3  | 56.4  | 53.7 | 51.7  | 50    | 100 |                        |

| t <sub>WUSLEEP</sub>  | Wakeup from<br>Sleep mode   | -                                 |                                              | 6     |       |      |       |       | -   | CPU<br>clock<br>cycles |

Table 39. Low-power mode wakeup timings

1. Guaranteed by characterization results.

# 6.3.7 External clock source characteristics

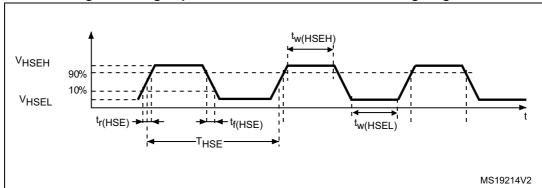

# High-speed external user clock generated from an external source

In bypass mode the HSE oscillator is switched off and the input pin is a standard GPIO. The external clock signal has to respect the I/O characteristics in *Section 6.3.14*. However, the recommended clock input waveform is shown in *Figure 14*.

| Symbol                                       | Parameter                                              | Conditions | Min         | Тур | Max             | Unit |

|----------------------------------------------|--------------------------------------------------------|------------|-------------|-----|-----------------|------|

| f <sub>HSE_ext</sub>                         | User external clock source<br>frequency <sup>(1)</sup> |            | 1           | 8   | 32              | MHz  |

| V <sub>HSEH</sub>                            | OSC_IN input pin high level voltage                    |            | $0.7V_{DD}$ | -   | V <sub>DD</sub> | V    |

| V <sub>HSEL</sub>                            | OSC_IN input pin low level voltage                     | -          | $V_{SS}$    | -   | $0.3V_{DD}$     |      |

| t <sub>w(HSEH)</sub><br>t <sub>w(HSEL)</sub> | OSC_IN high or low time <sup>(1)</sup>                 |            | 15          | -   | -               | 20   |

| t <sub>r(HSE)</sub><br>t <sub>f(HSE)</sub>   | OSC_IN rise or fall time <sup>(1)</sup>                |            | -           | -   | 20              | ns   |

1. Guaranteed by design.

## Figure 14. High-speed external clock source AC timing diagram

### **Prequalification trials**

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the Oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

## **Electromagnetic Interference (EMI)**

The electromagnetic field emitted by the device are monitored while a simple application is executed (toggling 2 LEDs through the I/O ports). This emission test is compliant with IEC 61967-2 standard which specifies the test board and the pin loading.

| Symbol           | Parameter  | Conditions                                                                           | Monitored       | Max vs. [f <sub>HSE</sub> /f <sub>HCLK</sub> ] | Unit |

|------------------|------------|--------------------------------------------------------------------------------------|-----------------|------------------------------------------------|------|

| Symbol 1         | Farameter  | contaitions                                                                          | frequency band  | 8/72 MHz                                       | Onic |

|                  |            | $V_{DD}$ = 3.6 V, $T_A$ = 25 °C,<br>LQFP100 package<br>compliant with IEC<br>61967-2 | 0.1 to 30 MHz   | 7                                              |      |

| 6                | Peak level |                                                                                      | 30 to 130 MHz   | 20                                             | dBµV |

| S <sub>EMI</sub> | reak level |                                                                                      | 130 MHz to 1GHz | 27                                             |      |

|                  |            | 01307-2                                                                              | SAE EMI Level   | 4                                              | -    |

Table 50. EMI characteristics

# 6.3.12 Electrical sensitivity characteristics

Based on three different tests (ESD, LU) using specific measurement methods, the device is stressed in order to determine its performance in terms of electrical sensitivity.

### Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts  $\times$  (n+1) supply pins). This test conforms to the JESD22-A114, ANSI/ESD STM5.3.1 standard.

| Symbol                | Ratings                                                  | Conditions                                                  |                                | Class | Maximum<br>value <sup>(1)</sup> | Unit |

|-----------------------|----------------------------------------------------------|-------------------------------------------------------------|--------------------------------|-------|---------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic<br>discharge voltage<br>(human body model) | $T_A = +25 \ ^{\circ}C$ , conforming to JESD22-A114         |                                | 2     | 2000                            |      |

|                       | Electrostatic                                            |                                                             | WLCSP100<br>package            | 3     | 250                             | V    |

| V <sub>ESD(CDM)</sub> | discharge voltage<br>(charge device model)               | T <sub>A</sub> = +25 °C, conforming<br>to ANSI/ESD STM5.3.1 | Packages<br>except<br>WLCSP100 | 4     | 500                             |      |

Table 51. ESD absolute maximum ratings

1. Guaranteed by characterization results.

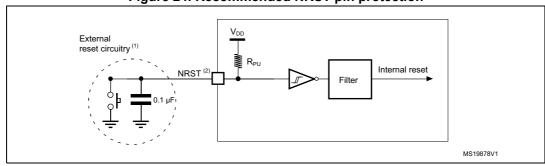

Figure 24. Recommended NRST pin protection

1. The reset network protects the device against parasitic resets.

The user must ensure that the level on the NRST pin can go below the V<sub>IL(NRST)</sub> max level specified in Table 57. Otherwise the reset will not be taken into account by the device.

## 6.3.16 Timer characteristics

The parameters given in *Table 58* are guaranteed by design.

Refer to Section 6.3.14: I/O port characteristics for details on the input/output alternate function characteristics (output compare, input capture, external clock, PWM output).

| Symbol                 | Parameter                   | Conditions                     | Min                                                                                       | Max                     | Unit                 |  |

|------------------------|-----------------------------|--------------------------------|-------------------------------------------------------------------------------------------|-------------------------|----------------------|--|

|                        |                             | -                              | 1                                                                                         | -                       | t <sub>TIMxCLK</sub> |  |

| t <sub>res(TIM)</sub>  | Timer resolution time       | f <sub>TIMxCLK</sub> = 72 MHz  | 13.9                                                                                      | -                       | ns                   |  |

| 163(1110)              |                             | f <sub>TIM1CLK</sub> = 144 MHz | 6.95                                                                                      | -                       | ns                   |  |

| f <sub>EXT</sub>       | Timer external clock        | -                              | 0                                                                                         | f <sub>TIMxCLK</sub> /2 | MHz                  |  |

| 'EXT                   | frequency on CH1 to CH4     | f <sub>TIMxCLK</sub> = 72 MHz  | 0         ITIMxCLK/2           0         36           -         16           -         32 |                         | MHz                  |  |

| Pos                    | Timer resolution            | TIMx (except TIM2)             | -                                                                                         | 16                      | bit                  |  |

| Res <sub>TIM</sub>     |                             | TIM2                           | -                                                                                         | 32                      | Dit                  |  |

|                        |                             | -                              | 1                                                                                         | 65536                   | t <sub>TIMxCLK</sub> |  |

| t <sub>COUNTER</sub>   | 16-bit counter clock period | f <sub>TIMxCLK</sub> = 72 MHz  | 0.0139                                                                                    | 910                     | μs                   |  |

| COUNTER                |                             | f <sub>TIM1CLK</sub> = 144 MHz | 0.0069                                                                                    | 455                     | μs                   |  |

|                        |                             | -                              | -                                                                                         | 65536 × 65536           | t <sub>TIMxCLK</sub> |  |

| t <sub>MAX_COUNT</sub> | Maximum possible count      | f <sub>TIMxCLK</sub> = 72 MHz  | -                                                                                         | 59.65                   | s                    |  |

|                        | with 32-bit counter         | f <sub>TIM1CLK</sub> = 144 MHz | -                                                                                         | 29.825                  | s                    |  |

Table 58. TIMx<sup>(1)(2)</sup> characteristics

1. TIMx is used as a general term to refer to the TIM1, TIM2, TIM3, TIM4, TIM15, TIM16 and TIM17 timers.

2. Guaranteed by design.

# 6.3.17 Communications interfaces

# I<sup>2</sup>C interface characteristics

The I<sup>2</sup>C interface meets the timings requirements of the I<sup>2</sup>C-bus specification and user manual rev.03 for:

- Standard-mode (Sm) : with a bit rate up to 100 Kbits/s

- Fast-mode (Fm) : with a bit rate up to 400 Kbits/s

- Fast-mode Plus (Fm+) : with a bit rate up to 1Mbits/s

The I<sup>2</sup>C timings requirements are guaranteed by design when the I<sup>2</sup>C peripheral is properly configured (refer to Reference manual).

The SDA and SCL I/O requirements are met with the following restrictions: the SDA and SCL I/O pins are "true" open-drain. When configured as open-drain, the PMOS connected between the I/O pin and VDDIOx is disabled, but is still present. Only FTf I/O pins support Fm+ low level output current maximum requirement. Refer to *Section 6.3.14: I/O port characteristics*.

All I<sup>2</sup>C I/Os embed an analog filter. refer to the *Table 62: I2C analog filter characteristics*.

| Symbol              | Parameter                                                                                       | Standa | rd mode             | Fast m | ode                | Fast Mo | de Plus                                                                                                         | Unit |

|---------------------|-------------------------------------------------------------------------------------------------|--------|---------------------|--------|--------------------|---------|-----------------------------------------------------------------------------------------------------------------|------|

| Symbol              | Parameter                                                                                       | Min    | Мах                 | Min    | Мах                | Min     | Max<br>1000<br>-<br>120<br>120<br>0.45 <sup>(2)</sup><br>0.45 <sup>(2)</sup><br>-<br>1<br>-<br>-<br>-<br>-<br>- | Unit |

| f <sub>SCL</sub>    | SCL clock frequency                                                                             | 0      | 100                 | 0      | 400                | 0       | 1000                                                                                                            | KHz  |

| t <sub>LOW</sub>    | Low period of the SCL clock                                                                     | 4.7    | -                   | 1.3    | -                  | 0.5     | -                                                                                                               | μs   |

| t <sub>HIGH</sub>   | High Period of the SCL clock                                                                    | 4      |                     | 0.6    |                    | 0.26    | -                                                                                                               | μs   |

| t <sub>r</sub>      | Rise time of both SDA and SCL signals                                                           | -      | 1000                | -      | 300                | -       | 120                                                                                                             | ns   |

| t <sub>f</sub>      | Fall time of both SDA and SCL signals                                                           | -      | 300                 | -      | 300                | -       | 120                                                                                                             | ns   |

| t <sub>HD;DAT</sub> | Data hold time                                                                                  | 0      | -                   | 0      | -                  | 0       | -                                                                                                               | μs   |

| t <sub>VD;DAT</sub> | Data valid time                                                                                 | -      | 3.45 <sup>(2)</sup> | -      | 0.9 <sup>(2)</sup> | -       | 0.45 <sup>(2)</sup>                                                                                             | μs   |

| t <sub>VD;ACK</sub> | Data valid acknowledge time                                                                     | -      | 3.45 <sup>(2)</sup> | -      | 0.9 <sup>(2)</sup> | -       | 0.45 <sup>(2)</sup>                                                                                             | μs   |

| t <sub>SU;DAT</sub> | Data setup time                                                                                 | 250    | -                   | 100    | -                  | 50      | -                                                                                                               | ns   |

| t <sub>hd:sta</sub> | Hold time (repeated) START condition                                                            | 4.0    | -                   | 0.6    | -                  | 0.26    | -                                                                                                               | μs   |

| t <sub>su:sta</sub> | Set-up time for a repeated START condition                                                      | 4.7    | -                   | 0.6    | -                  | 0.26    |                                                                                                                 | μs   |

| t <sub>su:sтo</sub> | Set-up time for STOP condition                                                                  | 4.0    | -                   | 0.6    | -                  | 0.26    | -                                                                                                               | μs   |

| t <sub>BUF</sub>    | Bus free time between a STOP and START condition                                                | 4.7    | -                   | 1.3    | -                  | 0.5     | -                                                                                                               | μs   |

| Cb                  | Capacitive load for each bus line                                                               | -      | 400                 | -      | 400                | -       | 550                                                                                                             | pF   |

| t <sub>SP</sub>     | Pulse width of spikes that are<br>suppressed by the analog filter for<br>Standard and Fast mode | 0      | 50 <sup>(3)</sup>   | 0      | 50 <sup>(3)</sup>  | -       | -                                                                                                               | ns   |

| Table 61. I2C timing | as specification | (see I2C | specification. | rev.03. | June 2007) <sup>(1)</sup> |

|----------------------|------------------|----------|----------------|---------|---------------------------|

|                      | jo opoomoanon    | 1000120  | opoolinoution, | 101.00, |                           |

| Symbol        | Parameter               | C                                                                  | Conditions                       |                     |      | Max<br>(4) | Unit |

|---------------|-------------------------|--------------------------------------------------------------------|----------------------------------|---------------------|------|------------|------|

|               |                         |                                                                    | Single ended                     | Fast channel 5.1 Ms | -    | ±6.5       |      |

| ET            | Total                   |                                                                    | Single ended                     | Slow channel 4.8 Ms | -    | ±6.5       |      |

|               | unadjusted<br>error     |                                                                    | Differential                     | Fast channel 5.1 Ms | -    | ±4         |      |

|               |                         |                                                                    | Differential                     | Slow channel 4.8 Ms | -    | ±4.5       |      |

|               |                         |                                                                    | Single and d                     | Fast channel 5.1 Ms | -    | ±3         |      |

| ГО            | Offect error            |                                                                    | Single ended                     | Slow channel 4.8 Ms | -    | ±3         |      |

| EO            | EO Offset error         |                                                                    | Differential                     | Fast channel 5.1 Ms | _    | ±2.5       |      |

|               |                         | Dillerential                                                       | Slow channel 4.8 Ms              | -                   | ±2.5 |            |      |

|               |                         |                                                                    |                                  | Fast channel 5.1 Ms | -    | ±6         |      |

| 50            | EG Gain error           | Single ended                                                       | Slow channel 4.8 Ms              | _                   | ±6   |            |      |

| EG Gain error |                         | Differential                                                       | Fast channel 5.1 Ms              | _                   | ±3.5 | LSB        |      |

|               |                         | Differential                                                       | Slow channel 4.8 Ms              | -                   | ±4   |            |      |

|               |                         | earity $2.0 \text{ V} \le \text{V}_{\text{DDA}} \le 3.6 \text{ V}$ | Single ended -<br>Differential - | Fast channel 5.1 Ms | -    | ±1.5       | -    |

| 50            | Differential            |                                                                    |                                  | Slow channel 4.8 Ms | -    | ±1.5       |      |

| ED            | error                   |                                                                    |                                  | Fast channel 5.1 Ms | _    | ±1.5       |      |

|               |                         | 64-pin package                                                     |                                  | Slow channel 4.8 Ms | -    | ±1.5       |      |

|               |                         |                                                                    | Cinalo ondod                     | Fast channel 5.1 Ms | -    | ±3         |      |

| -             | Integral                |                                                                    | Single ended                     | Slow channel 4.8 Ms | _    | ±3.5       |      |

| EL            | linearity<br>error      |                                                                    | Differential                     | Fast channel 5.1 Ms | -    | ±2         |      |

|               |                         |                                                                    | Differential                     | Slow channel 4.8 Ms | -    | ±2.5       |      |

|               |                         |                                                                    | Cinalo ondod                     | Fast channel 5.1 Ms | 10.4 | -          |      |

| ENOB          | Effective               |                                                                    | Single ended                     | Slow channel 4.8 Ms | 10.4 | -          | h:to |

| (5)           | number of bits          |                                                                    | Differential                     | Fast channel 5.1 Ms | 10.8 | -          | bits |

|               |                         |                                                                    | Differential                     | Slow channel 4.8 Ms | 10.8 | -          | 1    |

|               |                         |                                                                    | Single and d                     | Fast channel 5.1 Ms | 64   | -          |      |

| SINAD         | Signal-to-<br>noise and |                                                                    | Single ended                     | Slow channel 4.8 Ms | 63   | -          | dB   |

| (5)           | distortion<br>ratio     |                                                                    | Differential                     | Fast channel 5.1 Ms | 67   | -          |      |

|               | Tallo                   |                                                                    | Differential                     | Slow channel 4.8 Ms | 67   | -          |      |

Table 73. ADC accuracy, 64-pin packages<sup>(1)(2)(3)</sup>

#### STM32F302xB STM32F302xC

| Symbol                             | Parameter                                                                        | Conditions                                                 | Min | Тур | Мах | Unit |

|------------------------------------|----------------------------------------------------------------------------------|------------------------------------------------------------|-----|-----|-----|------|

| t <sub>WAKEUP</sub> <sup>(3)</sup> | DAC Control register)                                                            | C <sub>LOAD</sub> ∕50 pF,<br>R <sub>LOAD</sub> ≥ 5 kΩ      | -   | 6.5 | 10  | μs   |

| PSRR+ <sup>(1)</sup>               | Power supply rejection ratio<br>(to V <sub>DDA</sub> ) (static DC<br>measurement | C <sub>LOAD</sub> = 50 pF,<br>No R <sub>LOAD</sub> ≥ 5 kΩ, | -   | -67 | -40 | dB   |

#### Table 75. DAC characteristics (continued)

1. Guaranteed by design.

2. Quiescent mode refers to the state of the DAC a keeping steady value on the output, so no dynamic consumption is involved.

3. Guaranteed by characterization results.

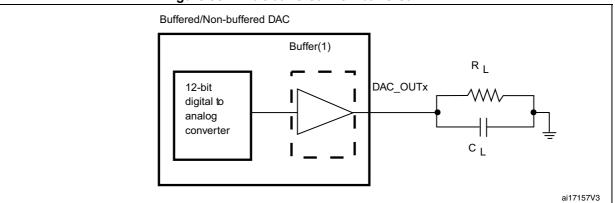

### Figure 36. 12-bit buffered /non-buffered DAC

1. The DAC integrates an output buffer that can be used to reduce the output impedance and to drive external loads directly without the use of an external operational amplifier. The buffer can be bypassed by configuring the BOFFx bit in the DAC\_CR register.

| Table 88. Document revision history (continued) |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------------------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Date                                            | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 29-Jan-2015                                     | 4        | Updated cover page with ADC up to 17 channels.<br>Updated <i>Section 6.3.20: Comparator characteristics</i> modifying ts_sc<br>characteristics in <i>Table 76</i> and adding <i>Figure 37: Maximum VREFINT</i><br><i>scaler startup time from power down</i> .<br>Updated I <sub>DD</sub> data in <i>Table 42: HSE oscillator characteristics</i> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 17-Apr-2015                                     | 5        | Updated <i>Figure 1: STM32F302xB/STM32F302xC block diagram</i><br>changing 32 KB of SRAM by 40 KB of SRAM.<br>Updated <i>Section 7: Package information</i> : with new package information<br>structure adding 1 sub paragraph for each package.<br>Updated <i>Figure 41: LQFP100 – 14 x 14 mm, low-profile quad flat</i><br><i>package top view example</i> removing gate mark.<br>Added note for all package device markings: "the following figure gives<br>an example of topside marking orientation versus pin 1 identifier<br>location".<br>Updated <i>Table 82: LQFP64 – 10 x 10 mm, low-profile quad flat package</i><br><i>mechanical data</i> .<br>Updated <i>Table 7: STM32F302xB/STM32F302xC peripheral</i><br><i>interconnect matrix</i> removing TIM8 reference and updating note below<br>the table, replacing by a reference to RM0365.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 22-Feb-2016                                     | 6        | <ul> <li>Added WLCSP100:</li> <li>Updated cover page.</li> <li>Updated Table 2: STM32F302xx family device features and peripheral counts.</li> <li>Added Figure 7: STM32F302xB/STM32F302xC WLCSP100 pinout.</li> <li>Updated Table 13: STM32F302xB/STM32F302xC pin definitions.</li> <li>Updated Table 24: General operating conditions.</li> <li>Added Section 7.4: WLCSP100 - 0.4 mm pitch wafer level chip scale package information.</li> <li>Updated Table 86: Package thermal characteristics.</li> <li>Updated Table 87: Ordering information scheme.</li> <li>Updated Table 87: Ordering information scheme.</li> <li>Updated Figure 4, Figure 5, Figure 6, Table 13 and Table 22 removing all VDD and VSS indexes.</li> <li>Updated Table 68: ADC characteristics adding V<sub>REF</sub>- negative voltage reference.</li> <li>Updated Table 21: Voltage characteristics adding table note 4.</li> <li>Updated Table 23: LSE oscillator characteristics (fLSE = 32.768 kHz) LSEDRV[1:0] bits.</li> <li>Updated Table 28: Embedded internal reference voltage V<sub>REFINT</sub> internal reference voltage (min and typ values).</li> <li>Updated Table 51: ESD absolute maximum ratings ESD CDM at class 3 and 4 including WLCSP100 package information.</li> </ul> |

Table 88. Document revision history (continued)

#### IMPORTANT NOTICE – PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2016 STMicroelectronics – All rights reserved

DocID025186 Rev 7