Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 72MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB          |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                  |

| Number of I/O              | 52                                                                    |

| Program Memory Size        | 256KB (256K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 40K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                             |

| Data Converters            | A/D 16x12b; D/A 1x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 64-LQFP                                                               |

| Supplier Device Package    | 64-LQFP (10x10)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f302rct6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2 Description

The STM32F302xB/STM32F302xC family is based on the high-performance ARM<sup>®</sup> Cortex<sup>®</sup>-M4 32-bit RISC core with FPU operating at a frequency of up to 72 MHz, and embedding a floating point unit (FPU), a memory protection unit (MPU) and an embedded trace macrocell (ETM). The family incorporates high-speed embedded memories (up to 256 Kbytes of Flash memory, up to 40 Kbytes of SRAM) and an extensive range of enhanced I/Os and peripherals connected to two APB buses.

The devices offer up to two fast 12-bit ADCs (5 Msps), four comparators, two operational amplifiers, up to one DAC channel, a low-power RTC, up to five general-purpose 16-bit timers, one general-purpose 32-bit timer, and one timer dedicated to motor control. They also feature standard and advanced communication interfaces: up to two I<sup>2</sup>Cs, up to three SPIs (two SPIs are with multiplexed full-duplex I2Ss), three USARTs, up to two UARTs, CAN and USB. To achieve audio class accuracy, the I2S peripherals can be clocked via an external PLL.

The STM32F302xB/STM32F302xC family operates in the -40 to +85 °C and -40 to +105 °C temperature ranges from a 2.0 to 3.6 V power supply. A comprehensive set of power-saving mode allows the design of low-power applications.

The STM32F302xB/STM32F302xC family offers devices in four packages ranging from 48 pins to 100 pins.

The set of included peripherals changes with the device chosen.

# 3.4 Embedded SRAM

STM32F302xB/STM32F302xC devices feature up to 40 Kbytes of embedded SRAM with hardware parity check on first 16 Kbytes of SRAM. The memory can be accessed in read/write at CPU clock speed with 0 wait states.

# 3.5 Boot modes

At startup, Boot0 pin and Boot1 option bit are used to select one of three boot options:

- Boot from user Flash

- Boot from system memory

- Boot from embedded SRAM

The boot loader is located in the system memory. It is used to reprogram the Flash memory by using USART1 (PA9/PA10), USART2 (PD5/PD6) or USB (PA11/PA12) through DFU (device firmware upgrade).

# 3.6 Cyclic redundancy check (CRC)

The CRC (cyclic redundancy check) calculation unit is used to get a CRC code using a configurable generator polynomial value and size.

Among other applications, CRC-based techniques are used to verify data transmission or storage integrity. In the scope of the EN/IEC 60335-1 standard, they offer a means of verifying the Flash memory integrity. The CRC calculation unit helps compute a signature of the software during runtime, to be compared with a reference signature generated at linktime and stored at a given memory location.

| Interconnect source                             | Interconnect<br>destination | Interconnect action                                            |

|-------------------------------------------------|-----------------------------|----------------------------------------------------------------|

| GPIO<br>RTCCLK<br>HSE/32<br>MC0                 | TIM16                       | Clock source used as input channel for HSI and LSI calibration |

| CSS<br>CPU (hard fault)<br>COMPx<br>PVD<br>GPIO | TIM1,<br>TIM15, 16, 17      | Timer break                                                    |

|                                                 | TIMx                        | External trigger, timer break                                  |

| GPIO                                            | ADCx<br>DAC1                | Conversion external trigger                                    |

| DAC1                                            | COMPx                       | Comparator inverting input                                     |

#### Table 4. STM32F302xB/STM32F302xC peripheral interconnect matrix (continued)

*Note:* For more details about the interconnect actions, please refer to the corresponding sections in the reference manual (RM0365.

# 3.9 Clocks and startup

System clock selection is performed on startup, however the internal RC 8 MHz oscillator is selected as default CPU clock on reset. An external 4-32 MHz clock can be selected, in which case it is monitored for failure. If failure is detected, the system automatically switches back to the internal RC oscillator. A software interrupt is generated if enabled. Similarly, full interrupt management of the PLL clock entry is available when necessary (for example with failure of an indirectly used external oscillator).

Several prescalers allow to configure the AHB frequency, the high speed APB (APB2) and the low speed APB (APB1) domains. The maximum frequency of the AHB and the high speed APB domains is 72 MHz, while the maximum allowed frequency of the low speed APB domain is 36 MHz.

44/144

|                          | Table 14. Alternate functions for port A (continued) |                      |     |                |              |              |                      |                   |               |               |              |          |      |            |              |

|--------------------------|------------------------------------------------------|----------------------|-----|----------------|--------------|--------------|----------------------|-------------------|---------------|---------------|--------------|----------|------|------------|--------------|

| Port<br>&<br>Pin<br>Name | AF0                                                  | AF1                  | AF2 | AF3            | AF4          | AF5          | AF6                  | AF7               | AF8           | AF9           | AF10         | AF11     | AF12 | AF14       | AF15         |

| PA12                     | -                                                    | TIM16_<br>CH1        | -   | -              | -            | -            | TIM1_CH2N            | USART1_<br>RTS_DE | COMP2<br>_OUT | CAN_TX        | TIM4_<br>CH2 | TIM1_ETR | -    | USB_<br>DP | EVENT<br>OUT |

| PA13                     | SWDIO<br>-JTMS                                       | TIM16_<br>CH1N       | -   | TSC_<br>G4_IO3 | -            | IR_<br>OUT   | -                    | USART3_<br>CTS    | -             | -             | TIM4_<br>CH3 | -        | -    | -          | EVENT<br>OUT |

| PA14                     | SWCLK<br>-JTCK                                       | -                    | -   | TSC_<br>G4_IO4 | I2C1_<br>SDA |              | TIM1_BKIN            | USART2_<br>TX     | -             | -             | -            | -        | -    | -          | EVENT<br>OUT |

| PA15                     | JTDI                                                 | TIM2_<br>CH1_<br>ETR |     | -              | I2C1_<br>SCL | SPI1_<br>NSS | SPI3_NSS,<br>I2S3_WS | USART2_<br>RX     | -             | TIM1_<br>BKIN | -            | -        | -    | -          | EVENT<br>OUT |

STM32F302xB STM32F302xC

**AF10**

-

-

-

AF12

-

-

-

\_

-

\_

-

-

TIM1

BKIN

-

-

-

-

-

\_

-

AF15

**EVENT**

**EVENT**

**EVENT**

**EVENT**

EVENT

**EVENT**

**EVENT**

**EVENT**

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT EVENT

OUT

OUT

OUT

OUT

OUT

**EVENT**

**EVENT**

EVENT

**EVENT**

Pinouts and pin description

| 36  | - | CH1N           | CH1          | G5_IO3         |

|-----|---|----------------|--------------|----------------|

| 37  | - | TIM17_<br>CH1N | TIM4_<br>CH2 | TSC_<br>G5_IO4 |

| 38  | - | TIM16_<br>CH1  | TIM4_<br>CH3 | TSC_<br>SYNC   |

| 39  | - | TIM17_<br>CH1  | TIM4_<br>CH4 |                |

| 810 | - | TIM2_<br>CH3   | -            | TSC_<br>SYNC   |

| 811 | - | TIM2_<br>CH4   | -            | TSC_<br>G6_IO1 |

| 812 | _ | -              | -            | TSC_<br>G6_IO2 |

DocID025186 Rev 7

# 45/144

Port & AF0 AF1 AF2 AF3 AF4 AF5 AF6 AF7 AF8 AF9 Pin Name TSC\_ TIM3 PB0 TIM1 CH2N \_ --\_ --G3 102 CH3 TIM3 TSC COMP4 TIM1\_CH3N PB1 ---\_ \_ G3 103 OUT CH4 TSC\_ PB2 ---------G3 104 JTDO-SPI1\_ SPI3 SCK, USART2 TIM2 TIM4\_ TSC\_ TIM3 TRACES PB3 \_ -CH2 G5 101 ETR SCK 12S3 CK ETR ТΧ WO TIM16 TIM3 TSC SPI1\_ SPI3 MISO, USART2\_ TIM17 NJTRST PB4 -\_ G5 102 MISO I2S3ext SD CH1 CH1 RX BKIN I2C1\_ SPI1\_ SPI3 MOSI, TIM16 TIM3 USART2 TIM17\_ PB5 ---SMBA MOSI I2S3\_SD CH2 CK CH1 BKIN TIM16 USART1 TIM4 TSC PB6 I2C1 SCL \_ -ТΧ I2C1\_ USART1 TIM3 PB --\_ SDA CH4 RX COMP1\_ CAN\_RX I2C1 SCL PB --OUT I2C1\_ COMP2\_ IR OUT CAN TX PB -SDA OUT USART3\_ PB \_ --\_ -ТΧ USART3\_ PΒ ----\_ RX 12C2 SPI2 NSS, TIM1 USART3 PB \_ -

12S2 WS

BKIN

CK

SMBA

Table 15. Alternate functions for port B

# 6.1.6 Power supply scheme

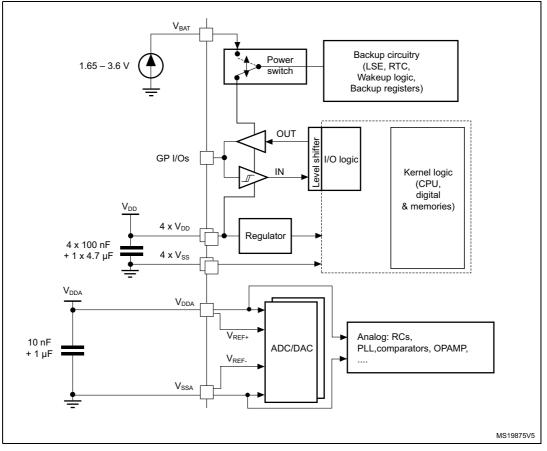

Figure 11. Power supply scheme

1. Dotted lines represent the internal connections on low pin count packages, joining the dedicated supply pins.

**Caution:** Each power supply pair (V<sub>DD</sub>/V<sub>SS</sub>, V<sub>DDA</sub>/V<sub>SSA</sub> etc..) must be decoupled with filtering ceramic capacitors as shown above. These capacitors must be placed as close as possible to, or below the appropriate pins on the underside of the PCB to ensure the good functionality of the device.

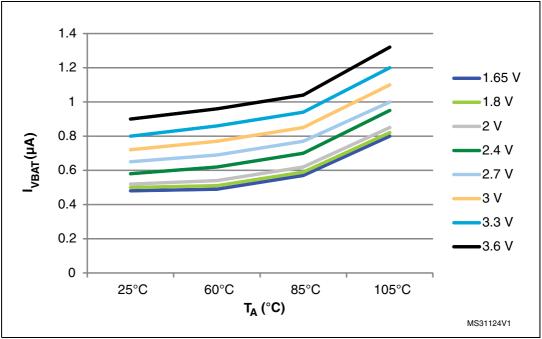

| Symbol   | Para              | (4)                                                                                           |       |      |      |      | Max<br>@V <sub>BAT</sub> = 3.6 V <sup>(2)</sup> |      |      | Unit |                          |                          |                           |      |

|----------|-------------------|-----------------------------------------------------------------------------------------------|-------|------|------|------|-------------------------------------------------|------|------|------|--------------------------|--------------------------|---------------------------|------|

| Symbol   | meter             | (1)                                                                                           | 1.65V | 1.8V | 2V   | 2.4V | 2.7V                                            | 3V   | 3.3V | 3.6V | T <sub>A</sub> =<br>25°C | T <sub>A</sub> =<br>85°C | T <sub>A</sub> =<br>105°C | Unit |

|          | Backup<br>domain  | LSE & RTC<br>ON; "Xtal<br>mode"<br>lower<br>driving<br>capability;<br>LSEDRV[1:<br>0] = '00'  | 0.48  | 0.50 | 0.52 | 0.58 | 0.65                                            | 0.72 | 0.80 | 0.90 | 1.1                      | 1.5                      | 2.0                       |      |

| IDD_VBAT | supply<br>current | LSE & RTC<br>ON; "Xtal<br>mode"<br>higher<br>driving<br>capability;<br>LSEDRV[1:<br>0] = '11' | 0.83  | 0.86 | 0.90 | 0.98 | 1.03                                            | 1.10 | 1.20 | 1.30 | 1.5                      | 2.2                      | 2.9                       | μA   |

Table 34. Typical and maximum current consumption from  $V_{\text{BAT}}$  supply

1. Crystal used: Abracon ABS07-120-32.768 kHz-T with a CL of 6 pF for typical values.

2. Guaranteed by characterization results.

Figure 13. Typical V<sub>BAT</sub> current consumption (LSE and RTC ON/LSEDRV[1:0] = '00')

#### Typical current consumption

The MCU is placed under the following conditions:

- V<sub>DD</sub> = V<sub>DDA</sub> = 3.3 V

- All I/O pins available on each package are in analog input configuration

- The Flash access time is adjusted to f<sub>HCLK</sub> frequency (0 wait states from 0 to 24 MHz, 1 wait state from 24 to 48 MHz and 2 wait states from 48 MHz to 72 MHz), and Flash prefetch is ON

- When the peripherals are enabled,  $f_{APB1} = f_{AHB/2}$ ,  $f_{APB2} = f_{AHB}$

- PLL is used for frequencies greater than 8 MHz

- AHB prescaler of 2, 4, 8,16 and 64 is used for the frequencies 4 MHz, 2 MHz, 1 MHz, 500 kHz and 125 kHz respectively.

#### Table 35. Typical current consumption in Run mode, code with data processing running from Flash

|                                     |                                 |                             |         | Т                      | ур                      |        |       |     |     |

|-------------------------------------|---------------------------------|-----------------------------|---------|------------------------|-------------------------|--------|-------|-----|-----|

| Symbol                              | Parameter                       | Conditions f <sub>HCL</sub> |         | Peripherals<br>enabled | Peripherals<br>disabled | Unit   |       |     |     |

|                                     |                                 |                             | 72 MHz  | 61.3                   | 28.0                    |        |       |     |     |

|                                     |                                 |                             | 64 MHz  | 54.8                   | 25.4                    |        |       |     |     |

|                                     |                                 |                             | 48 MHz  | 41.9                   | 19.3                    |        |       |     |     |

|                                     |                                 |                             | 32 MHz  | 28.5                   | 13.3                    |        |       |     |     |

|                                     |                                 |                             | 24 MHz  | 21.8                   | 10.4                    |        |       |     |     |

|                                     | Supply current in Run mode from |                             | 16 MHz  | 14.9                   | 7.2                     | mA     |       |     |     |

| I <sub>DD</sub>                     | V <sub>DD</sub> supply          |                             | 8 MHz   | 7.7                    | 3.9                     | - IIIA |       |     |     |

|                                     |                                 |                             | 4 MHz   | 4.5                    | 2.5                     |        |       |     |     |

|                                     |                                 | Running from HSE            | 2 MHz   | 2.8                    | 1.7                     |        |       |     |     |

|                                     |                                 |                             |         |                        |                         | 1 MHz  | 1 MHz | 1.9 | 1.3 |

|                                     |                                 |                             | 500 kHz | 1.4                    | 1.1                     |        |       |     |     |

|                                     |                                 | crystal clock 8 MHz,        | 125 kHz | 1.1                    | 0.9                     |        |       |     |     |

|                                     |                                 | code executing from         | 72 MHz  | 240.3                  | 239.5                   |        |       |     |     |

|                                     |                                 | Flash                       | 64 MHz  | 210.9                  | 210.3                   |        |       |     |     |

|                                     |                                 |                             | 48 MHz  | 155.8                  | 155.6                   |        |       |     |     |

|                                     |                                 |                             | 32 MHz  | 105.7                  | 105.6                   |        |       |     |     |

|                                     |                                 |                             | 24 MHz  | MHz 82.1               | 82.0                    |        |       |     |     |

| I <sub>DDA</sub> <sup>(1) (2)</sup> | Supply current in Run mode from |                             | 16 MHz  | 58.8                   | 58.8                    | μA     |       |     |     |

| 'DDA`´``                            | V <sub>DDA</sub> supply         |                             | 8 MHz   | 2.4                    | 2.4                     | μΑ     |       |     |     |

|                                     | DDA                             |                             | 4 MHz   | 2.4                    | 2.4                     | 1      |       |     |     |

|                                     |                                 |                             | 2 MHz   | 2.4                    | 2.4                     | 1      |       |     |     |

|                                     |                                 |                             | 1 MHz   | 2.4                    | 2.4                     | -      |       |     |     |

|                                     |                                 |                             | 500 kHz | 2.4                    | 2.4                     | 1      |       |     |     |

|                                     |                                 |                             | 125 kHz | 2.4                    | 2.4                     | ]      |       |     |     |

1. V<sub>DDA</sub> monitoring is ON.

2. When peripherals are enabled, the power consumption of the analog part of peripherals such as ADC, DAC, Comparators, OpAmp etc. is not included. Refer to the tables of characteristics in the subsequent sections.

## On-chip peripheral current consumption

The MCU is placed under the following conditions:

- all I/O pins are in analog input configuration

- all peripherals are disabled unless otherwise mentioned

- the given value is calculated by measuring the current consumption

- with all peripherals clocked off

- with only one peripheral clocked on

- ambient operating temperature at 25°C and  $V_{DD} = V_{DDA} = 3.3$  V.

#### Table 38. Peripheral current consumption

| Derinherol                 | Typical consumption <sup>(1)</sup> | Unit   |

|----------------------------|------------------------------------|--------|

| Peripheral                 | I <sub>DD</sub>                    | Onit   |

| BusMatrix <sup>(2)</sup>   | 12.6                               |        |

| DMA1                       | 7.6                                |        |

| DMA2                       | 6.1                                |        |

| CRC                        | 2.1                                |        |

| GPIOA                      | 10.0                               |        |

| GPIOB                      | 10.3                               |        |

| GPIOC                      | 2.2                                |        |

| GPIOD                      | 8.8                                |        |

| GPIOE                      | 3.3                                |        |

| GPIOF                      | 3.0                                |        |

| TSC                        | 5.5                                |        |

| ADC1&2                     | 17.3                               |        |

| APB2-Bridge <sup>(3)</sup> | 3.6                                |        |

| SYSCFG                     | 7.3                                | μA/MHz |

| TIM1                       | 40.0                               |        |

| SPI1                       | 8.8                                |        |

| USART1                     | 23.3                               |        |

| TIM15                      | 17.1                               |        |

| TIM16                      | 10.1                               |        |

| TIM17                      | 11.0                               |        |

| APB1-Bridge <sup>(3)</sup> | 6.1                                |        |

| TIM2                       | 49.1                               |        |

| TIM3                       | 38.8                               |        |

| TIM4                       | 38.3                               |        |

# 6.3.11 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

## Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- FTB: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 49*. They are based on the EMS levels and classes defined in the application note AN1709.

|   | Symbol            | Parameter                                                                                                                         | Conditions                                                                                                    | Level/<br>Class |

|---|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-----------------|

| ſ | V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                    | $V_{DD}$ = 3.3 V, LQFP100, T <sub>A</sub> = +25°C,<br>f <sub>HCLK</sub> = 72 MHz<br>conforms to IEC 61000-4-2 | 3B              |

|   | V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | $V_{DD}$ = 3.3 V, LQFP100, T <sub>A</sub> = +25°C,<br>f <sub>HCLK</sub> = 72 MHz<br>conforms to IEC 61000-4-4 | 4A              |

#### Table 49. EMS characteristics

#### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

#### Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical Data corruption (control registers...)

#### **Prequalification trials**

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the Oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

#### **Electromagnetic Interference (EMI)**

The electromagnetic field emitted by the device are monitored while a simple application is executed (toggling 2 LEDs through the I/O ports). This emission test is compliant with IEC 61967-2 standard which specifies the test board and the pin loading.

| Symbol           | Parameter  | Conditions                                        | Monitored               | Max vs. [f <sub>HSE</sub> /f <sub>HCLK</sub> ] | Unit |

|------------------|------------|---------------------------------------------------|-------------------------|------------------------------------------------|------|

| Symbol           | Farameter  | contaitions                                       | frequency band 8/72 MHz |                                                | Unit |

|                  |            |                                                   | 0.1 to 30 MHz           | 7                                              |      |

| 6                | Peak level | $V_{DD} = 3.6 V, T_A = 25 °C,$<br>LQFP100 package | 30 to 130 MHz           | 20                                             | dBµV |

| S <sub>EMI</sub> | Peak level |                                                   | 130 MHz to 1GHz         | 27                                             |      |

|                  |            | 01307-2                                           | SAE EMI Level           | 4                                              | -    |

Table 50. EMI characteristics

# 6.3.12 Electrical sensitivity characteristics

Based on three different tests (ESD, LU) using specific measurement methods, the device is stressed in order to determine its performance in terms of electrical sensitivity.

#### Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts  $\times$  (n+1) supply pins). This test conforms to the JESD22-A114, ANSI/ESD STM5.3.1 standard.

| Symbol                | Ratings                                                  | Conditions                                                  |                                | Class | Maximum<br>value <sup>(1)</sup> | Unit |

|-----------------------|----------------------------------------------------------|-------------------------------------------------------------|--------------------------------|-------|---------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic<br>discharge voltage<br>(human body model) | $T_A = +25 \ ^{\circ}C$ , conforming to JESD22-A114         |                                | 2     | 2000                            |      |

|                       | Electrostatic                                            |                                                             | WLCSP100<br>package            | 3     | 250                             | V    |

| V <sub>ESD(CDM)</sub> | discharge voltage<br>(charge device model)               | T <sub>A</sub> = +25 °C, conforming<br>to ANSI/ESD STM5.3.1 | Packages<br>except<br>WLCSP100 | 4     | 500                             |      |

Table 51. ESD absolute maximum ratings

1. Guaranteed by characterization results.

#### Static latch-up

Two complementary static tests are required on six parts to assess the latch-up performance:

- A supply overvoltage is applied to each power supply pin

- A current injection is applied to each input, output and configurable I/O pin

These tests are compliant with EIA/JESD 78A IC latch-up standard.

| Symbol | Parameter             | Conditions                            | Class      |

|--------|-----------------------|---------------------------------------|------------|

| LU     | Static latch-up class | $T_A = +105$ °C conforming to JESD78A | II level A |

# 6.3.13 I/O current injection characteristics

As a general rule, current injection to the I/O pins, due to external voltage below  $V_{SS}$  or above  $V_{DD}$  (for standard, 3 V-capable I/O pins) should be avoided during normal product operation. However, in order to give an indication of the robustness of the microcontroller in cases when abnormal injection accidentally happens, susceptibility tests are performed on a sample basis during device characterization.

#### Functional susceptibility to I/O current injection

While a simple application is executed on the device, the device is stressed by injecting current into the I/O pins programmed in floating input mode. While current is injected into the I/O pin, one at a time, the device is checked for functional failures.

The failure is indicated by an out of range parameter: ADC error above a certain limit (higher than 5 LSB TUE), out of conventional limits of induced leakage current on adjacent pins (out of  $-5 \mu$ A/+0  $\mu$ A range), or other functional failure (for example reset occurrence or oscillator frequency deviation).

The test results are given in Table 53.

|                  |                                                                                                                                                                                                                                                                                                                                | Functional s       | usceptibility      |      |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------|------|

| Symbol           | Description                                                                                                                                                                                                                                                                                                                    | Negative injection | Positive injection | Unit |

|                  | Injected current on BOOT0                                                                                                                                                                                                                                                                                                      | - 0                | NA                 |      |

|                  | Injected current on PC0, PC1, PC2, PC3, PF2, PA0, PA1, PA2, PA3, PF4, PA4, PA5, PA6, PA7, PC4, PC5, PB2 with induced leakage current on other pins from this group less than -50 $\mu$ A                                                                                                                                       | - 5                | -                  |      |

| I <sub>INJ</sub> | Injected current on PB0, PB1, PE7, PE8, PE9, PE10, PE11, PE12, PE13, PE14, PE15, PB12, PB13, PB14, PB15, PD8, PD9, PD10, PD11, PD12, PD13, PD14 with induced leakage current on other pins from this group less than -50 µA                                                                                                    | - 5                | -                  | mA   |

|                  | jected current on PC0, PC1, PC2, PC3, PF2, PA0,<br>A1, PA2, PA3, PF4, PA4, PA5, PA6, PA7, PC4, PC5,<br>B2, PB0, PB1, PE7, PE8, PE9, PE10, PE11, PE12,<br>E13, PE14, PE15, PB12, PB13, PB14, PB15, PD8, - ++<br>D9, PD10, PD11, PD12, PD13, PD14 with induced<br>akage current on other pins from this group less than<br>D0 μA |                    | +5                 |      |

|                  | Injected current on any other FT and FTf pins                                                                                                                                                                                                                                                                                  | - 5                | NA                 |      |

|                  | Injected current on any other pins                                                                                                                                                                                                                                                                                             | - 5                | +5                 |      |

*Note:* It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative currents.

#### **Output driving current**

The GPIOs (general purpose input/outputs) can sink or source up to +/-8 mA, and sink or source up to +/- 20 mA (with a relaxed  $V_{OL}/V_{OH}$ ).

In the user application, the number of I/O pins which can drive current must be limited to respect the absolute maximum rating specified in *Section 6.2*:

- The sum of the currents sourced by all the I/Os on V<sub>DD</sub>, plus the maximum Run consumption of the MCU sourced on V<sub>DD</sub>, cannot exceed the absolute maximum rating ΣI<sub>VDD</sub> (see *Table 22*).

- The sum of the currents sunk by all the I/Os on V<sub>SS</sub> plus the maximum Run consumption of the MCU sunk on V<sub>SS</sub> cannot exceed the absolute maximum rating ΣI<sub>VSS</sub> (see *Table 22*).

## **Output voltage levels**

Unless otherwise specified, the parameters given in *Table 55* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 24*. All I/Os (FT, TTa and TC unless otherwise specified) are CMOS and TTL compliant.

| Symbol                               | Parameter                                               | Conditions                                                  | Min                  | Max | Unit |

|--------------------------------------|---------------------------------------------------------|-------------------------------------------------------------|----------------------|-----|------|

| V <sub>OL</sub> <sup>(1)</sup>       | Output low level voltage for an I/O pin                 | CMOS port <sup>(2)</sup>                                    | -                    | 0.4 |      |

| V <sub>OH</sub> <sup>(3)</sup>       | Output high level voltage for an I/O pin                | I <sub>IO</sub> = +8 mA<br>2.7 V < V <sub>DD</sub> < 3.6 V  | V <sub>DD</sub> -0.4 | -   |      |

| V <sub>OL</sub> <sup>(1)</sup>       | Output low level voltage for an I/O pin                 | TTL port <sup>(2)</sup>                                     | -                    | 0.4 |      |

| V <sub>OH</sub> <sup>(3)</sup>       | Output high level voltage for an I/O pin                | I <sub>IO</sub> = +8 mA<br>2.7 V < V <sub>DD</sub> < 3.6 V  | 2.4                  | -   |      |

| V <sub>OL</sub> <sup>(1)(4)</sup>    | Output low level voltage for an I/O pin                 | I <sub>IO</sub> = +20 mA                                    | -                    | 1.3 | V    |

| V <sub>OH</sub> <sup>(3)(4)</sup>    | Output high level voltage for an I/O pin                | 2.7 V < V <sub>DD</sub> < 3.6 V                             | V <sub>DD</sub> -1.3 | -   |      |

| V <sub>OL</sub> <sup>(1)(4)</sup>    | Output low level voltage for an I/O pin                 | I <sub>IO</sub> = +6 mA                                     | -                    | 0.4 |      |

| V <sub>OH</sub> <sup>(3)(4)</sup>    | Output high level voltage for an I/O pin                | 2 V < V <sub>DD</sub> < 2.7 V                               | V <sub>DD</sub> -0.4 | -   |      |

| V <sub>OLFM+</sub> <sup>(1)(4)</sup> | Output low level voltage for an FTf I/O pin in FM+ mode | I <sub>IO</sub> = +20 mA<br>2.7 V < V <sub>DD</sub> < 3.6 V | -                    | 0.4 |      |

| Table 55. | Output voltage  | characteristics |

|-----------|-----------------|-----------------|

|           | o alpat follago |                 |

1. The I<sub>IO</sub> current sunk by the device must always respect the absolute maximum rating specified in *Table 22* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed  $\Sigma I_{IO(PIN)}$ .

2. TTL and CMOS outputs are compatible with JEDEC standards JESD36 and JESD52.

3. The I<sub>IO</sub> current sourced by the device must always respect the absolute maximum rating specified in *Table 22* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed  $\Sigma I_{IO(PIN)}$ .

4. Data based on design simulation.

| Table 59. IWDG min/max timeout period at 40 kHz (LSI) (*) |              |                                     |                                     |  |  |  |  |

|-----------------------------------------------------------|--------------|-------------------------------------|-------------------------------------|--|--|--|--|

| Prescaler divider                                         | PR[2:0] bits | Min timeout (ms) RL[11:0]=<br>0x000 | Max timeout (ms) RL[11:0]=<br>0xFFF |  |  |  |  |

| /4                                                        | 0            | 0.1                                 | 409.6                               |  |  |  |  |

| /8                                                        | 1            | 0.2                                 | 819.2                               |  |  |  |  |

| /16                                                       | 2            | 0.4                                 | 1638.4                              |  |  |  |  |

| /32                                                       | 3            | 0.8                                 | 3276.8                              |  |  |  |  |

| /64                                                       | 4            | 1.6                                 | 6553.6                              |  |  |  |  |

| /128                                                      | 5            | 3.2                                 | 13107.2                             |  |  |  |  |

| /256                                                      | 7            | 6.4                                 | 26214.4                             |  |  |  |  |

Table 59. IWDG min/max timeout period at 40 kHz (LSI) <sup>(1)</sup>

1. These timings are given for a 40 kHz clock but the microcontroller's internal RC frequency can vary from 30 to 60 kHz. Moreover, given an exact RC oscillator frequency, the exact timings still depend on the phasing of the APB interface clock versus the LSI clock so that there is always a full RC period of uncertainty.

| Table 60. WWDG min-max timeout value | e @72 MHz (PCLK) <sup>(1)</sup> |

|--------------------------------------|---------------------------------|

|--------------------------------------|---------------------------------|

| Prescaler | WDGTB | Min timeout value | Max timeout value |

|-----------|-------|-------------------|-------------------|

| 1         | 0     | 0.05687           | 3.6409            |

| 2         | 1     | 0.1137            | 7.2817            |

| 4         | 2     | 0.2275            | 14.564            |

| 8         | 3     | 0.4551            | 29.127            |

1. Guaranteed by design.

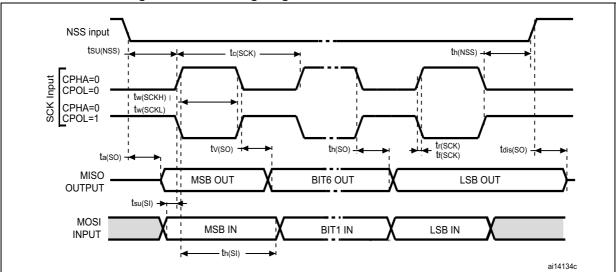

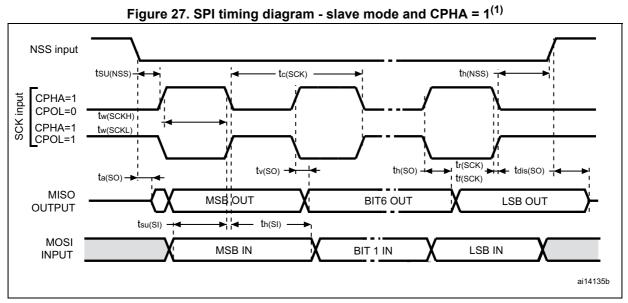

Figure 26. SPI timing diagram - slave mode and CPHA = 0

1. Measurement points are done at  $0.5V_{DD}$  and with external C<sub>L</sub> = 30 pF.

| Symbol                                    | Parameter                       | Conditions                     | Min | Тур | Max | Unit |  |  |

|-------------------------------------------|---------------------------------|--------------------------------|-----|-----|-----|------|--|--|

| Driver characteristics                    |                                 |                                |     |     |     |      |  |  |

| t <sub>r</sub>                            | Rise time <sup>(2)</sup>        | C <sub>L</sub> = 50 pF         | 4   | -   | 20  | ns   |  |  |

| t <sub>f</sub>                            | Fall time <sup>(2)</sup>        | C <sub>L</sub> = 50 pF         | 4   | -   | 20  | ns   |  |  |

| t <sub>rfm</sub>                          | Rise/ fall time matching        | t <sub>r</sub> /t <sub>f</sub> | 90  | -   | 110 | %    |  |  |

| V <sub>CRS</sub>                          | Output signal crossover voltage | -                              | 1.3 | -   | 2.0 | V    |  |  |

| Output driver<br>Impedance <sup>(3)</sup> | Z <sub>DRV</sub>                | driving high and low           | 28  | 40  | 44  | Ω    |  |  |

Table 67. USB: Full-speed electrical characteristics<sup>(1)</sup>

1. Guaranteed by design.

Measured from 10% to 90% of the data signal. For more detailed informations, please refer to USB Specification - Chapter 7 (version 2.0).

3. No external termination series resistors are required on USB\_DP (D+) and USB\_DM (D-), the matching impedance is already included in the embedded driver.

#### CAN (controller area network) interface

Refer to Section 6.3.14: I/O port characteristics for more details on the input/output alternate function characteristics (CAN\_TX and CAN\_RX).

| Symbol             | Parameter                 | С                                                                                                                      | Min <sup>(4)</sup> | Max <sup>(4)</sup>  | Unit |     |    |

|--------------------|---------------------------|------------------------------------------------------------------------------------------------------------------------|--------------------|---------------------|------|-----|----|

|                    | Oissa al ta               |                                                                                                                        | Single             | Fast channel 5.1 Ms | 64   | -   |    |

| SINAD              | Signal-to-<br>noise and   | •                                                                                                                      | Ended              | Slow channel 4.8 Ms | 63   | -   |    |

| (5)                | distortion<br>ratio       |                                                                                                                        | Differential       | Fast channel 5.1 Ms | 67   | -   |    |

|                    | Tallo                     |                                                                                                                        | Dillerential       | Slow channel 4.8 Ms | 67   | -   |    |

| SNR <sup>(5)</sup> | Signal-to-<br>noise ratio | ADC clock freq. $\leq$ 72 MHz,                                                                                         | Single<br>Ended    | Fast channel 5.1 Ms | 64   | -   |    |

|                    |                           | Signal-to-<br>noise ratioSampling freq. $\leq$ 5 Msps,<br>2 V $\leq$ V <sub>DDA</sub> , V <sub>REF+</sub> $\leq$ 3.6 V |                    | Slow channel 4.8 Ms | 64   | -   | dB |

| SINKY              |                           |                                                                                                                        | Differential       | Fast channel 5.1 Ms | 67   | -   | uБ |

|                    |                           | 100-pin package                                                                                                        | Dillerential       | Slow channel 4.8 Ms | 67   | -   |    |

|                    |                           | Total                                                                                                                  | Single             | Fast channel 5.1 Ms | -    | -74 |    |

| THD <sup>(5)</sup> |                           |                                                                                                                        | Ended              | Slow channel 4.8 Ms | -    | -74 |    |

|                    | harmonic<br>distortion    |                                                                                                                        | Differential       | Fast channel 5.1 Ms | -    | -78 |    |

|                    |                           |                                                                                                                        | Differential       | Slow channel 4.8 Ms | -    | -76 |    |

# Table 71. ADC accuracy, 100-pin packages<sup>(1)(2)(3)</sup> (continued)

1. ADC DC accuracy values are measured after internal calibration.

ADC accuracy vs. negative Injection Current: Injecting negative current on any analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative current. Any positive injection current within the limits specified for I<sub>INJ(PIN)</sub> and ΣI<sub>INJ(PIN)</sub> in Section 6.3.14 does not affect the ADC accuracy.

3. Better performance may be achieved in restricted  $V_{\text{DDA}}$ , frequency and temperature ranges.

4. Guaranteed by characterization results.

5. Value measured with a -0.5 dB full scale 50 kHz sine wave input signal.

# 7.5 Thermal characteristics

The maximum chip junction temperature (T<sub>J</sub>max) must never exceed the values given in *Table 24: General operating conditions on page 58*.

The maximum chip-junction temperature,  $T_{\rm J}$  max, in degrees Celsius, may be calculated using the following equation:

$$T_J max = T_A max + (P_D max x \Theta_{JA})$$

Where:

- T<sub>A</sub> max is the maximum ambient temperature in °C,

- $\Theta_{IA}$  is the package junction-to-ambient thermal resistance, in ° C/W,

- P<sub>D</sub> max is the sum of P<sub>INT</sub> max and P<sub>I/O</sub> max (P<sub>D</sub> max = P<sub>INT</sub> max + P<sub>I/O</sub>max),

- P<sub>INT</sub> max is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the maximum chip internal power.

$P_{I/O}$  max represents the maximum power dissipation on output pins where:

$\mathsf{P}_{\mathsf{I}/\mathsf{O}} \max = \Sigma \; (\mathsf{V}_{\mathsf{OL}} \times \mathsf{I}_{\mathsf{OL}}) + \Sigma ((\mathsf{V}_{\mathsf{DD}} - \mathsf{V}_{\mathsf{OH}}) \times \mathsf{I}_{\mathsf{OH}}),$

taking into account the actual V<sub>OL</sub> / I<sub>OL</sub> and V<sub>OH</sub> / I<sub>OH</sub> of the I/Os at low and high level in the application.

| Symbol          | Parameter                                                                  | Value | Unit |

|-----------------|----------------------------------------------------------------------------|-------|------|

|                 | Thermal resistance junction-ambient<br>LQFP64 - 10 × 10 mm / 0.5 mm pitch  | 45    |      |

| 0               | Thermal resistance junction-ambient<br>LQFP48 - 7 × 7 mm                   | 55    | °C/W |

| Θ <sub>JA</sub> | Thermal resistance junction-ambient<br>LQFP100 - 14 × 14 mm / 0.5 mm pitch | 41    | C/W  |

|                 | Thermal resistance junction-ambient<br>WLCSP100 - 0.4 mm pitch             | 40    |      |

#### Table 86. Package thermal characteristics

# 7.5.1 Reference document

JESD51-2 Integrated Circuits Thermal Test Method Environment Conditions - Natural Convection (Still Air). Available from www.jedec.org

# 8 Ordering information

| Example:                                        | STM32 | F | 302 | R | В | Т | 6 | xxx |

|-------------------------------------------------|-------|---|-----|---|---|---|---|-----|

| Device family                                   |       |   |     |   |   |   |   |     |

| STM32 = ARM-based 32-bit microcontroller        |       |   |     |   |   |   |   |     |

| Product type                                    |       |   |     |   |   |   |   |     |

| F = general-purpose                             |       |   |     |   |   |   |   |     |

| Device subfamily                                |       |   |     |   |   |   |   |     |

| 302 = STM32F302xx                               |       |   |     |   |   |   |   |     |

| Pin count                                       |       |   |     |   |   |   |   |     |

| C = 48 pins                                     |       |   |     |   |   |   |   |     |

| R = 64 pins                                     |       |   |     |   |   |   |   |     |

| V = 100 pins                                    |       |   |     |   |   |   |   |     |

| Flash memory size                               |       |   |     |   |   |   |   |     |

| B = 128 Kbytes of Flash memory                  |       |   |     |   |   |   |   |     |

| C = 256 Kbytes of Flash memory                  |       |   |     |   |   |   |   |     |

| Package                                         |       |   |     |   |   |   |   |     |

| T = LQFP                                        |       |   |     |   |   |   |   |     |

| Y = WLCSP                                       |       |   |     |   |   |   |   |     |

|                                                 |       |   |     |   |   |   |   |     |

| Temperature range                               |       |   |     |   |   |   |   |     |

| 6 = Industrial temperature range, -40 to 85 °C  |       |   |     |   |   |   |   |     |

| 7 = Industrial temperature range, -40 to 105 °C |       |   |     |   |   |   |   |     |

| Options                                         |       |   |     |   |   |   |   |     |

## Table 87. Ordering information scheme

xxx = programmed parts TR = tape and reel

For a list of available options (speed, package, etc.) or for further information on any aspect of this device, please contact your nearest ST sales office.