Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                       |  |

|----------------------------|-----------------------------------------------------------------------|--|

| Product Status             | Active                                                                |  |

| Core Processor             | ARM® Cortex®-M4                                                       |  |

| Core Size                  | 32-Bit Single-Core                                                    |  |

| Speed                      | 72MHz                                                                 |  |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB          |  |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                  |  |

| Number of I/O              | 87                                                                    |  |

| Program Memory Size        | 256KB (256K x 8)                                                      |  |

| Program Memory Type        | FLASH                                                                 |  |

| EEPROM Size                | -                                                                     |  |

| RAM Size                   | 40K x 8                                                               |  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                             |  |

| Data Converters            | A/D 17x12b; D/A 1x12b                                                 |  |

| Oscillator Type            | Internal                                                              |  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                    |  |

| Mounting Type              | Surface Mount                                                         |  |

| Package / Case             | 100-LQFP                                                              |  |

| Supplier Device Package    | 100-LQFP (14x14)                                                      |  |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f302vct7 |  |

|               |                      | 3.17.2                                                                                                            | General-purpose timers (TIM2, TIM3, TIM4, TIM15, TIM16, TIM17)                                                                                                                                                                                                                                                               | . 23                                                                      |

|---------------|----------------------|-------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

|               |                      | 3.17.3                                                                                                            | Basic timer (TIM6)                                                                                                                                                                                                                                                                                                           | 23                                                                        |

|               |                      | 3.17.4                                                                                                            | Independent watchdog (IWDG)                                                                                                                                                                                                                                                                                                  |                                                                           |

|               |                      | 3.17.5                                                                                                            | Window watchdog (WWDG)                                                                                                                                                                                                                                                                                                       |                                                                           |

|               |                      | 3.17.6                                                                                                            | SysTick timer                                                                                                                                                                                                                                                                                                                | 24                                                                        |

|               | 3.18                 | Real-tir                                                                                                          | me clock (RTC) and backup registers                                                                                                                                                                                                                                                                                          | . 24                                                                      |

|               | 3.19                 | Inter-in                                                                                                          | tegrated circuit interface (I <sup>2</sup> C)                                                                                                                                                                                                                                                                                | . 25                                                                      |

|               | 3.20                 | Univers                                                                                                           | sal synchronous/asynchronous receiver transmitter (USART)                                                                                                                                                                                                                                                                    | . 26                                                                      |

|               | 3.21                 | Univers                                                                                                           | sal asynchronous receiver transmitter (UART)                                                                                                                                                                                                                                                                                 | . 26                                                                      |

|               | 3.22                 | Serial p                                                                                                          | peripheral interface (SPI)/Inter-integrated sound interfaces (I2S)                                                                                                                                                                                                                                                           | . 27                                                                      |

|               | 3.23                 | Control                                                                                                           | ller area network (CAN)                                                                                                                                                                                                                                                                                                      | . 27                                                                      |

|               | 3.24                 | Univers                                                                                                           | sal serial bus (USB)                                                                                                                                                                                                                                                                                                         | . 27                                                                      |

|               | 3.25                 | Infrared                                                                                                          | d Transmitter                                                                                                                                                                                                                                                                                                                | . 28                                                                      |

|               | 3.26                 | Touch s                                                                                                           | sensing controller (TSC)                                                                                                                                                                                                                                                                                                     | . 28                                                                      |

|               | 3.27                 | Develo                                                                                                            | pment support                                                                                                                                                                                                                                                                                                                | . 30                                                                      |

|               |                      | 0.07.4                                                                                                            |                                                                                                                                                                                                                                                                                                                              | 30                                                                        |

|               |                      | 3.27.1                                                                                                            | Serial wire JTAG debug port (SWJ-DP)                                                                                                                                                                                                                                                                                         |                                                                           |

|               |                      | 3.27.1<br>3.27.2                                                                                                  | Serial wire JTAG debug port (SWJ-DP)                                                                                                                                                                                                                                                                                         | 30                                                                        |

| 4             | Dimo                 | 3.27.2                                                                                                            | Embedded trace macrocell™                                                                                                                                                                                                                                                                                                    |                                                                           |

| 4             | Pino                 | 3.27.2                                                                                                            |                                                                                                                                                                                                                                                                                                                              |                                                                           |

| <b>4</b><br>5 |                      | 3.27.2<br>uts and                                                                                                 | Embedded trace macrocell™                                                                                                                                                                                                                                                                                                    | . 31                                                                      |

| 5             | Mem                  | 3.27.2<br>uts and<br>ory map                                                                                      | Embedded trace macrocell™  pin description  pping                                                                                                                                                                                                                                                                            | . 31<br>. 51                                                              |

|               | Mem                  | 3.27.2  uts and  ory mar                                                                                          | Embedded trace macrocell™  pin description  pping  paracteristics                                                                                                                                                                                                                                                            | . 31<br>. 51<br>. 54                                                      |

| 5             | Mem                  | 3.27.2  uts and  ory mar                                                                                          | pin description                                                                                                                                                                                                                                                                                                              | . <b>31</b><br>. <b>51</b><br>. <b>54</b>                                 |

| 5             | Mem<br>Elect         | 3.27.2  uts and  ory mar                                                                                          | Embedded trace macrocell™  pin description  pping  paracteristics                                                                                                                                                                                                                                                            | . <b>31</b><br>. <b>51</b><br>. <b>54</b>                                 |

| 5             | Mem<br>Elect         | 3.27.2  uts and  ory map  trical ch  Parame 6.1.1 6.1.2                                                           | pin description  ping  aracteristics  eter conditions  Minimum and maximum values  Typical values                                                                                                                                                                                                                            | . <b>31</b> . <b>51</b> . <b>54</b> . 54                                  |

| 5             | Mem<br>Elect         | 3.27.2  uts and  ory map  trical ch  Parame 6.1.1 6.1.2 6.1.3                                                     | pin description  ping  aracteristics  eter conditions  Minimum and maximum values  Typical values  Typical curves                                                                                                                                                                                                            | . <b>31</b> . <b>54</b> . 54 . 54                                         |

| 5             | Mem<br>Elect         | 3.27.2  uts and  ory map  trical ch  Parame 6.1.1 6.1.2 6.1.3 6.1.4                                               | pin description  ping  paracteristics eter conditions  Minimum and maximum values  Typical values  Typical curves  Loading capacitor                                                                                                                                                                                         | . <b>51</b> . <b>54</b> . 54 . 54 . 54                                    |

| 5             | Mem<br>Elect         | 3.27.2  uts and  ory map  trical ch  Parame 6.1.1 6.1.2 6.1.3 6.1.4 6.1.5                                         | pin description  ping  aracteristics eter conditions  Minimum and maximum values  Typical values  Typical curves  Loading capacitor  Pin input voltage                                                                                                                                                                       | . <b>51</b> . <b>54</b> . 54 . 54 . 54 . 54                               |

| 5             | Mem<br>Elect         | 3.27.2  uts and  ory map  trical ch  Parame 6.1.1 6.1.2 6.1.3 6.1.4 6.1.5 6.1.6                                   | pin description  ping  paracteristics eter conditions  Minimum and maximum values  Typical values  Typical curves  Loading capacitor  Pin input voltage  Power supply scheme                                                                                                                                                 | . <b>51</b> . <b>54</b> . 54 . 54 . 54 . 54 . 54                          |

| 5             | Mem<br>Elect<br>6.1  | 3.27.2  uts and  ory map  trical ch  Parame 6.1.1 6.1.2 6.1.3 6.1.4 6.1.5 6.1.6 6.1.7                             | pin description  ping  paracteristics eter conditions  Minimum and maximum values  Typical values  Typical curves  Loading capacitor  Pin input voltage  Power supply scheme  Current consumption measurement                                                                                                                | . 51<br>. 54<br>. 54<br>. 54<br>. 54<br>. 54<br>. 54<br>. 54<br>. 55      |

| 5             | <b>Mem Elect</b> 6.1 | 3.27.2  uts and  ory map  trical ch  Parame 6.1.1 6.1.2 6.1.3 6.1.4 6.1.5 6.1.6 6.1.7 Absolut                     | pin description  ping  paracteristics eter conditions  Minimum and maximum values  Typical values  Typical curves  Loading capacitor  Pin input voltage  Power supply scheme  Current consumption measurement  te maximum ratings                                                                                            | . <b>51</b> . <b>54</b> . 54 . 54 . 54 . 54 . 54 . 55 . 56                |

| 5             | Mem<br>Elect<br>6.1  | 3.27.2  uts and  ory map  trical ch  Parame 6.1.1 6.1.2 6.1.3 6.1.4 6.1.5 6.1.6 6.1.7 Absolut Operati             | pin description  ping  paracteristics eter conditions  Minimum and maximum values  Typical values  Typical curves  Loading capacitor  Pin input voltage  Power supply scheme  Current consumption measurement  te maximum ratings  ing conditions                                                                            | . <b>51</b> . <b>54</b> . 54 . 54 . 54 . 54 . 54 . 55 . 56 . 56           |

| 5             | <b>Mem Elect</b> 6.1 | 3.27.2  uts and  ory map  trical ch  Parame 6.1.1 6.1.2 6.1.3 6.1.4 6.1.5 6.1.6 6.1.7 Absolut Operati 6.3.1       | pin description  ping  paracteristics eter conditions  Minimum and maximum values  Typical values  Typical curves  Loading capacitor  Pin input voltage  Power supply scheme  Current consumption measurement  te maximum ratings  ing conditions  General operating conditions                                              | . <b>51</b> . <b>54</b> . 54 . 54 . 54 . 54 . 54 . 55 . 56 . 56 . 58      |

| 5             | <b>Mem Elect</b> 6.1 | 3.27.2  uts and  ory map  trical ch  Parame 6.1.1 6.1.2 6.1.3 6.1.4 6.1.5 6.1.6 6.1.7 Absolut Operati 6.3.1 6.3.2 | pin description  ping  paracteristics eter conditions  Minimum and maximum values  Typical values  Typical curves  Loading capacitor  Pin input voltage  Power supply scheme  Current consumption measurement te maximum ratings ing conditions  General operating conditions  Operating conditions at power-up / power-down | . <b>51</b> . <b>54</b> . 54 . 54 . 54 . 54 . 54 . 55 . 56 . 56 . 58 . 59 |

| 5             | <b>Mem Elect</b> 6.1 | 3.27.2  uts and  ory map  trical ch  Parame 6.1.1 6.1.2 6.1.3 6.1.4 6.1.5 6.1.6 6.1.7 Absolut Operati 6.3.1       | pin description  ping  paracteristics eter conditions  Minimum and maximum values  Typical values  Typical curves  Loading capacitor  Pin input voltage  Power supply scheme  Current consumption measurement  te maximum ratings  ing conditions  General operating conditions                                              | . <b>51</b> . <b>54</b> . 54 . 54 . 54 . 54 . 54 . 55 . 56 . 56 . 58 . 59 |

# List of figures

| Figure 1.  | STM32F302xB/STM32F302xC block diagram                                            | 12 |

|------------|----------------------------------------------------------------------------------|----|

| Figure 2.  | Clock tree                                                                       | 18 |

| Figure 3.  | Infrared transmitter                                                             | 28 |

| Figure 4.  | STM32F302xB/STM32F302xC LQFP48 pinout                                            | 31 |

| Figure 5.  | STM32F302xB/STM32F302xC LQFP64 pinout                                            | 32 |

| Figure 6.  | STM32F302xB/STM32F302xC LQFP100 pinout                                           | 33 |

| Figure 7.  | STM32F302xB/STM32F302xC WLCSP100 pinout                                          |    |

| Figure 8.  | STM32F302xB/STM32F302xC memory map                                               | 51 |

| Figure 9.  | Pin loading conditions                                                           |    |

| Figure 10. | Pin input voltage                                                                |    |

| Figure 11. | Power supply scheme                                                              |    |

| Figure 12. | Current consumption measurement scheme                                           |    |

| Figure 13. | Typical V <sub>BAT</sub> current consumption (LSE and RTC ON/LSEDRV[1:0] = '00') |    |

| Figure 14. | High-speed external clock source AC timing diagram                               |    |

| Figure 15. | Low-speed external clock source AC timing diagram                                |    |

| Figure 16. | Typical application with an 8 MHz crystal                                        |    |

| Figure 17. | Typical application with a 32.768 kHz crystal                                    |    |

| Figure 18. | HSI oscillator accuracy characterization results for soldered parts              |    |

| Figure 19. | TC and TTa I/O input characteristics - CMOS port                                 |    |

| Figure 20. | TC and TTa I/O input characteristics - TTL port                                  |    |

| Figure 21. | Five volt tolerant (FT and FTf) I/O input characteristics - CMOS port            |    |

| Figure 22. | Five volt tolerant (FT and FTf) I/O input characteristics - TTL port             |    |

| Figure 23. | I/O AC characteristics definition                                                |    |

| Figure 24. | Recommended NRST pin protection                                                  |    |

| Figure 25. | I <sup>2</sup> C bus AC waveforms and measurement circuit                        |    |

| Figure 26. | SPI timing diagram - slave mode and CPHA = 0                                     |    |

| Figure 27. | SPI timing diagram - slave mode and CPHA = 1 <sup>(1)</sup>                      |    |

| Figure 28. | SPI timing diagram - master mode <sup>(1)</sup>                                  | 97 |

| Figure 29. | I <sup>2</sup> S slave timing diagram (Philips protocol) <sup>(1)</sup>          | 99 |

| Figure 30. | I <sup>2</sup> S master timing diagram (Philips protocol) <sup>(1)</sup>         | 99 |

| Figure 31. | USB timings: definition of data signal rise and fall time                        |    |

| Figure 32. | ADC typical current consumption on VDDA pin                                      |    |

| Figure 33. | ADC typical current consumption on VREF+ pin                                     |    |

| Figure 34. | ADC accuracy characteristics                                                     |    |

| Figure 35. | Typical connection diagram using the ADC                                         |    |

| Figure 36. | 12-bit buffered /non-buffered DAC                                                |    |

| Figure 37. | Maximum VREFINT scaler startup time from power down                              |    |

| Figure 38. | OPAMP voltage noise versus frequency                                             |    |

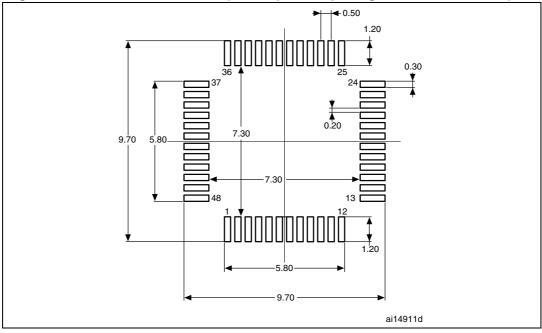

| Figure 39. | LQFP100 – 14 x 14 mm, low-profile quad flat package outline                      |    |

| Figure 40. | LQFP100 – 14 x 14 mm, low-profile quad flat package recommended footprint        |    |

| Figure 41. | LQFP100 – 14 x 14 mm, low-profile quad flat package top view example             |    |

| Figure 42. | LQFP64 – 10 x 10 mm, low-profile quad flat package outline                       |    |

| Figure 43. | LQFP64 – 10 x 10 mm, low-profile quad flat package recommended footprint         |    |

| Figure 44. | LQFP64 – 10 x 10 mm, low-profile quad flat package top view example              |    |

| Figure 45. | LQFP48 – 7 x 7 mm, low-profile quad flat package outline                         |    |

| Figure 46. | LQFP48 - 7 x 7 mm, low-profile quad flat package recommended footprint           |    |

| Figure 47. | LQFP48 - 7 x 7 mm, low-profile quad flat package top view example                |    |

| Figure 48. | WLCSP100 – 100L, 4.166 x 4.628 mm 0.4 mm pitch wafer level chip scale            |    |

|            |                                                                                  |    |

## 1 Introduction

This datasheet provides the ordering information and mechanical device characteristics of the STM32F302xB/STM32F302xC microcontrollers.

This STM32F302xB/STM32F302xC datasheet should be read in conjunction with the STM32F302xx reference manual (RM0365). The reference manual is available from the STMicroelectronics website *www.st.com*.

For information on the Cortex<sup>®</sup>-M4 core with FPU, please refer to:

- Cortex®-M4 with FPU Technical Reference Manual, available from ARM website www.arm.com.

- STM32F3xxx and STM32F4xxx Cortex<sup>®</sup>-M4 programming manual (PM0214) available from our website www.st.com.

Table 4. STM32F302xB/STM32F302xC peripheral interconnect matrix (continued)

| Interconnect source                             | Interconnect<br>destination | Interconnect action                                            |

|-------------------------------------------------|-----------------------------|----------------------------------------------------------------|

| GPIO<br>RTCCLK<br>HSE/32<br>MC0                 | TIM16                       | Clock source used as input channel for HSI and LSI calibration |

| CSS<br>CPU (hard fault)<br>COMPx<br>PVD<br>GPIO | TIM1,<br>TIM15, 16, 17      | Timer break                                                    |

|                                                 | TIMx                        | External trigger, timer break                                  |

| GPIO                                            | ADCx<br>DAC1                | Conversion external trigger                                    |

| DAC1                                            | COMPx                       | Comparator inverting input                                     |

Note:

For more details about the interconnect actions, please refer to the corresponding sections in the reference manual (RM0365.

## 3.9 Clocks and startup

System clock selection is performed on startup, however the internal RC 8 MHz oscillator is selected as default CPU clock on reset. An external 4-32 MHz clock can be selected, in which case it is monitored for failure. If failure is detected, the system automatically switches back to the internal RC oscillator. A software interrupt is generated if enabled. Similarly, full interrupt management of the PLL clock entry is available when necessary (for example with failure of an indirectly used external oscillator).

Several prescalers allow to configure the AHB frequency, the high speed APB (APB2) and the low speed APB (APB1) domains. The maximum frequency of the AHB and the high speed APB domains is 72 MHz, while the maximum allowed frequency of the low speed APB domain is 36 MHz.

## 3.10 General-purpose input/outputs (GPIOs)

Each of the GPIO pins can be configured by software as output (push-pull or open-drain), as input (with or without pull-up or pull-down) or as peripheral alternate function. Most of the GPIO pins are shared with digital or analog alternate functions. All GPIOs are high current capable except for analog inputs.

The I/Os alternate function configuration can be locked if needed following a specific sequence in order to avoid spurious writing to the I/Os registers.

Fast I/O handling allows I/O toggling up to 36 MHz.

## 3.11 Direct memory access (DMA)

The flexible general-purpose DMA is able to manage memory-to-memory, peripheral-to-memory and memory-to-peripheral transfers. The DMA controller supports circular buffer management, avoiding the generation of interrupts when the controller reaches the end of the buffer.

Each of the 12 DMA channels is connected to dedicated hardware DMA requests, with software trigger support for each channel. Configuration is done by software and transfer sizes between source and destination are independent.

The DMA can be used with the main peripherals: SPI,  $I^2C$ , USART, general-purpose timers, DAC and ADC.

## 3.12 Interrupts and events

### 3.12.1 Nested vectored interrupt controller (NVIC)

The STM32F302xB/STM32F302xC devices embed a nested vectored interrupt controller (NVIC) able to handle up to 66 maskable interrupt channels and 16 priority levels.

The NVIC benefits are the following:

- Closely coupled NVIC gives low latency interrupt processing

- Interrupt entry vector table address passed directly to the core

- Closely coupled NVIC core interface

- Allows early processing of interrupts

- Processing of late arriving higher priority interrupts

- Support for tail chaining

- Processor state automatically saved

- Interrupt entry restored on interrupt exit with no instruction overhead

The NVIC hardware block provides flexible interrupt management features with minimal interrupt latency.

## 3.13 Fast analog-to-digital converter (ADC)

Two fast analog-to-digital converters 5 MSPS, with selectable resolution between 12 and 6 bit, are embedded in the STM32F302xB/STM32F302xC family devices. The ADCs have up to 17 external channels (5 channels multiplexed between ADC1 and ADC2). Channels can be configured to be either single-ended input or differential input. The ADCs can perform conversions in single-shot or scan modes. In scan mode, automatic conversion is performed on a selected group of analog inputs.

The ADCs have also internal channels: Temperature sensor connected to ADC1 channel 16,  $V_{BAT/2}$  connected to ADC1 channel 17, Voltage reference  $V_{REFINT}$  connected to the 2 ADCs channel 18, VREFOPAMP1 connected to ADC1 channel 15 and VREFOPAMP2 connected to ADC2 channel 17.

Additional logic functions embedded in the ADC interface allow:

- Simultaneous sample and hold

- Interleaved sample and hold

- Single-shunt phase current reading techniques.

The ADC can be served by the DMA controller. 3 analog watchdogs per ADC are available.

An analog watchdog feature allows very precise monitoring of the converted voltage of one, some or all selected channels. An interrupt is generated when the converted voltage is outside the programmed thresholds.

The events generated by the general-purpose timers and the advanced-control timer (TIM1) can be internally connected to the ADC start trigger and injection trigger, respectively, to allow the application to synchronize A/D conversion and timers.

#### 3.13.1 Temperature sensor

The temperature sensor (TS) generates a voltage  $V_{\text{SENSE}}$  that varies linearly with temperature.

The temperature sensor is internally connected to the ADC1\_IN16 input channel which is used to convert the sensor output voltage into a digital value.

The sensor provides good linearity but it has to be calibrated to obtain good overall accuracy of the temperature measurement. As the offset of the temperature sensor varies from chip to chip due to process variation, the uncalibrated internal temperature sensor is suitable for applications that detect temperature changes only.

To improve the accuracy of the temperature sensor measurement, each device is individually factory-calibrated by ST. The temperature sensor factory calibration data are stored by ST in the system memory area, accessible in read-only mode.

## 3.13.2 Internal voltage reference (V<sub>REFINT</sub>)

The internal voltage reference ( $V_{REFINT}$ ) provides a stable (bandgap) voltage output for the ADC and Comparators.  $V_{REFINT}$  is internally connected to the ADCx\_IN18, x=1...2 input channel. The precise voltage of  $V_{REFINT}$  is individually measured for each part by ST during production test and stored in the system memory area. It is accessible in read-only mode.

Table 13. STM32F302xB/STM32F302xC pin definitions (continued)

|          | Pin nu  | umber  |        |                                                |          |               |       | Pin fui                                                            | nctions                                   |  |

|----------|---------|--------|--------|------------------------------------------------|----------|---------------|-------|--------------------------------------------------------------------|-------------------------------------------|--|

| WLCSP100 | LQFP100 | LQFP64 | LQFP48 | Pin name<br>(function<br>after<br>reset)       | Pin type | I/O structure | Notes | Alternate functions                                                | Additional functions                      |  |

| С9       | 7       | 2      | 2      | PC13 <sup>(2)</sup>                            | I/O      | TC            | -     | TIM1_CH1N                                                          | WKUP2, RTC_TAMP1,<br>RTC_TS, RTC_OUT      |  |

| C10      | 8       | 3      | 3      | PC14 <sup>(2)</sup><br>OSC32_IN<br>(PC14)      | I/O      | TC            | -     | -                                                                  | OSC32_IN                                  |  |

| D9       | 9       | 4      | 4      | PC15 <sup>(2)</sup><br>OSC32_<br>OUT<br>(PC15) | I/O      | тс            | i     | -                                                                  | OSC32_OUT                                 |  |

| D10      | 10      | -      | -      | PF9                                            | I/O      | FT            | (1)   | TIM15_CH1, SPI2_SCK,<br>EVENTOUT                                   | -                                         |  |

| E10      | 11      | -      | -      | PF10                                           | I/O      | FT            | (1)   | TIM15_CH2, SPI2_SCK,<br>EVENTOUT                                   | -                                         |  |

| F10      | 12      | 5      | 5      | PF0-<br>OSC_IN<br>(PF0)                        | I/O      | FTf           | -     | TIM1_CH3N, I2C2_SDA,                                               | OSC_IN                                    |  |

| F9       | 13      | 6      | 6      | PF1-<br>OSC_OUT<br>(PF1)                       | I/O      | FTf           | 1     | 12C2_SCL                                                           | OSC_OUT                                   |  |

| E9       | 14      | 7      | 7      | NRST                                           | I/O      | RS<br>T       |       | Device reset input / intern                                        | al reset output (active low)              |  |

| G10      | 15      | 8      | ı      | PC0                                            | I/O      | TTa           | (1)   | EVENTOUT                                                           | ADC12_IN6                                 |  |

| G9       | 16      | 9      | ı      | PC1                                            | I/O      | TTa           | (1)   | EVENTOUT                                                           | ADC12_IN7                                 |  |

| G8       | 17      | 10     | -      | PC2                                            | I/O      | TTa           | (1)   | EVENTOUT                                                           | ADC12_IN8                                 |  |

| H10      | 18      | 11     | -      | PC3                                            |          | TTa           |       |                                                                    | ADC12_IN9                                 |  |

| E8       | 19      | -      | -      | PF2                                            | I/O      | TTa           | (1)   | EVENTOUT                                                           | ADC12_IN10                                |  |

| Н8       | 20      | 12     | 8      | VSSA/<br>VREF-                                 | S        | -             | 1     | Analog ground/Nega                                                 | tive reference voltage                    |  |

| J8       | 21      | -      | -      | VREF+ <sup>(3)</sup>                           | S        | -             | -     | Positive reference voltage                                         |                                           |  |

| J10      | 22      | -      | -      | VDDA                                           | S        | -             | ı     | - Analog power supply                                              |                                           |  |

| -        | ı       | 13     | 9      | VDDA/<br>VREF+                                 | S        | -             | _     | Analog power supply/Positive reference voltage                     |                                           |  |

| H9       | 23      | 14     | 10     | PA0                                            | I/O      | TTa           | (4)   | USART2_CTS,<br>TIM2_CH1_ETR,<br>TSC_G1_IO1, COMP1_OUT,<br>EVENTOUT | ADC1_IN1, COMP1_INM,<br>RTC_ TAMP2, WKUP1 |  |

Table 13. STM32F302xB/STM32F302xC pin definitions (continued)

|          | Pin nu  | ımber  |        |                                          |          |               |       | Pin fur                                                                                                                  | nctions              |

|----------|---------|--------|--------|------------------------------------------|----------|---------------|-------|--------------------------------------------------------------------------------------------------------------------------|----------------------|

| WLCSP100 | LQFP100 | LQFP64 | LQFP48 | Pin name<br>(function<br>after<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                                                                                      | Additional functions |

| C3       | 82      | -      | -      | PD1                                      | I/O      | FT            | (1)   | CAN_TX, EVENTOUT                                                                                                         | -                    |

| A4       | 83      | 54     | -      | PD2                                      | I/O      | FT            | (1)   | UART5_RX, TIM3_ETR,<br>EVENTOUT                                                                                          | -                    |

| B4       | 84      | -      | -      | PD3                                      | I/O      | FT            | (1)   | USART2_CTS,<br>TIM2_CH1_ETR,<br>EVENTOUT                                                                                 | -                    |

| C4       | 85      | -      | -      | PD4                                      | I/O      | FT            | (1)   | USART2_RTS_DE,<br>TIM2_CH2, EVENTOUT                                                                                     | -                    |

| -        | 86      | -      | -      | PD5                                      | I/O      | FT            | (1)   | USART2_TX, EVENTOUT                                                                                                      | -                    |

| -        | 87      | -      | -      | PD6                                      | I/O      | FT            | (1)   | USART2_RX, TIM2_CH4,<br>EVENTOUT                                                                                         | -                    |

| D4       | 88      | -      | -      | PD7                                      | I/O      | FT            | (1)   | USART2_CK, TIM2_CH3,<br>EVENTOUT                                                                                         | -                    |

| A5       | 89      | 55     | 39     | PB3                                      | I/O      | FT            | -     | SPI3_SCK, I2S3_CK,<br>SPI1_SCK, USART2_TX,<br>TIM2_CH2, TIM3_ETR,<br>TIM4_ETR, TSC_G5_IO1,<br>JTDO-TRACESWO,<br>EVENTOUT | -                    |

| B5       | 90      | 56     | 40     | PB4                                      | I/O      | FT            | -     | SPI3_MISO, I2S3ext_SD,<br>SPI1_MISO, USART2_RX,<br>TIM3_CH1, TIM16_CH1,<br>TIM17_BKIN, TSC_G5_IO2,<br>NJTRST, EVENTOUT   | -                    |

| A6       | 91      | 57     | 41     | PB5                                      | I/O      | FT            | -     | SPI3_MOSI, SPI1_MOSI,<br>I2S3_SD, I2C1_SMBA,<br>USART2_CK, TIM16_BKIN,<br>TIM3_CH2, TIM17_CH1,<br>EVENTOUT               | -                    |

| В6       | 92      | 58     | 42     | PB6                                      | I/O      | FTf           | -     | I2C1_SCL, USART1_TX,<br>TIM16_CH1N, TIM4_CH1,<br>TSC_G5_IO3EVENTOUT                                                      | <u>-</u>             |

| C5       | 93      | 59     | 43     | PB7                                      | I/O      | FTf           | -     | I2C1_SDA, USART1_RX,<br>TIM3_CH4, TIM4_CH2,<br>TIM17_CH1N, TSC_G5_IO4,<br>EVENTOUT                                       | -                    |

| A7       | 94      | 60     | 44     | воото                                    | ı        | В             | -     | Boot memo                                                                                                                | ry selection         |

The parameters given in *Table 30* to *Table 34* are derived from tests performed under ambient temperature and supply voltage conditions summarized in *Table 24*.

Table 30. Typical and maximum current consumption from  $V_{DD}$  supply at  $V_{DD}$  = 3.6V

|                 | <b>)</b>             |                         |                   | All  | periphe             | erals en | abled               | All      | periphe             | erals dis | abled               |      |     |  |

|-----------------|----------------------|-------------------------|-------------------|------|---------------------|----------|---------------------|----------|---------------------|-----------|---------------------|------|-----|--|

| Symbol          | Parameter            | Conditions              | f <sub>HCLK</sub> | т    | М                   | ax @ T,  | A <sup>(1)</sup>    | <b>T</b> | М                   | ax @ T    | A <sup>(1)</sup>    | Unit |     |  |

|                 |                      |                         | ly                | Тур  | 25 °C               | 85 °C    | 105 °C              | Тур      | 25 °C               | 85 °C     | 105 °C              |      |     |  |

|                 |                      |                         | 72 MHz            | 61.2 | 65.8                | 67.6     | 68.5                | 27.8     | 30.3                | 30.7      | 31.5                |      |     |  |

|                 |                      |                         | 64 MHz            | 54.7 | 59.1                | 60.2     | 61.1                | 24.6     | 27.2                | 27.6      | 28.3                |      |     |  |

|                 |                      | External                | 48 MHz            | 41.7 | 45.1                | 46.2     | 47.2                | 19.2     | 21.1                | 21.4      | 21.8                |      |     |  |

|                 |                      | clock (HSE              | 32 MHz            | 28.1 | 31.5                | 32.5     | 32.7                | 12.9     | 14.6                | 14.8      | 15.3                |      |     |  |

|                 | Supply               | bypass)                 | 24 MHz            | 21.4 | 23.7                | 24.4     | 25.2                | 10.0     | 11.4                | 11.4      | 12.1                |      |     |  |

|                 | current in           |                         | 8 MHz             | 7.4  | 8.4                 | 8.6      | 9.4                 | 3.6      | 4.1                 | 4.4       | 5.0                 |      |     |  |

|                 | Run mode, executing  |                         | 1 MHz             | 1.3  | 1.6                 | 1.8      | 2.6                 | 0.8      | 1.0                 | 1.2       | 2.1                 |      |     |  |

|                 | from Flash           |                         | 64 MHz            | 49.7 | 54.4                | 55.4     | 56.3                | 24.5     | 27.2                | 27.4      | 28.1                |      |     |  |

|                 |                      | Internal<br>clock (HSI) | 48 MHz            | 37.9 | 42.2                | 43.0     | 43.5                | 18.9     | 21.4                | 21.5      | 21.6                | mA   |     |  |

|                 |                      |                         | 32 MHz            | 25.8 | 29.2                | 29.2     | 30.0                | 12.7     | 14.2                | 14.6      | 15.2                |      |     |  |

|                 |                      |                         | 24 MHz            | 19.7 | 22.3                | 22.6     | 23.2                | 6.7      | 7.7                 | 7.9       | 8.5                 |      |     |  |

|                 |                      |                         | 8 MHz             | 6.9  | 7.8                 | 8.3      | 8.8                 | 3.5      | 4.0                 | 4.4       | 5.0                 |      |     |  |

| I <sub>DD</sub> |                      |                         | 72 MHz            | 60.8 | 66.2 <sup>(2)</sup> | 69.7     | 70.4 <sup>(2)</sup> | 27.4     | 31.7 <sup>(2)</sup> | 32.2      | 32.5 <sup>(2)</sup> | IIIA |     |  |

|                 |                      |                         | 64 MHz            | 54.3 | 59.1                | 62.2     | 63.3                | 24.3     | 28.3                | 28.7      | 28.8                |      |     |  |

|                 |                      | External                | 48 MHz            | 41.0 | 45.6                | 47.3     | 47.9                | 18.3     | 21.6                | 21.9      | 22.1                |      |     |  |

|                 |                      | clock (HSE              | 32 MHz            | 27.6 | 32.4                | 32.4     | 32.9                | 12.3     | 15.0                | 15.2      | 15.4                |      |     |  |

|                 | Supply               | bypass)                 | 24 MHz            | 20.8 | 23.9                | 24.3     | 25.0                | 9.3      | 11.3                | 11.4      | 12.0                |      |     |  |

|                 | current in Run mode, |                         | 8 MHz             | 6.9  | 7.8                 | 8.7      | 9.0                 | 3.1      | 3.7                 | 4.2       | 4.9                 |      |     |  |

|                 | executing            |                         | 1 MHz             | 0.9  | 1.2                 | 1.5      | 2.3                 | 0.4      | 0.6                 | 1.0       | 1.8                 |      |     |  |

|                 | from RAM             |                         | 64 MHz            | 49.2 | 53.9                | 55.2     | 57.4                | 23.9     | 27.8                | 28.2      | 28.4                | ]    |     |  |

|                 |                      |                         | 48 MHz            | 37.3 | 40.8                | 41.4     | 44.1                | 18.2     | 21.0                | 21.6      | 21.9                | ]    |     |  |

|                 |                      | Internal clock (HSI)    | 32 MHz            | 25.1 | 27.6                | 29.1     | 30.1                | 12.0     | 14.0                | 14.5      | 15.1                |      |     |  |

|                 |                      |                         | 24 MHz            | 19.0 | 21.6                | 22.1     | 22.9                | 6.3      | 7.2                 | 7.7       | 8.1                 |      |     |  |

|                 |                      |                         |                   | -    | 8 MHz               | 6.4      | 7.3                 | 7.9      | 8.4                 | 3.0       | 3.5                 | 4.0  | 4.7 |  |

Table 30. Typical and maximum current consumption from  $V_{DD}$  supply at  $V_{DD}$  = 3.6V (continued)

|                 |                      |                       |                   | All  | periphe                             | erals en | abled  | All | abled |       |        |      |  |   |  |  |  |  |       |     |     |     |     |     |     |     |     |  |

|-----------------|----------------------|-----------------------|-------------------|------|-------------------------------------|----------|--------|-----|-------|-------|--------|------|--|---|--|--|--|--|-------|-----|-----|-----|-----|-----|-----|-----|-----|--|

| Symbol          | Parameter            | Conditions            | f <sub>HCLK</sub> | Tun  | Max @ T <sub>A</sub> <sup>(1)</sup> |          |        | T   | M     | Unit  |        |      |  |   |  |  |  |  |       |     |     |     |     |     |     |     |     |  |

|                 |                      |                       |                   | Тур  | 25 °C                               | 85 °C    | 105 °C | Тур | 25 °C | 85 °C | 105 °C |      |  |   |  |  |  |  |       |     |     |     |     |     |     |     |     |  |

|                 |                      |                       | 72 MHz            | 44.0 | 48.4                                | 49.4     | 50.5   | 6.6 | 7.5   | 7.9   | 8.7    |      |  |   |  |  |  |  |       |     |     |     |     |     |     |     |     |  |

|                 |                      |                       | 64 MHz            | 39.2 | 43.3                                | 44.0     | 45.2   | 6.0 | 6.8   | 7.2   | 7.9    |      |  |   |  |  |  |  |       |     |     |     |     |     |     |     |     |  |

|                 |                      | External              | 48 MHz            | 29.6 | 32.7                                | 33.3     | 34.3   | 4.5 | 5.2   | 5.6   | 6.3    |      |  |   |  |  |  |  |       |     |     |     |     |     |     |     |     |  |

|                 | Supply current in    | clock (HSE<br>bypass) | 32 MHz            | 19.7 | 23.3                                | 23.3     | 23.5   | 3.1 | 3.5   | 4.0   | 4.8    | mA   |  |   |  |  |  |  |       |     |     |     |     |     |     |     |     |  |

|                 |                      |                       | 24 MHz            | 14.9 | 17.6                                | 17.8     | 18.3   | 2.4 | 2.8   | 3.3   | 3.9    |      |  |   |  |  |  |  |       |     |     |     |     |     |     |     |     |  |

| 1               | Sleep<br>mode,       |                       | 8 MHz             | 4.9  | 5.7                                 | 6.1      | 6.9    | 0.8 | 1.0   | 1.4   | 2.2    |      |  |   |  |  |  |  |       |     |     |     |     |     |     |     |     |  |

| I <sub>DD</sub> | executing            |                       | 1 MHz             | 0.6  | 0.9                                 | 1.2      | 2.1    | 0.1 | 0.3   | 0.6   | 1.5    | IIIA |  |   |  |  |  |  |       |     |     |     |     |     |     |     |     |  |

|                 | from Flash<br>or RAM |                       | 64 MHz            | 34.2 | 38.1                                | 39.2     | 40.3   | 5.7 | 6.3   | 6.8   | 7.5    |      |  |   |  |  |  |  |       |     |     |     |     |     |     |     |     |  |

|                 | OI TO WI             |                       | 48 MHz            | 25.8 | 28.7                                | 29.6     | 30.3   | 4.3 | 4.8   | 5.2   | 5.9    |      |  |   |  |  |  |  |       |     |     |     |     |     |     |     |     |  |

|                 |                      | Internal clock (HSI)  | 32 MHz            | 17.4 | 19.4                                | 19.9     | 20.7   | 2.9 | 3.2   | 3.7   | 4.5    |      |  |   |  |  |  |  |       |     |     |     |     |     |     |     |     |  |

|                 |                      | , ,                   | 24 MHz            | 13.2 | 15.1                                | 15.6     | 15.9   | 1.5 | 1.8   | 2.2   | 2.9    |      |  |   |  |  |  |  |       |     |     |     |     |     |     |     |     |  |

|                 |                      |                       |                   |      |                                     | -        |        | _   |       |       |        | _    |  | _ |  |  |  |  | 8 MHz | 4.5 | 5.0 | 5.6 | 6.2 | 0.7 | 0.9 | 1.2 | 2.1 |  |

<sup>1.</sup> Guaranteed by characterization results unless otherwise specified.

Table 31. Typical and maximum current consumption from the  $V_{\text{DDA}}$  supply

|                  |                         |                |                   |     | V <sub>DDA</sub>                    | = 2.4 V | ,      | V <sub>DDA</sub> = 3.6 V |       |       |        |     |     |     |     |  |

|------------------|-------------------------|----------------|-------------------|-----|-------------------------------------|---------|--------|--------------------------|-------|-------|--------|-----|-----|-----|-----|--|

| Symbol           | Parameter               | Conditions (1) | f <sub>HCLK</sub> | Тур | Max @ T <sub>A</sub> <sup>(2)</sup> |         |        | Тур                      | М     | Unit  |        |     |     |     |     |  |

|                  |                         |                |                   | тур | 25 °C                               | 85 °C   | 105 °C | JP                       | 25 °C | 85 °C | 105 °C |     |     |     |     |  |

|                  |                         |                | 72 MHz            | 225 | 276                                 | 289     | 297    | 245                      | 302   | 319   | 329    |     |     |     |     |  |

|                  |                         |                | 64 MHz            | 198 | 249                                 | 261     | 268    | 216                      | 270   | 284   | 293    |     |     |     |     |  |

|                  |                         |                | 48 MHz            | 149 | 195                                 | 204     | 211    | 159                      | 209   | 222   | 230    |     |     |     |     |  |

|                  | Supply                  | HSE<br>bypass  | 32 MHz            | 102 | 145                                 | 152     | 157    | 110                      | 154   | 162   | 169    |     |     |     |     |  |

|                  | current in<br>Run/Sleep |                | 24 MHz            | 80  | 119                                 | 124     | 128    | 86                       | 126   | 131   | 135    |     |     |     |     |  |

| l                | mode,                   |                | 8 MHz             | 2   | 3                                   | 4       | 6      | 3                        | 4     | 5     | 9      | μΑ  |     |     |     |  |

| I <sub>DDA</sub> | code                    |                | 1 MHz             | 2   | 3                                   | 5       | 7      | 3                        | 4     | 6     | 9      | μΛ  |     |     |     |  |

|                  | executing<br>from Flash |                | 64 MHz            | 270 | 323                                 | 337     | 344    | 299                      | 354   | 371   | 381    |     |     |     |     |  |

|                  | or RAM                  |                | 48 MHz            | 220 | 269                                 | 280     | 286    | 244                      | 293   | 309   | 318    |     |     |     |     |  |

|                  |                         | HSI clock      | 32 MHz            | 173 | 218                                 | 228     | 233    | 193                      | 239   | 251   | 257    |     |     |     |     |  |

|                  |                         |                |                   |     |                                     |         | 24 MHz | 151                      | 194   | 200   | 204    | 169 | 211 | 219 | 225 |  |

|                  |                         |                |                   |     | 8 MHz                               | 73      | 97     | 99                       | 103   | 88    | 105    | 110 | 116 |     |     |  |

Current consumption from the V<sub>DDA</sub> supply is independent of whether the peripherals are on or off. Furthermore when the PLL is off, I<sub>DDA</sub> is independent from the frequency.

<sup>2.</sup> Guaranteed by characterization results.

<sup>2.</sup> Data based on characterization results and tested in production with code executing from RAM.

Table 32. Typical and maximum  $V_{\mbox{\scriptsize DD}}$  consumption in Stop and Standby modes

|                  | Do no mosto n                 |                                                  |       | Тур ( | @V <sub>DD</sub> ( | (V <sub>DD</sub> =\ |       |       |                        |                           |                            |      |

|------------------|-------------------------------|--------------------------------------------------|-------|-------|--------------------|---------------------|-------|-------|------------------------|---------------------------|----------------------------|------|

| Symbol Parameter |                               | Conditions                                       | 2.0 V | 2.4 V | 2.7 V              | 3.0 V               | 3.3 V | 3.6 V | T <sub>A</sub> = 25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | Unit |

|                  | Supply current in             | Regulator in run mode, all oscillators OFF       | 20.05 | 20.33 | 20.42              | 20.50               | 20.67 | 20.80 | 44.2 <sup>(2)</sup>    | 350                       | 735 <sup>(2)</sup>         |      |

|                  | Stop mode                     | Regulator in low-power mode, all oscillators OFF | 7.63  | 7.77  | 7.90               | 8.07                | 8.17  | 8.33  | 30.6 <sup>(2)</sup>    | 335                       | 720 <sup>(2)</sup>         | μA   |

|                  | 1- 1- 7                       | LSI ON and IWDG ON                               | 0.80  | 0.96  | 1.09               | 1.23                | 1.37  | 1.51  | -                      | -                         | ı                          |      |

|                  | current in<br>Standby<br>mode | LSI OFF and IWDG OFF                             | 0.60  | 0.74  | 0.83               | 0.93                | 1.02  | 1.11  | 5.0 <sup>(2)</sup>     | 7.8                       | 13.3 <sup>(2)</sup>        |      |

<sup>1.</sup> Guaranteed by characterization results unless otherwise specified.

Table 33. Typical and maximum  $V_{\text{DDA}}$  consumption in Stop and Standby modes

|                  |                               |           |                                                  | DDA   | Тур @                | V <sub>DD</sub> (       | V <sub>DD</sub> = | V <sub>DDA</sub> ) |       |                        |                        |                            |                                                        |      |      |      |      |      |      |   |   |   |  |

|------------------|-------------------------------|-----------|--------------------------------------------------|-------|----------------------|-------------------------|-------------------|--------------------|-------|------------------------|------------------------|----------------------------|--------------------------------------------------------|------|------|------|------|------|------|---|---|---|--|

| Symbol           | Parameter                     |           | Conditions                                       | 2.0 V | 2.4 V                | 2.7 V                   | 3.0 V             | 3.3 V              | 3.6 V | T <sub>A</sub> = 25 °C | T <sub>A</sub> = 85 °C | T <sub>A</sub> =<br>105 °C | Unit                                                   |      |      |      |      |      |      |   |   |   |  |

|                  | Supply                        | NO        | Regulator in run mode, all oscillators OFF       | 1.81  | 1.95                 | 2.07                    | 2.20              | 2.35               | 2.52  | 3.7                    | 5.5                    | 8.8                        |                                                        |      |      |      |      |      |      |   |   |   |  |

|                  | current in<br>Stop mode       | oring Ol  | Regulator in low-power mode, all oscillators OFF | 1.81  | 1.95                 | 2.07                    | 2.20              | 2.35               | 2.52  | 3.7                    | 5.5                    | 8.8                        |                                                        |      |      |      |      |      |      |   |   |   |  |

|                  | Supply                        |           | LSI ON and IWDG ON                               | 2.22  | 2.42                 | 2.59                    | 2.78              | 3.0                | 3.24  | ı                      | -                      | ı                          |                                                        |      |      |      |      |      |      |   |   |   |  |

|                  | current in<br>Standby<br>mode | $V_{DDA}$ | LSI OFF and IWDG<br>OFF                          | 1.69  | 1.82                 | 1.94                    | 2.08              | 2.23               | 2.40  | 3.5                    | 5.4                    | 9.2                        | μA                                                     |      |      |      |      |      |      |   |   |   |  |

| I <sub>DDA</sub> | Supply                        |           | Regulator in run mode, all oscillators OFF       | 1.05  | 1.08                 | 1.10                    | 1.15              | 1.22               | 1.29  | -                      | -                      | -                          | μΑ                                                     |      |      |      |      |      |      |   |   |   |  |

|                  | current in                    |           | current in                                       |       | current in Stop mode | current in<br>Stop mode |                   |                    |       |                        |                        | =                          | Regulator in low-power<br>mode, all oscillators<br>OFF | 1.05 | 1.08 | 1.10 | 1.15 | 1.22 | 1.29 | - | - | - |  |

|                  | - Capp.                       | Supply    |                                                  | _     | LSI ON and IWDG ON   | 1.44                    | 1.52              | 1.60               | 1.71  | 1.84                   | 1.98                   | į                          | -                                                      | -    |      |      |      |      |      |   |   |   |  |

|                  | current in<br>Standby<br>mode | VaaV      | LSI OFF and IWDG<br>OFF                          | 0.93  | 0.95                 | 0.98                    | 1.02              | 1.08               | 1.15  | -                      | -                      | -                          |                                                        |      |      |      |      |      |      |   |   |   |  |

<sup>1.</sup> Guaranteed by characterization results.

The total consumption is the sum of IDD and IDDA.

<sup>2.</sup> Data based on characterization results and tested in production.

#### I/O system current consumption

The current consumption of the I/O system has two components: static and dynamic.

#### I/O static current consumption

All the I/Os used as inputs with pull-up generate current consumption when the pin is externally held low. The value of this current consumption can be simply computed by using the pull-up/pull-down resistors values given in *Table 54: I/O static characteristics*.

For the output pins, any external pull-down or external load must also be considered to estimate the current consumption.

Additional I/O current consumption is due to I/Os configured as inputs if an intermediate voltage level is externally applied. This current consumption is caused by the input Schmitt trigger circuits used to discriminate the input value. Unless this specific configuration is required by the application, this supply current consumption can be avoided by configuring these I/Os in analog mode. This is notably the case of ADC input pins which should be configured as analog inputs.

#### Caution:

Any floating input pin can also settle to an intermediate voltage level or switch inadvertently, as a result of external electromagnetic noise. To avoid current consumption related to floating pins, they must either be configured in analog mode, or forced internally to a definite digital value. This can be done either by using pull-up/down resistors or by configuring the pins in output mode.

#### I/O dynamic current consumption

In addition to the internal peripheral current consumption (see *Table 38: Peripheral current consumption*), the I/Os used by an application also contribute to the current consumption. When an I/O pin switches, it uses the current from the MCU supply voltage to supply the I/O pin circuitry and to charge/discharge the capacitive load (internal or external) connected to the pin:

$$I_{SW} = V_{DD} \times f_{SW} \times C$$

where

$I_{SW}$  is the current sunk by a switching I/O to charge/discharge the capacitive load  $V_{DD}$  is the MCU supply voltage

f<sub>SW</sub> is the I/O switching frequency

C is the total capacitance seen by the I/O pin:  $C = C_{INT} + C_{EXT} + C_{S}$

The test pin is configured in push-pull output mode and is toggled by software at a fixed frequency.

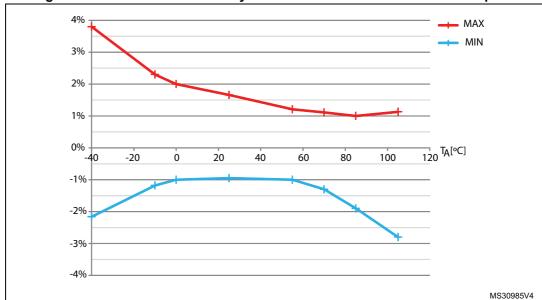

Figure 18. HSI oscillator accuracy characterization results for soldered parts

#### Low-speed internal (LSI) RC oscillator

Table 45. LSI oscillator characteristics<sup>(1)</sup>

| Symbol                              | Parameter                        | Min | Тур  | Max | Unit |

|-------------------------------------|----------------------------------|-----|------|-----|------|

| f <sub>LSI</sub>                    | Frequency                        | 30  | 40   | 50  | kHz  |

| t <sub>su(LSI)</sub> <sup>(2)</sup> | LSI oscillator startup time      | -   | -    | 85  | μs   |

| I <sub>DD(LSI)</sub> <sup>(2)</sup> | LSI oscillator power consumption | -   | 0.75 | 1.2 | μA   |

<sup>1.</sup>  $V_{DDA}$  = 3.3 V,  $T_A$  = -40 to 105 °C unless otherwise specified.

<sup>2.</sup> Guaranteed by design.

#### Static latch-up

Two complementary static tests are required on six parts to assess the latch-up performance:

- A supply overvoltage is applied to each power supply pin

- A current injection is applied to each input, output and configurable I/O pin

These tests are compliant with EIA/JESD 78A IC latch-up standard.

Table 52. Electrical sensitivities

| Symbol | Parameter             | Conditions                                     | Class      |  |

|--------|-----------------------|------------------------------------------------|------------|--|

| LU     | Static latch-up class | T <sub>A</sub> = +105 °C conforming to JESD78A | II level A |  |

#### 6.3.13 I/O current injection characteristics

As a general rule, current injection to the I/O pins, due to external voltage below  $V_{SS}$  or above  $V_{DD}$  (for standard, 3 V-capable I/O pins) should be avoided during normal product operation. However, in order to give an indication of the robustness of the microcontroller in cases when abnormal injection accidentally happens, susceptibility tests are performed on a sample basis during device characterization.

#### Functional susceptibility to I/O current injection

While a simple application is executed on the device, the device is stressed by injecting current into the I/O pins programmed in floating input mode. While current is injected into the I/O pin, one at a time, the device is checked for functional failures.

The failure is indicated by an out of range parameter: ADC error above a certain limit (higher than 5 LSB TUE), out of conventional limits of induced leakage current on adjacent pins (out of  $-5 \,\mu\text{A}/+0 \,\mu\text{A}$  range), or other functional failure (for example reset occurrence or oscillator frequency deviation).

The test results are given in Table 53.

Table 67. USB: Full-speed electrical characteristics<sup>(1)</sup>

| ranio or communication of the |                                 |                                |     |     |     |      |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|--------------------------------|-----|-----|-----|------|--|

| Symbol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Parameter                       | Conditions                     | Min | Тур | Max | Unit |  |