# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                              |

|----------------------------|------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                  |

| Core Size                  | 32-Bit Single-Core                                               |

| Speed                      | 50MHz                                                            |

| Connectivity               | I <sup>2</sup> C, IrDA, SmartCard, SPI, UART/USART               |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                       |

| Number of I/O              | 28                                                               |

| Program Memory Size        | 32KB (32K x 8)                                                   |

| Program Memory Type        | FLASH                                                            |

| EEPROM Size                | -                                                                |

| RAM Size                   | 8K x 8                                                           |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.8V                                                      |

| Data Converters            | A/D 20x10/12b; D/A 1x10b                                         |

| Oscillator Type            | Internal                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                |

| Mounting Type              | Surface Mount                                                    |

| Package / Case             | 40-VFQFN Exposed Pad                                             |

| Supplier Device Package    | 40-QFN (6x6)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/sim3l134-c-gmr |

|                            |                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 4.7.2       UART (UART0)       48         4.7.3       SPI (SPI0, SPI1)       49         4.7.4. I2C (I2C0)       49         4.8. Analog       50         4.8.1. 12-Bit Analog-to-Digital Converter (SARADC0)       50         4.8.1. 12-Bit Analog-to-Digital Converter (IDAC0)       50         4.8.2. 10-Bit Digital-to-Analog Converter (IDAC0)       50         4.8.3. Low Current Comparators (CMP0, CMP1)       50         4.9. Reset Sources       51         4.10. Security.       52         5. Ordering Information       53         6. Pin Definitions       55         6.1. SiM3L1x7 Pin Definitions       55         6.2. SiM3L1x4 Pin Definitions       62         6.3. SiM3L1x4 Pin Definitions       62         6.4. TQFP-80 Saceil Design       77         6.4.1. TQFP-80 Saceil Design       77         6.4.3. TQFP-80 Saceil Design       77         6.5.1. QFN-64 Sace Specifications       78         6.5.1. QFN-64 Sace Specifications       78         6.5.2. QFN-64 Stencil Design       80         6.5.3. QFN-64 Stencil Design       80         6.5.3. QFN-64 Stencil Design       80         6.6.3. TQFP-64 Sace Specifications       81         6.6.1. TQFP-64 Sace Specif                           |    |                                    | 40  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|------------------------------------|-----|

| 4.7.4.       I2C (I2C0)       49         4.8. Analog       50         4.8.1.       12-Bit Analog-to-Digital Converter (SARADC0)       50         4.8.2.       10-Bit Digital-to-Analog Converter (IDAC0)       50         4.8.3.       Low Current Comparators (CMP0, CMP1)       50         4.9.       Reset Sources       51         4.10. Security       52         4.11. On-Chip Debugging       52         5.       Ordering Information       53         6.       Pin Definitions       55         6.1.       SiM3L1x7 Pin Definitions       62         6.3.       SiM3L1x4 Pin Definitions       62         6.4.       TQFP-80 Stencil Design       77         6.4.1.       TQFP-80 Stencil Design       77         6.4.2.       TQFP-80 Stencil Design       77         6.4.3.       TQFP-80 Stencil Design       77         6.5.1.       QFN-64 Stencil Design       77         6.5.2.       QFN-64 Stencil Design       77         6.5.1.       QFN-64 Stencil Design       80         6.5.1.       QFN-64 Card Assembly       80         6.5.1.       QFN-64 Card Assembly       80         6.6.       TQFP-64 Stencil Design       <                                                                                |    |                                    |     |

| 4.8. Analog       50         4.8.1. 12-Bit Analog-to-Digital Converter (SARADC0)       50         4.8.2. 10-Bit Digital-to-Analog Converter (IDAC0)       50         4.8.3. Low Current Comparators (CMP0, CMP1)       50         4.9. Reset Sources       51         4.10. Security       52         4.11. On-Chip Debugging       52         5. Ordering Information       53         6. Pin Definitions       55         6.1. SiM3L1x7 Pin Definitions       62         6.3. SiM3L1x4 Pin Definitions       62         6.3. SiM3L1x4 Pin Definitions       69         6.4.1. TQFP-80 Solder Mask Design       77         6.4.2. TQFP-80 Stencil Design       77         6.4.3. TQFP-80 Card Assembly       77         6.5.1. QFN-64 Solder Mask Design       77         6.5.1. QFN-64 Solder Mask Design       80         6.5.2. QFN-64 Card Assembly       80         6.5.3. QFN-64 Card Assembly       80         6.5.3. QFN-64 Card Assembly       80         6.6.1. TQFP-64 Card Assembly       80         6.6.1. TQFP-64 Card Assembly       80         6.6.1. TQFP-64 Card Assembly       80         6.6.2. TQFP-64 Card Assembly       80         6.6.3. TQFP-64 Card Assembly       80 <th></th> <th></th> <th></th> |    |                                    |     |

| 4.8.1.       12-Bit Analog-to-Digital Converter (SARADC0)       50         4.8.2.       10-Bit Digital-to-Analog Converter (IDAC0)       50         4.8.3.       Low Current Comparators (CMP0, CMP1)       50         4.9.       Reset Sources.       51         4.10. Security       52         4.11. On-Chip Debugging       52         5.       Ordering Information       53         6.       Pin Definitions       55         6.1.       SiM3L1x7 Pin Definitions       55         6.2.       SiM3L1x7 Pin Definitions       62         6.3.       SiM3L1x4 Pin Definitions       62         6.3.       SiM3L1x4 Pin Definitions       69         6.4.       TQFP-80 Satencil Design       77         6.4.2.       TQFP-80 Stencil Design       77         6.4.3.       TQFP-80 Stencil Design       77         6.4.3.       TQFP-80 Stencil Design       77         6.5.0.       QFN-64 Stencil Design       77         6.5.1.       QFN-64 Stencil Design       80         6.5.2.       QFN-64 Stencil Design       80         6.5.3.       QFN-64 Stencil Design       80         6.5.1.       QFN-64 Stencil Design       80         6.5.2.                                                                           |    |                                    |     |

| 4.8.2.       10-Bit Digital-to-Analog Converter (IDAC0)       50         4.8.3.       Low Current Comparators (CMP0, CMP1)       50         4.9.       Reset Sources       51         4.10.Security       52         4.11.On-Chip Debugging       52         5.       Ordering Information       53         6.       Pin Definitions       55         6.1.       SiM3L1x7 Pin Definitions       62         6.2.       SiM3L1x7 Pin Definitions       62         6.3.       SiM3L1x4 Pin Definitions       62         6.4.       TQFP-80 Package Specifications       74         6.4.1.       TQFP-80 Solder Mask Design       77         6.4.2.       TQFP-80 Stencil Design       77         6.4.3.       TQFP-80 Card Assembly.       77         6.5.1.       QFN-64 Package Specifications       78         6.5.1.       QFN-64 Stencil Design       80         6.5.2.       QFN-64 Stencil Design       80         6.5.3.       QFN-64 Stencil Design       80         6.5.3.       QFN-64 Stencil Design       80         6.6.       TQFP-64 Solder Mask Design       84         6.6.1.       TQFP-64 Solder Mask Design       84         6.6.1.                                                                           |    |                                    |     |

| 4.8.3. Low Current Comparators (CMP0, CMP1)       50         4.9. Reset Sources       51         4.10.Security       52         4.11.On-Chip Debugging       52         5. Ordering Information       53         6. Pin Definitions       55         6.1. SiM3L1x7 Pin Definitions       55         6.2. SiM3L1x6 Pin Definitions       62         6.3. SiM3L1x4 Pin Definitions       62         6.4. TQFP-80 Package Specifications       74         6.4.1. TQFP-80 Solder Mask Design       77         6.4.2. TQFP-80 Stencil Design       77         6.4.3. TQFP-80 Card Assembly.       77         6.5.1. QFN-64 Package Specifications       78         6.5.1. QFN-64 Solder Mask Design       80         6.5.2. QFN-64 Stencil Design       80         6.5.3. QFN-64 Solder Mask Design       80         6.5.1. QFN-64 Solder Mask Design       80         6.5.2. QFN-64 Stencil Design       80         6.5.3. QFN-64 Card Assembly.       80         6.6. TQFP-64 Solder Mask Design       80         6.6. TQFP-64 Solder Mask Design       84         6.6.3. TQFP-64 Solder Mask Design       84         6.6.1. TQFP-64 Solder Mask Design       84         6.6.2. TQFP-64 Solder Mask Design                         |    |                                    |     |

| 4.9. Reset Sources       51         4.10.Security       52         4.11.On-Chip Debugging       52         5. Ordering Information       53         6. Pin Definitions       55         6.1. SIM3L1x7 Pin Definitions       62         6.2. SiM3L1x6 Pin Definitions       62         6.3. SiM3L1x4 Pin Definitions       69         6.4. TQFP-80 Solder Mask Design       77         6.4.2. TQFP-80 Solder Mask Design       77         6.4.3. TQFP-80 Solder Mask Design       77         6.4.3. TQFP-80 Solder Mask Design       77         6.4.3. TQFP-80 Solder Mask Design       77         6.5.1. QFN-64 Package Specifications       78         6.5.1. QFN-64 Stencil Design       80         6.5.2. QFN-64 Stencil Design       80         6.5.3. QFN-64 Stencil Design       80         6.5.4. TQFP-64 Solder Mask Design       80         6.5.2. QFN-64 Stencil Design       80         6.5.3. QFN-64 Card Assembly       80         6.6.1. TQFP-64 Solder Mask Design       80         6.6.1. TQFP-64 Solder Mask Design       84         6.6.2. TQFP-64 Solder Mask Design       84         6.6.3. TQFP-64 Card Assembly       80         6.6.4. TQFP-64 Solder Mask Design       84 <th></th> <th></th> <th></th> |    |                                    |     |

| 4.10.Security       52         4.11.On-Chip Debugging       52         5. Ordering Information       53         6. Pin Definitions       55         6.1. SiM3L1x7 Pin Definitions       55         6.2. SiM3L1x6 Pin Definitions       62         6.3. SiM3L1x4 Pin Definitions       69         6.4. TQFP-80 Package Specifications       74         6.4.1. TQFP-80 Solder Mask Design       77         6.4.2. TQFP-80 Stencil Design       77         6.4.3. TQFP-80 Stencil Design       77         6.4.3. TQFP-80 Card Assembly       77         6.5.1. QFN-64 Package Specifications       78         6.5.2. QFN-64 Stencil Design       80         6.5.2. QFN-64 Solder Mask Design       80         6.5.3. QFN-64 Card Assembly       80         6.6. TQFP-64 Solder Mask Design       80         6.6.1. TQFP-64 Solder Mask Design       81         6.6.2. TQFP-64 Stencil Design       84         6.6.3. TQFP-64 Stencil Design       84         6.6.3. TQFP-64 Stencil Design       84         6.7.1. QFN-40 Solder Mask Design       84         6.7.2. QFN-40 Solder Mask Design       87         6.7.3. QFN-40 Solder Mask Design       87         6.7.3. QFN-40 Solder Mask Design       87                        |    |                                    |     |

| 4.11.On-Chip Debugging       52         5. Ordering Information       53         6. Pin Definitions       55         6.1. SiM3L1x7 Pin Definitions       55         6.2. SiM3L1x6 Pin Definitions       62         6.3. SiM3L1x4 Pin Definitions       62         6.4. TQFP-80 Package Specifications       74         6.4.1. TQFP-80 Solder Mask Design       77         6.4.2. TQFP-80 Stencil Design       77         6.4.3. TQFP-80 Card Assembly       77         6.5.4.3. TQFP-80 Card Assembly       77         6.5.4.4.3. TQFP-80 Card Assembly       77         6.5.5.1 QFN-64 Solder Mask Design       80         6.5.2. QFN-64 Stencil Design       80         6.5.3. QFN-64 Solder Mask Design       80         6.5.4. QFN-64 Solder Mask Design       80         6.5.7 QFP-64 Stencil Design       80         6.6.8. TQFP-64 Solder Mask Design       80         6.6.1. TQFP-64 Solder Mask Design       84         6.6.2. TQFP-64 Stencil Design       84         6.6.3. TQFP-64 Card Assembly       84         6.7. QFN-40 Solder Mask Design       87         6.7.1. QFN-40 Solder Mask Design       87         6.7.2. QFN-40 Stencil Design       87         6.7.3. QFN-40 Solder Mask Design                  |    |                                    |     |

| 5. Ordering Information       53         6. Pin Definitions       55         6.1. SiM3L1x7 Pin Definitions       55         6.2. SiM3L1x6 Pin Definitions       62         6.3. SiM3L1x4 Pin Definitions       69         6.4. TQFP-80 Package Specifications       74         6.4.1. TQFP-80 Solder Mask Design       77         6.4.2. TQFP-80 Stencil Design       77         6.4.3. TQFP-80 Card Assembly       77         6.4.3. TQFP-80 Card Assembly       77         6.5.0 QFN-64 Package Specifications       78         6.5.1. QFN-64 Solder Mask Design       80         6.5.2. QFN-64 Stencil Design       80         6.5.3. QFN-64 Stencil Design       80         6.5.3. QFN-64 Card Assembly       80         6.6. TQFP-64 Package Specifications       81         6.6.1. TQFP-64 Solder Mask Design       84         6.6.2. TQFP-64 Stencil Design       84         6.6.3. TQFP-64 Card Assembly       84         6.7.0. QFN-40 Package Specifications       85         6.7.1. QFN-40 Solder Mask Design       87         6.7.2. QFN-40 Stencil Design       87         6.7.3. QFN-40 Stencil Design       87         6.7.3. QFN-40 Stencil Design       87         6.7.3. QFN-40 Stencil Design                |    |                                    |     |

| 6. Pin Definitions       55         6.1. SiM3L1x7 Pin Definitions       55         6.2. SiM3L1x6 Pin Definitions       62         6.3. SiM3L1x4 Pin Definitions       69         6.4. TQFP-80 Package Specifications       74         6.4.1. TQFP-80 Solder Mask Design       77         6.4.2. TQFP-80 Solder Mask Design       77         6.4.3. TQFP-80 Card Assembly       77         6.4.3. TQFP-80 Card Assembly       77         6.5.0 QFN-64 Package Specifications       78         6.5.1. QFN-64 Solder Mask Design       80         6.5.2. QFN-64 Stencil Design       80         6.5.3. QFN-64 Card Assembly       80         6.5.3. QFN-64 Card Assembly       80         6.6.1. TQFP-64 Solder Mask Design       80         6.6.2. TQFP-64 Stencil Design       84         6.6.3. TQFP-64 Solder Mask Design       84         6.6.2. TQFP-64 Stencil Design       84         6.6.3. TQFP-64 Solder Mask Design       84         6.6.3. TQFP-64 Solder Mask Design       84         6.7.1. QFN-40 Solder Mask Design       84         6.7.2. QFN-40 Solder Mask Design       87         6.7.3. QFN-40 Card Assembly       87         6.7.3. QFN-40 Card Assembly       87         6.7.3. QFN-40 Card Assem         |    |                                    |     |

| 6.1. SiM3L1x7 Pin Definitions       55         6.2. SiM3L1x6 Pin Definitions       62         6.3. SiM3L1x4 Pin Definitions       69         6.4. TQFP-80 Package Specifications       74         6.4.1. TQFP-80 Solder Mask Design       77         6.4.2. TQFP-80 Stencil Design       77         6.4.3. TQFP-80 Card Assembly       77         6.4.3. TQFP-80 Card Assembly       77         6.4.3. TQFP-80 Card Assembly       77         6.5.4.3. QFN-64 Package Specifications       78         6.5.1. QFN-64 Stencil Design       80         6.5.2. QFN-64 Stencil Design       80         6.5.3. QFN-64 Stencil Design       80         6.5.3. QFN-64 Card Assembly       80         6.6.1. TQFP-64 Stencil Design       80         6.6.2. TQFP-64 Stencil Design       84         6.6.3. TQFP-64 Card Assembly       84         6.6.3. TQFP-64 Card Assembly       84         6.6.4. TQFP-64 Card Assembly       84         6.6.7. QFN-40 Package Specifications       85         6.7.1. QFN-40 Solder Mask Design       84         6.7.2. QFN-40 Stencil Design       87         6.7.3. QFN-40 Card Assembly       87         6.7.3. QFN-40 Card Assembly       87         6.7.3. QFN-40 Card Assembly                |    |                                    |     |

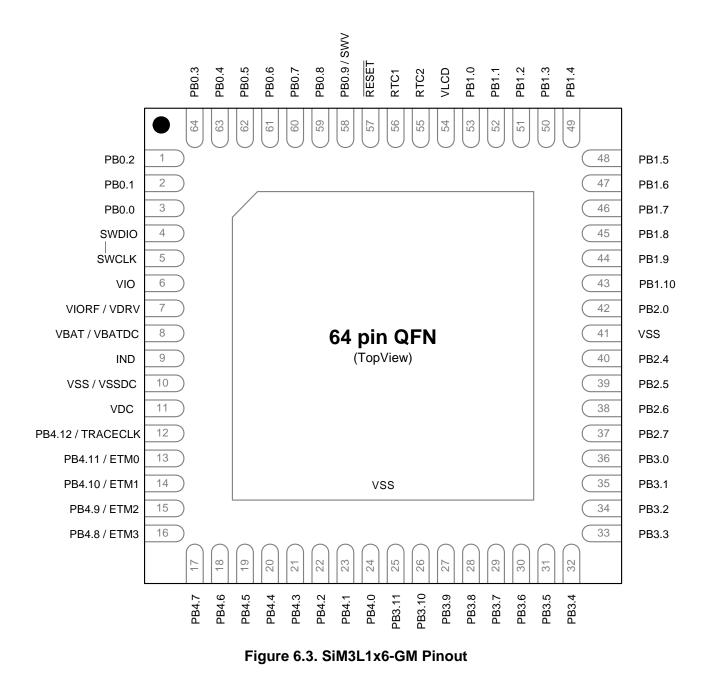

| 6.2. SiM3L1x6 Pin Definitions       62         6.3. SiM3L1x4 Pin Definitions       69         6.4. TQFP-80 Package Specifications       74         6.4.1. TQFP-80 Solder Mask Design       77         6.4.2. TQFP-80 Stencil Design       77         6.4.3. TQFP-80 Card Assembly       77         6.4.3. TQFP-80 Card Assembly       77         6.4.3. TQFP-80 Card Assembly       77         6.5.4.3. TQFP-80 Card Assembly       77         6.5.4.4.4.4.4.4.4.4.4.4.4.4.4.4.4.4.4.4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 6. |                                    |     |

| 6.3. SiM3L1x4 Pin Definitions       69         6.4. TQFP-80 Package Specifications       74         6.4.1. TQFP-80 Solder Mask Design       77         6.4.2. TQFP-80 Stencil Design       77         6.4.3. TQFP-80 Card Assembly       77         6.4.3. TQFP-80 Card Assembly       77         6.4.3. TQFP-80 Card Assembly       77         6.5. QFN-64 Package Specifications       78         6.5.1. QFN-64 Solder Mask Design       80         6.5.2. QFN-64 Stencil Design       80         6.5.3. QFN-64 Card Assembly       80         6.6. TQFP-64 Package Specifications       81         6.6.1. TQFP-64 Solder Mask Design       84         6.6.2. TQFP-64 Stencil Design       84         6.6.3. TQFP-64 Card Assembly       84         6.6.4.6.3. TQFP-64 Card Assembly       84         6.6.7. QFN-40 Package Specifications       85         6.7.1. QFN-40 Solder Mask Design       87         6.7.2. QFN-40 Solder Mask Design       87         6.7.3. QFN-40 Card Assembly       87         6.7.4.4.5.4.5.4.5.4.5.4.5.5.5.5.5.5.5.5.5                                 |    |                                    |     |

| 6.4. TQFP-80 Package Specifications       74         6.4.1. TQFP-80 Solder Mask Design       77         6.4.2. TQFP-80 Stencil Design       77         6.4.3. TQFP-80 Card Assembly       77         6.5. QFN-64 Package Specifications       78         6.5.1. QFN-64 Solder Mask Design       80         6.5.2. QFN-64 Stencil Design       80         6.5.3. QFN-64 Card Assembly       80         6.6. TQFP-64 Package Specifications       81         6.6.1. TQFP-64 Solder Mask Design       84         6.6.2. TQFP-64 Stencil Design       84         6.6.3. TQFP-64 Stencil Design       84         6.6.3. TQFP-64 Stencil Design       84         6.7.0 QFN-40 Package Specifications       85         6.7.1. QFN-40 Solder Mask Design       84         6.7.2. QFN-40 Stencil Design       87         6.7.3. QFN-40 Card Assembly       87         6.7.3. QFN-40 Card Assembly       87         6.7.3. QFN-40 Card Assembly       87         7.1. Revision Identification       88         7.1. Revision Identification       88         7.1. Revision Identification       88                                                                                                                                        |    |                                    |     |

| 6.4.1. TQFP-80 Solder Mask Design.       77         6.4.2. TQFP-80 Stencil Design.       77         6.4.3. TQFP-80 Card Assembly.       77         6.4.3. TQFP-80 Card Assembly.       77         6.5. QFN-64 Package Specifications       78         6.5.1. QFN-64 Solder Mask Design.       80         6.5.2. QFN-64 Stencil Design.       80         6.5.3. QFN-64 Card Assembly.       80         6.6. TQFP-64 Package Specifications       81         6.6.1. TQFP-64 Solder Mask Design.       84         6.6.2. TQFP-64 Stencil Design.       84         6.6.3. TQFP-64 Stencil Design.       84         6.6.3. TQFP-64 Card Assembly.       84         6.7.0 QFN-40 Package Specifications       85         6.7.1. QFN-40 Solder Mask Design.       84         6.7.2. QFN-40 Solder Mask Design.       84         6.7.2. QFN-40 Solder Mask Design.       87         6.7.3. QFN-40 Card Assembly.       87         6.7.3. QFN-40 Card Assembly.       87         7.1. Revision Identification       88         7.1. Revision Identification       88         90       90                                                                                                                                                 |    |                                    |     |

| 6.4.2. TQFP-80 Stencil Design       77         6.4.3. TQFP-80 Card Assembly       77         6.5. QFN-64 Package Specifications       78         6.5.1. QFN-64 Solder Mask Design       80         6.5.2. QFN-64 Stencil Design       80         6.5.3. QFN-64 Card Assembly       80         6.6. TQFP-64 Package Specifications       81         6.6.1. TQFP-64 Solder Mask Design       84         6.6.2. TQFP-64 Stencil Design       84         6.6.3. TQFP-64 Stencil Design       84         6.6.3. TQFP-64 Stencil Design       84         6.6.3. TQFP-64 Stencil Design       84         6.7.0 QFN-40 Package Specifications       85         6.7.1. QFN-64 Card Assembly       84         6.7.2. QFN-40 Solder Mask Design       87         6.7.3. QFN-40 Stencil Design       87         6.7.3. QFN-40 Card Assembly       87         7. Revision Specific Behavior       88         7.1. Revision Identification       88         7.1. Revision Identification       88         7.1. Revision Identification       88                                                                                                                                                                                               |    |                                    |     |

| 6.4.3. TQFP-80 Card Assembly.       77         6.5. QFN-64 Package Specifications       78         6.5.1. QFN-64 Solder Mask Design       80         6.5.2. QFN-64 Stencil Design       80         6.5.3. QFN-64 Card Assembly.       80         6.6. TQFP-64 Package Specifications       81         6.6.1. TQFP-64 Package Specifications       81         6.6.2. TQFP-64 Solder Mask Design       84         6.6.3. TQFP-64 Stencil Design       84         6.6.3. TQFP-64 Card Assembly.       84         6.6.3. TQFP-64 Card Assembly.       84         6.7.0. QFN-40 Package Specifications       85         6.7.1. QFN-40 Solder Mask Design       84         6.7.2. QFN-40 Solder Mask Design       87         6.7.2. QFN-40 Solder Mask Design       87         6.7.3. QFN-40 Card Assembly.       87         7.7. Revision Specific Behavior.       88         7.1. Revision Identification       88         7.1. Revision Identification       88         7.1. Revision Identification       88                                                                                                                                                                                                                      |    |                                    |     |

| 6.5. QFN-64 Package Specifications       78         6.5.1. QFN-64 Solder Mask Design       80         6.5.2. QFN-64 Stencil Design       80         6.5.3. QFN-64 Card Assembly       80         6.6. TQFP-64 Package Specifications       81         6.6.1. TQFP-64 Solder Mask Design       84         6.6.2. TQFP-64 Solder Mask Design       84         6.6.3. TQFP-64 Stencil Design       84         6.6.3. TQFP-64 Card Assembly       84         6.6.3. TQFP-64 Card Assembly       84         6.7. QFN-40 Package Specifications       85         6.7.1. QFN-40 Solder Mask Design       87         6.7.2. QFN-40 Stencil Design       87         6.7.3. QFN-40 Stencil Design       87         6.7.3. QFN-40 Card Assembly       87         7. Revision Specific Behavior       88         7.1. Revision Identification       88         Document Change List       90                                                                                                                                                                                                                                                                                                                                                |    | 6.4.2. TQFP-80 Stencil Design      | .77 |

| 6.5.1. QFN-64 Solder Mask Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    | 6.4.3. TQFP-80 Card Assembly       | .77 |

| 6.5.1. QFN-64 Solder Mask Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    | 6.5. QFN-64 Package Specifications | .78 |

| 6.5.3. QFN-64 Card Assembly.806.6. TQFP-64 Package Specifications816.6.1. TQFP-64 Solder Mask Design846.6.2. TQFP-64 Stencil Design846.6.3. TQFP-64 Card Assembly.846.7. QFN-40 Package Specifications856.7.1. QFN-40 Solder Mask Design876.7.2. QFN-40 Solder Mask Design876.7.3. QFN-40 Stencil Design877. Revision Specific Behavior887.1. Revision Identification88Document Change List                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    | 6.5.1. QFN-64 Solder Mask Design   | .80 |

| 6.6. TQFP-64 Package Specifications       81         6.6.1. TQFP-64 Solder Mask Design       84         6.6.2. TQFP-64 Stencil Design       84         6.6.3. TQFP-64 Card Assembly       84         6.7. QFN-40 Package Specifications       85         6.7.1. QFN-40 Solder Mask Design       87         6.7.2. QFN-40 Stencil Design       87         6.7.3. QFN-40 Card Assembly       87         7. Revision Specific Behavior       88         7.1. Revision Identification       88         Document Change List       90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    | 6.5.2. QFN-64 Stencil Design       | .80 |

| 6.6.1. TQFP-64 Solder Mask Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    | 6.5.3. QFN-64 Card Assembly        | .80 |

| 6.6.2. TQFP-64 Stencil Design       84         6.6.3. TQFP-64 Card Assembly       84         6.7. QFN-40 Package Specifications       85         6.7.1. QFN-40 Solder Mask Design       87         6.7.2. QFN-40 Stencil Design       87         6.7.3. QFN-40 Card Assembly       87         7. Revision Specific Behavior       88         7.1. Revision Identification       88         90       90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |                                    |     |

| 6.6.3. TQFP-64 Card Assembly.846.7. QFN-40 Package Specifications856.7.1. QFN-40 Solder Mask Design876.7.2. QFN-40 Stencil Design876.7.3. QFN-40 Card Assembly.877. Revision Specific Behavior887.1. Revision Identification88Document Change List90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    | 6.6.1. TQFP-64 Solder Mask Design  | .84 |

| 6.7. QFN-40 Package Specifications       85         6.7.1. QFN-40 Solder Mask Design       87         6.7.2. QFN-40 Stencil Design       87         6.7.3. QFN-40 Card Assembly       87         7. Revision Specific Behavior       88         7.1. Revision Identification       88         Document Change List       90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    | 6.6.2. TQFP-64 Stencil Design      | .84 |

| 6.7.1. QFN-40 Solder Mask Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    | 6.6.3. TQFP-64 Card Assembly       | .84 |

| 6.7.2. QFN-40 Stencil Design       87         6.7.3. QFN-40 Card Assembly       87         7. Revision Specific Behavior       88         7.1. Revision Identification       88         Document Change List       90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    | 6.7. QFN-40 Package Specifications | .85 |

| 6.7.3. QFN-40 Card Assembly                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    | 6.7.1. QFN-40 Solder Mask Design   | .87 |

| 7. Revision Specific Behavior                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    | 6.7.2. QFN-40 Stencil Design       | .87 |

| 7.1. Revision Identification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    | 6.7.3. QFN-40 Card Assembly        | .87 |

| Document Change List90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 7. | Revision Specific Behavior         | .88 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |                                    |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Do | ocument Change List                | .90 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Сс | ontact Information                 | .91 |

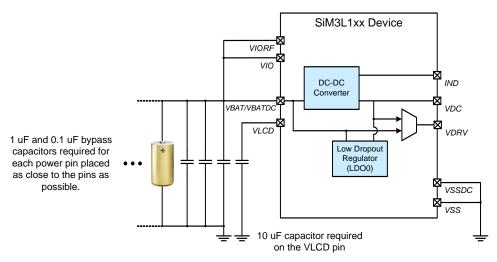

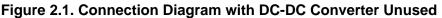

# 2. Typical Connection Diagrams

This section provides typical connection diagrams for SiM3L1xx devices.

### 2.1. Power

Figure 2.1 shows a typical connection diagram for the power pins of the SiM3L1xx devices when the dc-dc buck converter is not used.

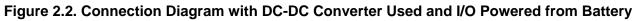

Figure 2.2 shows a typical connection diagram for the power pins of the SiM3L1xx devices when the internal dc-dc buck converter is in use and I/O are powered directly from the battery.

Figure 2.3 shows a typical connection diagram for the power pins of the SiM3L1xx devices when used with an external radio device like the Silicon Labs EZRadio<sup>®</sup> or EZRadioPRO<sup>®</sup> devices.

# 3. Electrical Specifications

## **3.1. Electrical Characteristics**

All electrical parameters in all Tables are specified under the conditions listed in Table 3.1, unless stated otherwise.

Table 3.1. Recommended Operating Conditions

| Parameter                                     | Symbol            | Test Condition | Min  | Тур | Max              | Unit |

|-----------------------------------------------|-------------------|----------------|------|-----|------------------|------|

| Operating Supply Voltage on<br>VBAT/VBATDC    | V <sub>BAT</sub>  |                | 1.8  | —   | 3.8              | V    |

| Operating Supply Voltage on VDC               | V <sub>DC</sub>   |                | 1.25 |     | 3.8              | V    |

| Operating Supply Voltage on VDRV              | V <sub>DRV</sub>  |                | 1.25 | —   | 3.8              | V    |

| Operating Supply Voltage on VIO               | V <sub>IO</sub>   |                | 1.8  |     | V <sub>BAT</sub> | V    |

| Operation Supply Voltage on VIORF             | V <sub>IORF</sub> |                | 1.8  |     | V <sub>BAT</sub> | V    |

| Operation Supply Voltage on VLCD              | V <sub>LCD</sub>  |                | 1.8  | _   | 3.8              | V    |

| System Clock Frequency (AHB)                  | f <sub>AHB</sub>  |                | 0    | _   | 50               | MHz  |

| Peripheral Clock Frequency (APB)              | f <sub>APB</sub>  |                | 0    |     | 50               | MHz  |

| Operating Ambient Temperature                 | T <sub>A</sub>    |                | -40  |     | +85              | °C   |

| Operating Junction Temperature                | TJ                |                | -40  |     | 105              | °C   |

| Note: All voltages with respect to $V_{SS}$ . |                   |                |      |     |                  |      |

#### Table 3.5. On-Chip Regulators

| Parameter                                                         | Symbol              | ymbol Test Condition                                          |      | Тур  | Max  | Unit  |

|-------------------------------------------------------------------|---------------------|---------------------------------------------------------------|------|------|------|-------|

| DC-DC Buck Converter                                              |                     |                                                               |      | 1    | 1    | -     |

| Input Voltage Range                                               | V <sub>DCIN</sub>   |                                                               | 1.8  |      | 3.8  | V     |

| Input Supply to Output Voltage Differ-<br>ential (for regulation) | V <sub>DCREG</sub>  |                                                               | 0.45 | _    | _    | V     |

| Output Voltage Range                                              | V <sub>DCOUT</sub>  |                                                               | 1.25 | —    | 3.8  | V     |

| Output Voltage Accuracy                                           | V <sub>DCACC</sub>  |                                                               | _    | ±25  | _    | mV    |

| Output Current                                                    | IDCOUT              |                                                               | _    | —    | 90   | mA    |

| Inductor Value <sup>1</sup>                                       | L <sub>DC</sub>     |                                                               | 0.47 | 0.56 | 0.68 | μH    |

| Inductor Current Rating                                           | I <sub>LDC</sub>    | I <sub>load</sub> < 50 mA                                     | 450  |      |      | mA    |

|                                                                   |                     | I <sub>load</sub> > 50 mA                                     | 550  |      | _    | mA    |

| Output Capacitor Value                                            | C <sub>DCOUT</sub>  |                                                               | 1    | 2.2  | 10   | μF    |

| Input Capacitor Value <sup>2</sup>                                | C <sub>DCIN</sub>   |                                                               | _    | 4.7  |      | μF    |

| Load Regulation                                                   | R <sub>load</sub>   |                                                               |      | 0.03 |      | mV/mA |

| Maximum DC Load Current During<br>Startup                         | I <sub>DCMAX</sub>  |                                                               | _    | —    | 5    | mA    |

| Switching Clock Frequency                                         | F <sub>DCCLK</sub>  |                                                               | 1.9  | 2.9  | 3.8  | MHz   |

| Local Oscillator Frequency                                        | F <sub>DCOSC</sub>  |                                                               | 2.4  | 2.9  | 3.4  | MHz   |

| LDO Regulators                                                    |                     |                                                               |      | 1    | 1    |       |

| Input Voltage Range <sup>3</sup>                                  | V <sub>LDOIN</sub>  | Sourced from VBAT                                             | 1.8  |      | 3.8  | V     |

|                                                                   |                     | Sourced from VDC                                              | 1.9  |      | 3.8  | V     |

| Output Voltage Range <sup>4</sup>                                 | V <sub>LDO</sub>    |                                                               | 0.8  | _    | 1.9  | V     |

| LDO Output Voltage Accuracy                                       | V <sub>LDOACC</sub> |                                                               | _    | ±25  | _    | mV    |

| Output Settings in PM8 (All LDOs)                                 | V <sub>LDO</sub>    | $1.8 \text{ V} \leq \text{V}_{\text{BAT}} \leq 2.9 \text{ V}$ |      | 1.5  | J    | V     |

|                                                                   |                     | 1.95 V <u>&lt;</u> V <sub>BAT</sub> <u>≤</u> 3.5 V            |      | 1.8  |      | V     |

|                                                                   |                     | 2.0 V ≤ V <sub>BAT</sub> ≤ 3.8 V                              |      | 1.9  |      | V     |

#### Notes:

1. See reference manual for recommended inductors.

- 2. Recommended: X7R or X5R ceramic capacitors with low ESR. Example: Murata GRM21BR71C225K with ESR < 10  $m\Omega$  (@ frequency > 1 MHz).

- Input voltage specification accounts for the internal LDO dropout voltage under the maximum load condition to ensure that the LDO output voltage will remain at a valid level as long as V<sub>LDOIN</sub> is at or above the specified minimum.

- 4. The memory LDO output should always be set equal to or lower than the output of the analog LDO. When lowering both LDOs (for example to go into PM8 under low supply conditions), first adjust the memory LDO and then the analog LDO. When raising the output of both LDOs, adjust the analog LDO before adjusting the memory LDO.

- 5. Output range represents the programmable output range, and does not reflect the minimum voltage under all conditions. Dropout when the input supply is close to the output setting is normal, and accounted for.

- 6. Analog peripheral specifications assume a 1.8 V output on the analog LDO.

Table 3.11. ACCTR (Advanced Capture Counter)

| Parameter                         | Symbol             | Test Condition       | Min | Тур   | Max | Unit |

|-----------------------------------|--------------------|----------------------|-----|-------|-----|------|

| LC Comparator Response Time,      | t <sub>RESP0</sub> | +100 mV Differential |     | 100   |     | ns   |

| CMPMD = 11<br>(Highest Speed)     |                    | –100 mV Differential |     | 150   |     | ns   |

| LC Comparator Response Time,      | t <sub>RESP3</sub> | +100 mV Differential | —   | 1.4   | —   | μs   |

| CMPMD = 00<br>(Lowest Power)      |                    | –100 mV Differential |     | 3.5   | _   | μs   |

| LC Comparator Positive Hysteresis | HYS <sub>CP+</sub> | CMPHYP = 00          |     | 0.37  |     | mV   |

| Mode 0 (CPMD = 11)                |                    | CMPHYP = 01          | —   | 7.9   | _   | mV   |

|                                   |                    | CMPHYP = 10          |     | 16.7  | _   | mV   |

|                                   |                    | CMPHYP = 11          |     | 32.8  | —   | mV   |

| LC Comparator Negative Hysteresis | HYS <sub>CP-</sub> | CMPHYN = 00          |     | 0.37  |     | mV   |

| Mode 0 (CPMD = 11)                |                    | CMPHYN = 01          |     | -7.9  | _   | mV   |

|                                   |                    | CMPHYN = 10          |     | -16.1 | —   | mV   |

|                                   |                    | CMPHYN = 11          |     | -32.7 | _   | mV   |

| LC Comparator Positive Hysteresis | HYS <sub>CP+</sub> | CMPHYP = 00          |     | 0.47  | _   | mV   |

| Mode 1 (CPMD = 10)                |                    | CMPHYP = 01          |     | 5.85  | _   | mV   |

|                                   |                    | CMPHYP = 10          |     | 12    | _   | mV   |

|                                   |                    | CMPHYP = 11          | —   | 24.4  |     | mV   |

| LC Comparator Negative Hysteresis | HYS <sub>CP-</sub> | CMPHYN = 00          |     | 0.47  | _   | mV   |

| Mode 1 (CPMD = 10)                |                    | CMPHYN = 01          |     | -6.0  |     | mV   |

|                                   |                    | CMPHYN = 10          |     | -12.1 |     | mV   |

|                                   |                    | CMPHYN = 11          |     | -24.6 |     | mV   |

| LC Comparator Positive Hysteresis | HYS <sub>CP+</sub> | CMPHYP = 00          |     | 0.66  |     | mV   |

| Mode 2 (CPMD = 01)                |                    | CMPHYP = 01          |     | 4.55  |     | mV   |

|                                   |                    | CMPHYP = 10          |     | 9.3   |     | mV   |

|                                   |                    | CMPHYP = 11          |     | 19    | —   | mV   |

| LC Comparator Negative Hysteresis | HYS <sub>CP-</sub> | CMPHYN = 00          |     | 0.6   | _   | mV   |

| Mode 2 (CPMD = 01)                |                    | CMPHYN = 01          |     | -4.5  | —   | mV   |

|                                   |                    | CMPHYN = 10          |     | -9.5  | —   | mV   |

|                                   |                    | CMPHYN = 11          |     | -19   | _   | mV   |

## Table 3.11. ACCTR (Advanced Capture Counter) (Continued)

| Parameter                                       | Symbol              | Test Condition         | Min   | Тур                  | Max                        | Unit  |

|-------------------------------------------------|---------------------|------------------------|-------|----------------------|----------------------------|-------|

| LC Comparator Positive Hysteresis               | HYS <sub>CP+</sub>  | CMPHYP = 00            | —     | 1.37                 | —                          | mV    |

| Mode 3 (CPMD = 00)                              |                     | CMPHYP = 01            | _     | 3.8                  | _                          | mV    |

|                                                 |                     | CMPHYP = 10            | _     | 7.8                  | _                          | mV    |

|                                                 |                     | CMPHYP = 11            | _     | 15.6                 | _                          | mV    |

| LC Comparator Negative Hysteresis               | HYS <sub>CP-</sub>  | CMPHYN = 00            | _     | 1.37                 |                            | mV    |

| Mode 3 (CPMD = 00)                              |                     | CMPHYN = 01            | _     | -3.9                 |                            | mV    |

|                                                 |                     | CMPHYN = 10            |       | -7.9                 | _                          | mV    |

|                                                 |                     | CMPHYN = 11            | _     | -16                  |                            | mV    |

| LC Comparator Input Range<br>(ACCTR0_LCIN pin)  | V <sub>IN</sub>     |                        | -0.25 | _                    | V <sub>BAT</sub> +<br>0.25 | V     |

| LC Comparator Common-Mode<br>Rejection Ratio    | CMRR <sub>CP</sub>  |                        | _     | 75                   | _                          | dB    |

| LC Comparator Power Supply Rejec-<br>tion Ratio | PSRR <sub>CP</sub>  |                        | _     | 72                   | —                          | dB    |

| LC Comparator Input Offset Voltage              | V <sub>OFF</sub>    | T <sub>A</sub> = 25 °C | -10   | 0                    | 10                         | mV    |

| LC Comparator Input Offset Tempco               | TC <sub>OFF</sub>   |                        | _     | 3.5                  | _                          | µV/°C |

| Reference DAC Offset Error                      | DAC <sub>EOFF</sub> |                        | -1    | —                    | 1                          | LSB   |

| Reference DAC Full Scale Output                 | DAC <sub>FS</sub>   | Low Range              | _     | V <sub>IO</sub> /8   | _                          | V     |

|                                                 |                     | High Range             | _     | V <sub>IO</sub>      |                            | V     |

| Reference DAC Step Size                         | DAC <sub>LSB</sub>  | Low Range (48 steps)   | _     | V <sub>IO</sub> /384 | _                          | V     |

|                                                 |                     | High Range (64 steps)  | _     | V <sub>IO</sub> /64  | _                          | V     |

| LC Oscillator Period                            | T <sub>LCOSC</sub>  |                        | _     | 25                   | _                          | ns    |

| LC Bias Output Impedance                        | R <sub>LCBIAS</sub> | 10 µA Load             | —     | 1                    | —                          | kΩ    |

| LC Bias Drive Strength                          | I <sub>LCBIAS</sub> |                        | _     | _                    | 2                          | mA    |

| Pull-Up Resistor Tolerance                      | R <sub>TOL</sub>    | PUVAL[4:2] = 0 to 6    | -15   | _                    | 15                         | %     |

|                                                 |                     | PUVAL[4:2] = 7         | -10   |                      | 10                         | %     |

## Table 3.16. Port I/O

| Parameter                                                    | Symbol          | Test Condition                                 | Min                     | Тур  | Max | Unit |

|--------------------------------------------------------------|-----------------|------------------------------------------------|-------------------------|------|-----|------|

| Output High Voltage (PB0, PB1,                               | V <sub>OH</sub> | Low Drive, I <sub>OH</sub> = -1 mA             | V <sub>IO</sub> – 0.7   |      |     | V    |

| PB3, or PB4)                                                 |                 | Low Drive, $I_{OH} = -10 \ \mu A$              | V <sub>IO</sub> – 0.1   | _    |     | V    |

|                                                              |                 | High Drive, I <sub>OH</sub> = –3 mA            | V <sub>IO</sub> – 0.7   | _    |     | V    |

|                                                              |                 | High Drive, $I_{OH} = -10 \ \mu A$             | V <sub>IO</sub> – 0.1   | _    | _   | V    |

| Output High Voltage (PB2)                                    | V <sub>OH</sub> | Low Drive, $I_{OH} = -1 \text{ mA}$            | $V_{IORF} - 0.7$        | _    | _   | V    |

|                                                              |                 | Low Drive, $I_{OH} = -10 \ \mu A$              | $V_{IORF} - 0.1$        | _    | _   | V    |

|                                                              |                 | High Drive, I <sub>OH</sub> = –3 mA            | $V_{IORF} - 0.7$        | _    | —   | V    |

|                                                              |                 | High Drive, $I_{OH} = -10 \ \mu A$             | V <sub>IORF</sub> - 0.1 | _    | —   | V    |

| Output Low Voltage (any Port I/O                             | V <sub>OL</sub> | Low Drive, I <sub>OL</sub> = 1.4 mA            | —                       | _    | 0.6 | V    |

| pin or RESET <sup>1</sup> )                                  |                 | Low Drive, $I_{OL} = 10 \ \mu A$               | —                       | _    | 0.1 | V    |

|                                                              |                 | High Drive, I <sub>OL</sub> = 8.5 mA           | —                       | _    | 0.6 | V    |

|                                                              |                 | High Drive, I <sub>OL</sub> = 10 μA            | —                       | _    | 0.1 | V    |

| Input High Vo <u>ltage (P</u> B0, PB1,<br>PB3, PB4 or RESET) | V <sub>IH</sub> |                                                | V <sub>IO</sub> – 0.6   |      |     | V    |

| Input High Voltage (PB2)                                     | V <sub>IH</sub> |                                                | V <sub>IORF</sub> - 0.6 | _    |     | V    |

| Input Low Voltage any Port I/O pin or RESET)                 | V <sub>IL</sub> |                                                | —                       |      | 0.6 | V    |

| Weak Pull-Up Current <sup>2</sup> (per pin)                  | I <sub>PU</sub> | V <sub>IO</sub> or V <sub>IORF</sub> = 1.8     | -6                      | -3.5 | -2  | μA   |

|                                                              |                 | V <sub>IO</sub> or V <sub>IORF</sub> = 3.8     | -32                     | -20  | -10 | μA   |

| Input Leakage<br>(Pullups off or Analog)                     | I <sub>LK</sub> | $0 \le V_{IN} \le V_{IO} \text{ or } V_{IORF}$ | -1                      |      | 1   | μA   |

Notes:

Specifications for RESET V<sub>OL</sub> adhere to the low drive setting.

On the SiM3L1x6 and SiM3L1x4 devices, the SWV pin will have double the weak pull-up current specified whenever the device is held in reset.

## 4.1. Power

The SiM3L1xx devices include a dc-dc buck converter that can take an input from 1.8–3.8 V and create an output from 1.25–3.8 V. In addition, SiM3L1xx devices include three low dropout regulators as part of the LDO0 module: one LDO powers the analog subsystems, one LDO powers the flash and SRAM memory at 1.8 V, and one LDO powers the digital and core circuitry. Each of these regulators can be independently powered from the dc-dc converter or directly from the battery voltage, and their outputs are adjustable to conserve system power. SiM3L1xx devices also include a low power charge pump in the PMU module for use in low power modes (PM8) to further reduce the power consumption of the device.

Figure 4.2 shows the power system configuration of these devices.

Figure 4.2. SiM3L1xx Power

#### 4.1.1. DC-DC Buck Converter (DCDC0)

SiM3L1xx devices include an on-chip step-down dc-dc converter to efficiently utilize the energy stored in the battery, thus extending the operational life time. The dc-dc converter is a switching buck converter with a programmable output voltage that should be at least 0.45 V lower than the input battery voltage; if this criteria is not met and the converter can no longer operate, the output of the dc-dc converter automatically connects to the battery. The dc-dc converter can supply up to 100 mA and can be used to power the MCU and/or external devices in the system.

The dc-dc converter has a built in voltage reference and oscillator and will automatically limit or turn off the switching activity in case the peak inductor current rises beyond a safe limit or the output voltage rises above the programmed target value. This allows the dc-dc converter output to be safely overdriven by a secondary power source (when available) in order to preserve battery life. When enabled, the dc-dc converter can source current into the output capacitor, but cannot sink current.

The dc-dc converter includes the following features:

- Efficiently utilizes the energy stored in a battery, extending its operational lifetime.

- Input range: 1.8 to 3.8 V.

- Output range: 1.25 to 3.8 V in 50 mV (1.25–1.8 V) or 100 mV (1.8–3.8 V) steps.

- Supplies up to 100 mA.

- Includes a voltage reference and an oscillator.

#### 4.1.5.6. Power Mode Summary

The power modes described above are summarized in Table 4.1. Table 3.2 and Table 3.3 provide more information on the power consumption and wake up times for each mode.

| Mode               | Description                                                                                                                                                                                                                                                                                                         | Notes                                                                                                                                                                                                                                          |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Normal             | <ul><li>Core operating at full speed</li><li>Code executing from flash</li></ul>                                                                                                                                                                                                                                    | <ul> <li>Full device operation</li> </ul>                                                                                                                                                                                                      |

| Power Mode 1 (PM1) | <ul> <li>Core operating at full speed</li> <li>Code executing from RAM</li> </ul>                                                                                                                                                                                                                                   | <ul> <li>Full device operation</li> <li>Higher CPU bandwidth than PM0 (RAM can operate with zero wait states at any frequency)</li> </ul>                                                                                                      |

| Power Mode 2 (PM2) | <ul> <li>Core halted</li> <li>AHB, APB and all peripherals operational at full speed</li> </ul>                                                                                                                                                                                                                     | <ul> <li>Fast wakeup from any interrupt source</li> </ul>                                                                                                                                                                                      |

| Power Mode 3 (PM3) | <ul> <li>All clocks to core and peripherals<br/>stopped</li> <li>Faster wake enabled by keeping<br/>LFOSC0 or RTC0TCLK active</li> </ul>                                                                                                                                                                            | <ul> <li>Wake on any wake source or reset<br/>source defined in the PMU</li> </ul>                                                                                                                                                             |

| Power Mode 4 (PM4) | <ul> <li>Core operating at low speed</li> <li>Code executing from flash</li> </ul>                                                                                                                                                                                                                                  | <ul> <li>Same capabilities as PM0, operating at lower speed</li> <li>Lower clock speed enables lower LDO output settings to save power</li> </ul>                                                                                              |

| Power Mode 5 (PM5) | <ul> <li>Core operating at low speed</li> <li>Code executing from RAM</li> </ul>                                                                                                                                                                                                                                    | <ul> <li>Same capabilities as PM1, operating at lower speed</li> <li>Lower clock speed enables lower LDO output settings to save power</li> </ul>                                                                                              |

| Power Mode 6 (PM6) | <ul> <li>Core halted</li> <li>AHB, APB and all peripherals operational at low speed</li> </ul>                                                                                                                                                                                                                      | <ul> <li>Same capabilities as PM2, operating at lower speed</li> <li>Lower clock speed enables lower LDO output settings to save power</li> <li>When running from LFOSC0, power is similar to PM3, but the device wakes much faster</li> </ul> |

| Power Mode 8 (PM8) | <ul> <li>Low power sleep</li> <li>LDO regulators are disabled and all active circuitry operates directly from VBAT</li> <li>The following functions are available:<br/>ACCTR0, RTC0, UART0 running from RTC0TCLK, LPTIMER0, port match, and the LCD controller</li> <li>Register and RAM state retention</li> </ul> | <ul> <li>Lowest power consumption</li> <li>Wake on any wake source or reset<br/>source defined in the PMU</li> </ul>                                                                                                                           |

#### Table 4.1. SiM3L1xx Power Modes

## 4.2. I/O

#### 4.2.1. General Features

The SiM3L1xx ports have the following features:

- 5 V tolerant.

- Push-pull or open-drain output modes to the VIO or VIORF voltage level.

- Analog or digital modes.

- Option for high or low output drive strength.

- Port Match allows the device to recognize a change on a port pin value.

- Internal pull-up resistors are enabled or disabled on a port-by-port basis.

- Two external interrupts with up to 16 inputs each provide monitoring capability for external signals.

- Internal Pulse Generator Timer (PB0 only) to generate simple square waves and pulses.

#### 4.2.2. Crossbar

The SiM3L1xx devices have one crossbar with the following features:

- Flexible peripheral assignment to port pins.

- Pins can be individually skipped to move peripherals as needed for design or layout considerations.

The crossbar has a fixed priority for each I/O function and assigns these functions to the port pins. When a digital resource is selected, the least-significant unassigned port pin is assigned to that resource. If a port pin is assigned, the crossbar skips that pin when assigning the next selected resource. Additionally, the crossbar will skip port pins whose associated bits in the PBSKIPEN registers are set. This provides flexibility when designing a system: pins involved with sensitive analog measurements can be moved away from digital I/O, and peripherals can be moved around the chip as needed to ease layout constraints.

## 4.5. Data Peripherals

#### 4.5.1. 10-Channel DMA Controller

The DMA facilitates autonomous peripheral operation, allowing the core to finish tasks more quickly without spending time polling or waiting for peripherals to interrupt. This helps reduce the overall power consumption of the system, as the device can spend more time in low-power modes.

The DMA controller has the following features:

- Utilizes ARM PrimeCell uDMA architecture.

- Implements 10 channels.

- DMA crossbar supports DTM0, DTM1, DTM2, SARADC0, IDAC0, I2C0, SPI0, SPI1, USART0, AES0, ENCDEC0, EPCA0, external pin triggers, and timers.

- Supports primary, alternate, and scatter-gather data structures to implement various types of transfers.

- Access allowed to all AHB and APB memory space.