# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                             |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                 |

| Core Size                  | 32-Bit Single-Core                                              |

| Speed                      | 50MHz                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, SmartCard, SPI, UART/USART              |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, POR, PWM, WDT                 |

| Number of I/O              | 51                                                              |

| Program Memory Size        | 64KB (64K × 8)                                                  |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | ·                                                               |

| RAM Size                   | 16K x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.8V                                                     |

| Data Converters            | A/D 23x10/12b; D/A 1x10b                                        |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 64-VFQFN Exposed Pad                                            |

| Supplier Device Package    | 64-QFN (9x9)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/sim3l146-c-gm |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Table 3.2. Power Consumption

| Parameter                                                                                                        | Symbol           | Test Condition                                                                        | Min | Тур  | Max  | Unit |

|------------------------------------------------------------------------------------------------------------------|------------------|---------------------------------------------------------------------------------------|-----|------|------|------|

| Digital Core Supply Current                                                                                      | • •              |                                                                                       |     | 1    | Ļ    |      |

| Normal Mode <sup>1,2,3,4</sup> —Full speed<br>with code executing flash,                                         | I <sub>BAT</sub> | F <sub>AHB</sub> = 49 MHz,<br>F <sub>APB</sub> = 24.5 MHz                             | —   | 17.5 | 18.9 | mA   |

| peripheral clocks ON                                                                                             |                  | F <sub>AHB</sub> = 20 MHz,<br>F <sub>APB</sub> = 10 MHz                               | —   | 6.7  | 7.2  | mA   |

|                                                                                                                  |                  | F <sub>AHB</sub> = 2.5 MHz,<br>F <sub>APB</sub> = 1.25 MHz                            | —   | 1.15 | 1.4  | mA   |

| Normal Mode <sup>1,2,3,4</sup> —Full speed<br>with code executing from flash,<br>peripheral clocks OFF           | I <sub>BAT</sub> | F <sub>AHB</sub> = 49 MHz,<br>F <sub>APB</sub> = 24.5 MHz                             | —   | 13.3 | 14.5 | mA   |

|                                                                                                                  |                  | F <sub>AHB</sub> = 20 MHz,<br>F <sub>APB</sub> = 10 MHz                               | —   | 5.4  | 5.9  | mA   |

|                                                                                                                  |                  | F <sub>AHB</sub> = 2.5 MHz,<br>F <sub>APB</sub> = 1.25 MHz                            | _   | 980  | 1.2  | μA   |

| Normal Mode <sup>1,2,3,4</sup> —Full speed<br>with code executing from flash,<br>LDOs powered by dc-dc at 1.9 V, | I <sub>BAT</sub> | F <sub>AHB</sub> = 49 MHz,<br>F <sub>APB</sub> = 24.5 MHz<br>V <sub>BAT</sub> = 3.3 V |     | 9.7  |      | mA   |

| peripheral clocks OFF                                                                                            |                  | F <sub>AHB</sub> = 49 MHz,<br>F <sub>APB</sub> = 24.5 MHz<br>V <sub>BAT</sub> = 3.8 V |     | 8.65 |      | mA   |

|                                                                                                                  |                  | F <sub>AHB</sub> = 20 MHz,<br>F <sub>APB</sub> = 10 MHz<br>V <sub>BAT</sub> = 3.3 V   | _   | 4.15 | _    | mA   |

|                                                                                                                  |                  | F <sub>AHB</sub> = 20 MHz,<br>F <sub>APB</sub> = 10 MHz<br>V <sub>BAT</sub> = 3.8 V   | _   | 3.9  | _    | mA   |

#### Notes:

1. Currents are additive. For example, where I<sub>BAT</sub> is specified and the mode is not mutually exclusive, enabling the functions increases supply current by the specified amount.

2. Includes all peripherals that cannot have clocks gated in the Clock Control module.

- 3. Includes LDO and PLL0OSC (>20 MHz) or LPOSC0 (<20 MHz) supply current.

- **4.** Internal Digital and Memory LDOs scaled to optimal output voltage.

- 5. Flash AHB clock turned off.

- 6. Running from internal LFO, Includes LFO supply current.

- 7. LCD0 current does not include switching currents for external load.

- 8. IDAC output current not included.

- 9. Does not include LC tank circuit.

- Does not include digital drive current or pullup current for active port I/O. Unloaded I<sub>VIO</sub> is included in all I<sub>BAT</sub> PM8 production test measurements.

#### Table 3.2. Power Consumption (Continued)

| Parameter                                                                                                       | Symbol           | Test Condition                                                                        | Min | Тур  | Max  | Unit |

|-----------------------------------------------------------------------------------------------------------------|------------------|---------------------------------------------------------------------------------------|-----|------|------|------|

| Power Mode 1 <sup>1,2,3,4</sup> —Full speed<br>with code executing from RAM,                                    | I <sub>BAT</sub> | F <sub>AHB</sub> = 49 MHz,<br>F <sub>APB</sub> = 24.5 MHz                             | —   | 13.4 | 16.6 | mA   |

| peripheral clocks ON                                                                                            |                  | F <sub>AHB</sub> = 20 MHz,<br>F <sub>APB</sub> = 10 MHz                               | —   | 4.7  |      | mA   |

|                                                                                                                 |                  | F <sub>AHB</sub> = 2.5 MHz,<br>F <sub>APB</sub> = 1.25 MHz                            | _   | 810  |      | μA   |

| Power Mode 1 <sup>1,2,3,4</sup> —Full speed<br>with code executing from RAM,                                    | I <sub>BAT</sub> | F <sub>AHB</sub> = 49 MHz,<br>F <sub>APB</sub> = 24.5 MHz                             |     | 9.4  | 12.5 | mA   |

| peripheral clocks OFF                                                                                           |                  | F <sub>AHB</sub> = 20 MHz,<br>F <sub>APB</sub> = 10 MHz                               | _   | 3.3  | _    | mA   |

|                                                                                                                 |                  | F <sub>AHB</sub> = 2.5 MHz,<br>F <sub>APB</sub> = 1.25 MHz                            | —   | 630  | _    | μA   |

| Power Mode 1 <sup>1,2,3,4</sup> —Full speed<br>with code executing from RAM,<br>LDOs powered by dc-dc at 1.9 V, | I <sub>BAT</sub> | F <sub>AHB</sub> = 49 MHz,<br>F <sub>APB</sub> = 24.5 MHz<br>V <sub>BAT</sub> = 3.3 V | _   | 7.05 |      | mA   |

| peripheral clocks OFF                                                                                           |                  | F <sub>AHB</sub> = 49 MHz,<br>F <sub>APB</sub> = 24.5 MHz<br>V <sub>BAT</sub> = 3.8 V |     | 6.3  | _    | mA   |

|                                                                                                                 |                  | F <sub>AHB</sub> = 20 MHz,<br>F <sub>APB</sub> = 10 MHz<br>V <sub>BAT</sub> = 3.3 V   | _   | 2.75 | —    | mA   |

|                                                                                                                 |                  | F <sub>AHB</sub> = 20 MHz,<br>F <sub>APB</sub> = 10 MHz<br>V <sub>BAT</sub> = 3.8 V   | _   | 2.6  | —    | mA   |

| Power Mode 2 <sup>1,2,3,4,5</sup> —Core halted with peripheral clocks ON                                        | I <sub>BAT</sub> | F <sub>AHB</sub> = 49 MHz,<br>F <sub>APB</sub> = 24.5 MHz                             | —   | 7.6  | 11.3 | mA   |

|                                                                                                                 |                  | F <sub>AHB</sub> = 20 MHz,<br>F <sub>APB</sub> = 10 MHz                               | _   | 2.75 |      | mA   |

|                                                                                                                 |                  | F <sub>AHB</sub> = 2.5 MHz,<br>F <sub>APB</sub> = 1.25 MHz                            | _   | 575  | _    | μA   |

Notes:

- 1. Currents are additive. For example, where I<sub>BAT</sub> is specified and the mode is not mutually exclusive, enabling the functions increases supply current by the specified amount.

- 2. Includes all peripherals that cannot have clocks gated in the Clock Control module.

- 3. Includes LDO and PLL0OSC (>20 MHz) or LPOSC0 (<20 MHz) supply current.

- 4. Internal Digital and Memory LDOs scaled to optimal output voltage.

- 5. Flash AHB clock turned off.

- 6. Running from internal LFO, Includes LFO supply current.

- 7. LCD0 current does not include switching currents for external load.

- **8.** IDAC output current not included.

- 9. Does not include LC tank circuit.

- Does not include digital drive current or pullup current for active port I/O. Unloaded I<sub>VIO</sub> is included in all I<sub>BAT</sub> PM8 production test measurements.

#### Table 3.2. Power Consumption (Continued)

| Parameter                      | Symbol               | Test Condition                                    | Min | Тур | Max | Unit |

|--------------------------------|----------------------|---------------------------------------------------|-----|-----|-----|------|

| SARADC0                        | ISARADC              | Sampling at 1 Msps, Internal<br>VREF used         |     | 1.2 | 1.6 | mA   |

|                                |                      | Sampling at 250 ksps, lowest power mode settings. |     | 390 | 540 | μA   |

| Temperature Sensor             | I <sub>TSENSE</sub>  |                                                   |     | 75  | 110 | μA   |

| Internal SAR Reference         | I <sub>REFFS</sub>   | Normal Power Mode                                 |     | 680 | _   | μA   |

|                                |                      | Normal Power Mode                                 |     | 160 | _   | μA   |

| VREF0                          | I <sub>REFP</sub>    |                                                   |     | 80  |     | μA   |

| Comparator 0 (CMP0),           | I <sub>CMP</sub>     | CMPMD = 11                                        |     | 0.5 | 2   | μA   |

| Comparator 1 (CMP1)            |                      | CMPMD = 10                                        |     | 3   | 8   | μA   |

|                                |                      | CMPMD = 01                                        |     | 10  | 16  | μA   |

|                                |                      | CMPMD = 00                                        |     | 25  | 42  | μA   |

| IDAC0 <sup>8</sup>             | I <sub>IDAC</sub>    |                                                   | _   | 70  | 100 | μA   |

| Voltage Supply Monitor (VMON0) | I <sub>VMON</sub>    |                                                   |     | 10  | 22  | μA   |

| Flash Current on VBAT          |                      |                                                   | 1   | 1   |     |      |

| Write Operation                | I <sub>FLASH-W</sub> |                                                   |     |     | 8   | mA   |

| Erase Operation                | I <sub>FLASH-E</sub> |                                                   |     | _   | 15  | mA   |

| Notes:                         | 1                    |                                                   | 1   | 1   | 1   | 1    |

1. Currents are additive. For example, where  $I_{BAT}$  is specified and the mode is not mutually exclusive, enabling the functions increases supply current by the specified amount.

- 2. Includes all peripherals that cannot have clocks gated in the Clock Control module.

- 3. Includes LDO and PLL0OSC (>20 MHz) or LPOSC0 (<20 MHz) supply current.

- 4. Internal Digital and Memory LDOs scaled to optimal output voltage.

- 5. Flash AHB clock turned off.

- 6. Running from internal LFO, Includes LFO supply current.

- 7. LCD0 current does not include switching currents for external load.

- 8. IDAC output current not included.

- 9. Does not include LC tank circuit.

- 10. Does not include digital drive current or pullup current for active port I/O. Unloaded IVIO is included in all IBAT PM8 production test measurements.

## Table 3.9. SAR ADC

| Parameter                    | Parameter Symbol Test Condition |                                                                 |     |      |                                          |      |

|------------------------------|---------------------------------|-----------------------------------------------------------------|-----|------|------------------------------------------|------|

| Resolution                   | N <sub>bits</sub>               | 12 Bit Mode                                                     |     | 12   |                                          | Bits |

|                              |                                 | 10 Bit Mode                                                     |     | 10   |                                          | Bits |

| Supply Voltage Requirements  | V <sub>ADC</sub>                | High Speed Mode                                                 | 2.2 |      | 3.8                                      | V    |

| (VBAT)                       |                                 | Low Power Mode                                                  | 1.8 |      | 3.8                                      | V    |

| Throughput Rate              | f <sub>S</sub>                  | 12 Bit Mode                                                     |     |      | 250                                      | ksps |

| (High Speed Mode)            |                                 | 10 Bit Mode                                                     |     |      | 1                                        | Msps |

| Throughput Rate              | f <sub>S</sub>                  | 12 Bit Mode                                                     |     |      | 62.5                                     | ksps |

| (Low Power Mode)             |                                 | 10 Bit Mode                                                     |     |      | 250                                      | ksps |

| Tracking Time                | t <sub>TRK</sub>                | High Speed Mode                                                 | 230 |      |                                          | ns   |

|                              |                                 | Low Power Mode                                                  | 450 |      |                                          | ns   |

| SAR Clock Frequency          | f <sub>SAR</sub>                | High Speed Mode                                                 |     |      | 16.24                                    | MHz  |

|                              |                                 | Low Power Mode                                                  |     |      | 4                                        | MHz  |

| Conversion Time              | t <sub>CNV</sub>                | 10-Bit Conversion,<br>SAR Clock = 16 MHz,<br>APB Clock = 40 MHz |     | ns   |                                          |      |

| Sample/Hold Capacitor        | C <sub>SAR</sub>                | Gain = 1                                                        | _   | 5    | _                                        | pF   |

|                              |                                 | Gain = 0.5                                                      |     | 2.5  |                                          | pF   |

| Input Pin Capacitance        | C <sub>IN</sub>                 | High Quality Inputs                                             |     | 18   | —                                        | pF   |

|                              |                                 | Normal Inputs                                                   |     | 20   | —                                        | pF   |

| Input Mux Impedance          | R <sub>MUX</sub>                | High Quality Inputs                                             |     | 300  | —                                        | Ω    |

|                              |                                 | Normal Inputs                                                   |     | 550  | _                                        | Ω    |

| Voltage Reference Range      | V <sub>REF</sub>                |                                                                 | 1   |      | V <sub>BAT</sub>                         | V    |

| Input Voltage Range*         | V <sub>IN</sub>                 | Gain = 1                                                        | 0   |      | V <sub>REF</sub>                         | V    |

|                              |                                 | Gain = 0.5                                                      | 0   | _    | $2 \mathrm{x} \mathrm{V}_{\mathrm{REF}}$ | V    |

| Power Supply Rejection Ratio | PSRR <sub>ADC</sub>             |                                                                 | _   | 70   | —                                        | dB   |

| DC Performance               |                                 |                                                                 |     |      |                                          |      |

| Integral Nonlinearity        | INL                             | 12 Bit Mode                                                     | —   | ±1   | ±1.9                                     | LSB  |

|                              |                                 | 10 Bit Mode                                                     |     | ±0.2 | ±0.5                                     | LSB  |

| Differential Nonlinearity    | DNL                             | 12 Bit Mode                                                     | -1  | ±0.7 | 1.8                                      | LSB  |

| (Guaranteed Monotonic)       |                                 | 10 Bit Mode                                                     |     | ±0.2 | ±0.5                                     | LSB  |

| Offset Error (using VREFGND) | E <sub>OFF</sub>                | 12 Bit Mode, VREF = 2.4 V                                       | -2  | 0    | 2                                        | LSB  |

|                              |                                 | 10 Bit Mode, VREF = 2.4 V                                       | -1  | 0    | 1                                        | LSB  |

Table 3.11. ACCTR (Advanced Capture Counter)

| Parameter                         | Symbol             | Test Condition       | Min | Тур   | Max | Unit |

|-----------------------------------|--------------------|----------------------|-----|-------|-----|------|

| LC Comparator Response Time,      | t <sub>RESP0</sub> | +100 mV Differential |     | 100   | _   | ns   |

| CMPMD = 11<br>(Highest Speed)     |                    | –100 mV Differential |     | 150   |     | ns   |

| LC Comparator Response Time,      | t <sub>RESP3</sub> | +100 mV Differential | —   | 1.4   | _   | μs   |

| CMPMD = 00<br>(Lowest Power)      |                    | -100 mV Differential |     | 3.5   |     | μs   |

| LC Comparator Positive Hysteresis | HYS <sub>CP+</sub> | CMPHYP = 00          |     | 0.37  |     | mV   |

| Mode 0 (CPMD = 11)                |                    | CMPHYP = 01          | —   | 7.9   | _   | mV   |

|                                   |                    | CMPHYP = 10          |     | 16.7  | _   | mV   |

|                                   |                    | CMPHYP = 11          |     | 32.8  | —   | mV   |

| LC Comparator Negative Hysteresis | HYS <sub>CP-</sub> | CMPHYN = 00          |     | 0.37  |     | mV   |

| Mode 0 (CPMD = 11)                |                    | CMPHYN = 01          |     | -7.9  | _   | mV   |

|                                   |                    | CMPHYN = 10          |     | -16.1 | —   | mV   |

|                                   |                    | CMPHYN = 11          |     | -32.7 | _   | mV   |

| LC Comparator Positive Hysteresis | HYS <sub>CP+</sub> | CMPHYP = 00          |     | 0.47  | _   | mV   |

| Mode 1 (CPMD = 10)                |                    | CMPHYP = 01          |     | 5.85  | _   | mV   |

|                                   |                    | CMPHYP = 10          |     | 12    | _   | mV   |

|                                   |                    | CMPHYP = 11          | —   | 24.4  |     | mV   |

| LC Comparator Negative Hysteresis | HYS <sub>CP-</sub> | CMPHYN = 00          |     | 0.47  | —   | mV   |

| Mode 1 (CPMD = 10)                |                    | CMPHYN = 01          |     | -6.0  |     | mV   |

|                                   |                    | CMPHYN = 10          |     | -12.1 |     | mV   |

|                                   |                    | CMPHYN = 11          |     | -24.6 |     | mV   |

| LC Comparator Positive Hysteresis | HYS <sub>CP+</sub> | CMPHYP = 00          |     | 0.66  |     | mV   |

| Mode 2 (CPMD = 01)                |                    | CMPHYP = 01          |     | 4.55  |     | mV   |

|                                   |                    | CMPHYP = 10          |     | 9.3   | _   | mV   |

|                                   |                    | CMPHYP = 11          |     | 19    |     | mV   |

| LC Comparator Negative Hysteresis | HYS <sub>CP-</sub> | CMPHYN = 00          |     | 0.6   | _   | mV   |

| Mode 2 (CPMD = 01)                |                    | CMPHYN = 01          |     | -4.5  | —   | mV   |

|                                   |                    | CMPHYN = 10          |     | -9.5  |     | mV   |

|                                   |                    | CMPHYN = 11          |     | -19   |     | mV   |

# Table 3.11. ACCTR (Advanced Capture Counter) (Continued)

| Parameter                                       | Symbol              | Test Condition         | Min   | Тур                  | Max                        | Unit  |

|-------------------------------------------------|---------------------|------------------------|-------|----------------------|----------------------------|-------|

| LC Comparator Positive Hysteresis               | HYS <sub>CP+</sub>  | CMPHYP = 00            | —     | 1.37                 | —                          | mV    |

| Mode 3 (CPMD = 00)                              |                     | CMPHYP = 01            | _     | 3.8                  | _                          | mV    |

|                                                 |                     | CMPHYP = 10            | _     | 7.8                  | _                          | mV    |

|                                                 |                     | CMPHYP = 11            | _     | 15.6                 | _                          | mV    |

| LC Comparator Negative Hysteresis               | HYS <sub>CP-</sub>  | CMPHYN = 00            | _     | 1.37                 |                            | mV    |

| Mode 3 (CPMD = 00)                              |                     | CMPHYN = 01            | _     | -3.9                 |                            | mV    |

|                                                 |                     | CMPHYN = 10            | -     | -7.9                 | _                          | mV    |

|                                                 |                     | CMPHYN = 11            | _     | -16                  |                            | mV    |

| LC Comparator Input Range<br>(ACCTR0_LCIN pin)  | V <sub>IN</sub>     |                        | -0.25 | _                    | V <sub>BAT</sub> +<br>0.25 | V     |

| LC Comparator Common-Mode<br>Rejection Ratio    | CMRR <sub>CP</sub>  |                        | _     | 75                   | _                          | dB    |

| LC Comparator Power Supply Rejec-<br>tion Ratio | PSRR <sub>CP</sub>  |                        | _     | 72                   | —                          | dB    |

| LC Comparator Input Offset Voltage              | V <sub>OFF</sub>    | T <sub>A</sub> = 25 °C | -10   | 0                    | 10                         | mV    |

| LC Comparator Input Offset Tempco               | TC <sub>OFF</sub>   |                        | _     | 3.5                  | _                          | µV/°C |

| Reference DAC Offset Error                      | DAC <sub>EOFF</sub> |                        | -1    | —                    | 1                          | LSB   |

| Reference DAC Full Scale Output                 | DAC <sub>FS</sub>   | Low Range              | _     | V <sub>IO</sub> /8   | _                          | V     |

|                                                 |                     | High Range             | _     | V <sub>IO</sub>      |                            | V     |

| Reference DAC Step Size                         | DAC <sub>LSB</sub>  | Low Range (48 steps)   | _     | V <sub>IO</sub> /384 | _                          | V     |

|                                                 |                     | High Range (64 steps)  | _     | V <sub>IO</sub> /64  | _                          | V     |

| LC Oscillator Period                            | T <sub>LCOSC</sub>  |                        | _     | 25                   | _                          | ns    |

| LC Bias Output Impedance                        | R <sub>LCBIAS</sub> | 10 µA Load             | —     | 1                    | —                          | kΩ    |

| LC Bias Drive Strength                          | I <sub>LCBIAS</sub> |                        | _     | _                    | 2                          | mA    |

| Pull-Up Resistor Tolerance                      | R <sub>TOL</sub>    | PUVAL[4:2] = 0 to 6    | -15   | _                    | 15                         | %     |

|                                                 |                     | PUVAL[4:2] = 7         | -10   |                      | 10                         | %     |

# 3.3. Absolute Maximum Ratings

Stresses above those listed under Table 3.18 may cause permanent damage to the device. This is a stress rating only and functional operation of the devices at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Parameter                                             | Symbol            | Test Condition                                 | Min                    | Max                    | Unit |

|-------------------------------------------------------|-------------------|------------------------------------------------|------------------------|------------------------|------|

| Ambient Temperature Under Bias                        | T <sub>BIAS</sub> |                                                | -55                    | 125                    | °C   |

| Storage Temperature                                   | T <sub>STG</sub>  |                                                | -65                    | 150                    | °C   |

| Voltage on VBAT/VBATDC                                | V <sub>BAT</sub>  |                                                | V <sub>SS</sub> 0.3    | 4.2                    | V    |

| Voltage on VDC                                        | V <sub>DC</sub>   |                                                | V <sub>SSDC</sub> -0.3 | 4.2                    | V    |

| Voltage on VDRV                                       | V <sub>DRV</sub>  |                                                | V <sub>SS</sub> -0.3   | 4.2                    | V    |

| Voltage on VIO                                        | V <sub>IO</sub>   |                                                | V <sub>SS</sub> -0.3   | 4.2                    | V    |

| Voltage on VIORF                                      | V <sub>IORF</sub> |                                                | V <sub>SS</sub> -0.3   | 4.2                    | V    |

| Voltage on VLCD                                       | V <sub>LCD</sub>  |                                                | V <sub>SS</sub> -0.3   | 4.2                    | V    |

| Voltage on I/O (PB0, PB1, PB3, PB4) or                | V <sub>IN</sub>   | V <sub>IO</sub> ≥ 3.3 V                        | V <sub>SS</sub> -0.3   | 5.8                    | V    |

| RESET <sup>1</sup>                                    | -                 | V <sub>IO</sub> < 3.3 V                        | V <sub>SS</sub> 0.3    | V <sub>IO</sub> +2.5   | V    |

| Voltage on PB2 I/O Pins <sup>1</sup>                  | V <sub>IN</sub>   | V <sub>IORF</sub> ≥ 3.3 V                      | V <sub>SS</sub> -0.3   | 5.8                    | V    |

|                                                       | -                 | V <sub>IORF</sub> < 3.3 V                      | V <sub>SS</sub> -0.3   | V <sub>IORF</sub> +2.5 | V    |

| Total Current Sunk into Supply Pins                   | I <sub>SUPP</sub> | VBAT/VBATDC, VIO,<br>VIORF, VDRV, VDC,<br>VLCD | _                      | 400                    | mA   |

| Total Current Sourced out of Ground Pins <sup>2</sup> | I <sub>VSS</sub>  | V <sub>SS,</sub> V <sub>SSDC</sub>             | 400                    | —                      | mA   |

| Current Sourced or Sunk by any I/O Pin                | I <sub>PIO</sub>  | All I/O and RESET                              | -100                   | 100                    | mA   |

| Power Dissipation at T <sub>A</sub> = 85 °C           | PD                | TQFP-80 Packages                               | _                      | 500                    | mW   |

|                                                       |                   | QFN-64 Packages                                | —                      | 800                    | mW   |

|                                                       |                   | TQFP-64 Packages                               | _                      | 650                    | mW   |

|                                                       |                   | QFN-40 Packages                                | _                      | 650                    | mW   |

Notes:

1. Exceeding the minimum  $V_{\text{IO}}$  voltage may cause current to flow through adjacent device pins.

2. VSS and VSSDC provide separate return current paths for device supplies, but are not isolated. They must always be connected to the same potential on board.

#### 4.5.4. 16/32-bit Enhanced CRC (ECRC0)

The ECRC module is designed to provide hardware calculations for flash memory verification and communications protocols. In addition to calculating a result from direct writes from firmware, the ECRC module can automatically snoop the APB bus and calculate a result from data written to or read from a particular peripheral. This allows for an automatic CRC result without directly feeding data through the ECRC module.

The supported 32-bit polynomial is 0x04C11DB7 (IEEE 802.3). The 16-bit polynomial is fully programmable.

The ECRC module includes the following features:

- Support for a programmable 16-bit polynomial and one fixed 32-bit polynomial.

- Byte-level bit reversal for the CRC input.

- Byte-order reorientation of words for the CRC input.

- Word or half-word bit reversal of the CRC result.

- Ability to configure and seed an operation in a single register write.

- Support for single-cycle parallel (unrolled) CRC computation for 32-, 16-, or 8-bit blocks.

- Capability to CRC 32 bits of data per peripheral bus (APB) clock.

- Automatic APB bus snooping.

- Support for DMA writes using firmware request mode.

#### 4.5.5. Encoder / Decoder (ENCDEC0)

The encoder / decoder module supports Manchester and Three-out-of-Six encoding and decoding from either firmware or DMA operations.

This module has the following features:

- Supports Manchester and Three-out-of-Six encoding and decoding.

- Automatic flag clearing when writing the input or reading the output data registers.

- Writing to the input data register automatically initiates an encode or decode operation.

- Optional output in one's complement format.

- Hardware error detection for invalid input data during decode operations, which helps reduce power consumption and packet turn-around time.

- Flexible byte swapping on the input or output data.

## 4.7. Communications Peripherals

### 4.7.1. USART (USART0)

The USART uses two signals (TX and RX) to communicate serially with an external device. In addition to these signals, the USART module can optionally use a clock (UCLK) or hardware handshaking (RTS and CTS).

The USART module provides the following features:

- Independent transmitter and receiver configurations with separate 16-bit baud rate generators.

- Synchronous or asynchronous transmissions and receptions.

- Clock master or slave operation with programmable polarity and edge controls.

- Up to 5 Mbaud (synchronous or asynchronous, TX or RX, and master or slave) or 1 Mbaud Smartcard (TX or RX).

- Individual enables for generated clocks during start, stop, and idle states.

- Internal transmit and receive FIFOs with flush capability and support for byte, half-word, and word reads and writes.

- Data bit lengths from 5 to 9 bits.

- Programmable inter-packet transmit delays.

- Auto-baud detection with support for the LIN SYNC byte.

- Automatic parity generation (with enable).

- Automatic start and stop generation (with separate enables).

- Transmit and receive hardware flow-control.

- Independent inversion correction for TX, RX, RTS, and CTS signals.

- IrDA modulation and demodulation with programmable pulse widths.

- Smartcard ACK/NACK support.

- Parity error, frame error, overrun, and underrun detection.

- Multi-master and half-duplex support.

- Multiple loop-back modes supported.

- Multi-processor communications support.

#### 4.7.2. UART (UART0)

The low-power UART uses two signals (TX and RX) to communicate serially with an external device.

The UART0 module can operate in PM8 mode by taking the clock directly from the RTC0 time clock (RTC0TCLK) and running from the low power mode charge pump. This will allow the system to conserve power while transmitting or receiving UART traffic. The UART supports standard baud-rates of 9600, 4800, 2400 and 1200 in this low power mode.

The UART0 module provides the following features:

- Independent transmitter and receiver configurations with separate 16-bit baud rate generators.

- Asynchronous transmissions and receptions.

- Up to 5 Mbaud (TX or RX).

- Internal transmit and receive FIFOs with flush capability and support for byte, half-word, and word reads and writes.

- Data bit lengths from 5 to 9 bits.

- Programmable inter-packet transmit delays.

- Auto-baud detection with support for the LIN SYNC byte.

- Automatic parity generation (with enable).

- Automatic start and stop generation (with separate enables).

- Independent inversion correction for TX and RX signals.

- Parity error, frame error, overrun, and underrun detection.

- Half-duplex support.

- Multiple loop-back modes supported.

- Multi-processor communications support.

- Operates at 9600, 4800, 2400, or 1200 baud in Power Mode 8.

### 4.7.3. SPI (SPI0, SPI1)

SPI is a 3- or 4-wire communication interface that includes a clock, input data, output data, and an optional select signal.

The SPI0 and SPI1 modules include the following features:

- Supports 3- or 4-wire master or slave modes.

- Supports up to 10 MHz clock in master mode and 5 MHz clock in slave mode.

- Support for all clock phase and slave select (NSS) polarity modes.

- 16-bit programmable clock rate.

- Programmable MSB-first or LSB-first shifting.

- 8-byte FIFO buffers for both transmit and receive data paths to support high speed transfers.

- Support for multiple masters on the same data lines.

In addition, the SPI modules include several features to support autonomous DMA transfers:

- Hardware NSS control.

- Programmable FIFO threshold levels.

- Configurable FIFO data widths.

- Master or slave hardware flow control for the MISO and MOSI signals.

SPI1 is on fixed pins and supports additional flow control options using a fixed input (SPI1CTS). Neither SPI1 nor the flow control input are on the crossbar.

#### 4.7.4. I2C (I2C0)

The I2C interface is a two-wire, bi-directional serial bus. The clock and data signals operate in open-drain mode with external pull-ups to support automatic bus arbitration.

Reads and writes to the interface are byte oriented with the I2C interface autonomously controlling the serial transfer of the data. Data can be transferred at up to 1/8th of the APB clock as a master or slave, which can be faster than allowed by the I2C specification, depending on the clock source used. A method of extending the clock-low duration is available to accommodate devices with different speed capabilities on the same bus.

The I2C interface may operate as a master and/or slave, and may function on a bus with multiple masters. The I2C provides control of SDA (serial data), SCL (serial clock) generation and synchronization, arbitration logic, and start/ stop control and generation.

The I2C0 module includes the following features:

- Standard (up to 100 kbps) and Fast (400 kbps) transfer speeds.

- Can operate down to APB clock divided by 32768 or up to APB clock divided by 8.

- Support for master, slave, and multi-master modes.

- Hardware synchronization and arbitration for multi-master mode.

- Clock low extending (clock stretching) to interface with faster masters.

- Hardware support for 7-bit slave and general call address recognition.

- Firmware support for 10-bit slave address decoding.

- Ability to disable all slave states.

- Programmable clock high and low period.

- Programmable data setup/hold times.

- Spike suppression up to 2 times the APB period.

Table 5.1. Product Selection Guide

| Ordering Part Number | Flash Memory (kB) | RAM (kB) | LCD Segments | Digital Port I/Os | Digital Port I/Os on the Crossbar | Number of SARADC0 Channels | Number of Comparator 0/1 Inputs (+/-) | Number of PMU Pin Wake Sources | Number of ACCTR0 Inputs and Outputs | JTAG Debugging Interface | ETM Debugging Interface | Serial Wire Debugging Interface | Lead-free (RoHS Compliant) | Package |

|----------------------|-------------------|----------|--------------|-------------------|-----------------------------------|----------------------------|---------------------------------------|--------------------------------|-------------------------------------|--------------------------|-------------------------|---------------------------------|----------------------------|---------|

| SiM3L167-C-GQ        | 256               | 32       | 160 (4x40)   | 62                | 38                                | 24                         | 15/15                                 | 14                             | 12                                  | $\checkmark$             | $\checkmark$            | $\checkmark$                    | $\checkmark$               | TQFP-80 |

| SiM3L166-C-GM        | 256               | 32       | 128 (4x32)   | 51                | 34                                | 23                         | 14/12                                 | 11                             | 12                                  |                          | $\checkmark$            | $\checkmark$                    | $\checkmark$               | QFN-64  |

| SiM3L166-C-GQ        | 256               | 32       | 128 (4x32)   | 51                | 34                                | 23                         | 14/12                                 | 11                             | 12                                  |                          | $\checkmark$            | $\checkmark$                    | $\checkmark$               | TQFP-64 |

| SiM3L164-C-GM        | 256               | 32       |              | 28                | 26                                | 20                         | 9/10                                  | 11                             | 5                                   |                          |                         | $\checkmark$                    | $\checkmark$               | QFN-40  |

| SiM3L157-C-GQ        | 128               | 32       | 160 (4x40)   | 62                | 38                                | 24                         | 15/15                                 | 14                             | 12                                  | $\checkmark$             | $\checkmark$            | $\checkmark$                    | $\checkmark$               | TQFP-80 |

| SiM3L156-C-GM        | 128               | 32       | 128 (4x32)   | 51                | 34                                | 23                         | 14/12                                 | 11                             | 12                                  |                          | $\checkmark$            | $\checkmark$                    | $\checkmark$               | QFN-64  |

| SiM3L156-C-GQ        | 128               | 32       | 128 (4x32)   | 51                | 34                                | 23                         | 14/12                                 | 11                             | 12                                  |                          | $\checkmark$            | $\checkmark$                    | $\checkmark$               | TQFP-64 |

| SiM3L154-C-GM        | 128               | 32       |              | 28                | 26                                | 20                         | 9/10                                  | 11                             | 5                                   |                          |                         | $\checkmark$                    | $\checkmark$               | QFN-40  |

| SiM3L146-C-GM        | 64                | 16       | 128 (4x32)   | 51                | 34                                | 23                         | 14/12                                 | 11                             | 12                                  |                          | $\checkmark$            | $\checkmark$                    | $\checkmark$               | QFN-64  |

| SiM3L146-C-GQ        | 64                | 16       | 128 (4x32)   | 51                | 34                                | 23                         | 14/12                                 | 11                             | 12                                  |                          | $\checkmark$            | $\checkmark$                    | $\checkmark$               | TQFP-64 |

| SiM3L144-C-GM        | 64                | 16       |              | 28                | 26                                | 20                         | 9/10                                  | 11                             | 5                                   |                          |                         | $\checkmark$                    | $\checkmark$               | QFN-40  |

| SiM3L136-C-GM        | 32                | 8        | 128 (4x32)   | 51                | 34                                | 23                         | 14/12                                 | 11                             | 12                                  |                          | $\checkmark$            | $\checkmark$                    | $\checkmark$               | QFN-64  |

| SiM3L136-C-GQ        | 32                | 8        | 128 (4x32)   | 51                | 34                                | 23                         | 14/12                                 | 11                             | 12                                  |                          | $\checkmark$            | $\checkmark$                    | $\checkmark$               | TQFP-64 |

| SiM3L134-C-GM        | 32                | 8        |              | 28                | 26                                | 20                         | 9/10                                  | 11                             | 5                                   |                          |                         | $\checkmark$                    | $\checkmark$               | QFN-40  |

| Pin Name           | Туре                                           | Pin Numbers (TQFP-80) | I/O Voltage Domain | Crossbar Capability | Port Match   | LCD Interface | Output Toggle Logic | External Trigger Inputs /<br>Digital Functions | Analog Functions  |  |  |  |

|--------------------|------------------------------------------------|-----------------------|--------------------|---------------------|--------------|---------------|---------------------|------------------------------------------------|-------------------|--|--|--|

| PB0.9              | Standard I/O                                   | 75                    | VIO                | >                   |              |               | ~                   | LPT0T1<br>INT0.9<br>WAKE.9<br>ACCTR0_LCPUL0    | ADC0.1<br>CMP0N.1 |  |  |  |

| PB0.10             | Standard I/O                                   | 74                    | VIO                | ~                   | ~            |               | ~                   | LPT0T2<br>INT0.10<br>WAKE.10<br>ACCTR0_LCPUL1  | ADC0.2<br>CMP1P.1 |  |  |  |

| PB0.11/<br>TDO/SWV | Standard I/O /<br>JTAG / Serial<br>Wire Viewer | 73                    | VIO                | ~                   | ~            |               | ~                   | LPT0T3<br>LPT0OUT1<br>INT0.11<br>WAKE.11       | ADC0.3<br>CMP1N.1 |  |  |  |

| PB1.0              | Standard I/O                                   | 66                    | VIO                | ~                   | ~            | LCD0.39       |                     | LPT0T4<br>INT0.12<br>ACCTR0_LCBIAS0            | CMP0P.2           |  |  |  |

| PB1.1              | Standard I/O                                   | 65                    | VIO                | ~                   | ~            | LCD0.38       |                     | LPT0T5<br>INT0.13<br>ACCTR0_LCBIAS1            | CMP0N.2           |  |  |  |

| PB1.2              | Standard I/O                                   | 64                    | VIO                | $\checkmark$        | $\checkmark$ | LCD0.37       |                     | LPT0T6<br>INT0.14<br>UART0_TX                  | CMP1P.2           |  |  |  |

| PB1.3              | Standard I/O                                   | 63                    | VIO                | >                   | ~            | LCD0.36       |                     | LPT0T7<br>INT0.15<br>UART0_RX                  | CMP1N.2           |  |  |  |

| PB1.4              | Standard I/O                                   | 62                    | VIO                | ~                   | $\checkmark$ | LCD0.35       |                     | ACCTR0_DBG0                                    | ADC0.4            |  |  |  |

| PB1.5              | Standard I/O                                   | 61                    | VIO                | $\checkmark$        | $\checkmark$ | LCD0.34       |                     | ACCTR0_DBG1                                    | ADC0.5            |  |  |  |

| PB1.6/TDI          | Standard I/O /<br>JTAG                         | 60                    | VIO                | ~                   | $\checkmark$ | LCD0.33       |                     |                                                | ADC0.6            |  |  |  |

| PB1.7              | Standard I/O                                   | 59                    | VIO                | ~                   | $\checkmark$ | LCD0.32       |                     | RTC0TCLK_OUT                                   | ADC0.7            |  |  |  |

# Table 6.1. Pin Definitions and Alternate Functions for SiM3L1x7 (Continued)

| Pin Name                 | Туре                  | Pin Numbers (TQFP-80) | I/O Voltage Domain | Crossbar Capability | Port Match   | LCD Interface | Output Toggle Logic | External Trigger Inputs /<br>Digital Functions | Analog Functions |

|--------------------------|-----------------------|-----------------------|--------------------|---------------------|--------------|---------------|---------------------|------------------------------------------------|------------------|

| PB4.9                    | Standard I/O          | 20                    | VIO                |                     | $\checkmark$ | LCD0.6        |                     |                                                |                  |

| PB4.10                   | Standard I/O          | 19                    | VIO                |                     | $\checkmark$ | LCD0.5        |                     |                                                |                  |

| PB4.11/<br>ETM3          | Standard I/O /<br>ETM | 18                    | VIO                |                     | ~            | LCD0.4        |                     |                                                |                  |

| PB4.12/<br>ETM2          | Standard I/O /<br>ETM | 17                    | VIO                |                     | ~            | LCD0.3        |                     |                                                |                  |

| PB4.13/<br>ETM1          | Standard I/O /<br>ETM | 16                    | VIO                |                     | V            | LCD0.2        |                     |                                                |                  |

| PB4.14/<br>ETM0          | Standard I/O /<br>ETM | 15                    | VIO                |                     | ~            | LCD0.1        |                     |                                                |                  |

| PB4.15/<br>TRACE-<br>CLK | Standard I/O /<br>ETM | 14                    | VIO                |                     | $\checkmark$ | LCD0.0        |                     |                                                |                  |

| Pin Name  | Туре                                   | Pin Numbers | I/O Voltage Domain | Crossbar Capability | Port Match | LCD Interface | Output Toggle Logic | External Trigger Inputs /<br>Digital Functions           | Analog Functions            |

|-----------|----------------------------------------|-------------|--------------------|---------------------|------------|---------------|---------------------|----------------------------------------------------------|-----------------------------|

| PB0.2     | Standard I/O                           | 1           | VIO                | XBR<br>0            | 7          |               | ~                   | INT0.2<br>WAKE.3                                         | ADC0.23<br>CMP1N.0<br>XTAL1 |

| PB0.3     | Standard I/O                           | 64          | VIO                | XBR<br>0            | ~          |               | ~                   | INT0.3<br>WAKE.4                                         | ADC0.0<br>CMP0P.1<br>IDAC0  |

| PB0.4     | Standard I/O                           | 63          | VIO                | XBR<br>0            | ~          |               | ~                   | INT0.4<br>WAKE.5<br>ACCTR0_STOP0                         | ACCTR0_IN0                  |

| PB0.5     | Standard I/O                           | 62          | VIO                | XBR<br>0            | ~          |               | ~                   | INT0.5<br>WAKE.6<br>ACCTR0_STOP1                         | ACCTR0_IN1                  |

| PB0.6     | Standard I/O                           | 61          | VIO                | XBR<br>0            | ~          |               | ~                   | INT0.6<br>WAKE.7                                         | ACCTR0_LCIN0                |

| PB0.7     | Standard I/O                           | 60          | VIO                | XBR<br>0            | ~          |               | V                   | LPT0T0<br>LPT0OUT0<br>INT0.7<br>WAKE.8                   | ACCTR0_LCIN1                |

| PB0.8     | Standard I/O                           | 59          | VIO                | XBR<br>0            | ~          |               | V                   | LPT0T1<br>INT0.8<br>WAKE.9<br>ACCTR0_LCPUL0              | ADC0.1<br>CMP0N.1           |

| PB0.9/SWV | Standard I/O<br>/Serial Wire<br>Viewer | 58          | VIO                | XBR<br>0            | ~          |               | V                   | LPT0T2<br>INT0.9<br>WAKE.10<br>LPT0OUT1<br>ACCTR0_LCPUL1 | ADC0.2<br>CMP1P.1           |

| PB1.0     | Standard I/O                           | 53          | VIO                | XBR<br>0            | ~          | LCD0.31       |                     | LPT0T4<br>INT0.12<br>ACCTR0_LCBIAS0                      | CMP0P.2                     |

# Table 6.2. Pin Definitions and Alternate Functions for SiM3L1x6 (Continued)

| 1                |                          | 1           |                    |                     |              |                     |                                                |                                        |

|------------------|--------------------------|-------------|--------------------|---------------------|--------------|---------------------|------------------------------------------------|----------------------------------------|

| Pin Name         | Туре                     | Pin Numbers | I/O Voltage Domain | Crossbar Capability | Port Match   | Output Toggle Logic | External Trigger Inputs /<br>Digital Functions | Analog Functions                       |

| VSS              | Ground                   | 9<br>25     |                    |                     |              |                     |                                                |                                        |

| VSSDC            | Ground (DC-DC)           | 9           |                    |                     |              |                     |                                                |                                        |

| VIO              | Power (I/O)              | 5           |                    |                     |              |                     |                                                |                                        |

| VIORF /<br>VDRV  | Power (RF I/O)           | 6           |                    |                     |              |                     |                                                |                                        |

| VBAT /<br>VBATDC |                          | 7           |                    |                     |              |                     |                                                |                                        |

| VDC              |                          | 10          |                    |                     |              |                     |                                                |                                        |

| IND              | DC-DC Inductor           | 8           |                    |                     |              |                     |                                                |                                        |

| RESET            | Active-low Reset         | 35          |                    |                     |              |                     |                                                |                                        |

| SWCLK            | Serial Wire              | 4           |                    |                     |              |                     |                                                |                                        |

| SWDIO            | Serial Wire              | 3           |                    |                     |              |                     |                                                |                                        |

| RTC1             | RTC Oscillator Input     | 34          |                    |                     |              |                     |                                                |                                        |

| RTC2             | RTC Oscillator<br>Output | 33          |                    |                     |              |                     |                                                |                                        |

| PB0.0            | Standard I/O             | 2           | VIO                | XBR0                | ~            | ~                   | INT0.0<br>WAKE.0                               | ADC0.20<br>VREF<br>CMP0P.0             |

| PB0.1            | Standard I/O             | 1           | VIO                | XBR0                | $\checkmark$ | ~                   | INT0.1<br>WAKE.2                               | ADC0.22<br>CMP0N.0<br>CMP1P.0<br>XTAL2 |

Table 6.3. Pin Definitions and Alternate Functions for SiM3L1x4

| Pin Name | Туре         | Pin Numbers | I/O Voltage Domain | Crossbar Capability | Port Match   | Output Toggle Logic | External Trigger Inputs /<br>Digital Functions | Analog Functions  |

|----------|--------------|-------------|--------------------|---------------------|--------------|---------------------|------------------------------------------------|-------------------|

| PB2.1    | Standard I/O | 28          | VIORF              | XBR0                | ~            |                     | LPT0T9<br>INT1.1<br>WAKE.13<br>VIORFCLK        | ADC0.3<br>CMP0N.4 |

| PB2.2    | Standard I/O | 27          | VIORF              | XBR0                | ~            |                     | LPT0T10<br>INT1.2<br>WAKE.14                   | ADC0.4<br>CMP1P.4 |

| PB2.3    | Standard I/O | 26          | VIORF              | XBR0                | $\checkmark$ |                     | LPT0T11<br>INT1.3<br>WAKE.15                   | ADC0.5<br>CMP1N.4 |

| PB2.4    | Standard I/O | 24          | VIORF              | XBR0                | ~            |                     | LPT0T12<br>INT1.4<br>SPI1_SCLK                 | ADC0.6<br>CMP0P.5 |

| PB2.5    | Standard I/O | 23          | VIORF              | XBR0                | ~            |                     | LPT0T13<br>INT1.5<br>SPI1_MISO                 | ADC0.7<br>CMP0N.5 |

| PB2.6    | Standard I/O | 22          | VIORF              | XBR0                | ~            |                     | LPT0T14<br>INT1.6<br>SPI1_MOSI                 | ADC0.8<br>CMP1P.5 |

| PB2.7    | Standard I/O | 21          | VIORF              | XBR0                | ~            |                     | INT1.7<br>SPI1_NSS                             | ADC0.9<br>CMP1N.5 |

| PB3.0    | Standard I/O | 20          | VIO                | XBR0                | $\checkmark$ |                     | INT1.8                                         | CMP0N.7           |

| PB3.1    | Standard I/O | 19          | VIO                | XBR0                | $\checkmark$ |                     | INT1.9                                         | CMP1P.7           |

| PB3.2    | Standard I/O | 18          | VIO                | XBR0                | $\checkmark$ |                     | INT1.10                                        | CMP1N.7           |

| PB3.3    | Standard I/O | 17          | VIO                | XBR0                | $\checkmark$ |                     | INT1.11                                        | ADC0.10           |

| PB3.4    | Standard I/O | 16          | VIO                | XBR0                | $\checkmark$ |                     | INT1.12                                        | ADC0.11           |

| PB3.5    | Standard I/O | 15          | VIO                | XBR0                | $\checkmark$ |                     | INT1.13                                        | ADC0.12           |

# Table 6.3. Pin Definitions and Alternate Functions for SiM3L1x4 (Continued)

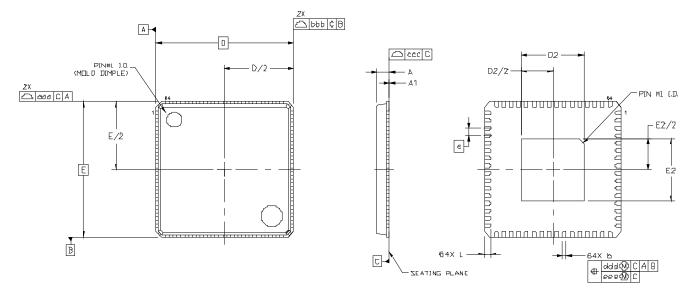

## 6.5. QFN-64 Package Specifications

|           |                | •        |      |  |  |  |

|-----------|----------------|----------|------|--|--|--|

| Dimension | Min            | Nominal  | Max  |  |  |  |

| A         | 0.80           | 0.85     | 0.90 |  |  |  |

| A1        | 0.00           | 0.02     | 0.05 |  |  |  |

| b         | 0.18           | 0.25     | 0.30 |  |  |  |

| D         |                | 9.00 BSC |      |  |  |  |

| D2        | 3.95 4.10 4.25 |          |      |  |  |  |

| e         | 0.50 BSC       |          |      |  |  |  |

| E         | 9.00 BSC       |          |      |  |  |  |

| E2        | 3.95 4.10 4.25 |          |      |  |  |  |

| L         | 0.30 0.40 0.5  |          |      |  |  |  |

| aaa       | aaa 0.10       |          |      |  |  |  |

| bbb       | 0.10           |          |      |  |  |  |

| CCC       | 0.08           |          |      |  |  |  |

| ddd       | 0.10           |          |      |  |  |  |

| eee       | 0.05           |          |      |  |  |  |

#### Table 6.6. QFN-64 Package Dimensions

Notes:

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- 3. This package outline conforms to JEDEC MO-220.

- **4.** Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

| Dimension | Min       | Nominal   | Мах  |  |  |  |

|-----------|-----------|-----------|------|--|--|--|

| A         | _         | —         | 1.20 |  |  |  |

| A1        | 0.05      | —         | 0.15 |  |  |  |

| A2        | 0.95      | 1.00      | 1.05 |  |  |  |

| b         | 0.17      | 0.22      | 0.27 |  |  |  |

| с         | 0.09      | —         | 0.20 |  |  |  |

| D         |           | 12.00 BSC |      |  |  |  |

| D1        | 10.00 BSC |           |      |  |  |  |

| е         | 0.50 BSC  |           |      |  |  |  |

| E         | 12.00 BSC |           |      |  |  |  |

| E1        | 10.00 BSC |           |      |  |  |  |

| L         | 0.45      | 0.75      |      |  |  |  |

| Θ         | 0°        | 3.5°      | 7°   |  |  |  |

| aaa       | _         |           | 0.20 |  |  |  |

| bbb       | —         | —         | 0.20 |  |  |  |

| ccc       | —         | —         | 0.08 |  |  |  |

| ddd       | _         | _         | 0.08 |  |  |  |

Table 6.8. TQFP-64 Package Dimensions

**4.** Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

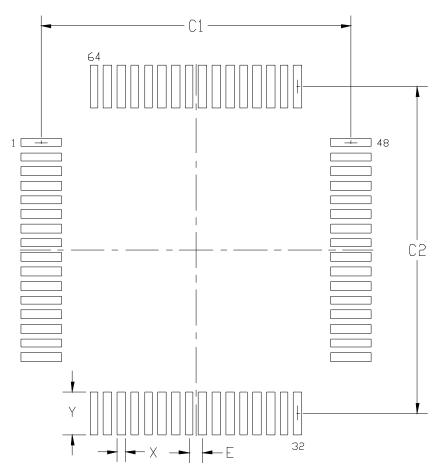

Figure 6.10. TQFP-64 Landing Diagram

| Table 6.9. TQFP-64 Landing Dia | agram Dimensions |

|--------------------------------|------------------|

|--------------------------------|------------------|

| Dimension                                                                                                                                                                             | Min        | Мах   |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------|--|--|--|--|

| C1                                                                                                                                                                                    | 11.30      | 11.40 |  |  |  |  |

| C2                                                                                                                                                                                    | 11.30      | 11.40 |  |  |  |  |

| E                                                                                                                                                                                     | E 0.50 BSC |       |  |  |  |  |

| Х                                                                                                                                                                                     | 0.20       | 0.30  |  |  |  |  |

| Y                                                                                                                                                                                     | 1.40       | 1.50  |  |  |  |  |

| <ul> <li>Notes:</li> <li>1. All dimensions shown are in millimeters (mm) unless otherwise noted.</li> <li>2. This land pattern design is based on the IPC-7351 guidelines.</li> </ul> |            |       |  |  |  |  |

#### 6.7.1. QFN-40 Solder Mask Design

All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60  $\mu$ m minimum, all the way around the pad.

#### 6.7.2. QFN-40 Stencil Design

- 1. A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 2. The stencil thickness should be 0.125 mm (5 mils).

- 3. The ratio of stencil aperture to land pad size should be 1:1 for all pads.

- 4. A 3x3 array of 1.1 mm square openings on a 1.6 mm pitch should be used for the center ground pad.

#### 6.7.3. QFN-40 Card Assembly

- 1. A No-Clean, Type-3 solder paste is recommended.

- 2. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.