Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                             |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                 |

| Core Size                  | 32-Bit Single-Core                                              |

| Speed                      | 50MHz                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, SmartCard, SPI, UART/USART              |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, POR, PWM, WDT                 |

| Number of I/O              | 51                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                  |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 16K x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.8V                                                     |

| Data Converters            | A/D 23x10/12b; D/A 1x10b                                        |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 64-TQFP                                                         |

| Supplier Device Package    | 64-TQFP (10x10)                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/sim3l146-c-gq |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 1. | Related Documents and Conventions                               | 5    |

|----|-----------------------------------------------------------------|------|

|    | 1.1. Related Documents                                          |      |

|    | 1.1.1. SiM3L1xx Reference Manual                                |      |

|    | 1.1.2. Hardware Access Layer (HAL) API Description              | 5    |

|    | 1.1.3. ARM Cortex-M3 Reference Manual                           | 5    |

|    | 1.2. Conventions                                                | 5    |

| 2. | Typical Connection Diagrams                                     | 6    |

|    | 2.1. Power                                                      |      |

| 3. | Electrical Specifications                                       | 8    |

|    | 3.1. Electrical Characteristics                                 |      |

|    | 3.2. Thermal Conditions                                         | . 30 |

|    | 3.3. Absolute Maximum Ratings                                   | .31  |

| 4. | Precision32 <sup>™</sup> SiM3L1xx System Overview               | .32  |

|    | 4.1. Power                                                      |      |

|    | 4.1.1. DC-DC Buck Converter (DCDC0)                             |      |

|    | 4.1.2. Three Low Dropout LDO Regulators (LDO0)                  |      |

|    | 4.1.3. Voltage Supply Monitor (VMON0)                           |      |

|    | 4.1.4. Power Management Unit (PMU)                              | .35  |

|    | 4.1.5. Device Power Modes                                       |      |

|    | 4.1.6. Process/Voltage/Temperature Monitor (TIMER2 and PVTOSC0) | . 38 |

|    | 4.2. I/O                                                        |      |

|    | 4.2.1. General Features                                         |      |

|    | 4.2.2. Crossbar                                                 |      |

|    | 4.3. Clocking                                                   |      |

|    | 4.3.1. PLL (PLL0)                                               |      |

|    | 4.3.2. Low Power Oscillator (LPOSC0)                            |      |

|    | 4.3.3. Low Frequency Oscillator (LFOSC0)                        |      |

|    | 4.3.4. External Oscillators (EXTOSC0)                           |      |

|    | 4.4. Integrated LCD Controller (LCD0)                           |      |

|    | 4.5. Data Peripherals                                           |      |

|    | 4.5.1. 10-Channel DMA Controller                                |      |

|    | 4.5.2. Data Transfer Managers (DTM0, DTM1, DTM2)                | .43  |

|    | 4.5.3. 128/192/256-bit Hardware AES Encryption (AES0)           |      |

|    | 4.5.4. 16/32-bit Enhanced CRC (ECRC0)                           |      |

|    | 4.5.5. Encoder / Decoder (ENCDEC0)                              |      |

|    | 4.6. Counters/Timers                                            |      |

|    | 4.6.1. 32-bit Timer (TIMER0, TIMER1, TIMER2)                    |      |

|    | 4.6.2. Enhanced Programmable Counter Array (EPCA0)              |      |

|    | 4.6.3. Real-Time Clock (RTC0)                                   |      |

|    | 4.6.4. Low Power Timer (LPTIMER0)                               |      |

|    | 4.6.5. Watchdog Timer (WDTIMER0)                                |      |

|    | 4.6.6. Low Power Mode Advanced Capture Counter (ACCTR0)         |      |

|    | 4.7. Communications Peripherals                                 |      |

|    | 4.7.1. USART (USART0)                                           | .48  |

| 4.7.2       UART (UART0)       48         4.7.3       SPI (SPI0, SPI1)       49         4.7.4. I2C (I2C0)       49         4.8. Analog       50         4.8.1. 12-Bit Analog-to-Digital Converter (SARADC0)       50         4.8.1. 12-Bit Analog-to-Digital Converter (IDAC0)       50         4.8.2. 10-Bit Digital-to-Analog Converter (IDAC0)       50         4.8.3. Low Current Comparators (CMP0, CMP1)       50         4.9. Reset Sources       51         4.10. Security.       52         5. Ordering Information       53         6. Pin Definitions       55         6.1. SiM3L1x7 Pin Definitions       55         6.2. SiM3L1x4 Pin Definitions       62         6.3. SiM3L1x4 Pin Definitions       62         6.4. TQFP-80 Saceil Design       77         6.4.1. TQFP-80 Saceil Design       77         6.4.3. TQFP-80 Saceil Design       77         6.5.1. QFN-64 Sace Specifications       78         6.5.1. QFN-64 Sace Specifications       78         6.5.2. QFN-64 Stencil Design       80         6.5.3. QFN-64 Stencil Design       80         6.5.3. QFN-64 Stencil Design       80         6.6.3. TQFP-64 Sace Specifications       81         6.6.1. TQFP-64 Sace Specif                                                 |    |                                    | 40  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|------------------------------------|-----|

| 4.7.4.       I2C (I2C0)       49         4.8. Analog       50         4.8.1.       12-Bit Analog-to-Digital Converter (SARADC0)       50         4.8.2.       10-Bit Digital-to-Analog Converter (IDAC0)       50         4.8.3.       Low Current Comparators (CMP0, CMP1)       50         4.9.       Reset Sources       51         4.10.Security       52         4.11.On-Chip Debugging       52         5.       Ordering Information       53         6.       Pin Definitions       55         6.1.       SiM311x7 Pin Definitions       62         6.3.       SiM311x4 Pin Definitions       62         6.3.       SiM311x4 Pin Definitions       62         6.4.       TQFP-80 Stencil Design       77         6.4.1.       TQFP-80 Stencil Design       77         6.4.2.       TQFP-80 Stencil Design       77         6.4.3.       TQFP-80 Stencil Design       77         6.5.1.       QFN-64 Stencil Design       77         6.5.2.       QFN-64 Stencil Design       80         6.5.1.       QFN-64 Card Assembly       77         6.5.2.       QFN-64 Card Assembly       80         6.6.1.       TQFP-64 Solder Mask Design                                                                                                         |    |                                    |     |

| 4.8. Analog       50         4.8.1. 12-Bit Analog-to-Digital Converter (SARADC0)       50         4.8.2. 10-Bit Digital-to-Analog Converter (IDAC0)       50         4.8.3. Low Current Comparators (CMP0, CMP1)       50         4.9. Reset Sources       51         4.10. Security       52         4.11. On-Chip Debugging       52         5. Ordering Information       53         6. Pin Definitions       55         6.1. SiM3L1x7 Pin Definitions       62         6.3. SiM3L1x4 Pin Definitions       62         6.3. SiM3L1x4 Pin Definitions       69         6.4.1. TQFP-80 Solder Mask Design       77         6.4.2. TQFP-80 Stencil Design       77         6.4.3. TQFP-80 Card Assembly       77         6.5.1. QFN-64 Solder Mask Design       77         6.5.1. QFN-64 Solder Mask Design       80         6.5.2. QFN-64 Card Assembly       80         6.5.3. QFN-64 Card Assembly       80         6.5.3. QFN-64 Card Assembly       80         6.6.1. TQFP-64 Card Assembly       80         6.6.1. TQFP-64 Card Assembly       80         6.6.1. TQFP-64 Card Assembly       80         6.6.2. TQFP-64 Card Assembly       80         6.6.3. TQFP-64 Card Assembly       80 <th></th> <th></th> <th></th>                       |    |                                    |     |

| 4.8.1.       12-Bit Analog-to-Digital Converter (SARADC0)       50         4.8.2.       10-Bit Digital-to-Analog Converter (IDAC0)       50         4.8.3.       Low Current Comparators (CMP0, CMP1)       50         4.9.       Reset Sources.       51         4.10. Security       52         4.11. On-Chip Debugging       52         5.       Ordering Information       53         6.       Pin Definitions       55         6.1.       SiM3L1x7 Pin Definitions       55         6.2.       SiM3L1x7 Pin Definitions       62         6.3.       SiM3L1x4 Pin Definitions       62         6.3.       SiM3L1x4 Pin Definitions       69         6.4.       TQFP-80 Satencil Design       77         6.4.2.       TQFP-80 Stencil Design       77         6.4.3.       TQFP-80 Stencil Design       77         6.4.3.       TQFP-80 Stencil Design       77         6.5.0.       QFN-64 Stencil Design       77         6.5.1.       QFN-64 Stencil Design       80         6.5.2.       QFN-64 Stencil Design       80         6.5.3.       QFN-64 Stencil Design       80         6.5.1.       QFN-64 Stencil Design       80         6.5.2.                                                                                                 |    |                                    |     |

| 4.8.2.       10-Bit Digital-to-Analog Converter (IDAC0)       50         4.8.3.       Low Current Comparators (CMP0, CMP1)       50         4.9.       Reset Sources       51         4.10.Security       52         4.11.On-Chip Debugging       52         5.       Ordering Information       53         6.       Pin Definitions       55         6.1.       SiM3L1x7 Pin Definitions       62         6.2.       SiM3L1x7 Pin Definitions       62         6.3.       SiM3L1x4 Pin Definitions       62         6.4.       TQFP-80 Package Specifications       74         6.4.1.       TQFP-80 Solder Mask Design       77         6.4.2.       TQFP-80 Stencil Design       77         6.4.3.       TQFP-80 Card Assembly.       77         6.5.1.       QFN-64 Package Specifications       78         6.5.1.       QFN-64 Stencil Design       80         6.5.2.       QFN-64 Stencil Design       80         6.5.3.       QFN-64 Stencil Design       80         6.5.3.       QFN-64 Stencil Design       80         6.6.       TQFP-64 Solder Mask Design       84         6.6.1.       TQFP-64 Solder Mask Design       84         6.6.1.                                                                                                 |    |                                    |     |

| 4.8.3. Low Current Comparators (CMP0, CMP1)       50         4.9. Reset Sources       51         4.10.Security       52         4.11.On-Chip Debugging       52         5. Ordering Information       53         6. Pin Definitions       55         6.1. SiM3L1x7 Pin Definitions       55         6.2. SiM3L1x6 Pin Definitions       62         6.3. SiM3L1x4 Pin Definitions       62         6.4. TQFP-80 Package Specifications       74         6.4.1. TQFP-80 Solder Mask Design       77         6.4.2. TQFP-80 Stencil Design       77         6.4.3. TQFP-80 Card Assembly.       77         6.5.1. QFN-64 Package Specifications       78         6.5.1. QFN-64 Solder Mask Design       80         6.5.2. QFN-64 Stencil Design       80         6.5.3. QFN-64 Card Assembly.       80         6.6. TQFP-64 Solder Mask Design       80         6.6. TQFP-64 Solder Mask Design       84         6.6.3. TQFP-64 Sencil Design       84         6.6.1. TQFP-64 Solder Mask Design       84         6.6.2. TQFP-64 Solder Mask Design       84         6.6.3. TQFP-64 Solder Mask Design       84         6.6.1. TQFP-64 Solder Mask Design       84         6.7.1. QFN-40 Solder Mask Design <td< th=""><th></th><th></th><th></th></td<> |    |                                    |     |

| 4.9. Reset Sources       51         4.10.Security       52         4.11.On-Chip Debugging       52         5. Ordering Information       53         6. Pin Definitions       55         6.1. SIM3L1x7 Pin Definitions       62         6.2. SiM3L1x6 Pin Definitions       62         6.3. SiM3L1x4 Pin Definitions       69         6.4. TQFP-80 Solder Mask Design       77         6.4.2. TQFP-80 Solder Mask Design       77         6.4.3. TQFP-80 Solder Mask Design       77         6.4.3. TQFP-80 Solder Mask Design       77         6.4.3. TQFP-80 Solder Mask Design       77         6.5.1. QFN-64 Package Specifications       78         6.5.1. QFN-64 Stencil Design       80         6.5.2. QFN-64 Stencil Design       80         6.5.3. QFN-64 Stencil Design       80         6.5.4. TQFP-64 Solder Mask Design       80         6.5.2. QFN-64 Stencil Design       84         6.6.1. TQFP-64 Solder Mask Design       80         6.6.1. TQFP-64 Solder Mask Design       84         6.6.2. TQFP-64 Solder Mask Design       84         6.6.3. TQFP-64 Card Assembly       80         6.6.1. TQFP-64 Solder Mask Design       84         6.6.2. TQFP-64 Card Assembly       84 </th <th></th> <th></th> <th></th>                 |    |                                    |     |

| 4.10.Security       52         4.11.On-Chip Debugging       52         5. Ordering Information       53         6. Pin Definitions       55         6.1. SiM3L1x7 Pin Definitions       55         6.2. SiM3L1x6 Pin Definitions       62         6.3. SiM3L1x4 Pin Definitions       69         6.4. TQFP-80 Package Specifications       74         6.4.1. TQFP-80 Solder Mask Design       77         6.4.2. TQFP-80 Stencil Design       77         6.4.3. TQFP-80 Stencil Design       77         6.4.3. TQFP-80 Card Assembly       77         6.5.1. QFN-64 Package Specifications       78         6.5.2. QFN-64 Stencil Design       80         6.5.2. QFN-64 Solder Mask Design       80         6.5.3. QFN-64 Card Assembly       80         6.6. TQFP-64 Solder Mask Design       80         6.6.1. TQFP-64 Solder Mask Design       81         6.6.2. TQFP-64 Stencil Design       84         6.6.3. TQFP-64 Stencil Design       84         6.6.3. TQFP-64 Stencil Design       84         6.7.1. QFN-40 Solder Mask Design       84         6.7.2. QFN-40 Solder Mask Design       87         6.7.3. QFN-40 Solder Mask Design       87         6.7.3. QFN-40 Solder Mask Design       87                                              |    |                                    |     |

| 4.11.On-Chip Debugging       52         5. Ordering Information       53         6. Pin Definitions       55         6.1. SiM3L1x7 Pin Definitions       55         6.2. SiM3L1x6 Pin Definitions       62         6.3. SiM3L1x4 Pin Definitions       62         6.4. TQFP-80 Package Specifications       74         6.4.1. TQFP-80 Solder Mask Design       77         6.4.2. TQFP-80 Stencil Design       77         6.4.3. TQFP-80 Card Assembly       77         6.5.4.3. TQFP-80 Card Assembly       77         6.5.4.4.3. TQFP-80 Card Assembly       77         6.5.5.1 QFN-64 Solder Mask Design       80         6.5.2. QFN-64 Stencil Design       80         6.5.3. QFN-64 Solder Mask Design       80         6.5.4. QFN-64 Solder Mask Design       80         6.5.7 QFP-64 Stencil Design       80         6.6.8. TQFP-64 Solder Mask Design       80         6.6.1. TQFP-64 Solder Mask Design       84         6.6.2. TQFP-64 Stencil Design       84         6.6.3. TQFP-64 Card Assembly       84         6.7. QFN-40 Solder Mask Design       87         6.7.1. QFN-40 Solder Mask Design       87         6.7.2. QFN-40 Stencil Design       87         6.7.3. QFN-40 Solder Mask Design                                        |    |                                    |     |

| 5. Ordering Information       53         6. Pin Definitions       55         6.1. SiM3L1x7 Pin Definitions       55         6.2. SiM3L1x6 Pin Definitions       62         6.3. SiM3L1x4 Pin Definitions       69         6.4. TQFP-80 Package Specifications       74         6.4.1. TQFP-80 Solder Mask Design       77         6.4.2. TQFP-80 Stencil Design       77         6.4.3. TQFP-80 Card Assembly       77         6.4.3. TQFP-80 Card Assembly       77         6.5.0 QFN-64 Package Specifications       78         6.5.1. QFN-64 Solder Mask Design       80         6.5.2. QFN-64 Stencil Design       80         6.5.3. QFN-64 Stencil Design       80         6.5.3. QFN-64 Card Assembly       80         6.6. TQFP-64 Package Specifications       81         6.6.1. TQFP-64 Solder Mask Design       84         6.6.2. TQFP-64 Stencil Design       84         6.6.3. TQFP-64 Card Assembly       84         6.7.0. QFN-40 Package Specifications       85         6.7.1. QFN-40 Solder Mask Design       87         6.7.2. QFN-40 Stencil Design       87         6.7.3. QFN-40 Stencil Design       87         6.7.3. QFN-40 Stencil Design       87         6.7.3. QFN-40 Stencil Design                                      |    |                                    |     |

| 6. Pin Definitions       55         6.1. SiM3L1x7 Pin Definitions       55         6.2. SiM3L1x6 Pin Definitions       62         6.3. SiM3L1x4 Pin Definitions       69         6.4. TQFP-80 Package Specifications       74         6.4.1. TQFP-80 Solder Mask Design       77         6.4.2. TQFP-80 Solder Mask Design       77         6.4.3. TQFP-80 Card Assembly       77         6.4.3. TQFP-80 Card Assembly       77         6.5.0 QFN-64 Package Specifications       78         6.5.1. QFN-64 Solder Mask Design       80         6.5.2. QFN-64 Stencil Design       80         6.5.3. QFN-64 Card Assembly       80         6.5.3. QFN-64 Card Assembly       80         6.6.1. TQFP-64 Solder Mask Design       80         6.6.2. TQFP-64 Stencil Design       84         6.6.3. TQFP-64 Solder Mask Design       84         6.6.2. TQFP-64 Stencil Design       84         6.6.3. TQFP-64 Solder Mask Design       84         6.6.3. TQFP-64 Solder Mask Design       84         6.7.1. QFN-40 Solder Mask Design       84         6.7.2. QFN-40 Solder Mask Design       87         6.7.3. QFN-40 Card Assembly       87         6.7.3. QFN-40 Card Assembly       87         6.7.3. QFN-40 Card Assem                               |    |                                    |     |

| 6.1. SiM3L1x7 Pin Definitions       55         6.2. SiM3L1x6 Pin Definitions       62         6.3. SiM3L1x4 Pin Definitions       69         6.4. TQFP-80 Package Specifications       74         6.4.1. TQFP-80 Solder Mask Design       77         6.4.2. TQFP-80 Stencil Design       77         6.4.3. TQFP-80 Card Assembly       77         6.4.3. TQFP-80 Card Assembly       77         6.4.3. TQFP-80 Card Assembly       77         6.5.4.3. QFN-64 Package Specifications       78         6.5.1. QFN-64 Stencil Design       80         6.5.2. QFN-64 Stencil Design       80         6.5.3. QFN-64 Stencil Design       80         6.5.3. QFN-64 Card Assembly       80         6.6.1. TQFP-64 Stencil Design       80         6.6.2. TQFP-64 Stencil Design       84         6.6.3. TQFP-64 Card Assembly       84         6.6.3. TQFP-64 Card Assembly       84         6.7.1. QFN-40 Solder Mask Design       84         6.7.2. QFN-40 Stencil Design       87         6.7.1. QFN-40 Solder Mask Design       87         6.7.2. QFN-40 Stencil Design       87         6.7.3. QFN-40 Card Assembly       87         6.7.3. QFN-40 Card Assembly       87         6.7.3. QFN-40 Card Assembly                                          |    |                                    |     |

| 6.2. SiM3L1x6 Pin Definitions       62         6.3. SiM3L1x4 Pin Definitions       69         6.4. TQFP-80 Package Specifications       74         6.4.1. TQFP-80 Solder Mask Design       77         6.4.2. TQFP-80 Stencil Design       77         6.4.3. TQFP-80 Card Assembly       77         6.4.3. TQFP-80 Card Assembly       77         6.4.3. TQFP-80 Card Assembly       77         6.5.4.3. TQFP-80 Card Assembly       77         6.5.4.4.4.4.4.4.4.4.4.4.4.4.4.4.4.4.4.4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 6. |                                    |     |

| 6.3. SiM3L1x4 Pin Definitions       69         6.4. TQFP-80 Package Specifications       74         6.4.1. TQFP-80 Solder Mask Design       77         6.4.2. TQFP-80 Stencil Design       77         6.4.3. TQFP-80 Card Assembly       77         6.4.3. TQFP-80 Card Assembly       77         6.4.3. TQFP-80 Card Assembly       77         6.5. QFN-64 Package Specifications       78         6.5.1. QFN-64 Solder Mask Design       80         6.5.2. QFN-64 Stencil Design       80         6.5.3. QFN-64 Card Assembly       80         6.6. TQFP-64 Package Specifications       81         6.6.1. TQFP-64 Solder Mask Design       84         6.6.2. TQFP-64 Stencil Design       84         6.6.3. TQFP-64 Card Assembly       84         6.6.4.6.3. TQFP-64 Card Assembly       84         6.6.7. QFN-40 Package Specifications       85         6.7.1. QFN-40 Solder Mask Design       87         6.7.2. QFN-40 Solder Mask Design       87         6.7.3. QFN-40 Card Assembly       87         6.7.4.4.5.4.5.4.5.4.5.4.5.5.5.5.5.5.5.5.5                                                       |    |                                    |     |

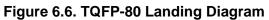

| 6.4. TQFP-80 Package Specifications       74         6.4.1. TQFP-80 Solder Mask Design       77         6.4.2. TQFP-80 Stencil Design       77         6.4.3. TQFP-80 Card Assembly       77         6.5. QFN-64 Package Specifications       78         6.5.1. QFN-64 Solder Mask Design       80         6.5.2. QFN-64 Stencil Design       80         6.5.3. QFN-64 Card Assembly       80         6.6. TQFP-64 Package Specifications       81         6.6.1. TQFP-64 Solder Mask Design       84         6.6.2. TQFP-64 Stencil Design       84         6.6.3. TQFP-64 Stencil Design       84         6.6.3. TQFP-64 Stencil Design       84         6.7.0 QFN-40 Package Specifications       85         6.7.1. QFN-40 Solder Mask Design       84         6.7.2. QFN-40 Stencil Design       87         6.7.3. QFN-40 Card Assembly       87         6.7.3. QFN-40 Card Assembly       87         6.7.3. QFN-40 Card Assembly       87         7.1. Revision Identification       88         7.1. Revision Identification       88         7.1. Revision Identification       88                                                                                                                                                              |    |                                    |     |

| 6.4.1. TQFP-80 Solder Mask Design.       77         6.4.2. TQFP-80 Stencil Design.       77         6.4.3. TQFP-80 Card Assembly.       77         6.4.3. TQFP-80 Card Assembly.       77         6.5. QFN-64 Package Specifications       78         6.5.1. QFN-64 Solder Mask Design.       80         6.5.2. QFN-64 Stencil Design.       80         6.5.3. QFN-64 Card Assembly.       80         6.6. TQFP-64 Package Specifications       81         6.6.1. TQFP-64 Solder Mask Design.       84         6.6.2. TQFP-64 Stencil Design.       84         6.6.3. TQFP-64 Stencil Design.       84         6.6.3. TQFP-64 Card Assembly.       84         6.7.0 QFN-40 Package Specifications       85         6.7.1. QFN-40 Solder Mask Design.       84         6.7.2. QFN-40 Solder Mask Design.       84         6.7.2. QFN-40 Solder Mask Design.       87         6.7.3. QFN-40 Card Assembly.       87         6.7.3. QFN-40 Card Assembly.       87         7.1. Revision Identification       88         7.1. Revision Identification       88         90       90                                                                                                                                                                       |    |                                    |     |

| 6.4.2. TQFP-80 Stencil Design       77         6.4.3. TQFP-80 Card Assembly       77         6.5. QFN-64 Package Specifications       78         6.5.1. QFN-64 Solder Mask Design       80         6.5.2. QFN-64 Stencil Design       80         6.5.3. QFN-64 Card Assembly       80         6.6. TQFP-64 Package Specifications       81         6.6.1. TQFP-64 Solder Mask Design       84         6.6.2. TQFP-64 Stencil Design       84         6.6.3. TQFP-64 Stencil Design       84         6.6.3. TQFP-64 Stencil Design       84         6.6.3. TQFP-64 Stencil Design       84         6.7.0 QFN-40 Package Specifications       85         6.7.1. QFN-64 Card Assembly       84         6.7.2. QFN-40 Solder Mask Design       87         6.7.3. QFN-40 Stencil Design       87         6.7.3. QFN-40 Card Assembly       87         7. Revision Specific Behavior       88         7.1. Revision Identification       88         7.1. Revision Identification       88         7.1. Revision Identification       88                                                                                                                                                                                                                     |    |                                    |     |

| 6.4.3. TQFP-80 Card Assembly.       77         6.5. QFN-64 Package Specifications       78         6.5.1. QFN-64 Solder Mask Design       80         6.5.2. QFN-64 Stencil Design       80         6.5.3. QFN-64 Card Assembly.       80         6.6. TQFP-64 Package Specifications       81         6.6.1. TQFP-64 Package Specifications       81         6.6.2. TQFP-64 Solder Mask Design       84         6.6.3. TQFP-64 Stencil Design       84         6.6.3. TQFP-64 Card Assembly.       84         6.6.3. TQFP-64 Card Assembly.       84         6.7.0. QFN-40 Package Specifications       85         6.7.1. QFN-40 Solder Mask Design       84         6.7.2. QFN-40 Solder Mask Design       87         6.7.2. QFN-40 Solder Mask Design       87         6.7.3. QFN-40 Card Assembly.       87         7.7. Revision Specific Behavior.       88         7.1. Revision Identification       88         7.1. Revision Identification       88         7.1. Revision Identification       88                                                                                                                                                                                                                                            |    |                                    |     |

| 6.5. QFN-64 Package Specifications       78         6.5.1. QFN-64 Solder Mask Design       80         6.5.2. QFN-64 Stencil Design       80         6.5.3. QFN-64 Card Assembly       80         6.6. TQFP-64 Package Specifications       81         6.6.1. TQFP-64 Solder Mask Design       84         6.6.2. TQFP-64 Solder Mask Design       84         6.6.3. TQFP-64 Stencil Design       84         6.6.3. TQFP-64 Card Assembly       84         6.6.3. TQFP-64 Card Assembly       84         6.7. QFN-40 Package Specifications       85         6.7.1. QFN-40 Solder Mask Design       87         6.7.2. QFN-40 Stencil Design       87         6.7.3. QFN-40 Stencil Design       87         6.7.3. QFN-40 Card Assembly       87         7. Revision Specific Behavior       88         7.1. Revision Identification       88         Document Change List       90                                                                                                                                                                                                                                                                                                                                                                      |    | 6.4.2. TQFP-80 Stencil Design      | .77 |

| 6.5.1. QFN-64 Solder Mask Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    | 6.4.3. TQFP-80 Card Assembly       | .77 |

| 6.5.1. QFN-64 Solder Mask Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    | 6.5. QFN-64 Package Specifications | .78 |

| 6.5.3. QFN-64 Card Assembly.806.6. TQFP-64 Package Specifications816.6.1. TQFP-64 Solder Mask Design846.6.2. TQFP-64 Stencil Design846.6.3. TQFP-64 Card Assembly.846.7. QFN-40 Package Specifications856.7.1. QFN-40 Solder Mask Design876.7.2. QFN-40 Solder Mask Design876.7.3. QFN-40 Stencil Design877. Revision Specific Behavior887.1. Revision Identification88Document Change List                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    | 6.5.1. QFN-64 Solder Mask Design   | .80 |

| 6.6. TQFP-64 Package Specifications       81         6.6.1. TQFP-64 Solder Mask Design       84         6.6.2. TQFP-64 Stencil Design       84         6.6.3. TQFP-64 Card Assembly       84         6.7. QFN-40 Package Specifications       85         6.7.1. QFN-40 Solder Mask Design       87         6.7.2. QFN-40 Stencil Design       87         6.7.3. QFN-40 Card Assembly       87         7. Revision Specific Behavior       88         7.1. Revision Identification       88         Document Change List       90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    | 6.5.2. QFN-64 Stencil Design       | .80 |

| 6.6.1. TQFP-64 Solder Mask Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    | 6.5.3. QFN-64 Card Assembly        | .80 |

| 6.6.2. TQFP-64 Stencil Design       84         6.6.3. TQFP-64 Card Assembly       84         6.7. QFN-40 Package Specifications       85         6.7.1. QFN-40 Solder Mask Design       87         6.7.2. QFN-40 Stencil Design       87         6.7.3. QFN-40 Card Assembly       87         7. Revision Specific Behavior       88         7.1. Revision Identification       88         90       90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |                                    |     |

| 6.6.3. TQFP-64 Card Assembly.846.7. QFN-40 Package Specifications856.7.1. QFN-40 Solder Mask Design876.7.2. QFN-40 Stencil Design876.7.3. QFN-40 Card Assembly.877. Revision Specific Behavior887.1. Revision Identification88Document Change List90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    | 6.6.1. TQFP-64 Solder Mask Design  | .84 |

| 6.7. QFN-40 Package Specifications       85         6.7.1. QFN-40 Solder Mask Design       87         6.7.2. QFN-40 Stencil Design       87         6.7.3. QFN-40 Card Assembly       87         7. Revision Specific Behavior       88         7.1. Revision Identification       88         Document Change List       90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    | 6.6.2. TQFP-64 Stencil Design      | .84 |

| 6.7.1. QFN-40 Solder Mask Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    | 6.6.3. TQFP-64 Card Assembly       | .84 |

| 6.7.2. QFN-40 Stencil Design       87         6.7.3. QFN-40 Card Assembly       87         7. Revision Specific Behavior       88         7.1. Revision Identification       88         Document Change List       90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    | 6.7. QFN-40 Package Specifications | .85 |

| 6.7.3. QFN-40 Card Assembly                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    | 6.7.1. QFN-40 Solder Mask Design   | .87 |

| 7. Revision Specific Behavior                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    | 6.7.2. QFN-40 Stencil Design       | .87 |

| 7.1. Revision Identification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    | 6.7.3. QFN-40 Card Assembly        | .87 |

| Document Change List90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 7. | Revision Specific Behavior         | .88 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |                                    |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Do | ocument Change List                | .90 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Co | ontact Information                 | .91 |

### Table 3.2. Power Consumption (Continued)

| Parameter                      | Symbol               | Test Condition                                    | Min | Тур | Max | Unit |

|--------------------------------|----------------------|---------------------------------------------------|-----|-----|-----|------|

| SARADC0                        | ISARADC              | Sampling at 1 Msps, Internal<br>VREF used         |     | 1.2 | 1.6 | mA   |

|                                |                      | Sampling at 250 ksps, lowest power mode settings. |     | 390 | 540 | μA   |

| Temperature Sensor             | I <sub>TSENSE</sub>  |                                                   |     | 75  | 110 | μA   |

| Internal SAR Reference         | I <sub>REFFS</sub>   | Normal Power Mode                                 |     | 680 | _   | μA   |

|                                |                      | Normal Power Mode                                 |     | 160 | _   | μA   |

| VREF0                          | I <sub>REFP</sub>    |                                                   |     | 80  |     | μA   |

| Comparator 0 (CMP0),           | I <sub>CMP</sub>     | CMPMD = 11                                        |     | 0.5 | 2   | μA   |

| Comparator 1 (CMP1)            |                      | CMPMD = 10                                        |     | 3   | 8   | μA   |

|                                |                      | CMPMD = 01                                        |     | 10  | 16  | μA   |

|                                |                      | CMPMD = 00                                        |     | 25  | 42  | μA   |

| IDAC0 <sup>8</sup>             | I <sub>IDAC</sub>    |                                                   | _   | 70  | 100 | μA   |

| Voltage Supply Monitor (VMON0) | I <sub>VMON</sub>    |                                                   |     | 10  | 22  | μA   |

| Flash Current on VBAT          |                      |                                                   | 1   | 1   |     |      |

| Write Operation                | I <sub>FLASH-W</sub> |                                                   |     |     | 8   | mA   |

| Erase Operation                | I <sub>FLASH-E</sub> |                                                   | _   | _   | 15  | mA   |

| Notes:                         | 1                    |                                                   | 1   | 1   | 1   | 1    |

1. Currents are additive. For example, where  $I_{BAT}$  is specified and the mode is not mutually exclusive, enabling the functions increases supply current by the specified amount.

- 2. Includes all peripherals that cannot have clocks gated in the Clock Control module.

- 3. Includes LDO and PLL0OSC (>20 MHz) or LPOSC0 (<20 MHz) supply current.

- 4. Internal Digital and Memory LDOs scaled to optimal output voltage.

- 5. Flash AHB clock turned off.

- 6. Running from internal LFO, Includes LFO supply current.

- 7. LCD0 current does not include switching currents for external load.

- 8. IDAC output current not included.

- 9. Does not include LC tank circuit.

- 10. Does not include digital drive current or pullup current for active port I/O. Unloaded IVIO is included in all IBAT PM8 production test measurements.

### Table 3.7. Internal Oscillators

| Parameter                                                               | Symbol                 | Test Condition                                                                                | Min   | Тур  | Max   | Unit   |

|-------------------------------------------------------------------------|------------------------|-----------------------------------------------------------------------------------------------|-------|------|-------|--------|

| Phase-Locked Loop (PLL0OSC                                              |                        |                                                                                               | L     |      | 1     |        |

| Calibrated Output Frequency<br>(Free-running output mode,<br>RANGE = 2) | f <sub>PLL0OSC</sub>   | Full Temperature and<br>Supply Range                                                          | 48.3  | 49   | 49.7  | MHz    |

| Power Supply Sensitivity<br>(Free-running output mode,<br>RANGE = 2)    | PSS <sub>PLL0OSC</sub> | T <sub>A</sub> = 25 °C,<br>Fout = 49 MHz                                                      | _     | 300  |       | ppm/V  |

| Temperature Sensitivity<br>(Free-running output mode,<br>RANGE = 2)     | TS <sub>PLL0OSC</sub>  | V <sub>BAT</sub> = 3.3 V,<br>Fout = 49 MHz                                                    | _     | 50   |       | ppm/°C |

| Adjustable Output Frequency<br>Range                                    | f <sub>PLL0OSC</sub>   |                                                                                               | 23    | _    | 50    | MHz    |

| Lock Time                                                               | t <sub>PLL0LOCK</sub>  | f <sub>REF</sub> = 20 MHz,<br>f <sub>PLL0OSC</sub> = 50 MHz<br>M=39, N=99,<br>LOCKTH = 0      |       | 2.75 |       | μs     |

|                                                                         |                        | f <sub>REF</sub> = 2.5 MHz,<br>f <sub>PLL0OSC</sub> = 50 MHz<br>M=19, N=399,<br>LOCKTH = 0    |       | 9.45 |       | μs     |

|                                                                         |                        | f <sub>REF</sub> = 32.768 kHz,<br>f <sub>PLL0OSC</sub> = 50 MHz<br>M=0, N=1524,<br>LOCKTH = 0 |       | 92   | _     | μs     |

| Low Power Oscillator (LPOSC0                                            | )                      | 1                                                                                             | I     | I    | 1     |        |

| Oscillator Frequency                                                    | f <sub>LPOSC</sub>     | Full Temperature and<br>Supply Range                                                          | 19    | 20   | 21    | MHz    |

| Divided Oscillator Frequency                                            | f <sub>LPOSCD</sub>    | Full Temperature and<br>Supply Range                                                          | 2.375 | 2.5  | 2.625 | MHz    |

| Power Supply Sensitivity                                                | PSS <sub>LPOSC</sub>   | T <sub>A</sub> = 25 °C                                                                        |       | 0.5  | _     | %/V    |

| Temperature Sensitivity                                                 | TS <sub>LPOSC</sub>    | V <sub>BAT</sub> = 3.3 V                                                                      |       | 55   | _     | ppm/°C |

| Low Frequency Oscillator (LFO                                           | SC0)                   |                                                                                               |       |      | ·     |        |

| Oscillator Frequency                                                    | f <sub>LFOSC</sub>     | Full Temperature and<br>Supply Range                                                          | 13.4  | 16.4 | 19.7  | kHz    |

|                                                                         |                        | T <sub>A</sub> = 25 °C,<br>V <sub>BAT</sub> = 3.3 V                                           | 15.8  | 16.4 | 17.3  | kHz    |

| Power Supply Sensitivity                                                | PSS <sub>LFOSC</sub>   | T <sub>A</sub> = 25 °C                                                                        |       | 2.4  | _     | %/V    |

| Temperature Sensitivity                                                 | TS <sub>LFOSC</sub>    | V <sub>BAT</sub> = 3.3 V                                                                      |       | 0.2  |       | %/°C   |

### Table 3.11. ACCTR (Advanced Capture Counter) (Continued)

| Parameter                                       | Symbol              | Test Condition         | Min   | Тур                  | Max                        | Unit  |

|-------------------------------------------------|---------------------|------------------------|-------|----------------------|----------------------------|-------|

| LC Comparator Positive Hysteresis               | HYS <sub>CP+</sub>  | CMPHYP = 00            | —     | 1.37                 | —                          | mV    |

| Mode 3 (CPMD = 00)                              |                     | CMPHYP = 01            | _     | 3.8                  | _                          | mV    |

|                                                 |                     | CMPHYP = 10            | _     | 7.8                  | _                          | mV    |

|                                                 |                     | CMPHYP = 11            | _     | 15.6                 | _                          | mV    |

| LC Comparator Negative Hysteresis               | HYS <sub>CP-</sub>  | CMPHYN = 00            | _     | 1.37                 |                            | mV    |

| Mode 3 (CPMD = 00)                              |                     | CMPHYN = 01            | _     | -3.9                 |                            | mV    |

|                                                 |                     | CMPHYN = 10            |       | -7.9                 | _                          | mV    |

|                                                 |                     | CMPHYN = 11            | _     | -16                  |                            | mV    |

| LC Comparator Input Range<br>(ACCTR0_LCIN pin)  | V <sub>IN</sub>     |                        | -0.25 | _                    | V <sub>BAT</sub> +<br>0.25 | V     |

| LC Comparator Common-Mode<br>Rejection Ratio    | CMRR <sub>CP</sub>  |                        | _     | 75                   | _                          | dB    |

| LC Comparator Power Supply Rejec-<br>tion Ratio | PSRR <sub>CP</sub>  |                        | _     | 72                   | —                          | dB    |

| LC Comparator Input Offset Voltage              | V <sub>OFF</sub>    | T <sub>A</sub> = 25 °C | -10   | 0                    | 10                         | mV    |

| LC Comparator Input Offset Tempco               | TC <sub>OFF</sub>   |                        | _     | 3.5                  | _                          | µV/°C |

| Reference DAC Offset Error                      | DAC <sub>EOFF</sub> |                        | -1    | —                    | 1                          | LSB   |

| Reference DAC Full Scale Output                 | DAC <sub>FS</sub>   | Low Range              | _     | V <sub>IO</sub> /8   | _                          | V     |

|                                                 |                     | High Range             | _     | V <sub>IO</sub>      |                            | V     |

| Reference DAC Step Size                         | DAC <sub>LSB</sub>  | Low Range (48 steps)   | _     | V <sub>IO</sub> /384 | _                          | V     |

|                                                 |                     | High Range (64 steps)  | _     | V <sub>IO</sub> /64  | _                          | V     |

| LC Oscillator Period                            | T <sub>LCOSC</sub>  |                        | _     | 25                   | _                          | ns    |

| LC Bias Output Impedance                        | R <sub>LCBIAS</sub> | 10 µA Load             | —     | 1                    | —                          | kΩ    |

| LC Bias Drive Strength                          | I <sub>LCBIAS</sub> |                        | _     | _                    | 2                          | mA    |

| Pull-Up Resistor Tolerance                      | R <sub>TOL</sub>    | PUVAL[4:2] = 0 to 6    | -15   | _                    | 15                         | %     |

|                                                 |                     | PUVAL[4:2] = 7         | -10   |                      | 10                         | %     |

### Table 3.16. Port I/O

| Parameter                                                    | Symbol          | Test Condition                                 | Min                     | Тур  | Max | Unit |

|--------------------------------------------------------------|-----------------|------------------------------------------------|-------------------------|------|-----|------|

| Output High Voltage (PB0, PB1,                               | V <sub>OH</sub> | Low Drive, I <sub>OH</sub> = -1 mA             | V <sub>IO</sub> – 0.7   | _    |     | V    |

| PB3, or PB4)                                                 |                 | Low Drive, $I_{OH} = -10 \ \mu A$              | V <sub>IO</sub> – 0.1   | _    |     | V    |

|                                                              |                 | High Drive, $I_{OH} = -3 \text{ mA}$           | V <sub>IO</sub> – 0.7   | —    | _   | V    |

|                                                              |                 | High Drive, $I_{OH} = -10 \ \mu A$             | V <sub>IO</sub> – 0.1   | _    | —   | V    |

| Output High Voltage (PB2)                                    | V <sub>OH</sub> | Low Drive, $I_{OH} = -1 \text{ mA}$            | $V_{IORF} - 0.7$        | _    | —   | V    |

|                                                              |                 | Low Drive, $I_{OH} = -10 \ \mu A$              | $V_{IORF} - 0.1$        | —    | —   | V    |

|                                                              |                 | High Drive, I <sub>OH</sub> = -3 mA            | $V_{IORF} - 0.7$        | _    | —   | V    |

|                                                              |                 | High Drive, $I_{OH} = -10 \ \mu A$             | V <sub>IORF</sub> - 0.1 | _    | —   | V    |

| Output Low Voltage (any Port I/O                             | V <sub>OL</sub> | Low Drive, I <sub>OL</sub> = 1.4 mA            | —                       | _    | 0.6 | V    |

| pin or RESET <sup>1</sup> )                                  |                 | Low Drive, $I_{OL} = 10 \ \mu A$               | —                       | _    | 0.1 | V    |

|                                                              |                 | High Drive, I <sub>OL</sub> = 8.5 mA           | —                       | _    | 0.6 | V    |

|                                                              |                 | High Drive, I <sub>OL</sub> = 10 µA            | —                       | _    | 0.1 | V    |

| Input High Vo <u>ltage (P</u> B0, PB1,<br>PB3, PB4 or RESET) | V <sub>IH</sub> |                                                | V <sub>IO</sub> – 0.6   |      | _   | V    |

| Input High Voltage (PB2)                                     | V <sub>IH</sub> |                                                | V <sub>IORF</sub> - 0.6 | _    |     | V    |

| Input Low Voltage any Port I/O pin or RESET)                 | V <sub>IL</sub> |                                                | —                       | _    | 0.6 | V    |

| Weak Pull-Up Current <sup>2</sup> (per pin)                  | I <sub>PU</sub> | V <sub>IO</sub> or V <sub>IORF</sub> = 1.8     | -6                      | -3.5 | -2  | μA   |

|                                                              |                 | V <sub>IO</sub> or V <sub>IORF</sub> = 3.8     | -32                     | -20  | -10 | μA   |

| Input Leakage<br>(Pullups off or Analog)                     | I <sub>LK</sub> | $0 \le V_{IN} \le V_{IO} \text{ or } V_{IORF}$ | -1                      |      | 1   | μA   |

Notes:

Specifications for RESET V<sub>OL</sub> adhere to the low drive setting.

On the SiM3L1x6 and SiM3L1x4 devices, the SWV pin will have double the weak pull-up current specified whenever the device is held in reset.

### 4.1. Power

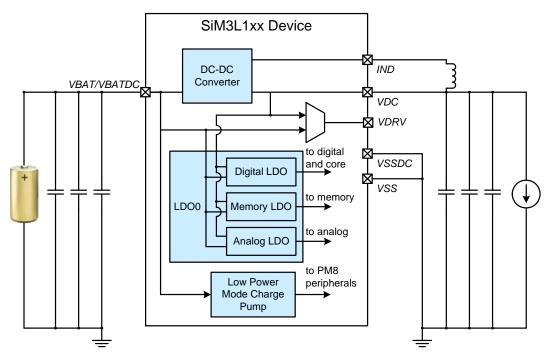

The SiM3L1xx devices include a dc-dc buck converter that can take an input from 1.8–3.8 V and create an output from 1.25–3.8 V. In addition, SiM3L1xx devices include three low dropout regulators as part of the LDO0 module: one LDO powers the analog subsystems, one LDO powers the flash and SRAM memory at 1.8 V, and one LDO powers the digital and core circuitry. Each of these regulators can be independently powered from the dc-dc converter or directly from the battery voltage, and their outputs are adjustable to conserve system power. SiM3L1xx devices also include a low power charge pump in the PMU module for use in low power modes (PM8) to further reduce the power consumption of the device.

Figure 4.2 shows the power system configuration of these devices.

Figure 4.2. SiM3L1xx Power

### 4.1.1. DC-DC Buck Converter (DCDC0)

SiM3L1xx devices include an on-chip step-down dc-dc converter to efficiently utilize the energy stored in the battery, thus extending the operational life time. The dc-dc converter is a switching buck converter with a programmable output voltage that should be at least 0.45 V lower than the input battery voltage; if this criteria is not met and the converter can no longer operate, the output of the dc-dc converter automatically connects to the battery. The dc-dc converter can supply up to 100 mA and can be used to power the MCU and/or external devices in the system.

The dc-dc converter has a built in voltage reference and oscillator and will automatically limit or turn off the switching activity in case the peak inductor current rises beyond a safe limit or the output voltage rises above the programmed target value. This allows the dc-dc converter output to be safely overdriven by a secondary power source (when available) in order to preserve battery life. When enabled, the dc-dc converter can source current into the output capacitor, but cannot sink current.

The dc-dc converter includes the following features:

- Efficiently utilizes the energy stored in a battery, extending its operational lifetime.

- Input range: 1.8 to 3.8 V.

- Output range: 1.25 to 3.8 V in 50 mV (1.25–1.8 V) or 100 mV (1.8–3.8 V) steps.

- Supplies up to 100 mA.

- Includes a voltage reference and an oscillator.

#### 4.6.3. Real-Time Clock (RTC0)

The RTC module includes a 32-bit timer that allows up to 36 hours of independent time-keeping when used with a 32.768 kHz watch crystal. The RTC provides three alarm events in addition to a missing clock event, which can also function as interrupt, reset, or wakeup sources on SiM3L1xx devices.

The RTC module includes internal loading capacitors that are programmable to 16 discrete levels, allowing compatibility with a wide range of crystals.

The RTC timer clock can be buffered and routed to a port bank pin to provide an accurate, low frequency clock to other devices while the core is in its lowest power down mode. The module also includes a low power internal low frequency oscillator that reduces low power mode current and is available for other modules to use as a clock source.

The RTC module includes the following features:

- 32-bit timer (supports up to 36 hours) with three separate alarms.

- Option for one alarm to automatically reset the RTC timer.

- Missing clock detector.

- Can be used with the internal Low Frequency Oscillator or with an external 32.768 kHz crystal (no additional resistors or capacitors necessary).

- Programmable internal loading capacitors support a wide range of external 32.768 kHz crystals.

- The RTC timer clock (RTC0CLK) can be buffered and routed to an I/O pin to provide an accurate, low frequency clock to other devices while the core is in its lowest power down mode.

- The RTC module can be powered from the low power mode charge pump for lowest possible power consumption while in PM8.

#### 4.6.4. Low Power Timer (LPTIMER0)

The Low Power Timer (LPTIMER) module runs from the RTC timer clock (RTC0CLK), allowing the LPTIMER to operate even if the AHB and APB clocks are disabled. The LPTIMER counter can increment using one of two clock sources: the clock selected by the RTC0 module, or rising or falling edges of an external signal.

The Low Power Timer includes the following features:

- Runs on low-frequency RTC timer clock (RTC0TCLK).

- The LPTIMER counter can increment using one of two clock sources: the RTC0TCLK or rising or falling edges of an external signal.

- Overflow and threshold-match detection.

- Timer reset on threshold-match allows square-wave generation at a variable output frequency.

- Supports PWM with configurable period and duty cycle.

- The LPTIMER module can be powered from the low power mode charge pump for lowest possible power consumption while in PM8.

#### 4.6.5. Watchdog Timer (WDTIMER0)

The WDTIMER module includes a 16-bit timer, a programmable early warning interrupt, and a programmable reset period. The timer registers are protected from inadvertent access by an independent lock and key interface.

The watchdog timer runs from the low frequency oscillator (LFOSC0).

The Watchdog Timer has the following features:

- Programmable timeout interval.

- Optional interrupt to warn when the Watchdog Timer is nearing the reset trip value.

- Lock-out feature to prevent any modification until a system reset.

### 4.7. Communications Peripherals

### 4.7.1. USART (USART0)

The USART uses two signals (TX and RX) to communicate serially with an external device. In addition to these signals, the USART module can optionally use a clock (UCLK) or hardware handshaking (RTS and CTS).

The USART module provides the following features:

- Independent transmitter and receiver configurations with separate 16-bit baud rate generators.

- Synchronous or asynchronous transmissions and receptions.

- Clock master or slave operation with programmable polarity and edge controls.

- Up to 5 Mbaud (synchronous or asynchronous, TX or RX, and master or slave) or 1 Mbaud Smartcard (TX or RX).

- Individual enables for generated clocks during start, stop, and idle states.

- Internal transmit and receive FIFOs with flush capability and support for byte, half-word, and word reads and writes.

- Data bit lengths from 5 to 9 bits.

- Programmable inter-packet transmit delays.

- Auto-baud detection with support for the LIN SYNC byte.

- Automatic parity generation (with enable).

- Automatic start and stop generation (with separate enables).

- Transmit and receive hardware flow-control.

- Independent inversion correction for TX, RX, RTS, and CTS signals.

- IrDA modulation and demodulation with programmable pulse widths.

- Smartcard ACK/NACK support.

- Parity error, frame error, overrun, and underrun detection.

- Multi-master and half-duplex support.

- Multiple loop-back modes supported.

- Multi-processor communications support.

#### 4.7.2. UART (UART0)

The low-power UART uses two signals (TX and RX) to communicate serially with an external device.

The UART0 module can operate in PM8 mode by taking the clock directly from the RTC0 time clock (RTC0TCLK) and running from the low power mode charge pump. This will allow the system to conserve power while transmitting or receiving UART traffic. The UART supports standard baud-rates of 9600, 4800, 2400 and 1200 in this low power mode.

The UART0 module provides the following features:

- Independent transmitter and receiver configurations with separate 16-bit baud rate generators.

- Asynchronous transmissions and receptions.

- Up to 5 Mbaud (TX or RX).

- Internal transmit and receive FIFOs with flush capability and support for byte, half-word, and word reads and writes.

- Data bit lengths from 5 to 9 bits.

- Programmable inter-packet transmit delays.

- Auto-baud detection with support for the LIN SYNC byte.

- Automatic parity generation (with enable).

- Automatic start and stop generation (with separate enables).

- Independent inversion correction for TX and RX signals.

- Parity error, frame error, overrun, and underrun detection.

- Half-duplex support.

- Multiple loop-back modes supported.

- Multi-processor communications support.

- Operates at 9600, 4800, 2400, or 1200 baud in Power Mode 8.

### 4.7.3. SPI (SPI0, SPI1)

SPI is a 3- or 4-wire communication interface that includes a clock, input data, output data, and an optional select signal.

The SPI0 and SPI1 modules include the following features:

- Supports 3- or 4-wire master or slave modes.

- Supports up to 10 MHz clock in master mode and 5 MHz clock in slave mode.

- Support for all clock phase and slave select (NSS) polarity modes.

- 16-bit programmable clock rate.

- Programmable MSB-first or LSB-first shifting.

- 8-byte FIFO buffers for both transmit and receive data paths to support high speed transfers.

- Support for multiple masters on the same data lines.

In addition, the SPI modules include several features to support autonomous DMA transfers:

- Hardware NSS control.

- Programmable FIFO threshold levels.

- Configurable FIFO data widths.

- Master or slave hardware flow control for the MISO and MOSI signals.

SPI1 is on fixed pins and supports additional flow control options using a fixed input (SPI1CTS). Neither SPI1 nor the flow control input are on the crossbar.

#### 4.7.4. I2C (I2C0)

The I2C interface is a two-wire, bi-directional serial bus. The clock and data signals operate in open-drain mode with external pull-ups to support automatic bus arbitration.