Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                 |

|----------------------------|-----------------------------------------------------------------|

| Product Status             | Not For New Designs                                             |

| Core Processor             | ARM® Cortex®-M3                                                 |

| Core Size                  | 32-Bit Single-Core                                              |

| Speed                      | 50MHz                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, SmartCard, SPI, UART/USART              |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                      |

| Number of I/O              | 28                                                              |

| Program Memory Size        | 128KB (128K x 8)                                                |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 32K x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.8V                                                     |

| Data Converters            | A/D 20x10/12b; D/A 1x10b                                        |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 40-VFQFN Exposed Pad                                            |

| Supplier Device Package    | 40-QFN (6x6)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/sim3l154-c-gm |

2

**Table 3.2. Power Consumption (Continued)**

| Parameter                      | Symbol               | Test Condition                                    | Min | Тур | Max | Unit |

|--------------------------------|----------------------|---------------------------------------------------|-----|-----|-----|------|

| SARADC0                        | I <sub>SARADC</sub>  | Sampling at 1 Msps, Internal VREF used            | _   | 1.2 | 1.6 | mA   |

|                                |                      | Sampling at 250 ksps, lowest power mode settings. | _   | 390 | 540 | μA   |

| Temperature Sensor             | I <sub>TSENSE</sub>  |                                                   | _   | 75  | 110 | μA   |

| Internal SAR Reference         | I <sub>REFFS</sub>   | Normal Power Mode                                 | _   | 680 | _   | μA   |

|                                |                      | Normal Power Mode                                 | _   | 160 | _   | μA   |

| VREF0                          | I <sub>REFP</sub>    |                                                   | _   | 80  | _   | μA   |

| Comparator 0 (CMP0),           | I <sub>CMP</sub>     | CMPMD = 11                                        | _   | 0.5 | 2   | μA   |

| Comparator 1 (CMP1)            |                      | CMPMD = 10                                        | _   | 3   | 8   | μA   |

|                                |                      | CMPMD = 01                                        | _   | 10  | 16  | μA   |

|                                |                      | CMPMD = 00                                        | _   | 25  | 42  | μA   |

| IDAC0 <sup>8</sup>             | I <sub>IDAC</sub>    |                                                   | _   | 70  | 100 | μA   |

| Voltage Supply Monitor (VMON0) | I <sub>VMON</sub>    |                                                   | _   | 10  | 22  | μA   |

| Flash Current on VBAT          |                      |                                                   | I   | I   | I   |      |

| Write Operation                | I <sub>FLASH-W</sub> |                                                   | _   | _   | 8   | mA   |

| Erase Operation                | I <sub>FLASH-E</sub> |                                                   | _   | _   | 15  | mA   |

## Notes:

- 1. Currents are additive. For example, where I<sub>BAT</sub> is specified and the mode is not mutually exclusive, enabling the functions increases supply current by the specified amount.

- 2. Includes all peripherals that cannot have clocks gated in the Clock Control module.

- 3. Includes LDO and PLL0OSC (>20 MHz) or LPOSC0 (≤20 MHz) supply current.

- 4. Internal Digital and Memory LDOs scaled to optimal output voltage.

- 5. Flash AHB clock turned off.

- 6. Running from internal LFO, Includes LFO supply current.

- 7. LCD0 current does not include switching currents for external load.

- 8. IDAC output current not included.

- 9. Does not include LC tank circuit.

- **10.** Does not include digital drive current or pullup current for active port I/O. Unloaded I<sub>VIO</sub> is included in all I<sub>BAT</sub> PM8 production test measurements.

14

Table 3.5. On-Chip Regulators (Continued)

| Parameter                                                         | Symbol              | Test Condition             | Min | Тур | Max | Unit |

|-------------------------------------------------------------------|---------------------|----------------------------|-----|-----|-----|------|

| Memory LDO Output Setting <sup>5</sup>                            | V <sub>LDOMEM</sub> | During Programming         | 1.8 | _   | 1.9 | V    |

|                                                                   |                     | During Normal<br>Operation | 1.5 | _   | 1.9 | ٧    |

| Digital LDO Output Setting                                        | $V_{LDODIG}$        | F <sub>AHB</sub> ≤ 20 MHz  | 1.0 | _   | 1.9 | V    |

|                                                                   |                     | F <sub>AHB</sub> > 20 MHz  | 1.2 | _   | 1.9 | V    |

| Analog LDO Output Setting During<br>Normal Operation <sup>6</sup> | V <sub>LDOANA</sub> |                            |     | 1.8 |     | V    |

#### Notes:

- 1. See reference manual for recommended inductors.

- 2. Recommended: X7R or X5R ceramic capacitors with low ESR. Example: Murata GRM21BR71C225K with ESR < 10 m $\Omega$  (@ frequency > 1 MHz).

- 3. Input voltage specification accounts for the internal LDO dropout voltage under the maximum load condition to ensure that the LDO output voltage will remain at a valid level as long as  $V_{LDOIN}$  is at or above the specified minimum.

- **4.** The memory LDO output should always be set equal to or lower than the output of the analog LDO. When lowering both LDOs (for example to go into PM8 under low supply conditions), first adjust the memory LDO and then the analog LDO. When raising the output of both LDOs, adjust the analog LDO before adjusting the memory LDO.

- **5.** Output range represents the programmable output range, and does not reflect the minimum voltage under all conditions. Dropout when the input supply is close to the output setting is normal, and accounted for.

- 6. Analog peripheral specifications assume a 1.8 V output on the analog LDO.

Table 3.9. SAR ADC

| Parameter                    | Symbol                          | Test Condition                                                  | Min   | Тур  | Max                | Unit |

|------------------------------|---------------------------------|-----------------------------------------------------------------|-------|------|--------------------|------|

| Resolution                   | N <sub>bits</sub>               | 12 Bit Mode                                                     |       | 12   |                    | Bits |

|                              |                                 | 10 Bit Mode                                                     |       | 10   |                    | Bits |

| Supply Voltage Requirements  | V <sub>ADC</sub>                | High Speed Mode                                                 | 2.2   | _    | 3.8                | V    |

| (VBAT)                       |                                 | Low Power Mode                                                  | 1.8   |      | 3.8                | V    |

| Throughput Rate              | f <sub>S</sub>                  | 12 Bit Mode                                                     | _     | _    | 250                | ksps |

| (High Speed Mode)            |                                 | 10 Bit Mode                                                     | _     | _    | 1                  | Msps |

| Throughput Rate              | f <sub>S</sub>                  | 12 Bit Mode                                                     | _     | _    | 62.5               | ksps |

| (Low Power Mode)             |                                 | 10 Bit Mode                                                     | _     | _    | 250                | ksps |

| Tracking Time                | t <sub>TRK</sub>                | High Speed Mode                                                 | 230   | _    | _                  | ns   |

|                              |                                 | Low Power Mode                                                  | 450   | _    | _                  | ns   |

| SAR Clock Frequency          | f <sub>SAR</sub>                | High Speed Mode                                                 | _     | _    | 16.24              | MHz  |

|                              |                                 | Low Power Mode                                                  | _     | MHz  |                    |      |

| Conversion Time              | t <sub>CNV</sub>                | 10-Bit Conversion,<br>SAR Clock = 16 MHz,<br>APB Clock = 40 MHz | 762.5 |      |                    | ns   |

| Sample/Hold Capacitor        | Hold Capacitor C <sub>SAR</sub> |                                                                 | _     | 5    | _                  | pF   |

|                              |                                 | Gain = 0.5                                                      | _     | 2.5  | _                  | pF   |

| Input Pin Capacitance        | C <sub>IN</sub>                 | High Quality Inputs                                             | _     | 18   | _                  | pF   |

|                              |                                 | Normal Inputs                                                   | _     | 20   | _                  | pF   |

| Input Mux Impedance          | R <sub>MUX</sub>                | High Quality Inputs                                             | _     | 300  | _                  | Ω    |

|                              |                                 | Normal Inputs                                                   | _     | 550  | _                  | Ω    |

| Voltage Reference Range      | V <sub>REF</sub>                |                                                                 | 1     | _    | V <sub>BAT</sub>   | V    |

| Input Voltage Range*         | V <sub>IN</sub>                 | Gain = 1                                                        | 0     | _    | V <sub>REF</sub>   | V    |

|                              |                                 | Gain = 0.5                                                      | 0     | _    | 2xV <sub>REF</sub> | V    |

| Power Supply Rejection Ratio | PSRR <sub>ADC</sub>             |                                                                 | _     | 70   | _                  | dB   |

| DC Performance               |                                 |                                                                 |       |      |                    |      |

| Integral Nonlinearity        | INL                             | 12 Bit Mode                                                     | _     | ±1   | ±1.9               | LSB  |

|                              |                                 | 10 Bit Mode                                                     | _     | ±0.2 | ±0.5               | LSB  |

| Differential Nonlinearity    | DNL                             | 12 Bit Mode                                                     | -1    | ±0.7 | 1.8                | LSB  |

| (Guaranteed Monotonic)       |                                 | 10 Bit Mode                                                     | _     | ±0.2 | ±0.5               | LSB  |

| Offset Error (using VREFGND) | E <sub>OFF</sub>                | 12 Bit Mode, VREF = 2.4 V                                       | -2    | 0    | 2                  | LSB  |

|                              |                                 | 10 Bit Mode, VREF = 2.4 V                                       | -1    | 0    | 1                  | LSB  |

Table 3.10. IDAC

| Parameter                                        | Symbol            | Test Condition                          | Min  | Тур   | Max                    | Unit   |

|--------------------------------------------------|-------------------|-----------------------------------------|------|-------|------------------------|--------|

| Static Performance                               |                   |                                         |      |       |                        |        |

| Resolution                                       | N <sub>bits</sub> |                                         |      | 10    |                        | Bits   |

| Integral Nonlinearity                            | INL               |                                         |      | ±0.5  | ±2                     | LSB    |

| Differential Nonlinearity (Guaranteed Monotonic) | DNL               |                                         | _    | ±0.5  | ±1                     | LSB    |

| Output Compliance Range                          | V <sub>OCR</sub>  |                                         | _    | _     | V <sub>BAT</sub> – 1.0 | V      |

| Full Scale Output Current                        | I <sub>OUT</sub>  | 2 mA Range,<br>T <sub>A</sub> = 25 °C   | 1.98 | 2.046 | 2.1                    | mA     |

|                                                  |                   | 1 mA Range,<br>T <sub>A</sub> = 25 °C   | 0.99 | 1.023 | 1.05                   | mA     |

|                                                  |                   | 0.5 mA Range,<br>T <sub>A</sub> = 25 °C | 491  | 511.5 | 525                    | μA     |

| Offset Error                                     | E <sub>OFF</sub>  |                                         | _    | 250   | _                      | nA     |

| Full Scale Error Tempco                          | TC <sub>FS</sub>  | 2 mA Range                              | _    | 100   | _                      | ppm/°C |

| VBAT Power Supply Rejection Ratio                |                   | 2 mA Range                              | _    | -220  | _                      | ppm/V  |

| Test Load Impedance (to V <sub>SS</sub> )        | R <sub>TEST</sub> |                                         | _    | 1     | _                      | kΩ     |

| Dynamic Performance                              | 1                 |                                         |      |       | 1                      |        |

| Output Settling Time to 1/2 LSB                  |                   | min output to max output                | _    | 1.2   | _                      | μs     |

| Startup Time                                     |                   |                                         | _    | 3     | _                      | μs     |

**Table 3.14. Comparator**

| Parameter                 | Symbol              | Test Condition       | Min | Тур   | Max | Unit |

|---------------------------|---------------------|----------------------|-----|-------|-----|------|

| Response Time, CMPMD = 00 | t <sub>RESP0</sub>  | +100 mV Differential | _   | 100   | _   | ns   |

| (Highest Speed)           |                     | -100 mV Differential | _   | 150   | _   | ns   |

| Response Time, CMPMD = 11 | t <sub>RESP3</sub>  | +100 mV Differential | _   | 1.4   | _   | μs   |

| (Lowest Power)            |                     | -100 mV Differential | _   | 3.5   | _   | μs   |

| Positive Hysteresis       | HYS <sub>CP+</sub>  | CMPHYP = 00          | _   | 0.37  | _   | mV   |

| Mode 0 (CPMD = 00)        |                     | CMPHYP = 01          | _   | 7.9   | _   | mV   |

|                           |                     | CMPHYP = 10          | _   | 16.7  | _   | mV   |

|                           |                     | CMPHYP = 11          | _   | 32.8  | _   | mV   |

| Negative Hysteresis       | HYS <sub>CP</sub>   | CMPHYN = 00          | _   | 0.37  | _   | mV   |

| Mode 0 (CPMD = 00)        |                     | CMPHYN = 01          | _   | -7.9  | _   | mV   |

|                           |                     | CMPHYN = 10          | _   | -16.1 | _   | mV   |

|                           |                     | CMPHYN = 11          | _   | -32.7 | _   | mV   |

| Positive Hysteresis       | HYS <sub>CP+</sub>  | CMPHYP = 00          | _   | 0.47  | _   | mV   |

| Mode 1 (CPMD = 01)        |                     | CMPHYP = 01          | _   | 5.85  | _   | mV   |

|                           |                     | CMPHYP = 10          | _   | 12    | _   | mV   |

|                           |                     | CMPHYP = 11          | _   | 24.4  | _   | mV   |

| Negative Hysteresis       | HYS <sub>CP</sub>   | CMPHYN = 00          | _   | 0.47  | _   | mV   |

| Mode 1 (CPMD = 01)        |                     | CMPHYN = 01          | _   | -6.0  | _   | mV   |

|                           |                     | CMPHYN = 10          | _   | -12.1 | _   | mV   |

|                           |                     | CMPHYN = 11          | _   | -24.6 | _   | mV   |

| Positive Hysteresis       | HYS <sub>CP+</sub>  | CMPHYP = 00          | _   | 0.66  | _   | mV   |

| Mode 2 (CPMD = 10)        |                     | CMPHYP = 01          | _   | 4.55  | _   | mV   |

|                           |                     | CMPHYP = 10          | _   | 9.3   | _   | mV   |

|                           |                     | CMPHYP = 11          | _   | 19    | _   | mV   |

| Negative Hysteresis       | HYS <sub>CP</sub> - | CMPHYN = 00          | _   | 0.6   | _   | mV   |

| Mode 2 (CPMD = 10)        |                     | CMPHYN = 01          | _   | -4.5  | _   | mV   |

|                           |                     | CMPHYN = 10          | _   | -9.5  | _   | mV   |

|                           |                     | CMPHYN = 11          | _   | -19   | _   | mV   |

- Supports synchronizing the regulator switching with the system clock.

- Automatically limits the peak inductor current if the load current rises beyond a safe limit.

- Automatically goes into bypass mode if the battery voltage cannot provide sufficient headroom.

- Sources current, but cannot sink current.

#### 4.1.2. Three Low Dropout LDO Regulators (LDO0)

The SiM3L1xx devices include one LDO0 module with three low dropout regulators. Each of these regulators have independent switches to select the battery voltage or the output of the dc-dc converter as the input to each LDO, and an adjustable output voltage.

The LDOs consume little power and provide flexibility in choosing a power supply for the system. Each regulator can be independently adjusted between 0.8 and 1.9 V output.

## 4.1.3. Voltage Supply Monitor (VMON0)

The SiM3L1xx devices include a voltage supply monitor that can monitor the main supply voltage. This module includes the following features:

- Main supply "VBAT Low" (VBAT below the early warning threshold) notification.

- Holds the device in reset if the main VBAT supply drops below the VBAT Reset threshold.

The voltage supply monitor allows devices to function in known, safe operating conditions without the need for external hardware.

#### 4.1.4. Power Management Unit (PMU)

The Power Management Unit on the SiM3L1xx manages the power systems of the device. It manages the power-up sequence during power on and the wake up sources for PM8. On power-up, the PMU ensures the core voltages are a proper value before core instruction execution begins.

The VDRV pin powers external circuitry from either the VBAT battery input voltage or the output of the dc-dc converter on VDC. The PMU includes an internal switch to select one of these sources for the VDRV pin.

The PMU has a specialized VBAT-divided-by-2 charge pump that can power some internal modules while in PM8 to save power.

The PMU module includes the following features:

- Provides the enable or disable for the analog power system, including the three LDO regulators.

- Up to 14 pin wake inputs can wake the device from Power Mode 8.

- The Low Power Timer, RTC0 (alarms and oscillator failure), Comparator 0, Advanced Capture Counter, LCD0 VBAT monitor, UART0, low power mode charge pump failure, and the RESET pin can also serve as wake sources for Power Mode 8.

- Controls which 4 kB RAM blocks are retained while in Power Mode 8.

- Provides a PMU\_Asleep signal to a pin as an indicator that the device is in PM8.

- Specialized charge pump to reduce power consumption in PM8.

Provides control for the internal switch between VBAT and VDC to power the VDRV pin for external circuitry.

#### 4.1.5. Device Power Modes

The SiM3L1xx devices feature seven low power modes in addition to normal operating mode. Several peripherals provide wake up sources for these low power modes, including the Low Power Timer (LPTIMER0), RTC0 (alarms and oscillator failure notification), Comparator 0 (CMP0), Advanced Capture Counter (ACCTR0), LCD VBAT monitor (LCD0), UART0, low power mode charge pump failure, and PMU Pin Wake.

In addition, all peripherals can have their clocks disabled to reduce power consumption whenever a peripheral is not being used using the clock control (CLKCTRL) registers.

#### 4.1.5.1. Normal Mode (Power Mode 0) and Power Mode 4

Normal Mode and Power Mode 4 are fully operational modes with code executing from flash memory. PM4 is the same as Normal Mode, but with the clocks operating at a lower speed. This enables power to be conserved by reducing the LDO regulator outputs.

## 4.1.6. Process/Voltage/Temperature Monitor (TIMER2 and PVTOSC0)

The Process/Voltage/Temperature monitor consists of two modules (TIMER2 and PVTOSC0) designed to monitor the digital circuit performance of the SiM3L1xx device.

The PVT oscillator (PVTOSC0) consists of two oscillators, one operating from the memory LDO and one operating from the digital LDO. These oscillators have two independent speed options and provide the clocks for two 16-bit timers in the TIMER2 module using the EX input. By monitoring the resulting counts of the TIMER2 timers, firmware can monitor the current device performance and increase the scalable LDO regulator (LDO0) output voltages as needed or decrease the output voltages to save power.

The PVT monitor has the following features:

- Two separate oscillators and timers for the memory and digital logic voltage domains.

- Two oscillator output divider settings.

- Provides a method for monitoring digital performance to allow firmware to adjust the scalable LDO regulator output voltages to the lowest level possible, saving power.

#### 4.2. I/O

#### 4.2.1. General Features

The SiM3L1xx ports have the following features:

- 5 V tolerant.

- Push-pull or open-drain output modes to the VIO or VIORF voltage level.

- Analog or digital modes.

- Option for high or low output drive strength.

- Port Match allows the device to recognize a change on a port pin value.

- Internal pull-up resistors are enabled or disabled on a port-by-port basis.

- Two external interrupts with up to 16 inputs each provide monitoring capability for external signals.

- Internal Pulse Generator Timer (PB0 only) to generate simple square waves and pulses.

#### 4.2.2. Crossbar

The SiM3L1xx devices have one crossbar with the following features:

- Flexible peripheral assignment to port pins.

- Pins can be individually skipped to move peripherals as needed for design or layout considerations.

The crossbar has a fixed priority for each I/O function and assigns these functions to the port pins. When a digital resource is selected, the least-significant unassigned port pin is assigned to that resource. If a port pin is assigned, the crossbar skips that pin when assigning the next selected resource. Additionally, the crossbar will skip port pins whose associated bits in the PBSKIPEN registers are set. This provides flexibility when designing a system: pins involved with sensitive analog measurements can be moved away from digital I/O, and peripherals can be moved around the chip as needed to ease layout constraints.

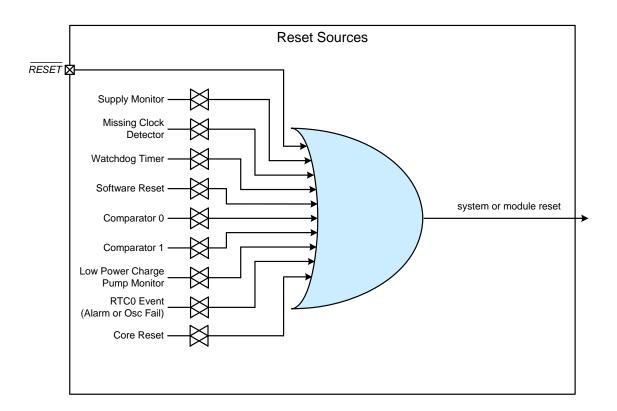

#### 4.9. Reset Sources

Reset circuitry allows the controller to be easily placed in a predefined default condition. On entry to this reset state, the following occur:

- The core halts program execution.

- Module registers are initialized to their defined reset values unless the bits reset only with a power-on reset.

- External port pins are forced to a known state.

- Interrupts and timers are disabled.

- AHB peripheral clocks to flash and RAM are enabled.

- Clocks to all APB peripherals other than the Watchdog Timer and DMAXBAR are disabled.

All registers are reset to the predefined values noted in the register descriptions unless the bits only reset with a power-on reset. The contents of RAM are unaffected during a reset; any previously stored data is preserved as long as power is not lost.

The Port I/O latches are reset to 1 in open-drain mode. Weak pullups are enabled during and after the reset. For VBAT Supply Monitor and power-on resets, the RESET pin is driven low until the device exits the reset state.

On exit from the reset state, the program counter (PC) is reset, and the system clock defaults to the internal low-power oscillator. The Watchdog Timer is enabled with the low frequency oscillator as its clock source. Program execution begins at location 0x00000000.

All RSTSRC0 registers may be locked against writes by setting the CLKRSTL bit in the LOCK0\_PERIPHLOCK0 register to 1.

The reset sources can also optionally reset individual modules, including the low power mode charge pump, UARTO, LCDO, advanced capture counter (ACCTRO), and RTCO.

Figure 4.4. SiM3L1xx Reset Sources Block Diagram

# 6. Pin Definitions

# 6.1. SiM3L1x7 Pin Definitions

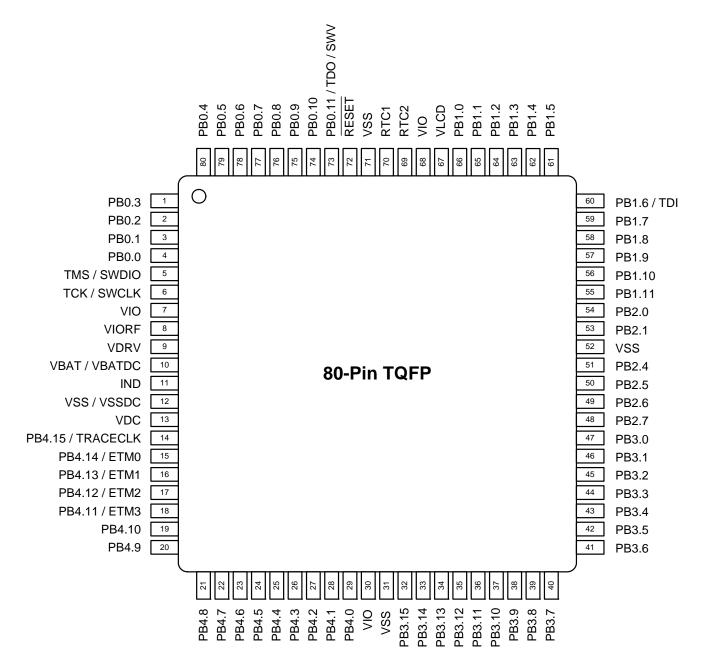

Figure 6.1. SiM3L1x7-GQ Pinout

Table 6.1. Pin Definitions and Alternate Functions for SiM3L1x7 (Continued)

| Pin Name | Туре         | Pin Numbers (TQFP-80) | I/O Voltage Domain | Crossbar Capability | Port Match | LCD Interface | Output Toggle Logic | External Trigger Inputs /<br>Digital Functions | Analog Functions   |

|----------|--------------|-----------------------|--------------------|---------------------|------------|---------------|---------------------|------------------------------------------------|--------------------|

| PB1.8    | Standard I/O | 58                    | VIO                | <b>V</b>            | <b>V</b>   | LCD0.31       |                     |                                                | CMP0P.3            |

| PB1.9    | Standard I/O | 57                    | VIO                | <b>\</b>            | <b>/</b>   | LCD0.30       |                     |                                                | CMP0N.3            |

| PB1.10   | Standard I/O | 56                    | VIO                | <b>V</b>            | <b>V</b>   | LCD0.29       |                     |                                                | CMP1P.3            |

| PB1.11   | Standard I/O | 55                    | VIO                | <b>/</b>            | <b>V</b>   | LCD0.28       |                     |                                                | CMP1N.3            |

| PB2.0    | Standard I/O | 54                    | VIORF              | ✓                   | ✓          |               |                     | LPT0T8<br>INT1.0<br>WAKE.12<br>SPI1_CTS        | ADC0.8<br>CMP0P.4  |

| PB2.1    | Standard I/O | 53                    | VIORF              | <b>V</b>            | ✓          |               |                     | LPT0T9<br>INT1.1<br>WAKE.13<br>VIORFCLK        | ADC0.9<br>CMP0N.4  |

| PB2.4    | Standard I/O | 51                    | VIORF              | ✓                   | ✓          |               |                     | LPT0T12<br>INT1.4<br>SPI1_SCLK                 | ADC0.10<br>CMP0P.5 |

| PB2.5    | Standard I/O | 50                    | VIORF              | ✓                   | ✓          |               |                     | LPT0T13<br>INT1.5<br>SPI1_MISO                 | ADC0.11<br>CMP0N.5 |

| PB2.6    | Standard I/O | 49                    | VIORF              | ✓                   | ✓          |               |                     | LPT0T14<br>INT1.6<br>SPI1_MOSI                 | ADC0.12<br>CMP1P.5 |

| PB2.7    | Standard I/O | 48                    | VIORF              | <b>√</b>            | <b>√</b>   |               |                     | INT1.7<br>SPI1_NSS                             | ADC0.13<br>CMP1N.5 |

| PB3.0    | Standard I/O | 47                    | VIO                | <b>/</b>            | <b>✓</b>   | LCD0.27       |                     | INT1.8                                         | ADC0.14            |

| PB3.1    | Standard I/O | 46                    | VIO                | /                   | /          | LCD0.26       |                     | INT1.9                                         | ADC0.15            |

| PB3.2    | Standard I/O | 45                    | VIO                | ✓                   | ✓          | LCD0.25       |                     | INT1.10                                        | ADC0.16            |

| PB3.3    | Standard I/O | 44                    | VIO                | <b>✓</b>            | ✓          | LCD0.24       |                     | INT1.11                                        | ADC0.17            |

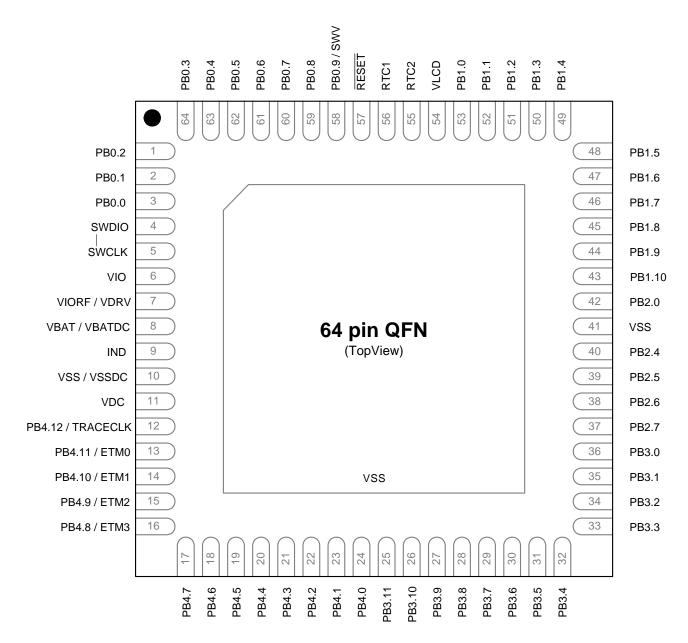

Figure 6.3. SiM3L1x6-GM Pinout

Table 6.2. Pin Definitions and Alternate Functions for SiM3L1x6 (Continued)

|           |                                        | I           | l                  | 1                   | ı          |               | ı                   |                                                          |                             |

|-----------|----------------------------------------|-------------|--------------------|---------------------|------------|---------------|---------------------|----------------------------------------------------------|-----------------------------|

| Pin Name  | Туре                                   | Pin Numbers | I/O Voltage Domain | Crossbar Capability | Port Match | LCD Interface | Output Toggle Logic | External Trigger Inputs / Digital Functions              | Analog Functions            |

| PB0.2     | Standard I/O                           | 1           | VIO                | XBR<br>0            | ✓          |               | <b>✓</b>            | INT0.2<br>WAKE.3                                         | ADC0.23<br>CMP1N.0<br>XTAL1 |

| PB0.3     | Standard I/O                           | 64          | VIO                | XBR<br>0            | ✓          |               | ✓                   | INT0.3<br>WAKE.4                                         | ADC0.0<br>CMP0P.1<br>IDAC0  |

| PB0.4     | Standard I/O                           | 63          | VIO                | XBR<br>0            | ✓          |               | ✓                   | INT0.4<br>WAKE.5<br>ACCTR0_STOP0                         | ACCTR0_IN0                  |

| PB0.5     | Standard I/O                           | 62          | VIO                | XBR<br>0            | ✓          |               | ✓                   | INT0.5<br>WAKE.6<br>ACCTR0_STOP1                         | ACCTR0_IN1                  |

| PB0.6     | Standard I/O                           | 61          | VIO                | XBR<br>0            | ✓          |               | ✓                   | INT0.6<br>WAKE.7                                         | ACCTR0_LCIN0                |

| PB0.7     | Standard I/O                           | 60          | VIO                | XBR<br>0            | ✓          |               | <b>V</b>            | LPT0T0<br>LPT0OUT0<br>INT0.7<br>WAKE.8                   | ACCTR0_LCIN1                |

| PB0.8     | Standard I/O                           | 59          | VIO                | XBR<br>0            | ✓          |               | ✓                   | LPT0T1<br>INT0.8<br>WAKE.9<br>ACCTR0_LCPUL0              | ADC0.1<br>CMP0N.1           |

| PB0.9/SWV | Standard I/O<br>/Serial Wire<br>Viewer | 58          | VIO                | XBR<br>0            | V          |               | V                   | LPT0T2<br>INT0.9<br>WAKE.10<br>LPT0OUT1<br>ACCTR0_LCPUL1 | ADC0.2<br>CMP1P.1           |

| PB1.0     | Standard I/O                           | 53          | VIO                | XBR<br>0            | <b>√</b>   | LCD0.31       |                     | LPT0T4<br>INT0.12<br>ACCTR0_LCBIAS0                      | CMP0P.2                     |

Table 6.2. Pin Definitions and Alternate Functions for SiM3L1x6 (Continued)

| Pin Name | Туре         | Pin Numbers | I/O Voltage Domain | Crossbar Capability | Port Match | LCD Interface | Output Toggle Logic | External Trigger Inputs /<br>Digital Functions | Analog Functions  |

|----------|--------------|-------------|--------------------|---------------------|------------|---------------|---------------------|------------------------------------------------|-------------------|

| PB1.1    | Standard I/O | 52          | VIO                | XBR<br>0            | \          | LCD0.30       |                     | LPT0T5<br>INT0.13<br>ACCTR0_LCBIAS1            | CMP0N.2           |

| PB1.2    | Standard I/O | 51          | VIO                | XBR<br>0            | <b>\</b>   | LCD0.29       |                     | LPT0T6<br>INT0.14<br>UART0_TX                  | CMP1P.2           |

| PB1.3    | Standard I/O | 50          | VIO                | XBR<br>0            | <b>V</b>   | LCD0.28       |                     | LPT0T7<br>INT0.15<br>UART0_RX                  | CMP1N.2           |

| PB1.4    | Standard I/O | 49          | VIO                | XBR<br>0            | <b>/</b>   | LCD0.27       |                     | ACCTR0_DBG0                                    | ADC0.3            |

| PB1.5    | Standard I/O | 48          | VIO                | XBR<br>0            | ✓          | LCD0.26       |                     | ACCTR0_DBG1                                    | ADC0.4            |

| PB1.6    | Standard I/O | 47          | VIO                | XBR<br>0            | ✓          | LCD0.25       |                     | RTC0TCLK_OUT                                   | ADC0.5            |

| PB1.7    | Standard I/O | 46          | VIO                | XBR<br>0            | ✓          | LCD0.24       |                     |                                                | CMP0P.3           |

| PB1.8    | Standard I/O | 45          | VIO                | XBR<br>0            | <b>V</b>   | LCD0.23       |                     |                                                | CMP0N.3           |

| PB1.9    | Standard I/O | 44          | VIO                | XBR<br>0            | >          | LCD0.22       |                     |                                                | CMP1P.3           |

| PB1.10   | Standard I/O | 43          | VIO                | XBR<br>0            | <b>✓</b>   | LCD0.21       |                     |                                                | CMP1N.3           |

| PB2.0    | Standard I/O | 42          | VIOR<br>F          | XBR<br>0            | ✓          |               |                     | LPT0T8<br>INT1.0<br>WAKE.12<br>SPI1_CTS        | ADC0.6<br>CMP0P.4 |

| PB2.4    | Standard I/O | 40          | VIOR<br>F          | XBR<br>0            | <b>√</b>   |               |                     | LPT0T12<br>INT1.4<br>SPI1_SCLK                 | ADC0.7<br>CMP0P.5 |

Table 6.2. Pin Definitions and Alternate Functions for SiM3L1x6 (Continued)

| Pin Name            | Туре                  | Pin Numbers | I/O Voltage Domain | Crossbar Capability | Port Match | LCD Interface | Output Toggle Logic | External Trigger Inputs /<br>Digital Functions | Analog Functions |

|---------------------|-----------------------|-------------|--------------------|---------------------|------------|---------------|---------------------|------------------------------------------------|------------------|

| PB4.0               | Standard I/O          | 24          | VIO                |                     | <b>V</b>   | COM0.1        |                     |                                                |                  |

| PB4.1               | Standard I/O          | 23          | VIO                |                     | ~          | COM0.0        |                     |                                                |                  |

| PB4.2               | Standard I/O          | 22          | VIO                |                     | <b>V</b>   | LCD0.10       |                     |                                                | ADC0.19          |

| PB4.3               | Standard I/O          | 21          | VIO                |                     | <b>✓</b>   | LCD0.9        |                     |                                                |                  |

| PB4.4               | Standard I/O          | 20          | VIO                |                     | <b>V</b>   | LCD0.8        |                     |                                                |                  |

| PB4.5               | Standard I/O          | 19          | VIO                |                     | <b>V</b>   | LCD0.7        |                     |                                                |                  |

| PB4.6               | Standard I/O          | 18          | VIO                |                     | <b>✓</b>   | LCD0.6        |                     | PMU_Asleep                                     |                  |

| PB4.7               | Standard I/O          | 17          | VIO                |                     | <b>V</b>   | LCD0.5        |                     |                                                |                  |

| PB4.8/ETM3          | Standard I/O /<br>ETM | 16          | VIO                |                     | <b>V</b>   | LCD0.4        |                     |                                                |                  |

| PB4.9/ETM2          | Standard I/O /<br>ETM | 15          | VIO                |                     | V          | LCD0.3        |                     |                                                |                  |

| PB4.10/<br>ETM1     | Standard I/O /<br>ETM | 14          | VIO                |                     | V          | LCD0.2        |                     |                                                |                  |

| PB4.11/<br>ETM0     | Standard I/O /<br>ETM | 13          | VIO                |                     | ✓          | LCD0.1        |                     |                                                |                  |

| PB4.12/<br>TRACECLK | Standard I/O /<br>ETM | 12          | VIO                |                     | V          | LCD0.0        |                     |                                                |                  |

Table 6.3. Pin Definitions and Alternate Functions for SiM3L1x4 (Continued)

| Pin Name | Туре         | Pin Numbers | I/O Voltage Domain | Crossbar Capability | Port Match | Output Toggle Logic | External Trigger Inputs / Digital Functions | Analog Functions |

|----------|--------------|-------------|--------------------|---------------------|------------|---------------------|---------------------------------------------|------------------|

| PB3.6    | Standard I/O | 14          | VIO                | XBR0                | <b>V</b>   |                     | INT1.14                                     | ADC0.13          |

| PB3.7    | Standard I/O | 13          | VIO                | XBR0                | <b>V</b>   |                     | INT1.15                                     | ADC0.14          |

| PB3.8    | Standard I/O | 12          | VIO                |                     | <b>√</b>   |                     |                                             | ADC0.15          |

| PB3.9    | Standard I/O | 11          | VIO                |                     | <b>V</b>   |                     |                                             | ADC0.16          |

73

Table 6.4. TQFP-80 Package Dimensions

| Min            | Nominal                      | Max  |  |  |  |  |  |  |

|----------------|------------------------------|------|--|--|--|--|--|--|

| _              | _                            | 1.20 |  |  |  |  |  |  |

| 0.05           | _                            | 0.15 |  |  |  |  |  |  |

| 0.95 1.00 1.05 |                              |      |  |  |  |  |  |  |

| 0.17           | 0.20                         | 0.27 |  |  |  |  |  |  |

| 0.09           | 0.20                         |      |  |  |  |  |  |  |

| 14.00 BSC      |                              |      |  |  |  |  |  |  |

| 12.00 BSC      |                              |      |  |  |  |  |  |  |

| 0.50 BSC       |                              |      |  |  |  |  |  |  |

| 14.00 BSC      |                              |      |  |  |  |  |  |  |

|                | 12.00 BSC                    |      |  |  |  |  |  |  |

| 0.45           | 0.60                         | 0.75 |  |  |  |  |  |  |

|                | 1.00 Ref                     |      |  |  |  |  |  |  |

| 0°             | 3.5°                         | 7°   |  |  |  |  |  |  |

|                | 0.20                         |      |  |  |  |  |  |  |

|                | 0.20                         |      |  |  |  |  |  |  |

|                | 0.08                         |      |  |  |  |  |  |  |

|                | 0.08                         |      |  |  |  |  |  |  |

|                | 0.05                         |      |  |  |  |  |  |  |

|                | 0.05<br>0.95<br>0.17<br>0.09 | 0.05 |  |  |  |  |  |  |

# Notes:

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- 3. This package outline conforms to JEDEC MS-026, variant ADD.

- **4.** Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

## 6.4.1. TQFP-80 Solder Mask Design

All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60 µm minimum, all the way around the pad.

# 6.4.2. TQFP-80 Stencil Design

- 1. A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 2. The stencil thickness should be 0.125 mm (5 mils).

- 3. The ratio of stencil aperture to land pad size should be 1:1 for all pads.

## 6.4.3. TQFP-80 Card Assembly

- 1. A No-Clean, Type-3 solder paste is recommended.

- 2. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

## 6.7.1. QFN-40 Solder Mask Design

All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60 µm minimum, all the way around the pad.

# 6.7.2. QFN-40 Stencil Design

- 1. A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 2. The stencil thickness should be 0.125 mm (5 mils).

- 3. The ratio of stencil aperture to land pad size should be 1:1 for all pads.

- 4. A 3x3 array of 1.1 mm square openings on a 1.6 mm pitch should be used for the center ground pad.

## 6.7.3. QFN-40 Card Assembly

- 1. A No-Clean, Type-3 solder paste is recommended.

- 2. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.