Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                             |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                 |

| Core Size                  | 32-Bit Single-Core                                              |

| Speed                      | 50MHz                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, SmartCard, SPI, UART/USART              |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, POR, PWM, WDT                 |

| Number of I/O              | 51                                                              |

| Program Memory Size        | 256KB (256K x 8)                                                |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 32K x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.8V                                                     |

| Data Converters            | A/D 23x10/12b; D/A 1x10b                                        |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 64-TQFP                                                         |

| Supplier Device Package    | 64-TQFP (10x10)                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/sim3l166-c-gq |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 1. | Related Documents and Conventions                               | 5    |

|----|-----------------------------------------------------------------|------|

|    | 1.1. Related Documents                                          |      |

|    | 1.1.1. SiM3L1xx Reference Manual                                |      |

|    | 1.1.2. Hardware Access Layer (HAL) API Description              | 5    |

|    | 1.1.3. ARM Cortex-M3 Reference Manual                           | 5    |

|    | 1.2. Conventions                                                | 5    |

| 2. | Typical Connection Diagrams                                     | 6    |

|    | 2.1. Power                                                      |      |

| 3. | Electrical Specifications                                       | 8    |

|    | 3.1. Electrical Characteristics                                 |      |

|    | 3.2. Thermal Conditions                                         | . 30 |

|    | 3.3. Absolute Maximum Ratings                                   | .31  |

| 4. | Precision32 <sup>™</sup> SiM3L1xx System Overview               | .32  |

|    | 4.1. Power                                                      |      |

|    | 4.1.1. DC-DC Buck Converter (DCDC0)                             |      |

|    | 4.1.2. Three Low Dropout LDO Regulators (LDO0)                  |      |

|    | 4.1.3. Voltage Supply Monitor (VMON0)                           |      |

|    | 4.1.4. Power Management Unit (PMU)                              | .35  |

|    | 4.1.5. Device Power Modes                                       |      |

|    | 4.1.6. Process/Voltage/Temperature Monitor (TIMER2 and PVTOSC0) | . 38 |

|    | 4.2. I/O                                                        |      |

|    | 4.2.1. General Features                                         |      |

|    | 4.2.2. Crossbar                                                 |      |

|    | 4.3. Clocking                                                   |      |

|    | 4.3.1. PLL (PLL0)                                               |      |

|    | 4.3.2. Low Power Oscillator (LPOSC0)                            |      |

|    | 4.3.3. Low Frequency Oscillator (LFOSC0)                        |      |

|    | 4.3.4. External Oscillators (EXTOSC0)                           |      |

|    | 4.4. Integrated LCD Controller (LCD0)                           |      |

|    | 4.5. Data Peripherals                                           |      |

|    | 4.5.1. 10-Channel DMA Controller                                |      |

|    | 4.5.2. Data Transfer Managers (DTM0, DTM1, DTM2)                | .43  |

|    | 4.5.3. 128/192/256-bit Hardware AES Encryption (AES0)           |      |

|    | 4.5.4. 16/32-bit Enhanced CRC (ECRC0)                           |      |

|    | 4.5.5. Encoder / Decoder (ENCDEC0)                              |      |

|    | 4.6. Counters/Timers                                            |      |

|    | 4.6.1. 32-bit Timer (TIMER0, TIMER1, TIMER2)                    |      |

|    | 4.6.2. Enhanced Programmable Counter Array (EPCA0)              |      |

|    | 4.6.3. Real-Time Clock (RTC0)                                   |      |

|    | 4.6.4. Low Power Timer (LPTIMER0)                               |      |

|    | 4.6.5. Watchdog Timer (WDTIMER0)                                |      |

|    | 4.6.6. Low Power Mode Advanced Capture Counter (ACCTR0)         |      |

|    | 4.7. Communications Peripherals                                 |      |

|    | 4.7.1. USART (USART0)                                           | .48  |

### Table 3.2. Power Consumption

| Parameter                                                                                                        | Symbol           | Test Condition                                                                        | Min | Тур  | Max  | Unit |

|------------------------------------------------------------------------------------------------------------------|------------------|---------------------------------------------------------------------------------------|-----|------|------|------|

| Digital Core Supply Current                                                                                      | • •              |                                                                                       |     | 1    | Ļ    |      |

| Normal Mode <sup>1,2,3,4</sup> —Full speed<br>with code executing from flash,<br>peripheral clocks ON            | I <sub>BAT</sub> | F <sub>AHB</sub> = 49 MHz,<br>F <sub>APB</sub> = 24.5 MHz                             | —   | 17.5 | 18.9 | mA   |

|                                                                                                                  |                  | F <sub>AHB</sub> = 20 MHz,<br>F <sub>APB</sub> = 10 MHz                               | —   | 6.7  | 7.2  | mA   |

|                                                                                                                  |                  | F <sub>AHB</sub> = 2.5 MHz,<br>F <sub>APB</sub> = 1.25 MHz                            | —   | 1.15 | 1.4  | mA   |

| Normal Mode <sup>1,2,3,4</sup> —Full speed<br>with code executing from flash,                                    | I <sub>BAT</sub> | F <sub>AHB</sub> = 49 MHz,<br>F <sub>APB</sub> = 24.5 MHz                             | —   | 13.3 | 14.5 | mA   |

| peripheral clocks OFF                                                                                            |                  | F <sub>AHB</sub> = 20 MHz,<br>F <sub>APB</sub> = 10 MHz                               | —   | 5.4  | 5.9  | mA   |

|                                                                                                                  | -                | F <sub>AHB</sub> = 2.5 MHz,<br>F <sub>APB</sub> = 1.25 MHz                            | _   | 980  | 1.2  | μA   |

| Normal Mode <sup>1,2,3,4</sup> —Full speed<br>with code executing from flash,<br>LDOs powered by dc-dc at 1.9 V, | I <sub>BAT</sub> | F <sub>AHB</sub> = 49 MHz,<br>F <sub>APB</sub> = 24.5 MHz<br>V <sub>BAT</sub> = 3.3 V |     | 9.7  |      | mA   |

| peripheral clocks OFF                                                                                            |                  | F <sub>AHB</sub> = 49 MHz,<br>F <sub>APB</sub> = 24.5 MHz<br>V <sub>BAT</sub> = 3.8 V |     | 8.65 |      | mA   |

|                                                                                                                  |                  | F <sub>AHB</sub> = 20 MHz,<br>F <sub>APB</sub> = 10 MHz<br>V <sub>BAT</sub> = 3.3 V   | _   | 4.15 | _    | mA   |

|                                                                                                                  |                  | F <sub>AHB</sub> = 20 MHz,<br>F <sub>APB</sub> = 10 MHz<br>V <sub>BAT</sub> = 3.8 V   | _   | 3.9  | _    | mA   |

### Notes:

1. Currents are additive. For example, where I<sub>BAT</sub> is specified and the mode is not mutually exclusive, enabling the functions increases supply current by the specified amount.

2. Includes all peripherals that cannot have clocks gated in the Clock Control module.

- 3. Includes LDO and PLL0OSC (>20 MHz) or LPOSC0 (<20 MHz) supply current.

- **4.** Internal Digital and Memory LDOs scaled to optimal output voltage.

- 5. Flash AHB clock turned off.

- 6. Running from internal LFO, Includes LFO supply current.

- 7. LCD0 current does not include switching currents for external load.

- 8. IDAC output current not included.

- 9. Does not include LC tank circuit.

- Does not include digital drive current or pullup current for active port I/O. Unloaded I<sub>VIO</sub> is included in all I<sub>BAT</sub> PM8 production test measurements.

### Table 3.2. Power Consumption (Continued)

| Parameter                                                                                                       | Symbol           | Test Condition                                                                        | Min | Тур  | Max  | Unit |

|-----------------------------------------------------------------------------------------------------------------|------------------|---------------------------------------------------------------------------------------|-----|------|------|------|

| Power Mode 1 <sup>1,2,3,4</sup> —Full speed<br>with code executing from RAM,                                    | I <sub>BAT</sub> | F <sub>AHB</sub> = 49 MHz,<br>F <sub>APB</sub> = 24.5 MHz                             | —   | 13.4 | 16.6 | mA   |

| peripheral clocks ON                                                                                            |                  | F <sub>AHB</sub> = 20 MHz,<br>F <sub>APB</sub> = 10 MHz                               | —   | 4.7  |      | mA   |

|                                                                                                                 |                  | F <sub>AHB</sub> = 2.5 MHz,<br>F <sub>APB</sub> = 1.25 MHz                            | _   | 810  |      | μA   |

| Power Mode 1 <sup>1,2,3,4</sup> —Full speed<br>with code executing from RAM,                                    | I <sub>BAT</sub> | F <sub>AHB</sub> = 49 MHz,<br>F <sub>APB</sub> = 24.5 MHz                             |     | 9.4  | 12.5 | mA   |

| peripheral clocks OFF                                                                                           |                  | F <sub>AHB</sub> = 20 MHz,<br>F <sub>APB</sub> = 10 MHz                               | —   | 3.3  | _    | mA   |

|                                                                                                                 |                  | F <sub>AHB</sub> = 2.5 MHz,<br>F <sub>APB</sub> = 1.25 MHz                            | —   | 630  | _    | μA   |

| Power Mode 1 <sup>1,2,3,4</sup> —Full speed<br>with code executing from RAM,<br>LDOs powered by dc-dc at 1.9 V, | I <sub>BAT</sub> | F <sub>AHB</sub> = 49 MHz,<br>F <sub>APB</sub> = 24.5 MHz<br>V <sub>BAT</sub> = 3.3 V | _   | 7.05 |      | mA   |

| peripheral clocks OFF                                                                                           |                  | F <sub>AHB</sub> = 49 MHz,<br>F <sub>APB</sub> = 24.5 MHz<br>V <sub>BAT</sub> = 3.8 V |     | 6.3  | _    | mA   |

|                                                                                                                 |                  | F <sub>AHB</sub> = 20 MHz,<br>F <sub>APB</sub> = 10 MHz<br>V <sub>BAT</sub> = 3.3 V   | _   | 2.75 | —    | mA   |

|                                                                                                                 |                  | F <sub>AHB</sub> = 20 MHz,<br>F <sub>APB</sub> = 10 MHz<br>V <sub>BAT</sub> = 3.8 V   | _   | 2.6  | —    | mA   |

| Power Mode 2 <sup>1,2,3,4,5</sup> —Core halted with peripheral clocks ON                                        | I <sub>BAT</sub> | F <sub>AHB</sub> = 49 MHz,<br>F <sub>APB</sub> = 24.5 MHz                             | —   | 7.6  | 11.3 | mA   |

|                                                                                                                 |                  | F <sub>AHB</sub> = 20 MHz,<br>F <sub>APB</sub> = 10 MHz                               | _   | 2.75 |      | mA   |

|                                                                                                                 |                  | F <sub>AHB</sub> = 2.5 MHz,<br>F <sub>APB</sub> = 1.25 MHz                            | _   | 575  | _    | μA   |

Notes:

- 1. Currents are additive. For example, where I<sub>BAT</sub> is specified and the mode is not mutually exclusive, enabling the functions increases supply current by the specified amount.

- 2. Includes all peripherals that cannot have clocks gated in the Clock Control module.

- 3. Includes LDO and PLL0OSC (>20 MHz) or LPOSC0 (<20 MHz) supply current.

- 4. Internal Digital and Memory LDOs scaled to optimal output voltage.

- 5. Flash AHB clock turned off.

- 6. Running from internal LFO, Includes LFO supply current.

- 7. LCD0 current does not include switching currents for external load.

- **8.** IDAC output current not included.

- 9. Does not include LC tank circuit.

- Does not include digital drive current or pullup current for active port I/O. Unloaded I<sub>VIO</sub> is included in all I<sub>BAT</sub> PM8 production test measurements.

# Table 3.3. Power Mode Wake Up Times

| Parameter                                                                           | Symbol             | Test Condition | Min | Тур | Max | Unit      |

|-------------------------------------------------------------------------------------|--------------------|----------------|-----|-----|-----|-----------|

| Power Mode 2 or 6 Wake Time                                                         | t <sub>PM2</sub>   |                | 4   | —   | 5   | clocks    |

| Power Mode 3 Fast Wake Time<br>(using LFO as clock source)                          | t <sub>PM3FW</sub> |                | _   | 425 | _   | μs        |

| Power Mode 8 Wake Time                                                              | t <sub>PM8</sub>   |                |     | 3.8 |     | μs        |

| Notes:<br>1. Wake times are specified as the t<br>This includes latency to recogniz |                    |                | •   |     |     | wing WFI. |

# Table 3.4. Reset and Supply Monitor

| Parameter                                                            | Symbol              | Test Condition                                                | Min  | Тур  | Max  | Unit |

|----------------------------------------------------------------------|---------------------|---------------------------------------------------------------|------|------|------|------|

| V <sub>BAT</sub> High Supply Monitor Threshold                       | V <sub>VBATMH</sub> | Early Warning                                                 | _    | 2.20 | —    | V    |

| (VBATHITHEN = 1)                                                     |                     | Reset                                                         | 1.95 | 2.05 | 2.1  | V    |

| V <sub>BAT</sub> Low Supply Monitor Threshold                        | V <sub>VBATML</sub> | Early Warning                                                 | —    | 1.85 | —    | V    |

| (VBATHITHEN = 0)                                                     |                     | Reset                                                         | 1.70 | 1.75 | 1.77 | V    |

| Power-On Reset (POR) Threshold                                       | V <sub>POR</sub>    | Rising Voltage on $V_{BAT}$                                   | _    | 1.4  | —    | V    |

|                                                                      |                     | Falling Voltage on<br>V <sub>BAT</sub>                        | 0.8  | 1    | 1.3  | V    |

| V <sub>BAT</sub> Ramp Time                                           | t <sub>RMP</sub>    | Time to $V_{BAT} \ge 1.8 \text{ V}$                           | 10   |      | 3000 | μs   |

| Reset Delay from POR                                                 | t <sub>POR</sub>    | Relative to V <sub>BAT</sub> ≥<br>V <sub>POR</sub>            | 3    | _    | 100  | ms   |

| Reset Delay from non-POR source                                      | t <sub>RST</sub>    | Time between release<br>of reset source and<br>code execution | —    | 10   | _    | μs   |

| RESET Low Time to Generate Reset                                     | t <sub>RSTL</sub>   |                                                               | 50   | _    | —    | ns   |

| Missing Clock Detector Response<br>Time (final rising edge to reset) | t <sub>MCD</sub>    | F <sub>AHB</sub> > 1 MHz                                      | —    | 0.5  | 1.5  | ms   |

| Missing Clock Detector Trigger<br>Frequency                          | F <sub>MCD</sub>    |                                                               | —    | 2.5  | 10   | kHz  |

| V <sub>BAT</sub> Supply Monitor Turn-On Time                         | t <sub>MON</sub>    |                                                               | —    | 2    |      | μs   |

### Table 3.9. SAR ADC

| Parameter                    | Symbol              | Test Condition                                                  | Min | Тур   | Max                                      | Unit |

|------------------------------|---------------------|-----------------------------------------------------------------|-----|-------|------------------------------------------|------|

| Resolution                   | N <sub>bits</sub>   | 12 Bit Mode                                                     |     | 12    |                                          | Bits |

|                              |                     | 10 Bit Mode                                                     |     | 10    |                                          | Bits |

| Supply Voltage Requirements  | V <sub>ADC</sub>    | High Speed Mode                                                 | 2.2 |       | 3.8                                      | V    |

| (VBAT)                       |                     | Low Power Mode                                                  | 1.8 |       | 3.8                                      | V    |

| Throughput Rate              | f <sub>S</sub>      | 12 Bit Mode                                                     |     |       | 250                                      | ksps |

| (High Speed Mode)            |                     | 10 Bit Mode                                                     |     |       | 1                                        | Msps |

| Throughput Rate              | f <sub>S</sub>      | 12 Bit Mode                                                     |     |       | 62.5                                     | ksps |

| (Low Power Mode)             |                     | 10 Bit Mode                                                     |     |       | 250                                      | ksps |

| Tracking Time                | t <sub>TRK</sub>    | High Speed Mode                                                 | 230 |       |                                          | ns   |

|                              |                     | Low Power Mode                                                  | 450 |       |                                          | ns   |

| SAR Clock Frequency          | f <sub>SAR</sub>    | High Speed Mode                                                 |     |       | 16.24                                    | MHz  |

|                              |                     | Low Power Mode                                                  |     |       | 4                                        | MHz  |

| Conversion Time              | t <sub>CNV</sub>    | 10-Bit Conversion,<br>SAR Clock = 16 MHz,<br>APB Clock = 40 MHz |     | 762.5 |                                          |      |

| Sample/Hold Capacitor        | C <sub>SAR</sub>    | Gain = 1                                                        | _   | 5     | _                                        | pF   |

|                              |                     | Gain = 0.5                                                      |     | 2.5   |                                          | pF   |

| Input Pin Capacitance        | C <sub>IN</sub>     | High Quality Inputs                                             |     | 18    | —                                        | pF   |

|                              |                     | Normal Inputs                                                   |     | 20    | —                                        | pF   |

| Input Mux Impedance          | R <sub>MUX</sub>    | High Quality Inputs                                             |     | 300   | —                                        | Ω    |

|                              |                     | Normal Inputs                                                   |     | 550   | _                                        | Ω    |

| Voltage Reference Range      | V <sub>REF</sub>    |                                                                 | 1   |       | V <sub>BAT</sub>                         | V    |

| Input Voltage Range*         | V <sub>IN</sub>     | Gain = 1                                                        | 0   |       | V <sub>REF</sub>                         | V    |

|                              |                     | Gain = 0.5                                                      | 0   | _     | $2 \mathrm{x} \mathrm{V}_{\mathrm{REF}}$ | V    |

| Power Supply Rejection Ratio | PSRR <sub>ADC</sub> |                                                                 | _   | 70    | —                                        | dB   |

| DC Performance               |                     |                                                                 |     |       |                                          |      |

| Integral Nonlinearity        | INL                 | 12 Bit Mode                                                     | —   | ±1    | ±1.9                                     | LSB  |

|                              |                     | 10 Bit Mode                                                     |     | ±0.2  | ±0.5                                     | LSB  |

| Differential Nonlinearity    | DNL                 | 12 Bit Mode                                                     | -1  | ±0.7  | 1.8                                      | LSB  |

| (Guaranteed Monotonic)       |                     | 10 Bit Mode                                                     |     | ±0.2  | ±0.5                                     | LSB  |

| Offset Error (using VREFGND) | E <sub>OFF</sub>    | 12 Bit Mode, VREF = 2.4 V                                       | -2  | 0     | 2                                        | LSB  |

|                              |                     | 10 Bit Mode, VREF = 2.4 V                                       | -1  | 0     | 1                                        | LSB  |

### Table 3.10. IDAC

| Parameter                                           | Symbol            | Test Condition                          | Min  | Тур   | Max                       | Unit   |

|-----------------------------------------------------|-------------------|-----------------------------------------|------|-------|---------------------------|--------|

| Static Performance                                  | <u> </u>          |                                         |      | I.    | 1                         |        |

| Resolution                                          | N <sub>bits</sub> |                                         |      | 10    |                           | Bits   |

| Integral Nonlinearity                               | INL               |                                         |      | ±0.5  | ±2                        | LSB    |

| Differential Nonlinearity (Guaranteed<br>Monotonic) | DNL               |                                         |      | ±0.5  | ±1                        | LSB    |

| Output Compliance Range                             | V <sub>OCR</sub>  |                                         |      |       | V <sub>BAT</sub> –<br>1.0 | V      |

| Full Scale Output Current                           | I <sub>OUT</sub>  | 2 mA Range,<br>T <sub>A</sub> = 25 °C   | 1.98 | 2.046 | 2.1                       | mA     |

|                                                     |                   | 1 mA Range,<br>T <sub>A</sub> = 25 °C   | 0.99 | 1.023 | 1.05                      | mA     |

|                                                     |                   | 0.5 mA Range,<br>T <sub>A</sub> = 25 °C | 491  | 511.5 | 525                       | μA     |

| Offset Error                                        | E <sub>OFF</sub>  |                                         |      | 250   |                           | nA     |

| Full Scale Error Tempco                             | TC <sub>FS</sub>  | 2 mA Range                              |      | 100   |                           | ppm/°C |

| VBAT Power Supply Rejection Ratio                   |                   | 2 mA Range                              |      | -220  |                           | ppm/V  |

| Test Load Impedance (to V <sub>SS</sub> )           | R <sub>TEST</sub> |                                         |      | 1     |                           | kΩ     |

| Dynamic Performance                                 | 1                 |                                         |      |       |                           |        |

| Output Settling Time to 1/2 LSB                     |                   | min output to max<br>output             | _    | 1.2   | —                         | μs     |

| Startup Time                                        |                   |                                         |      | 3     | —                         | μs     |

Table 3.11. ACCTR (Advanced Capture Counter)

| Parameter                                               | Symbol             | Test Condition       | Min | Тур   | Max | Unit |

|---------------------------------------------------------|--------------------|----------------------|-----|-------|-----|------|

| LC Comparator Response Time,                            | t <sub>RESP0</sub> | +100 mV Differential |     | 100   | _   | ns   |

| CMPMD = 11<br>(Highest Speed)                           |                    | –100 mV Differential |     | 150   |     | ns   |

| LC Comparator Response Time,                            | t <sub>RESP3</sub> | +100 mV Differential | —   | 1.4   | _   | μs   |

| CMPMD = 00<br>(Lowest Power)                            |                    | -100 mV Differential |     | 3.5   |     | μs   |

| LC Comparator Positive Hysteresis                       | HYS <sub>CP+</sub> | CMPHYP = 00          |     | 0.37  |     | mV   |

| Mode 0 (CPMD = 11)                                      |                    | CMPHYP = 01          | —   | 7.9   | _   | mV   |

|                                                         |                    | CMPHYP = 10          |     | 16.7  | _   | mV   |

|                                                         |                    | CMPHYP = 11          |     | 32.8  | —   | mV   |

| LC Comparator Negative Hysteresis                       | HYS <sub>CP-</sub> | CMPHYN = 00          |     | 0.37  |     | mV   |

| Mode 0 (CPMD = 11)                                      |                    | CMPHYN = 01          |     | -7.9  | _   | mV   |

|                                                         |                    | CMPHYN = 10          |     | -16.1 | —   | mV   |

|                                                         |                    | CMPHYN = 11          |     | -32.7 | _   | mV   |

| LC Comparator Positive Hysteresis<br>Mode 1 (CPMD = 10) | HYS <sub>CP+</sub> | CMPHYP = 00          |     | 0.47  | _   | mV   |

|                                                         |                    | CMPHYP = 01          |     | 5.85  | _   | mV   |

|                                                         |                    | CMPHYP = 10          |     | 12    | _   | mV   |

|                                                         |                    | CMPHYP = 11          | —   | 24.4  |     | mV   |

| LC Comparator Negative Hysteresis                       | HYS <sub>CP-</sub> | CMPHYN = 00          |     | 0.47  | —   | mV   |

| Mode 1 (CPMD = 10)                                      |                    | CMPHYN = 01          |     | -6.0  |     | mV   |

|                                                         |                    | CMPHYN = 10          |     | -12.1 |     | mV   |

|                                                         |                    | CMPHYN = 11          |     | -24.6 |     | mV   |

| LC Comparator Positive Hysteresis                       | HYS <sub>CP+</sub> | CMPHYP = 00          |     | 0.66  |     | mV   |

| Mode 2 (CPMD = 01)                                      |                    | CMPHYP = 01          |     | 4.55  |     | mV   |

|                                                         |                    | CMPHYP = 10          |     | 9.3   | _   | mV   |

|                                                         |                    | CMPHYP = 11          |     | 19    |     | mV   |

| LC Comparator Negative Hysteresis                       | HYS <sub>CP-</sub> | CMPHYN = 00          |     | 0.6   | _   | mV   |

| Mode 2 (CPMD = 01)                                      |                    | CMPHYN = 01          |     | -4.5  | —   | mV   |

|                                                         |                    | CMPHYN = 10          |     | -9.5  |     | mV   |

|                                                         |                    | CMPHYN = 11          |     | -19   |     | mV   |

# Table 3.14. Comparator (Continued)

| Parameter                    | Symbol             | Test Condition         | Min   | Тур  | Max                        | Unit  |

|------------------------------|--------------------|------------------------|-------|------|----------------------------|-------|

| Positive Hysteresis          | HYS <sub>CP+</sub> | CMPHYP = 00            |       | 1.37 |                            | mV    |

| Mode 3 (CPMD = 11)           |                    | CMPHYP = 01            | _     | 3.8  | —                          | mV    |

|                              |                    | CMPHYP = 10            |       | 7.8  |                            | mV    |

|                              |                    | CMPHYP = 11            |       | 15.6 |                            | mV    |

| Negative Hysteresis          | HYS <sub>CP-</sub> | CMPHYN = 00            |       | 1.37 |                            | mV    |

| Mode 3 (CPMD = 11)           |                    | CMPHYN = 01            |       | -3.9 |                            | mV    |

|                              |                    | CMPHYN = 10            |       | -7.9 |                            | mV    |

|                              |                    | CMPHYN = 11            |       | -16  |                            | mV    |

| Input Range (CP+ or CP–)     | V <sub>IN</sub>    |                        | -0.25 |      | V <sub>BAT</sub> +<br>0.25 | V     |

| Input Pin Capacitance        | C <sub>CP</sub>    |                        |       | 7.5  |                            | pF    |

| Common-Mode Rejection Ratio  | CMRR <sub>CP</sub> |                        |       | 75   |                            | dB    |

| Power Supply Rejection Ratio | PSRR <sub>CP</sub> |                        |       | 72   |                            | dB    |

| Input Offset Voltage         | V <sub>OFF</sub>   | T <sub>A</sub> = 25 °C | -10   | 0    | 10                         | mV    |

| Input Offset Tempco          | TC <sub>OFF</sub>  |                        | _     | 3.5  | —                          | µV/°C |

| Reference DAC Resolution     | N <sub>Bits</sub>  |                        |       | 6    |                            | bits  |

# Table 3.15. LCD0

| Parameter                        | Symbol             | Test Condition | Min | Тур | Max | Unit |

|----------------------------------|--------------------|----------------|-----|-----|-----|------|

| Charge Pump Output Voltage Error | V <sub>CPERR</sub> |                |     | ±50 | _   | mV   |

| LCD Clock Frequency              | F <sub>LCD</sub>   |                | 16  |     | 33  | kHz  |

# Table 3.16. Port I/O

| Parameter                                                    | Symbol          | Test Condition                                 | Min                     | Тур  | Max | Unit |

|--------------------------------------------------------------|-----------------|------------------------------------------------|-------------------------|------|-----|------|

| Output High Voltage (PB0, PB1,                               | V <sub>OH</sub> | Low Drive, I <sub>OH</sub> = -1 mA             | V <sub>IO</sub> – 0.7   | _    |     | V    |

| PB3, or PB4)                                                 |                 | Low Drive, $I_{OH} = -10 \ \mu A$              | V <sub>IO</sub> – 0.1   | _    |     | V    |

|                                                              |                 | High Drive, $I_{OH} = -3 \text{ mA}$           | V <sub>IO</sub> – 0.7   | —    | _   | V    |

|                                                              |                 | High Drive, $I_{OH} = -10 \ \mu A$             | V <sub>IO</sub> – 0.1   | _    | —   | V    |

| Output High Voltage (PB2)                                    | V <sub>OH</sub> | Low Drive, $I_{OH} = -1 \text{ mA}$            | $V_{IORF} - 0.7$        | _    | —   | V    |

|                                                              |                 | Low Drive, $I_{OH} = -10 \ \mu A$              | $V_{IORF} - 0.1$        | —    | —   | V    |

|                                                              |                 | High Drive, I <sub>OH</sub> = -3 mA            | $V_{IORF} - 0.7$        | _    | —   | V    |

|                                                              |                 | High Drive, $I_{OH} = -10 \ \mu A$             | V <sub>IORF</sub> - 0.1 | _    | —   | V    |

| Output Low Voltage (any Port I/O                             | V <sub>OL</sub> | Low Drive, I <sub>OL</sub> = 1.4 mA            | —                       | _    | 0.6 | V    |

| pin or $\overline{RESET}^1$ )                                |                 | Low Drive, $I_{OL} = 10 \ \mu A$               | —                       | _    | 0.1 | V    |

|                                                              |                 | High Drive, I <sub>OL</sub> = 8.5 mA           | —                       | _    | 0.6 | V    |

|                                                              |                 | High Drive, I <sub>OL</sub> = 10 µA            | —                       | _    | 0.1 | V    |

| Input High Vo <u>ltage (P</u> B0, PB1,<br>PB3, PB4 or RESET) | V <sub>IH</sub> |                                                | V <sub>IO</sub> – 0.6   |      | _   | V    |

| Input High Voltage (PB2)                                     | V <sub>IH</sub> |                                                | V <sub>IORF</sub> - 0.6 | _    |     | V    |

| Input Low Voltage any Port I/O pin or RESET)                 | V <sub>IL</sub> |                                                | —                       | _    | 0.6 | V    |

| Weak Pull-Up Current <sup>2</sup> (per pin)                  | I <sub>PU</sub> | V <sub>IO</sub> or V <sub>IORF</sub> = 1.8     | -6                      | -3.5 | -2  | μA   |

|                                                              |                 | V <sub>IO</sub> or V <sub>IORF</sub> = 3.8     | -32                     | -20  | -10 | μA   |

| Input Leakage<br>(Pullups off or Analog)                     | I <sub>LK</sub> | $0 \le V_{IN} \le V_{IO} \text{ or } V_{IORF}$ | -1                      |      | 1   | μA   |

Notes:

Specifications for RESET V<sub>OL</sub> adhere to the low drive setting.

On the SiM3L1x6 and SiM3L1x4 devices, the SWV pin will have double the weak pull-up current specified whenever the device is held in reset.

### 4.1.5.6. Power Mode Summary

The power modes described above are summarized in Table 4.1. Table 3.2 and Table 3.3 provide more information on the power consumption and wake up times for each mode.

| Mode               | Description                                                                                                                                                                                                                                                                                                         | Notes                                                                                                                                                                                                                                          |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Normal             | <ul><li>Core operating at full speed</li><li>Code executing from flash</li></ul>                                                                                                                                                                                                                                    | <ul> <li>Full device operation</li> </ul>                                                                                                                                                                                                      |

| Power Mode 1 (PM1) | <ul> <li>Core operating at full speed</li> <li>Code executing from RAM</li> </ul>                                                                                                                                                                                                                                   | <ul> <li>Full device operation</li> <li>Higher CPU bandwidth than PM0 (RAM can operate with zero wait states at any frequency)</li> </ul>                                                                                                      |

| Power Mode 2 (PM2) | <ul> <li>Core halted</li> <li>AHB, APB and all peripherals operational at full speed</li> </ul>                                                                                                                                                                                                                     | <ul> <li>Fast wakeup from any interrupt source</li> </ul>                                                                                                                                                                                      |

| Power Mode 3 (PM3) | <ul> <li>All clocks to core and peripherals<br/>stopped</li> <li>Faster wake enabled by keeping<br/>LFOSC0 or RTC0TCLK active</li> </ul>                                                                                                                                                                            | <ul> <li>Wake on any wake source or reset<br/>source defined in the PMU</li> </ul>                                                                                                                                                             |

| Power Mode 4 (PM4) | <ul> <li>Core operating at low speed</li> <li>Code executing from flash</li> </ul>                                                                                                                                                                                                                                  | <ul> <li>Same capabilities as PM0, operating at lower speed</li> <li>Lower clock speed enables lower LDO output settings to save power</li> </ul>                                                                                              |

| Power Mode 5 (PM5) | <ul> <li>Core operating at low speed</li> <li>Code executing from RAM</li> </ul>                                                                                                                                                                                                                                    | <ul> <li>Same capabilities as PM1, operating at lower speed</li> <li>Lower clock speed enables lower LDO output settings to save power</li> </ul>                                                                                              |

| Power Mode 6 (PM6) | <ul> <li>Core halted</li> <li>AHB, APB and all peripherals operational at low speed</li> </ul>                                                                                                                                                                                                                      | <ul> <li>Same capabilities as PM2, operating at lower speed</li> <li>Lower clock speed enables lower LDO output settings to save power</li> <li>When running from LFOSC0, power is similar to PM3, but the device wakes much faster</li> </ul> |

| Power Mode 8 (PM8) | <ul> <li>Low power sleep</li> <li>LDO regulators are disabled and all active circuitry operates directly from VBAT</li> <li>The following functions are available:<br/>ACCTR0, RTC0, UART0 running from RTC0TCLK, LPTIMER0, port match, and the LCD controller</li> <li>Register and RAM state retention</li> </ul> | <ul> <li>Lowest power consumption</li> <li>Wake on any wake source or reset<br/>source defined in the PMU</li> </ul>                                                                                                                           |

### Table 4.1. SiM3L1xx Power Modes

# 4.4. Integrated LCD Controller (LCD0)

SiM3L1xx devices contain an LCD segment driver and on-chip bias generation that supports static, 2-mux, 3-mux and 4-mux LCDs with 1/2 or 1/3 bias. The on-chip charge pump with programmable output voltage allows software contrast control which is independent of the supply voltage. LCD timing is derived from the RTC timer clock (RTC0TCLK) to allow precise control over the refresh rate.

The SiM3L1xx devices use registers to store the enabled/disabled state of individual LCD segments. All LCD waveforms are generated on-chip based on the contents of these registers with flexible waveform control to reduce power consumption wherever possible. An LCD blinking function is also supported on a subset of LCD segments.

The LCD0 module has the following features:

- Up to 40 segment pins and 4 common pins.

- Supports LCDs with 1/2 or 1/3 bias.

- Includes an on-chip charge pump with programmable output that allows firmware to control the contrast independent of the supply voltage.

- The RTC timer clock (RTC0TCLK) determines the LCD timing and refresh rate.

- All LCD waveforms are generated on-chip based on the contents of the LCD0 registers with flexible waveform control.

- LCD segments can be placed in a discharge state for a configurable number of RTC clock cycles before switching to the next state to reduce power consumption due to display loading.

- Includes a VBAT monitor that can serve as a wakeup source for Power Mode 8.

- Supports four hardware auto-contrast modes: bypass, constant, minimum, and auto-bypass.

- Supports hardware blinking for up to 8 segments.

### 4.6.3. Real-Time Clock (RTC0)

The RTC module includes a 32-bit timer that allows up to 36 hours of independent time-keeping when used with a 32.768 kHz watch crystal. The RTC provides three alarm events in addition to a missing clock event, which can also function as interrupt, reset, or wakeup sources on SiM3L1xx devices.

The RTC module includes internal loading capacitors that are programmable to 16 discrete levels, allowing compatibility with a wide range of crystals.

The RTC timer clock can be buffered and routed to a port bank pin to provide an accurate, low frequency clock to other devices while the core is in its lowest power down mode. The module also includes a low power internal low frequency oscillator that reduces low power mode current and is available for other modules to use as a clock source.

The RTC module includes the following features:

- 32-bit timer (supports up to 36 hours) with three separate alarms.

- Option for one alarm to automatically reset the RTC timer.

- Missing clock detector.

- Can be used with the internal Low Frequency Oscillator or with an external 32.768 kHz crystal (no additional resistors or capacitors necessary).

- Programmable internal loading capacitors support a wide range of external 32.768 kHz crystals.

- The RTC timer clock (RTC0CLK) can be buffered and routed to an I/O pin to provide an accurate, low frequency clock to other devices while the core is in its lowest power down mode.

- The RTC module can be powered from the low power mode charge pump for lowest possible power consumption while in PM8.

#### 4.6.4. Low Power Timer (LPTIMER0)

The Low Power Timer (LPTIMER) module runs from the RTC timer clock (RTC0CLK), allowing the LPTIMER to operate even if the AHB and APB clocks are disabled. The LPTIMER counter can increment using one of two clock sources: the clock selected by the RTC0 module, or rising or falling edges of an external signal.

The Low Power Timer includes the following features:

- Runs on low-frequency RTC timer clock (RTC0TCLK).

- The LPTIMER counter can increment using one of two clock sources: the RTC0TCLK or rising or falling edges of an external signal.

- Overflow and threshold-match detection.

- Timer reset on threshold-match allows square-wave generation at a variable output frequency.

- Supports PWM with configurable period and duty cycle.

- The LPTIMER module can be powered from the low power mode charge pump for lowest possible power consumption while in PM8.

#### 4.6.5. Watchdog Timer (WDTIMER0)

The WDTIMER module includes a 16-bit timer, a programmable early warning interrupt, and a programmable reset period. The timer registers are protected from inadvertent access by an independent lock and key interface.

The watchdog timer runs from the low frequency oscillator (LFOSC0).

The Watchdog Timer has the following features:

- Programmable timeout interval.

- Optional interrupt to warn when the Watchdog Timer is nearing the reset trip value.

- Lock-out feature to prevent any modification until a system reset.

### 4.6.6. Low Power Mode Advanced Capture Counter (ACCTR0)

The SiM3L1xx devices contain a low-power Advanced Capture Counter module that runs from the RTC0 clock domain and can be used with digital inputs, switch topology circuits (reed switches), or with LC resonant circuits. For switch topology circuits, the module charges one or two external lines by pulsing internal pull-up resistors and detecting whether the reed switch is open or closed. For LC resonant circuits, the inputs are periodically energized to produce a dampened sine wave and configurable discriminator circuits detect the resulting decay time-constant.

The advanced capture counter has the following general features:

- Single or differential inputs supporting single, dual, and quadrature modes of operation.

- Variety of interrupt and PM8 wake up sources.

- Provides feedback of the direction history, current and previous states, and condition flags.

The advanced capture counter has the following features for switch circuit topologies:

- Ultra low power input comparators.

- Supports a wide range of pull-up resistor values with a self-calibration engine.

- Asymmetrical integrators for low-pass filtering and switch debounce.

- Two 24-bit counters and two 24-bit digital threshold comparators.

- Supports switch flutter detection.

For LC resonant circuit topologies, the advanced capture counter includes:

- Separate minimum and maximum count registers and polarity, pulse, and toggle controls.

- Zone-based programmable timing.

- Two input comparators with support for a positive side input bias at VIO divided by 2.

- Supports a configurable excitation pulse width based on a 40 MHz oscillator and timer or an external digital stop signal.

- Two 8-bit peak counters that saturate at full scale for detecting the number of LC resonant peaks.

- Two discriminators with programmable thresholds.

- Supports a sample and hold mode for Wheatstone bridges.

All devices in the SiM3L1xx family include the low power mode advanced capture counter (ACCTR0). Table 4.2 lists the supported inputs and outputs for each of the packages.

### Table 4.2. SiM3L1xx Supported Advanced Capture Counter Inputs and Outputs

| Input/Output   | SiM3L1x7     | SiM3L1x6     | SiM3L1x4 |

|----------------|--------------|--------------|----------|

| ACCTR0_IN0     | $\checkmark$ | $\checkmark$ | ~        |

| ACCTR0_IN1     | $\checkmark$ | ~            | ~        |

| ACCTR0_LCIN0   | $\checkmark$ | ~            |          |

| ACCTR0_LCIN1   | $\checkmark$ | ~            | ~        |

| ACCTR0_STOP0   | $\checkmark$ | ~            | ~        |

| ACCTR0_STOP1   | $\checkmark$ | ~            | ~        |

| ACCTR0_LCPUL0  | $\checkmark$ | ~            |          |

| ACCTR0_LCPUL1  | $\checkmark$ | ~            |          |

| ACCTR0_LCBIAS0 | $\checkmark$ | ~            |          |

| ACCTR0_LCBIAS1 | $\checkmark$ | ~            |          |

| ACCTR0_DBG0    | V            | $\checkmark$ |          |

| ACCTR0_DBG1    | $\checkmark$ | $\checkmark$ |          |

| Pin Name | Туре         | Pin Numbers (TQFP-80) | I/O Voltage Domain | Crossbar Capability | Port Match   | LCD Interface | Output Toggle Logic | External Trigger Inputs /<br>Digital Functions | Analog Functions              |

|----------|--------------|-----------------------|--------------------|---------------------|--------------|---------------|---------------------|------------------------------------------------|-------------------------------|

| PB0.0    | Standard I/O | 4                     | VIO                | V                   | ~            |               | ~                   | INT0.0<br>WAKE.0                               | ADC0.20<br>VREF<br>CMP0P.0    |

| PB0.1    | Standard I/O | 3                     | VIO                | ~                   | 1            |               | 1                   | INT0.1<br>WAKE.1                               | ADC0.21<br>VREFGND<br>CMP0N.0 |

| PB0.2    | Standard I/O | 2                     | VIO                | ~                   | ~            |               | ~                   | INT0.2<br>WAKE.2                               | ADC0.22<br>CMP1P.0<br>XTAL2   |

| PB0.3    | Standard I/O | 1                     | VIO                | ~                   | ~            |               | ~                   | INT0.3<br>WAKE.3                               | ADC0.23<br>CMP1N.0<br>XTAL1   |

| PB0.4    | Standard I/O | 80                    | VIO                | ~                   | ~            |               | ~                   | INT0.4<br>WAKE.4                               | ADC0.0<br>CMP0P.1<br>IDAC0    |

| PB0.5    | Standard I/O | 79                    | VIO                | ~                   | ~            |               | $\checkmark$        | INT0.5<br>WAKE.5<br>ACCTR0_STOP0               | ACCTR0_IN0                    |

| PB0.6    | Standard I/O | 78                    | VIO                | V                   | ~            |               | ~                   | INT0.6<br>WAKE.6<br>ACCTR0_STOP1               | ACCTR0_IN1                    |

| PB0.7    | Standard I/O | 77                    | VIO                | ~                   | ~            |               | ~                   | INT0.7<br>WAKE.7                               | ACCTR0_LCIN0                  |

| PB0.8    | Standard I/O | 76                    | VIO                | ~                   | $\checkmark$ |               | ~                   | LPT0T0<br>LPT0OUT0<br>INT0.8<br>WAKE.8         | ACCTR0_LCIN1                  |

# Table 6.1. Pin Definitions and Alternate Functions for SiM3L1x7 (Continued)

| Pin Name | Туре         | Pin Numbers | I/O Voltage Domain | Crossbar Capability | Port Match   | Output Toggle Logic | External Trigger Inputs /<br>Digital Functions | Analog Functions  |  |

|----------|--------------|-------------|--------------------|---------------------|--------------|---------------------|------------------------------------------------|-------------------|--|

| PB2.1    | Standard I/O | 28          | VIORF              | XBR0                | ~            |                     | LPT0T9<br>INT1.1<br>WAKE.13<br>VIORFCLK        | ADC0.3<br>CMP0N.4 |  |

| PB2.2    | Standard I/O | 27          | VIORF              | XBR0                | ~            |                     | LPT0T10<br>INT1.2<br>WAKE.14                   | ADC0.4<br>CMP1P.4 |  |

| PB2.3    | Standard I/O | 26          | VIORF              | XBR0                | $\checkmark$ |                     | LPT0T11<br>INT1.3<br>WAKE.15                   | ADC0.5<br>CMP1N.4 |  |

| PB2.4    | Standard I/O | 24          | VIORF              | XBR0                | ~            |                     | LPT0T12<br>INT1.4<br>SPI1_SCLK                 | ADC0.6<br>CMP0P.5 |  |

| PB2.5    | Standard I/O | 23          | VIORF              | XBR0                | ~            |                     | LPT0T13<br>INT1.5<br>SPI1_MISO                 | ADC0.7<br>CMP0N.5 |  |

| PB2.6    | Standard I/O | 22          | VIORF              | XBR0                | ~            |                     | LPT0T14<br>INT1.6<br>SPI1_MOSI                 | ADC0.8<br>CMP1P.5 |  |

| PB2.7    | Standard I/O | 21          | VIORF              | XBR0                | ~            |                     | INT1.7<br>SPI1_NSS                             | ADC0.9<br>CMP1N.5 |  |

| PB3.0    | Standard I/O | 20          | VIO                | XBR0                | $\checkmark$ |                     | INT1.8                                         | CMP0N.7           |  |

| PB3.1    | Standard I/O | 19          | VIO                | XBR0                | $\checkmark$ |                     | INT1.9                                         | CMP1P.7           |  |

| PB3.2    | Standard I/O | 18          | VIO                | XBR0                | $\checkmark$ |                     | INT1.10                                        | CMP1N.7           |  |

| PB3.3    | Standard I/O | 17          | VIO                | XBR0                | $\checkmark$ |                     | INT1.11                                        | ADC0.10           |  |

| PB3.4    | Standard I/O | 16          | VIO                | XBR0                | $\checkmark$ |                     | INT1.12                                        | ADC0.11           |  |

| PB3.5    | Standard I/O | 15          | VIO                | XBR0                | $\checkmark$ |                     | INT1.13                                        | ADC0.12           |  |

# Table 6.3. Pin Definitions and Alternate Functions for SiM3L1x4 (Continued)

| Dimension | Min       | Nominal   | Мах  |  |  |

|-----------|-----------|-----------|------|--|--|

| A         | _         | —         | 1.20 |  |  |

| A1        | 0.05      | —         | 0.15 |  |  |

| A2        | 0.95      | 1.00      | 1.05 |  |  |

| b         | 0.17      | 0.22      | 0.27 |  |  |

| С         | 0.09      | —         | 0.20 |  |  |

| D         |           | 12.00 BSC |      |  |  |

| D1        |           | 10.00 BSC |      |  |  |

| е         | 0.50 BSC  |           |      |  |  |

| E         | 12.00 BSC |           |      |  |  |

| E1        | 10.00 BSC |           |      |  |  |

| L         | 0.45      | 0.60      | 0.75 |  |  |

| Θ         | 0°        | 3.5°      | 7°   |  |  |

| aaa       | _         |           | 0.20 |  |  |

| bbb       | —         | —         | 0.20 |  |  |

| ccc       | —         | —         | 0.08 |  |  |

| ddd       | _         | _         | 0.08 |  |  |

Table 6.8. TQFP-64 Package Dimensions

**4.** Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

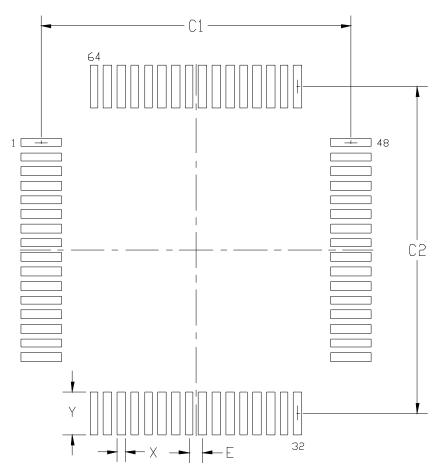

Figure 6.10. TQFP-64 Landing Diagram

| Table 6.9. TQFP-64 Landing Dia | agram Dimensions |

|--------------------------------|------------------|

|--------------------------------|------------------|

| Dimension                                                                                                                                                                             | Min      | Мах   |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------|--|--|--|--|

| C1                                                                                                                                                                                    | 11.30    | 11.40 |  |  |  |  |

| C2                                                                                                                                                                                    | 11.30    | 11.40 |  |  |  |  |

| E                                                                                                                                                                                     | 0.50 BSC |       |  |  |  |  |

| Х                                                                                                                                                                                     | 0.20     | 0.30  |  |  |  |  |

| Y 1.40 1.50                                                                                                                                                                           |          |       |  |  |  |  |

| <ul> <li>Notes:</li> <li>1. All dimensions shown are in millimeters (mm) unless otherwise noted.</li> <li>2. This land pattern design is based on the IPC-7351 guidelines.</li> </ul> |          |       |  |  |  |  |

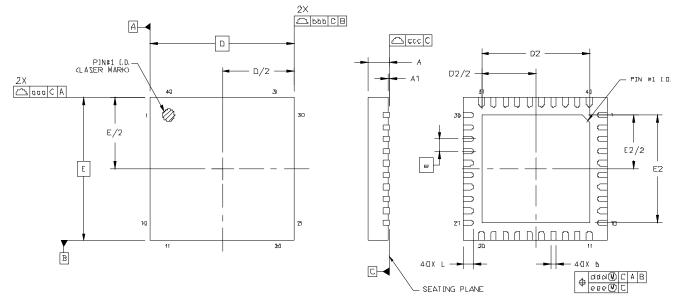

### 6.7. QFN-40 Package Specifications

| Dimension | Min            | Nominal | Max  |  |  |

|-----------|----------------|---------|------|--|--|

| A         | 0.80           | 0.85    | 0.90 |  |  |

| A1        | 0.00           | 0.02    | 0.05 |  |  |

| b         | 0.18           | 0.25    | 0.30 |  |  |

| D         | 6.00 BSC       |         |      |  |  |

| D2        | 4.35 4.50 4.65 |         |      |  |  |

| e         | 0.50 BSC       |         |      |  |  |

| E         | 6.00 BSC       |         |      |  |  |

| E2        | 4.35 4.5 4.65  |         |      |  |  |

| L         | 0.30 0.40 0.50 |         |      |  |  |

| aaa       | 0.10           |         |      |  |  |

| bbb       | 0.10           |         |      |  |  |

| CCC       | 0.08           |         |      |  |  |

| ddd       | 0.10           |         |      |  |  |

| eee       | 0.05           |         |      |  |  |

| Nataa     |                |         |      |  |  |

### Table 6.10. QFN-40 Package Dimensions

#### Notes:

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- 3. This package outline conforms to JEDEC MO-220.

- **4.** Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

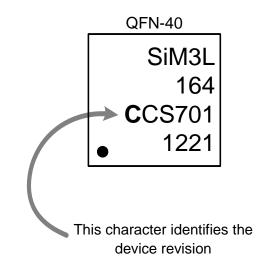

Figure 7.3. SiM3L1x4-GM Revision Information

# DOCUMENT CHANGE LIST

# **Revision 0.5 to Revision 1.0**

- Updated Electrical Specifications Tables with latest characterization data and production test limits.

- Added missing signal ACCTR0\_LCPUL1 to Table 6.2, "Pin Definitions and Alternate Functions for SiM3L1x6," on page 64.

- Removed ACCTR0\_LCIN1 and ACCTR0\_STOP0/1 signals from Table 6.3, "Pin Definitions and Alternate Functions for SiM3L1x4," on page 70.

- Updated Figure 6.8, "TFBGA-80 Package Drawing," on page 79.

# **Revision 1.0 to Revision 1.1**

■ Removed all references to BGA-80 and the parts SiM3L167-C-GL and SiM3L157-C-GL.