Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Not For New Designs                                                                      |

|----------------------------|------------------------------------------------------------------------------------------|

| Core Processor             | 8051                                                                                     |

| Core Size                  | 8-Bit                                                                                    |

| Speed                      | 25MHz                                                                                    |

| Connectivity               | EBI/EMI, Serial Port                                                                     |

| Peripherals                | POR, WDT                                                                                 |

| Number of I/O              | 36                                                                                       |

| Program Memory Size        | -                                                                                        |

| Program Memory Type        | ROMIess                                                                                  |

| EEPROM Size                | -                                                                                        |

| RAM Size                   | 1K x 8                                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                              |

| Data Converters            | -                                                                                        |

| Oscillator Type            | Internal                                                                                 |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                                          |

| Mounting Type              | Surface Mount                                                                            |

| Package / Case             | 44-BQFP                                                                                  |

| Supplier Device Package    | -                                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nuvoton-technology-corporation-america/w77l032a25fl |

|                            |                                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 5. FUNCTIONAL DESCRIPTION

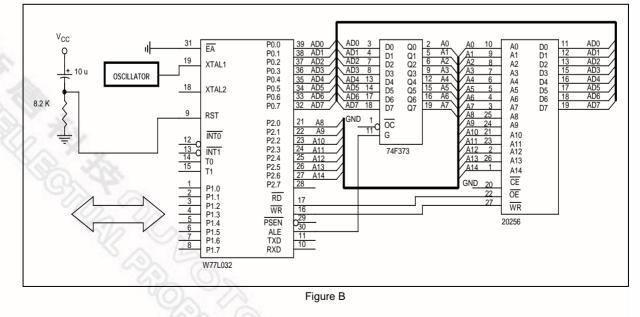

The W77L032 is 8052 pin compatible and instruction set compatible. It includes the resources of the standard 8052 such as four 8-bit I/O Ports, three 16-bit timer/counters, full duplex serial port and interrupt sources.

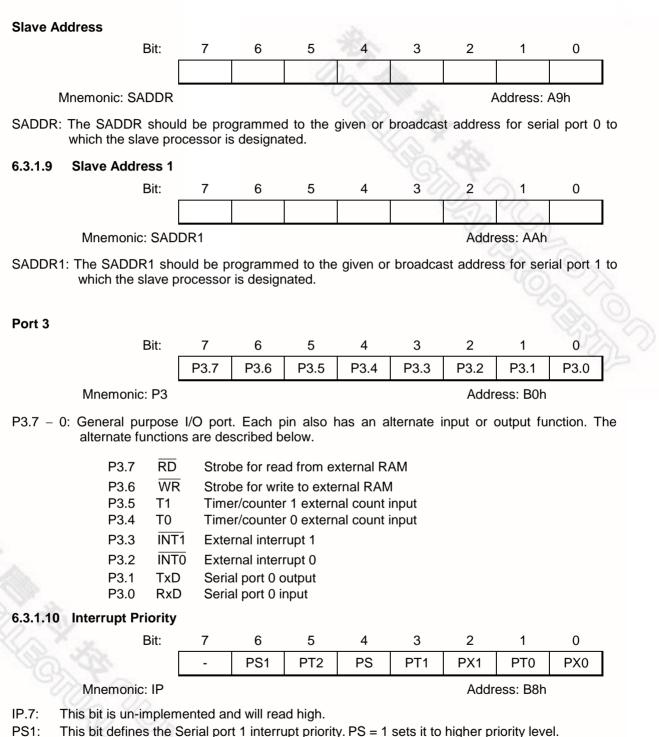

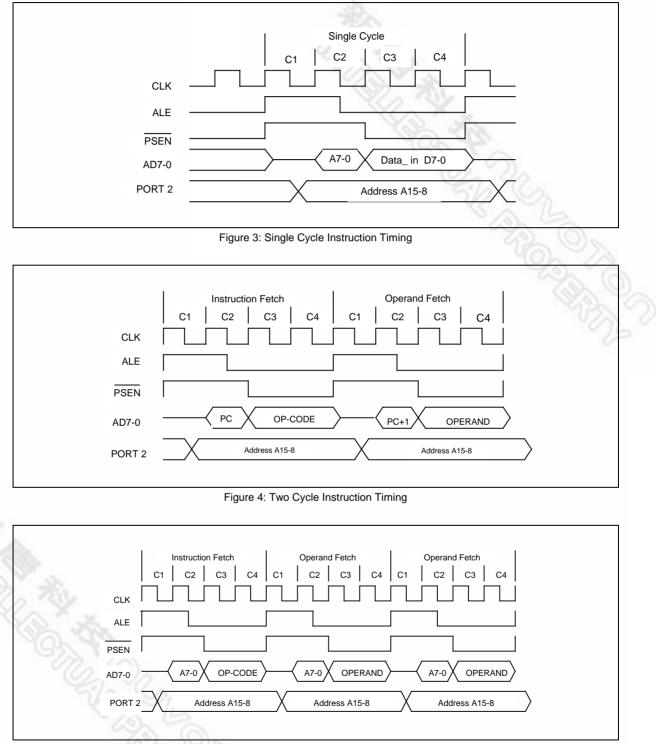

The W77L032 features a faster running and better performance 8-bit CPU with a redesigned core processor without wasted clock and memory cycles. it improves the performance not just by running at high frequency but also by reducing the machine cycle duration from the standard 8052 period of twelve clocks to four clock cycles for the majority of instructions. This improves performance by an average of 1.5 to 3 times. The W77L032 also provides dual Data Pointers (DPTRs) to speed up block data memory transfers. It can also adjust the duration of the MOVX instruction (access to off-chip data memory) between two machine cycles and nine machine cycles. This flexibility allows the W77L032 to work efficiently with both fast and slow RAMs and peripheral devices. In addition, the W77L032 contains on-chip 1KB MOVX SRAM, the address of which is between 0000H and 03FFH. It only can be accessed by MOVX instruction; this on-chip SRAM is optional under software control.

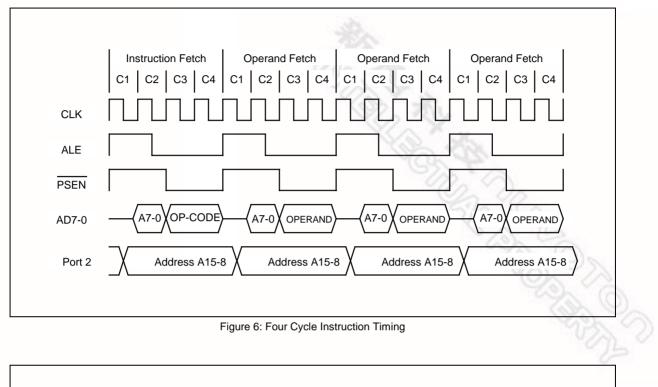

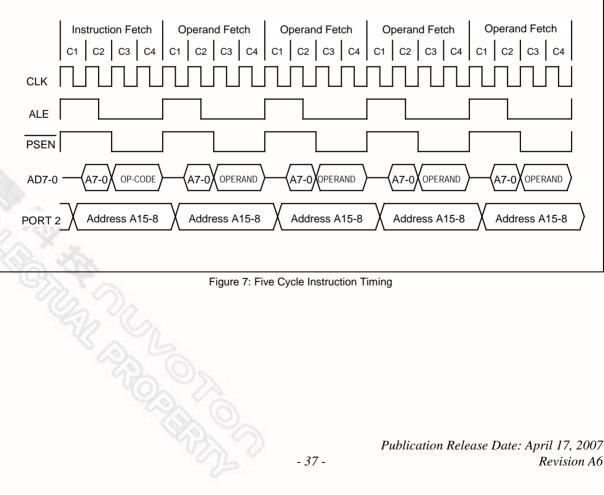

The W77L032 is an 8052 compatible device that gives the user the features of the original 8052 device, but with improved speed and power consumption characteristics. It has the same instruction set as the 8051 family, with one addition: DEC DPTR (op-code A5H, the DPTR is decreased by 1). While the original 8051 family was designed to operate at 12 clock periods per machine cycle, the W77L032 operates at a much reduced clock rate of only 4 clock periods per machine cycle. This naturally speeds up the execution of instructions. Consequently, the W77L032 can run at a higher speed as compared to the original 8052, even if the same crystal is used. Since the W77L032 is a fully static CMOS design, it can also be operated at a lower crystal clock, giving the same throughput in terms of instruction execution, yet reducing the power consumption.

The 4 clocks per machine cycle feature in the W77L032 is responsible for a three-fold increase in execution speed. The W77L032 has all the standard features of the 8052, and has a few extra peripherals and features as well.

### 5.1 I/O Ports

The W77L032 has four 8-bit ports and one extra 4-bit port. Port 0 can be used as an Address/Data bus when external program is running or external memory/device is accessed by MOVC or MOVX instruction. In these cases, it has strong pull-ups and pull-downs, and does not need any external pull-ups. Otherwise it can be used as a general I/O port with open-drain circuit. Port 2 is used chiefly as the upper 8-bits of the Address bus when port 0 is used as an address/data bus. It also has strong pull-ups and pull-downs when it serves as an address bus. Port 1 and 3 act as I/O ports with alternate functions. Port 4 is only available on 44-pin PLCC/QFP package type. It serves as a general purpose I/O port as Port 1 and Port 3. The P4.0 has an alternate function WAIT which is the wait state control signal. When wait state control signal is enabled, P4.0 is input only.

### 5.2 Serial I/O

The W77L032 has two enhanced serial ports that are functionally similar to the serial port of the original 8052 family. However the serial ports on the W77L032 can operate in different modes in order to obtain timing similarity as well. Note that the serial port 0 can use Timer 1 or 2 as baud rate generator, but the serial port 1 can only use Timer 1 as baud rate generator. The serial ports have the enhanced features of Automatic Address recognition and Frame Error detection.

# nuvoTon

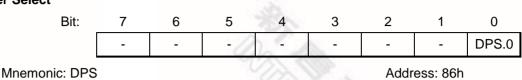

#### **Data Pointer Select**

DPS.0: This bit is used to select either the DPL,DPH pair or the DPL1, DPH1 pair as the active Data Pointer. When set to 1, DPL1, DPH1 will be selected, otherwise DPL, DPH will be selected.

DPS.1 – 7: These bits are reserved, but will read 0.

#### **Power Control**

| Bit:         | 7    | 6     | 5 | 4   | 3         | 2   | ~C | 0   |

|--------------|------|-------|---|-----|-----------|-----|----|-----|

|              | SM0D | SMOD0 | - | -   | GF1       | GF0 | PD | IDL |

| Mnemonic: PC |      |       |   | Add | ress: 87h | 0,  |    |     |

SMOD : This bit doubles the serial port baud rate in mode 1, 2, and 3 when set to 1.

- SMOD0: Framing Error Detection Enable: When SMOD0 is set to 1, then SCON.7(SCON1.7) indicates a Frame Error and acts as the FE(FE\_1) flag. When SMOD0 is 0, then SCON.7(SCON1.7) acts as per the standard 8052 function.

- GF1 0: These two bits are general purpose user flags.

- PD: Setting this bit causes the W77L032 to go into the POWER DOWN mode. In this mode all the clocks are stopped and program execution is frozen.

- IDL: Setting this bit causes the W77L032 to go into the IDLE mode. In this mode the clocks to the CPU are stopped, so program execution is frozen. But the clock to the serial, timer and interrupt blocks is not stopped, and these blocks continue operating.

#### **Timer Control**

| Bit: | 7   | 6   | 5   | 4   | 3   | 2  | 1   | 0  |

|------|-----|-----|-----|-----|-----|----|-----|----|

|      | TF1 | TR1 | TF0 | TR0 | IE1 | IT | IE0 | IT |

|      |     |     |     |     |     |    |     |    |

#### Mnemonic: TCON

Address: 88h

- TF1: Timer 1 overflow flag: This bit is set when Timer 1 overflows. It is cleared automatically when the program does a timer 1 interrupt service routine. Software can also set or clear this bit.

- TR1: Timer 1 run control: This bit is set or cleared by software to turn timer/counter on or off.

- TF0: Timer 0 overflow flag: This bit is set when Timer 0 overflows. It is cleared automatically when the program does a timer 0 interrupt service routine. Software can also set or clear this bit.

- TR0: Timer 0 run control: This bit is set or cleared by software to turn timer/counter on or off.

- IE1: Interrupt 1 edge detect: Set by hardware when an edge/level is detected on INT1. This bit is cleared by hardware when the service routine is vectored to only if the interrupt was edge triggered. Otherwise it follows the pin.

- IT1: Interrupt 1 type control: Set/cleared by software to specify falling edge/ low level triggered external inputs.

# nuvoTon

PT2: This bit defines the Timer 2 interrupt priority. PT2 = 1 sets it to higher priority level.

PS: This bit defines the Serial port 0 interrupt priority. PS = 1 sets it to higher priority level.

- PT1: This bit defines the Timer 1 interrupt priority.

- PX1: This bit defines the External interrupt 1 priority.

- rity. PX1 = 1 sets it to higher priority level.

- PT0: This bit defines the Timer 0 interrupt priority.

- PT0 = 1 sets it to higher priority level.

PT1 = 1 sets it to higher priority level.

### **Timer 2 Capture MSB**

| Bit:        | 7           | 6                                         | 5         |         | 4      | 3        | 2     |           | 1        | 0         |

|-------------|-------------|-------------------------------------------|-----------|---------|--------|----------|-------|-----------|----------|-----------|

|             | RCAP2H.7    | RCAP2H.6                                  | RCAP2     | H.5 RC/ | AP2H.4 | RCAP2H.3 | RCAP2 | H.2 RC    | AP2H.1   | RCAP2H    |

| N           | Inemonic: R | CAP2H                                     |           |         |        |          |       |           | Addr     | ess: CBh  |

| RCA         | RCAF        | egister is us<br>2H is also<br>eload mode | used as   |         |        |          |       |           |          |           |

| Time        | er 2 LSB    |                                           |           |         |        |          |       |           |          |           |

|             |             | Bit:                                      | 7         | 6       | 5      | 4        | 3     | 2         | 1        | 0         |

|             |             |                                           | TL2.7     | TL2.6   | TL2.5  | TL2.4    | TL2.3 | TL2.2     | TL2.1    | TL2.0     |

|             | Mner        | monic: TL2                                |           |         |        |          |       | Addr      | ess: CC  | h (0).    |

| TL2:        | Timer 2     | LSB                                       |           |         |        |          |       |           |          |           |

| 6.3.1       | .17 Timer   | 2 MSB                                     |           |         |        |          |       |           |          |           |

|             |             | Bit:                                      | 7         | 6       | 5      | 4        | 3     | 2         | 1        | 0         |

|             |             |                                           | TH2.7     | TH2.6   | TH2.5  | TH2.4    | TH2.3 | TH2.2     | TH2.1    | TH2.0     |

|             | Mner        | monic: TH2                                |           |         |        |          |       | Addr      | ess: CD  | h         |

| TH2:        | Timer 2     | MSB                                       |           |         |        |          |       |           |          |           |

| 6.3.1       | .18 Progra  | am Status V                               | Vord      |         |        |          |       |           |          |           |

|             |             | Bit:                                      | 7         | 6       | 5      | 4        | 3     | 2         | 1        | 0         |

|             |             |                                           | CY        | AC      | F0     | RS1      | RS0   | OV        | F1       | Р         |

|             | Mnemon      | ic: PSW                                   |           |         |        |          |       |           | Address  | : D0h     |

| CY:         |             | ig: Set for a<br>s also used a            |           |         |        |          |       | rry being | g genera | ted from  |

| AC:         | •           | carry: Set w<br>g 0: General              |           | •       | •      |          | -     |           | e high o | rder nibb |

| FU:         |             |                                           |           |         |        |          |       |           |          |           |

| F0:<br>RS.1 | – 0: Regist | er bank sele                              | ect bits: |         |        |          |       |           |          |           |

| RS0 | Register bank | Address           |

|-----|---------------|-------------------|

| 0   | 0             | 00-07h            |

| 1   | 1             | 08-0Fh            |

| 0   | 2             | 10-17h            |

| 1   | 3             | 18-1Fh            |

|     | 0             | 0 0<br>1 1<br>0 2 |

OV: Overflow flag: Set when a carry was generated from the seventh bit but not from the 8th bit as a result of the previous operation, or vice-versa.

F1: User Flag 1: General purpose flag that can be set or cleared by the user by software

P: Parity flag: Set/cleared by hardware to indicate odd/even number of 1's in the accumulator.

# nuvoton

#### Watchdog Control

| Bit: | 7      | 6   | 5 | 4    | 3    | 2    | 1   | 0   |

|------|--------|-----|---|------|------|------|-----|-----|

|      | SMOD_1 | POR | 5 |      | WDIF | WTRF | EWT | RWT |

|      |        |     |   | 22 N |      |      |     |     |

Mnemonic: WDCON

Address: D8h

SMOD 1: This bit doubles the Serial Port 1 baud rate in mode 1, 2, and 3 when set to 1.

- POR: Power-on reset flag. Hardware will set this flag on a power up condition. This flag can be read or written by software. A write by software is the only way to clear this bit once it is set.

- WDIF: Watchdog Timer Interrupt Flag. If the watchdog interrupt is enabled, hardware will set this bit to indicate that the watchdog interrupt has occurred. If the interrupt is not enabled, then this bit indicates that the time-out period has elapsed. This bit must be cleared by software.

- WTRF: Watchdog Timer Reset Flag. Hardware will set this bit when the watchdog timer causes a reset. Software can read it but must clear it manually. A power-fail reset will also clear the bit. This bit helps software in determining the cause of a reset. If EWT = 0, the watchdog timer will have no affect on this bit.

- EWT: Enable Watchdog timer Reset. Setting this bit will enable the Watchdog timer Reset function.

- RWT: Reset Watchdog Timer. This bit helps in putting the watchdog timer into a know state. It also helps in resetting the watchdog timer before a time-out occurs. Failing to set the RWT before time-out will cause an interrupt, if EWDI (EIE.4) is set, and 512 clocks after that a watchdog timer reset will be generated if EWT is set. This bit is self-clearing by hardware.

The WDCON SFR is set to a 0x0x0xx0b on an external reset. WTRF is set to a 1 on a Watchdog timer reset, but to a 0 on power on/down resets. WTRF is not altered by an external reset. POR is set to 1 by a power-on reset. EWT is set to 0 on a Power-on reset and unaffected by other resets.

All the bits in this SFR have unrestricted read access. POR, EWT, WDIF and RWT require Timed Access procedure to write. The remaining bits have unrestricted write accesses.

#### 6.3.1.19 Accumulator

| Bit: | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|------|-------|-------|-------|-------|-------|-------|-------|-------|

|      | ACC.7 | ACC.6 | ACC.5 | ACC.4 | ACC.3 | ACC.2 | ACC.1 | ACC.0 |

#### Mnemonic: ACC

Address: E0h

ACC.7 - 0: The A (or ACC) register is the standard 8052 accumulator.

| Table 3. Instruction Timing for W77L032, continued |  |

|----------------------------------------------------|--|

|----------------------------------------------------|--|

|   | INSTRUCTION    | HEX<br>OP-CODE | BYTES | W77L032<br>MACHINE<br>CYCLES | W77L032<br>CLOCK<br>CYCLES | 8032<br>CLOCK<br>CYCLES | W77L032<br>VS.8032<br>SPEED RATIO |

|---|----------------|----------------|-------|------------------------------|----------------------------|-------------------------|-----------------------------------|

| Ν | MOV A, R2      | EA             | 1     | 1000                         | 4                          | 12                      | 3                                 |

|   | MOV A, R3      | EB             | 1     | 1 6                          | 4                          | 12                      | 3                                 |

| - | MOV A, R4      | EC             | 1     | 1                            | 4                          | 12                      | 3                                 |

|   | MOV A, R5      | ED             | 1     | 1                            | 4                          | 12                      | 3                                 |

| - | MOV A, R6      | EE             | 1     | 1                            | 4                          | 12                      | 3                                 |

|   | MOV A, R7      | EF             | 1     | 1                            | 4                          | 12                      | 3                                 |

| Ν | MOV A, @R0     | E6             | 1     | 1                            | 4                          | 12                      | 3                                 |

| Ν | MOV A, @R1     | E7             | 1     | 1                            | 4                          | 12                      | 3                                 |

|   | MOV A, direct  | E5             | 2     | 2                            | 8                          | 12                      | 1.5                               |

|   | MOV A, #data   | 74             | 2     | 2                            | 8                          | 12                      | 1.5                               |

| - | MOV R0, A      | F8             | 1     | 1                            | 4                          | 12                      | 3                                 |

| - | MOV R1, A      | F9             | 1     | 1                            | 4                          | 12                      | 3                                 |

|   | MOV R2, A      | FA             | 1     | 1                            | 4                          | 12                      | 3                                 |

|   | MOV R3, A      | FB             | 1     | 1                            | 4                          | 12                      | 3                                 |

|   | MOV R4, A      | FC             | 1     | 1                            | 4                          | 12                      | 3                                 |

|   | MOV R5, A      | FD             | 1     | 1                            | 4                          | 12                      | 3                                 |

|   | MOV R6, A      | FE             | 1     | 1                            | 4                          | 12                      | 3                                 |

|   | MOV R7, A      | FF             | 1     | 1                            | 4                          | 12                      | 3                                 |

|   | MOV R0, direct | A8             | 2     | 2                            | 8                          | 12                      | 1.5                               |

| - | MOV R1, direct | A9             | 2     | 2                            | 8                          | 12                      | 1.5                               |

| - | MOV R2, direct | AA             | 2     | 2                            | 8                          | 12                      | 1.5                               |

| - | MOV R3, direct | AB             | 2     | 2                            | 8                          | 12                      | 1.5                               |

|   | MOV R4, direct | AC             | 2     | 2                            | 8                          | 12                      | 1.5                               |

|   | MOV R5, direct | AD             | 2     | 2                            | 8                          | 12                      | 1.5                               |

|   | MOV R6, direct | AE             | 2     | 2                            | 8                          | 12                      | 1.5                               |

|   | MOV R7, direct | AF             | 2     | 2                            | 8                          | 12                      | 1.5                               |

| - | MOV R0, #data  | 78             | 2     | 2                            | 8                          | 12                      | 1.5                               |

|   | MOV R1, #data  | 79             | 2     | 2                            | 8                          | 12                      | 1.5                               |

| _ | MOV R2, #data  | 7A             | 2     | 2                            | 8                          | 12                      | 1.5                               |

| - | MOV R3, #data  | 7B             | 2     | 2                            | 8                          | 12                      | 1.5                               |

| - | MOV R4, #data  | 7C             | 2     | 2                            | 8                          | 12                      | 1.5                               |

|   | MOV R5, #data  | 7D             | 2     | 2                            | 8                          | 12                      | 1.5                               |

|   | MOV R6, #data  | 7E             | 2     | 2                            | 8                          | 12                      | 1.5                               |

| _ |                | 7F             |       | 2                            | 8                          | 12                      | 1.5                               |

| INSTRUCTION       | HEX<br>OP-CODE | BYTES | W77L032<br>MACHINE<br>CYCLES | W77L032<br>CLOCK<br>CYCLES | 8032<br>CLOCK<br>CYCLES | W77L032<br>VS.8032<br>SPEED RATIC |

|-------------------|----------------|-------|------------------------------|----------------------------|-------------------------|-----------------------------------|

| SUBB A, @R0       | 96             | 1     | 1 73                         | 4                          | 12                      | 3                                 |

| SUBB A, @R1       | 97             | 1     | 1 (                          | 4                          | 12                      | 3                                 |

| SUBB A, direct    | 95             | 2     | 2                            | 8                          | 12                      | 1.5                               |

| SUBB A, #data     | 94             | 2     | 2                            | 8                          | 12                      | 1.5                               |

| XCH A, R0         | C8             | 1     | 1                            | 4                          | 12                      | 3                                 |

| XCH A, R1         | C9             | 1     | 1                            | 4                          | 12                      | 3                                 |

| XCH A, R2         | CA             | 1     | 1                            | 4                          | 12                      | 3                                 |

| XCH A, R3         | СВ             | 1     | 1                            | 4                          | 12                      | 3                                 |

| XCH A, R4         | CC             | 1     | 1                            | 4                          | 12                      | 3                                 |

| XCH A, R5         | CD             | 1     | 1                            | 4                          | 12                      | 3                                 |

| XCH A, R6         | CE             | 1     | 1                            | 4                          | 12                      | 3                                 |

| XCH A, R7         | CF             | 1     | 1                            | 4                          | 12                      | 3                                 |

| XCH A, @R0        | C6             | 1     | 1                            | 4                          | 12                      | 3                                 |

| XCH A, @R1        | C7             | 1     | 1                            | 4                          | 12                      | 3                                 |

| XCHD A, @R0       | D6             | 1     | 1                            | 4                          | 12                      | 3                                 |

| XCHD A, @R1       | D7             | 1     | 1                            | 4                          | 12                      | 3                                 |

| XCH A, direct     | C5             | 2     | 2                            | 8                          | 12                      | 1.5                               |

| XRL A, R0         | 68             | 1     | 1                            | 4                          | 12                      | 3                                 |

| XRL A, R1         | 69             | 1     | 1                            | 4                          | 12                      | 3                                 |

| XRL A, R2         | 6A             | 1     | 1                            | 4                          | 12                      | 3                                 |

| XRL A, R3         | 6B             | 1     | 1                            | 4                          | 12                      | 3                                 |

| XRL A, R4         | 6C             | 1     | 1                            | 4                          | 12                      | 3                                 |

| XRL A, R5         | 6D             | 1     | 1                            | 4                          | 12                      | 3                                 |

| XRL A, R6         | 6E             | 1     | 1                            | 4                          | 12                      | 3                                 |

| XRL A, R7         | 6F             | 1     | 1                            | 4                          | 12                      | 3                                 |

| XRL A, @R0        | 66             | 1     | 1                            | 4                          | 12                      | 3                                 |

| XRL A, @R1        | 67             | 1     | 1                            | 4                          | 12                      | 3                                 |

| XRL A, direct     | 65             | 2     | 2                            | 8                          | 12                      | 1.5                               |

| XRL A, #data      | 64             | 2     | 2                            | 8                          | 12                      | 1.5                               |

| XRL direct, A     | 62             | 2     | 2                            | 8                          | 12                      | 1.5                               |

| XRL direct, #data | 63             | 3     | 3                            | 12                         | 24                      | 2                                 |

# nuvoTon

Figure 5: Three Cycle Instruction Timing

# nuvoton

#### Figure 7: Five Cycle Instruction Timing

Publication Release Date: April 17, 2007 Revision A6

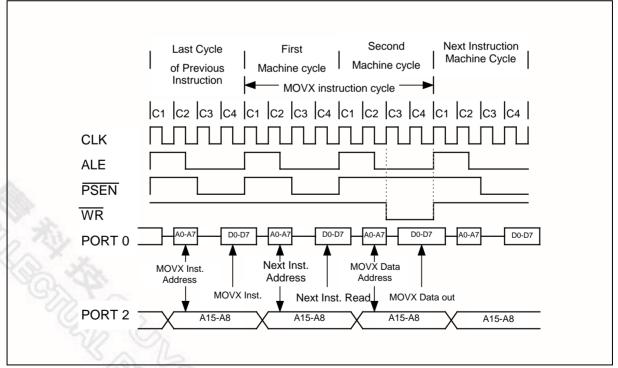

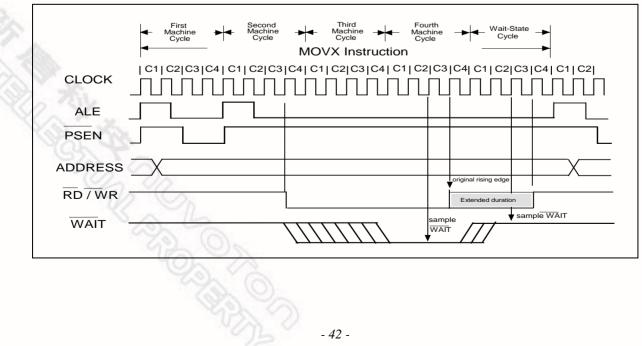

#### 7.1.1 MOVX Instruction

The W77L032, like the standard 8032, uses the MOVX instruction to access external Data Memory. This Data Memory includes both off-chip memory as well as memory mapped peripherals. While the results of the MOVX instruction are the same as in the standard 8032, the operation and the timing of the strobe signals have been modified in order to give the user much greater flexibility.

The MOVX instruction is of two types, the MOVX @Ri and MOVX @DPTR. In the MOVX @Ri, the address of the external data comes from two sources. The lower 8-bits of the address are stored in the Ri register of the selected working register bank. The upper 8-bits of the address come from the port 2 SFR. In the MOVX @DPTR type, the full 16-bit address is supplied by the Data Pointer.

Since the W77L032 has two Data Pointers, DPTR and DPTR1, the user has to select between the two by setting or clearing the DPS bit. The Data Pointer Select bit (DPS) is the LSB of the DPS SFR, which exists at location 86h. No other bits in this SFR have any effect, and they are set to 0. When DPS is 0, then DPTR is selected, and when set to 1, DPTR1 is selected. The user can switch between DPTR and DPTR1 by toggling the DPS bit. The quickest way to do this is by the INC instruction. The advantage of having two Data Pointers is most obvious while performing block move operations. The accompanying code shows how the use of two separate Data Pointers speeds up the execution time for code performing the same task.

#### Block Move with single Data Pointer:

- ; SH and SL are the high and low bytes of Source Address

- ; DH and DL are the high and low bytes of Destination Address

- ; CNT is the number of bytes to be moved

#### Machine cycles of W77L032

|       |          |                                                    | # |

|-------|----------|----------------------------------------------------|---|

| MOV   | R2, #CNT | ; Load R2 with the count value                     | 2 |

| MOV   | R3, #SL  | ; Save low byte of Source Address in R3            | 2 |

| MOV   | R4, #SH  | ; Save high byte of Source address in R4           | 2 |

| MOV   | R5, #DL  | ; Save low byte of Destination Address in R5       | 2 |

| MOV   | R6, #DH  | ; Save high byte of Destination address in R6      | 2 |

| LOOP: |          |                                                    |   |

| MOV   | DPL, R3  | ; Load DPL with low byte of Source address         | 2 |

| MOV   | DPH, R4  | ; Load DPH with high byte of Source address        | 2 |

| MOVX  | A, @DPTR | ; Get byte from Source to Accumulator              | 2 |

| INC   | DPTR     | ; Increment Source Address to next byte            | 2 |

| MOV   | R3, DPL  | ; Save low byte of Source address in R3            | 2 |

| MOV   | R4, DPH  | ; Save high byte of Source Address in R4           | 2 |

| MOV   | DPL, R5  | ; Load low byte of Destination Address in DPL      | 2 |

| MOV   | DPH, R6  | ; Load high byte of Destination Address in DPH     | 2 |

| MOVX  | @DPTR, A | ; Write data to destination                        | 2 |

| INC   | DPTR     | ; Increment Destination Address                    | 2 |

| MOV   | DPL, R5  | ; Save low byte of new destination address in R5 2 |   |

| MOV   | DPH, R6  | ; Save high byte of new destination address in R6  | 2 |

| DJNZ  | R2, LOOP | ; Decrement count and do LOOP again if count <> 0  | 2 |

|       |          |                                                    |   |

CPU was held for the desired period. There is no effect on any other instruction or its timing. By default, the Stretch value is set at 1, giving a MOVX instruction of 3 machine cycles. If desired by the user the stretch value can be set to 0 to give the fastest MOVX instruction of only 2 machine cycles.

| M2 | M1 | МО | Machine<br>Cycles | RD or WR<br>Strobe Width<br>in Clocks | RD or WR<br>Strobe Width<br>@25 MHz | RD or WR<br>Strobe Width<br>@40 MHz |

|----|----|----|-------------------|---------------------------------------|-------------------------------------|-------------------------------------|

| 0  | 0  | 0  | 2                 | 2                                     | 80 nS                               | 50 nS                               |

| 0  | 0  | 1  | 3 (Default)       | 4                                     | 160 nS                              | 100 nS                              |

| 0  | 1  | 0  | 4                 | 8                                     | 320 nS                              | 200 nS                              |

| 0  | 1  | 1  | 5                 | 12                                    | 480 nS                              | 300 nS                              |

| 1  | 0  | 0  | 6                 | 16                                    | 640 nS                              | 400 nS                              |

| 1  | 0  | 1  | 7                 | 20                                    | 800 nS                              | 500 nS                              |

| 1  | 1  | 0  | 8                 | 24                                    | 960 nS                              | 600 nS                              |

| 1  | 1  | 1  | 9                 | 28                                    | 1120 nS                             | 700 nS                              |

Table 4. Data Memory Cycle Stretch Values

Figure 8: Data Memory Write with Stretch Value = 0

#### Wait State Control Signal

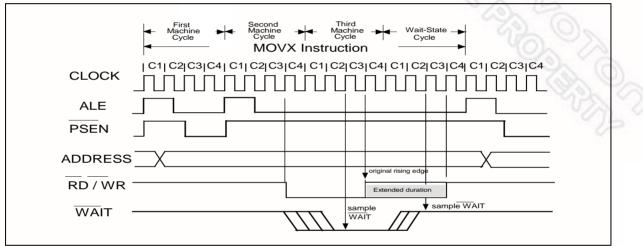

Either with the software using stretch value to change the required machine cycle of MOVX instruction,

the W77L032 provides another hardware signal  $\overline{WAIT}$  to implement the wider duration of external data access timing. This wait state control signal is the alternate function of P4.0 such that it can only be invoked to 44-pin PLCC/QFP package type. The wait state control signal can be enabled by setting WS (ROMMAP.7) bit. When enabled, the setting of stretch value decides the minimum length of MOVX instruction cycle and the device will sample the  $\overline{WAIT}$  pin at each C3 state before the rising edge of read/write strobe signal during MOVX instruction. Once this signal being recongnized, one more machine cycle (wait state cycle) will be inserted into next cycle. The inserted wait state cycles are unlimited, so the MOVX instruction cycle will end in which the wait state control signal is deactivated. Using wait state control signal allows a dynamically access timing to a selected external peripheral. The WS bit is accessed by the Timed Access Protection procedure.

#### Wait State Control Signal Timing (when Stretch = 1)

Wait State Control Signal Timing ( when Stretch = 2 )

# ηυνοτοη

### **10. INTERRUPTS**

The W77L032 has a two priority level interrupt structure with 12 interrupt sources. Each of the interrupt sources has an individual priority bit, flag, interrupt vector and enable bit. In addition, the interrupts can be globally enabled or disabled.

### **10.1 Interrupt Sources**

The External Interrupts INTO and INT1 can be either edge triggered or level triggered, depending on bits ITO and IT1. The bits IEO and IE1 in the TCON register are the flags which are checked to generate the interrupt. In the edge triggered mode, the INTx inputs are sampled in every machine cycle. If the sample is high in one cycle and low in the next, then a high to low transition is detected and the interrupts request flag IEx in TCON or EXIF is set. The flag bit requests the interrupt. Since the external interrupts are sampled every machine cycle, they have to be held high or low for at least one complete machine cycle. The IEx flag is automatically cleared when the service routine is called. If the level triggered mode is selected, then the requesting source has to hold the pin low till the interrupt is serviced. The IEx flag will not be cleared by the hardware on entering the service routine. If the interrupt continues to be held low even after the service routine is completed, then the processor may acknowledge another interrupt request from the same source. Note that the external interrupts INT2 to

INT5 are edge triggered only. By default, the individual interrupt flag corresponding to external interrupt 2 to 5 must be cleared manually by software. It can be configured with hardware cleared by setting the corresponding bit HCx in the T2MOD register. For instance, if HC2 is set hardware will clear IE2 flag after program enters the interrupt 2 service routine.

The Timer 0 and 1 Interrupts are generated by the TF0 and TF1 flags. These flags are set by the overflow in the Timer 0 and Timer 1. The TF0 and TF1 flags are automatically cleared by the hardware when the timer interrupt is serviced. The Timer 2 interrupt is generated by a logical OR of the TF2 and the EXF2 flags. These flags are set by overflow or capture/reload events in the timer 2 operation. The hardware does not clear these flags when a timer 2 interrupt is executed. Software has to resolve the cause of the interrupt between TF2 and EXF2 and clear the appropriate flag.

The Watchdog timer can be used as a system monitor or a simple timer. In either case, when the timeout count is reached, the Watchdog timer interrupt flag WDIF (WDCON.3) is set. If the interrupt is enabled by the enable bit EIE.4, then an interrupt will occur.

The Serial block can generate interrupts on reception or transmission. There are two interrupt sources from the Serial block, which are obtained by the RI and TI bits in the SCON SFR and RI\_1 and TI\_1 in the SCON1 SFR. These bits are not automatically cleared by the hardware, and the user will have to clear these bits using software.

All the bits that generate interrupts can be set or reset by hardware, and thereby software initiated interrupts can be generated. Each of the individual interrupts can be enabled or disabled by setting or clearing a bit in the IE SFR. IE also has a global enable/disable bit EA, which can be cleared to disable all the interrupt, at once.

### **10.2 Priority Level Structure**

There are two priority levels for the interrupts, high and low. The interrupt source can be individually set to either high or low levels. Naturally, a higher priority interrupt cannot be interrupted by a lower priority interrupt. However there exists a pre-defined hierarchy amongst the interrupts themselves. This hierarchy comes into play when the interrupt controller has to resolve simultaneous requests having the same priority level. This hierarchy is defined as shown below; the interrupts are numbered starting from the highest priority to the lowest.

# nuvoton

### **11. PROGRAMMABLE TIMERS/COUNTERS**

The W77L032 has three 16-bit programmable timer/counters and one programmable Watchdog timer. The Watchdog timer is operationally guite different from the other two timers.

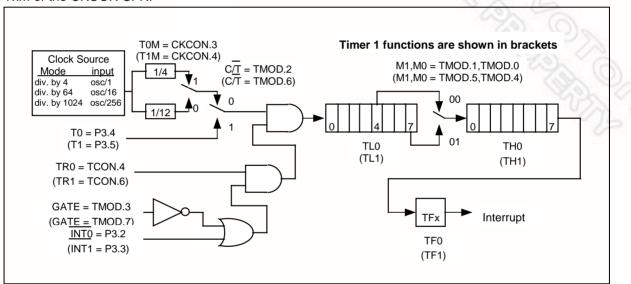

### 11.1 Timer/Counters 0 & 1

The W77L032 has two 16-bit Timer/Counters. Each of these Timer/Counters has two 8 bit registers which form the 16 bit counting register. For Timer/Counter 0 they are TH0, the upper 8 bits register, and TL0, the lower 8 bit register. Similarly Timer/Counter 1 has two 8 bit registers, TH1 and TL1. The two can be configured to operate either as timers, counting machine cycles or as counters counting external inputs.

When configured as a "Timer", the timer counts clock cycles. The timer clock can be programmed to be thought of as 1/12 of the system clock or 1/4 of the system clock. In the "Counter" mode, the register is incremented on the falling edge of the external input pin, T0 in case of Timer 0, and T1 for Timer 1. The T0 and T1 inputs are sampled in every machine cycle at C4. If the sampled value is high in one machine cycle and low in the next, then a valid high to low transition on the pin is recognized and the count register is incremented. Since it takes two machine cycles to recognize a negative transition on the pin, the maximum rate at which counting will take place is 1/24 of the master clock frequency. In either the "Timer" or "Counter" mode, the count register will be updated at C3. Therefore, in the "Timer" mode, the recognized negative transition on pin T0 and T1 can cause the count register value to be updated only in the machine cycle following the one in which the negative edge was detected.

The "Timer" or "Counter" function is selected by the "C/ $\overline{T}$ " bit in the TMOD Special Function Register. Each Timer/Counter has one selection bit for its own: bit 2 of TMOD selects the function for Timer/Counter 0 and bit 6 of TMOD selects the function for Timer/Counter 1. In addition each Timer/Counter can be set to operate in any one of four possible modes. The mode selection is done by bits M0 and M1 in the TMOD SFR.

### 11.2 Time-base Selection

The W77L032 gives the user two modes of operation for the timer. The timers can be programmed to operate like the standard 8051 family, counting at the rate of 1/12 of the clock speed. This will ensure that timing loops on the W77L032 and the standard 8051 can be matched. This is the default mode of operation of the W77L032 timers. The user also has the option to count in the turbo mode, where the timers will increment at the rate of 1/4 clock speed. This will straight-away increase the counting speed three times. This selection is done by the TOM and T1M bits in CKCON SFR. A reset sets these bits to 0, and the timers then operate in the standard 8051 mode. The user should set these bits to 1 if the timers are to operate in turbo mode. , c<sub>h</sub>

#### 11.2.1 Mode 0

In Mode 0, the timer/counters act as a 8 bit counter with a 5 bit, divide by 32 pre-scale. In this mode we have a 13 bit timer/counter. The 13 bit counter consists of 8 bits of THx and 5 lower bits of TLx. The upper 3 bits of TLx are ignored.

The negative edge of the clock increments the count in the TLx register. When the fifth bit in TLx moves from 1 to 0, then the count in the THx register is incremented. When the count in THx moves from FFh to 00h, then the overflow flag TFx in TCON SFR is set. The counted input is enabled only if TRx is set and either GATE = 0 or  $\overline{INTx} = 1$ . When  $C/\overline{T}$  is set to 0, then it will count clock cycles, and if  $C/\overline{T}$  is set to 1, then it will count 1 to 0 transitions on T0 (P3.4) for timer 0 and T1 (P3.5) for timer 1. When the 13 bit count reaches 1FFFh the next count will cause it to roll-over to 0000h. The timer overflow flag TFx of the relevant timer is set and if enabled an interrupts will occur. Note that when used as a timer, the time-base may be either clock cycles/12 or clock cycles/4 as selected by the bits TxM of the CKCON SFR.

Figure 11: Timer/Counter Mode 0 & Mode 1

### 11.2.2 Mode 1

Mode 1 is similar to Mode 0 except that the counting register forms a 16 bit counter, rather than a 13 bit counter. This means that all the bits of THx and TLx are used. Roll-over occurs when the timer moves from a count of FFFFh to 0000h. The timer overflow flag TFx of the relevant timer is set and if enabled an interrupt will occur. The selection of the time-base in the timer mode is similar to that in Mode 0. The gate function operates similarly to that in Mode 0.

#### 11.2.3 Mode 2

In Mode 2, the timer/counter is in the Auto Reload Mode. In this mode, TLx acts as a 8 bit count register, while THx holds the reload value. When the TLx register overflows from FFh to 00h, the TFx bit in TCON is set and TLx is reloaded with the contents of THx, and the counting process continues from here. The reload operation leaves the contents of the THx register unchanged. Counting is enabled by the TRx bit and proper setting of GATE and INTx pins. As in the other two modes 0 and 1, mode 2 allows counting of either clock cycles (clock/12 or clock/4) or pulses on pin Tn.

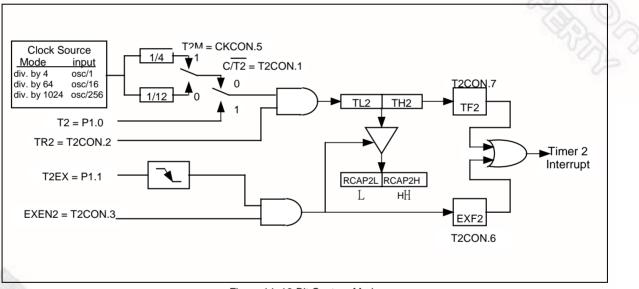

### 11.3 Timer/Counter 2

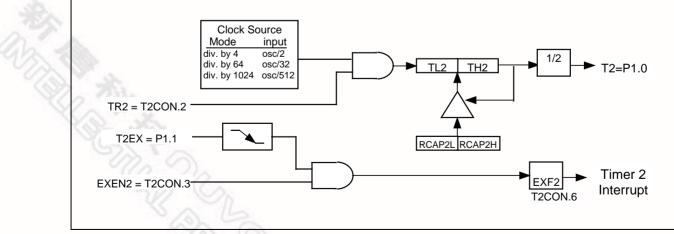

Timer/Counter 2 is a 16 bit up/down counter which is configured by the T2MOD register and controlled by the T2CON register. Timer/Counter 2 is equipped with a capture/reload capability. As with the Timer 0 and Timer 1 counters, there exists considerable flexibility in selecting and controlling the clock, and in defining the operating mode. The clock source for Timer/Counter 2 may be selected for either the external T2 pin (C/T2 = 1) or the crystal oscillator, which is divided by 12 or 4 (C/T2 = 0). The clock is then enabled when TR2 is a 1, and disabled when TR2 is a 0.

### 11.3.1 Capture Mode

The capture mode is enabled by setting the  $CP/\overline{RL2}$  bit in the T2CON register to a 1. In the capture mode, Timer/Counter 2 serves as a 16 bit up counter. When the counter rolls over from FFFFh to 0000h, the TF2 bit is set, which will generate an interrupt request. If the EXEN2 bit is set, then a negative transition of T2EX pin will cause the value in the TL2 and TH2 register to be captured by the RCAP2L and RCAP2H registers. This action also causes the EXF2 bit in T2CON to be set, which will also generate an interrupt. Setting the T2CR bit (T2MOD.3), the W77L032 allows hardware to reset timer 2 automatically after the value of TL2 and TH2 have been captured.

Figure 14. 16-Bit Capture Mode

### 11.3.2 Auto-reload Mode, Counting Up

The auto-reload mode as an up counter is enabled by clearing the CP/ $\overline{\text{RL2}}$  bit in the T2CON register and clearing the DCEN bit in T2MOD register. In this mode, Timer/Counter 2 is a 16 bit up counter. When the counter rolls over from FFFFh, a reload is generated that causes the contents of the RCAP2L and RCAP2H registers to be reloaded into the TL2 and TH2 registers. The reload action also sets the TF2 bit. If the EXEN2 bit is set, then a negative transition of T2EX pin will also cause a reload. This action also sets the EXF2 bit in T2CON.

# nuvoton

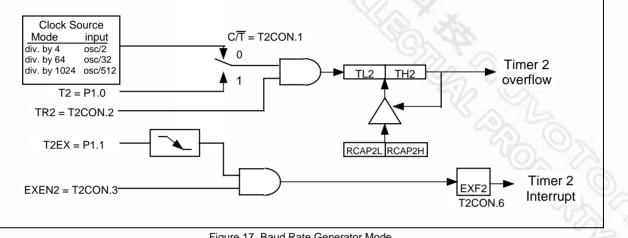

### 11.4 Baud Rate Generator Mode

The baud rate generator mode is enabled by setting either the RCLK or TCLK bits in T2CON register. While in the baud rate generator mode, Timer/Counter 2 is a 16 bit counter with auto reload when the count rolls over from FFFFh. However, rolling over does not set the TF2 bit. If EXEN2 bit is set, then a negative transition of the T2EX pin will set EXF2 bit in the T2CON register and cause an interrupt request.

#### Figure 17. Baud Rate Generator Mode

#### 11.4.1 Programmable Clock-out

Timer 2 is equipped with a new clock-out feature which outputs a 50% duty cycle clock on P1.0. It can be invoked as a programmable clock generator. To configure Timer 2 with clock-out mode, software must initiate it by setting bit T2OE = 1, C/T2 = 0 and CP/RL = 0. Setting bit TR2 will start the timer. This mode is similar to the baud rate generator mode, it will not generate an interrupt while Timer 2 overflow. So it is possible to use Timer 2 as a baud rate generator and a clock generator at the same time. The clock-out frequency is determined by the following equation:

The Clock-out Frequency = Oscillator Frequency / [4 X (RCAP2H, RCAP2L)]

Figure 18. Programmable Clock-Out Mode

11.5 Watchdog Timer

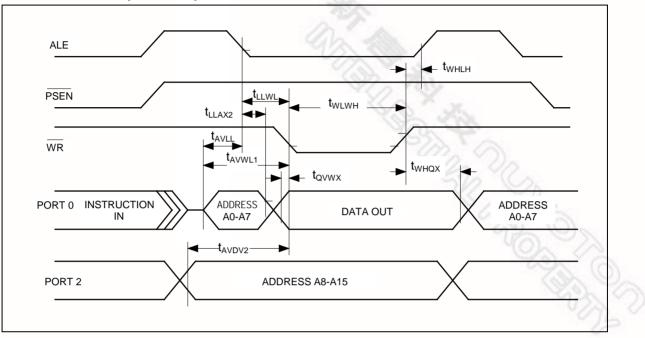

### 14.2.1 MOVX Characteristics Using Strech Memory Cycles

| PARAMETER                                                         | SYM.               | VARIABLE<br>CLOCK<br>MIN.                              | VARIABLE<br>CLOCK<br>MAX.                                               | UNITS | STRECH                         |

|-------------------------------------------------------------------|--------------------|--------------------------------------------------------|-------------------------------------------------------------------------|-------|--------------------------------|

| Data Access ALE Pulse Width                                       | t <sub>LLHL2</sub> | 1.5 t <sub>CLCL</sub> - 5<br>2.0 t <sub>CLCL</sub> - 5 | 大大                                                                      | nS    | $t_{MCS} = 0$<br>$t_{MCS} > 0$ |

| Address Hold After ALE Low for<br>MOVX Write                      | t <sub>LLAX2</sub> | 0.5 t <sub>CLCL</sub> - 5                              | S. A                                                                    | nS    |                                |

| RD Pulse Width                                                    | t <sub>RLRH</sub>  | 2.0 t <sub>CLCL</sub> - 5<br>t <sub>MCS</sub> - 10     | N.                                                                      | nS    | $t_{MCS} = 0$ $t_{MCS} > 0$    |

| WR Pulse Width                                                    | t <sub>WLWH</sub>  | 2.0 t <sub>CLCL</sub> - 5<br>t <sub>MCS</sub> - 10     | - K                                                                     | nS    | $t_{MCS} = 0$<br>$t_{MCS} > 0$ |

| RD Low to Valid Data In                                           | t <sub>RLDV</sub>  |                                                        | 2.0 t <sub>CLCL</sub> - 20<br>t <sub>MCS</sub> - 20                     | nS    | $t_{MCS} = 0$<br>$t_{MCS} > 0$ |

| Data Hold after Read                                              | t <sub>RHDX</sub>  | 0                                                      |                                                                         | nS    | 2                              |

| Data Float after Read                                             | t <sub>RHDZ</sub>  |                                                        | t <sub>CLCL</sub> - 5<br>2.0 t <sub>CLCL</sub> - 5                      | nS    | $t_{MCS} = 0$<br>$t_{MCS} > 0$ |

| ALE Low to Valid Data In                                          | t <sub>LLDV</sub>  |                                                        | 2.5 t <sub>CLCL</sub> - 5<br>t <sub>MCS</sub> + 2t <sub>CLCL</sub> - 40 | nS    | $t_{MCS} = 0$<br>$t_{MCS} > 0$ |

| Port 0 Address to Valid Data In                                   | t <sub>AVDV1</sub> |                                                        | 3.0 t <sub>CLCL</sub> - 20<br>2.0t <sub>CLCL</sub> - 5                  | nS    | $t_{MCS} = 0$<br>$t_{MCS} > 0$ |

| Port 2 Address to Valid Data In                                   | t <sub>AVDV2</sub> |                                                        | 3.5 t <sub>CLCL</sub> - 20<br>2.5 t <sub>CLCL</sub> - 5                 | nS    | $t_{MCS} = 0$<br>$t_{MCS} > 0$ |

| ALE Low to RD or WR Low                                           | t <sub>LLWL</sub>  | 0.5 t <sub>CLCL</sub> - 5<br>1.5 t <sub>CLCL</sub> - 5 | 0.5 t <sub>CLCL</sub> + 5<br>1.5 t <sub>CLCL</sub> + 5                  | nS    | $t_{MCS} = 0$<br>$t_{MCS} > 0$ |

| Port 0 Address to RD or WR Low                                    | t <sub>AVWL</sub>  | t <sub>CLCL</sub> - 5<br>2.0 t <sub>CLCL</sub> - 5     |                                                                         | nS    | $t_{MCS} = 0$<br>$t_{MCS} > 0$ |

| Port 2 Address to RD or WR Low                                    | t <sub>AVWL2</sub> | 1.5 t <sub>CLCL</sub> - 5<br>2.5 t <sub>CLCL</sub> - 5 |                                                                         | nS    | $t_{MCS} = 0$<br>$t_{MCS} > 0$ |

| Data Valid to WR Transition                                       | t <sub>QVWX</sub>  | -5<br>1.0 t <sub>CLCL</sub> - 5                        |                                                                         | nS    | $t_{MCS} = 0$<br>$t_{MCS} > 0$ |

| Data Hold after Write                                             | t <sub>wHQX</sub>  | t <sub>CLCL</sub> - 5<br>2.0 t <sub>CLCL</sub> - 5     |                                                                         | nS    | $t_{MCS} = 0$<br>$t_{MCS} > 0$ |

| RD Low to Address Float                                           | t <sub>RLAZ</sub>  |                                                        | 0.5 t <sub>CLCL</sub> - 5                                               | nS    |                                |

| $\overline{\text{RD}}$ or $\overline{\text{WR}}$ High to ALE High | t <sub>WHLH</sub>  | 0<br>1.0 t <sub>CLCL</sub> - 5                         | 10<br>1.0 t <sub>CLCL</sub> + 5                                         | nS    | $t_{MCS} = 0$<br>$t_{MCS} > 0$ |

Note: t<sub>MCS</sub> is a time period related to the Stretch memory cycle selection. The following table shows the time period of t<sub>MCS</sub> for each selection of the Stretch value.

# nuvoTon

### 15.3 Data Memory Write Cycle

# nuvoTon

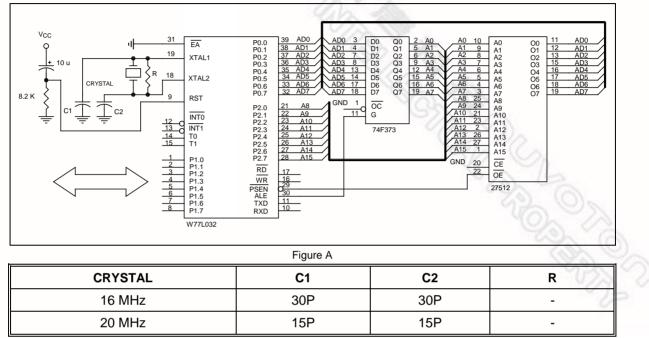

### **16. TYPICAL APPLICATION CIRCUITS**

### 16.1 Expanded External Program Memory and Crystal

The above table shows the reference values for crystal applications.

Note: C1, C2, R components refer to Figure A.

### 16.2 Expanded External Data Memory and Oscillator