Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product StatusActiveCore ProcessoreZ8Core Size8-Bit                    |  |

|------------------------------------------------------------------------|--|

|                                                                        |  |

| Core Size 8-Bit                                                        |  |

|                                                                        |  |

| Speed 20MHz                                                            |  |

| Connectivity -                                                         |  |

| Peripherals Brown-out Detect/Reset, LED, POR, PWM, WDT                 |  |

| Number of I/O 17                                                       |  |

| Program Memory Size 4KB (4K x 8)                                       |  |

| Program Memory Type FLASH                                              |  |

| EEPROM Size -                                                          |  |

| RAM Size 256 x 8                                                       |  |

| Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6V                                  |  |

| Data Converters   A/D 7x10b                                            |  |

| Oscillator Type Internal                                               |  |

| Operating Temperature -40°C ~ 105°C (TA)                               |  |

| Mounting Type Through Hole                                             |  |

| Package / Case         20-DIP (0.300", 7.62mm)                         |  |

| Supplier Device Package 20-PDIP                                        |  |

| Purchase URL https://www.e-xfl.com/product-detail/zilog/z8f043aph020eg |  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Z8 Encore!<sup>®</sup> F083A Series Product Specification

| Table 119. | Power-On Reset and Voltage Brown-Out Electrical Characteristics<br>and Timing |

|------------|-------------------------------------------------------------------------------|

| Table 120. | Flash Memory Electrical Characteristics and Timing 191                        |

| Table 121. | Watchdog Timer Electrical Characteristics and Timing 191                      |

| Table 122. | Nonvolatile Data Storage                                                      |

| Table 123. | Analog-to-Digital Converter Electrical Characteristics and Timing 192         |

| Table 124. | Comparator Electrical Characteristics                                         |

| Table 125. | GPIO Port Input Timing 194                                                    |

| Table 126. | GPIO Port Output Timing 195                                                   |

| Table 127. | On-Chip Debugger Timing 196                                                   |

| Table 128. | Power Consumption Reference Table 197                                         |

| Table 129. | Z8 Encore! F083A Series Ordering Matrix 199                                   |

| Table 130. | Package and Pin Count Description 202                                         |

| Table 131. | Timer 0 High Byte Register (T0H) 203                                          |

| Table 132. | Timer 0 Low Byte Register (T0L) 204                                           |

| Table 133. | Timer 0 Reload High Byte Register (T0RH) 204                                  |

| Table 134. | Timer 0 Reload Low Byte Register (T0RL)                                       |

| Table 135. | Timer 0 PWM High Byte Register (T0PWMH) 204                                   |

| Table 136. | Timer 0 PWM Low Byte Register (T0PWML) 205                                    |

| Table 137. | Timer 0 Control Register 0 (T0CTL0) 205                                       |

| Table 138. | Timer 0 Control Register 1 (T0CTL1) 205                                       |

| Table 139. | Timer 1 High Byte Register (T1H) 205                                          |

| Table 140. | Timer 1 Low Byte Register (T1L) 206                                           |

| Table 141. | Timer 1 Reload High Byte Register (T1RH) 206                                  |

| Table 142. | Timer 1 Reload Low Byte Register (T1RL)                                       |

| Table 143. | Timer 1 PWM High Byte Register (T1PWMH) 206                                   |

| Table 144. | Timer 1 PWM Low Byte Register (T1PWML) 207                                    |

| Table 145. | Timer 1 Control Register 0 (T1CTL0) 207                                       |

| Table 146. | Timer 1 Control Register 1 (T1CTL1)                                           |

| Table 147. | ADC Control Register 0 (ADCCTL0) 208                                          |

| Table 148. | ADC Data High Byte Register (ADCD_H) 209                                      |

# **Address Space**

The eZ8 CPU accesses three distinct address spaces as follows:

- The Register File addresses access for the general purpose registers and the eZ8 CPU, peripheral and GPIO port control registers

- Program Memory addresses access for all of the memory locations having executable code and/or data

- The Data Memory addresses access for all of the memory locations containing only the data

The following sections describe these three address spaces. For more detailed information about the eZ8 CPU and its address space, refer to the <u>eZ8 CPU Core User Manual</u> (<u>UM0128</u>), available for download on <u>www.zilog.com</u>.

# **Register File**

The Register File address space in the Z8 Encore! MCU is 4KB (4096 bytes). The Register File consists of two sections: control registers and general purpose registers. When instructions are executed, registers defined as source are read and registers defined as destinations are written. The architecture of the eZ8 CPU allows all general purpose registers to function as accumulators, address pointers, index registers, stack areas or scratch pad memory.

The upper 256 bytes of the 4KB Register File address space are reserved for control of the eZ8 CPU, on-chip peripherals and the I/O ports. These registers are located at addresses from F00H to FFFH. Some of the addresses within the 256 B Control Register section are reserved (unavailable). Reading from a reserved Register File address returns an undefined value. Writing to reserved Register File addresses is not recommended and produces unpredictable results.

The on-chip RAM always begins at address 000H in the Register File address space. The Z8 Encore! F083A Series devices contain up to 256 B of on-chip RAM. Reading from Register File addresses outside the available RAM addresses (and not within the Control Register address space), returns an undefined value. Writing to these Register File addresses has no effect.

| Address (  | Hex) Register Description             | Mnemonic | Reset (Hex) | Page #              |

|------------|---------------------------------------|----------|-------------|---------------------|

| Trim Bit C | Control                               |          |             |                     |

| FF6        | Trim Bit Address                      | TRMADR   | 00          | 126                 |

| FF7        | Trim Data                             | TRMDR    | XX          | 127                 |

| Flash Mer  | nory Controller                       |          |             |                     |

| FF8        | Flash Control                         | FCTL     | 00          | 120                 |

| FF8        | Flash Status                          | FSTAT    | 00          | 121                 |

| FF9        | Flash Page Select                     | FPS      | 00          | 122                 |

|            | Flash Sector Protect                  | FPROT    | 00          | 122                 |

| FFA        | Flash Programming Frequency High Byte | FFREQH   | 00          | 123                 |

| FFB        | Flash Programming Frequency Low Byte  | FFREQL   | 00          | 123                 |

| eZ8 CPU    |                                       |          |             |                     |

| FFC        | Flags                                 | —        | XX          | Refer to the        |

| FFD        | Register Pointer                      | RP       | XX          | eZ8 CPU             |

| FFE        | Stack Pointer High Byte               | SPH      | XX          | Core User<br>Manual |

| FFF        | Stack Pointer Low Byte                | SPL      | XX          | <u>(UM0128)</u>     |

| Note: XX = | = Undefined.                          |          |             |                     |

## Table 8. Register File Address Map (Continued)

The VBO circuit is either enabled or disabled during STOP Mode. Operations during STOP Mode are set by the VBO\_AO Flash option bit. For more details about configuring VBO\_AO, see the <u>Flash Option Bits</u> chapter on page 124.

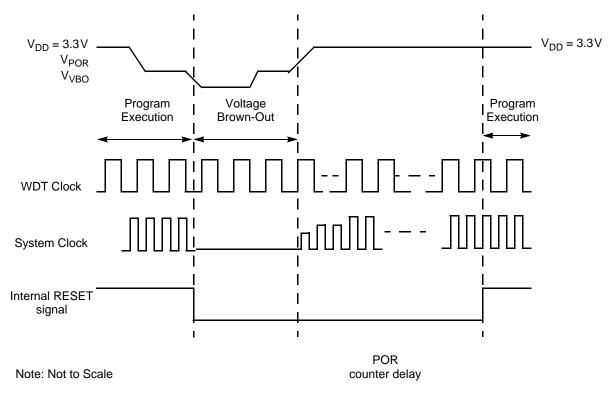

Figure 7. Voltage Brown-Out Reset Operation

# Watchdog Timer Reset

If the device is in NORMAL or STOP Mode, the WDT initiates a system reset at time-out if the WDT\_RES Flash option bit is programmed to 1. This is the unprogrammed state of the WDT\_RES Flash option bit. If the bit is programmed to 0, it configures the WDT to cause an interrupt, not a system reset, at time-out. The WDT status bit in the Reset Status (RSTSTAT) Register is set to 1 to signify that the reset was initiated by the WDT.

# **External Reset Input**

The  $\overline{\text{RESET}}$  pin has a schmitt-triggered input and an internal pull-up resistor. Once the  $\overline{\text{RESET}}$  pin is asserted for a minimum of four system clock cycles, the device progresses through the system reset sequence. Because of the possible asynchronicity of the system clock and reset signals, the required reset duration may be three or four clock periods. A

# Port A–D Output Data Register

The Port A–D Output Data Register, shown in Table 30, controls the output data to the pins.

| Bit     | 7     | 6                      | 5     | 4     | 3     | 2     | 1     | 0     |  |

|---------|-------|------------------------|-------|-------|-------|-------|-------|-------|--|

| Field   | POUT7 | POUT6                  | POUT5 | POUT4 | POUT3 | POUT2 | POUT1 | POUT0 |  |

| RESET   | 0     | 0                      | 0     | 0     | 0     | 0     | 0     | 0     |  |

| R/W     | R/W   | R/W                    | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |  |

| Address |       | FD3H, FD7H, FDBH, FDFH |       |       |       |       |       |       |  |

#### Table 30. Port A–D Output Data Register (PxOUT)

#### Bit Description

[7:0] Port Output Data

PxOUT These bits contain the data to be driven to the port pins. The values are only driven if the corresponding pin is configured as an output and the pin is not configured for alternate function operation.

0 = Drive a logical 0 (Low).

1 = Drive a logical 1 (High). High value is not driven if the drain has been disabled by setting the corresponding port output Control Register bit to 1.

Note: x indicates the specific GPIO port pin number (7–0).

- 5. Enable the timer interrupt, if appropriate and set the timer interrupt priority by writing to the relevant interrupt registers. By default, the timer interrupt is generated for both input capture and reload events. If appropriate, configure the timer interrupt to be generated only at the input capture event or the reload event by setting TICONFIG field of the TxCTL1 Register.

- 6. Configure the associated GPIO port pin for the timer input alternate function.

- 7. Write to the Timer Control Register to enable the timer and initiate counting.

In CAPTURE Mode, the elapsed time between the timer start and the capture event is calculated using the following equation:

Capture Elapsed Time (s) =  $\frac{(Capture Value - Start Value) \times Prescale}{System Clock Frequency (Hz)}$

## **CAPTURE RESTART Mode**

In CAPTURE RESTART Mode, the current timer count value is recorded when an acceptable external timer input transition occurs. The capture count value is written to the timer PWM High and Low Byte registers. The timer input is the system clock. The TPOL bit in the Timer Control Register determines whether the capture occurs on a rising edge or a falling edge of the timer input signal. When a capture event occurs, an interrupt is generated and the count value in the Timer High and Low Byte registers is reset to 0001H; counting then resumes. The INPCAP bit in the TxCTL1 Register is set to indicate that the timer interrupt is caused by an input capture event.

If no capture event occurs, the timer counts up to the 16-bit compare value that is stored in the Timer Reload High and Low Byte registers. Upon reaching the reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in the TxCTL1 Register is cleared to indicate that the timer interrupt is not caused by an input capture event.

Observe the following steps to configure a timer for CAPTURE RESTART Mode and to initiate the count.

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for CAPTURE RESTART Mode. Setting the mode also involves writing to TMODEHI bit in the TxCTL1 Register

- Set the prescale value

- Set the capture edge (rising or falling) for the timer input

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

| Bit    | Description (Continued)                                                                                                                                                     |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [0]    | Input Capture Event                                                                                                                                                         |

| INPCAP | This bit indicates whether the most recent timer interrupt is caused by a timer input capture event.                                                                        |

|        | <ul> <li>0 = Previous timer interrupt is not caused by timer input capture event.</li> <li>1 = Previous timer interrupt is caused by timer input capture event .</li> </ul> |

# Timer 0–1 Control Register 1

The Timer 0–1 Control (TxCTL1) Register, shown in Table 57, enables/disables the timers, set the prescaler value and determines the timer operating mode.

| Bit     | 7          | 6    | 5          | 4   | 3   | 2   | 1    | 0   |  |  |

|---------|------------|------|------------|-----|-----|-----|------|-----|--|--|

| Field   | TEN        | TPOL | PRES TMODE |     |     |     | PRES |     |  |  |

| RESET   | 0          | 0    | 0          | 0   | 0   | 0   | 0    | 0   |  |  |

| R/W     | R/W        | R/W  | R/W        | R/W | R/W | R/W | R/W  | R/W |  |  |

| Address | F07H, F0FH |      |            |     |     |     |      |     |  |  |

| Bit | Description                                           |

|-----|-------------------------------------------------------|

| [7] | Timer Enable                                          |

| TEN | 0 = Timer is disabled.<br>1 = Timer enabled to count. |

# ADC Data Low Bits Register

The ADC Data Low Bits Register, shown in Table 65, contain the lower bits of the ADC output as well as an overflow status bit. Access to the ADC Data Low Bits Register is read-only. Reading the ADC Data High Byte Register latches lower bits of the ADC in the ADC Low Bits Register.

| Bit     | 7    | 6   | 5        | 4 | 3 | 2 | 1 | 0 |

|---------|------|-----|----------|---|---|---|---|---|

| Field   | ADC  | CDL | Reserved |   |   |   |   |   |

| RESET   | Х    |     | Х        |   |   |   |   |   |

| R/W     | F    | र   | R        |   |   |   |   |   |

| Address | F73H |     |          |   |   |   |   |   |

| Table 65. | ADC Data | Low Bits | Register | (ADCD_L) |

|-----------|----------|----------|----------|----------|

|-----------|----------|----------|----------|----------|

| Bit   | Description                                                                                                                                                                                                                                  |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:6] | ADC Low Bits<br>00–11b = These bits are the two least significant bits of the 10-bit ADC output. These bits are<br>undefined after a reset. The low bits are latched into this register whenever the ADC Data High<br>Byte Register is read. |

| [5:0] | <b>Reserved</b><br>These bits are reserved and must be programmed to 000000.                                                                                                                                                                 |

# Sample Settling Time Register

The <u>Sample Settling</u> Time Register, shown in Table 66, is used to program the delay after the <u>SAMPLE/HOLD</u> signal is asserted and before the START signal is asserted; the conversion then begins. The number of clock cycles required for settling will vary from system to system depending on the system clock period used. The system designer must program this register to contain the number of clocks required to meet a  $0.5 \mu s$  minimum settling time.

| Bit     | 7 | 6    | 5     | 4 | 3 | 2  | 1  | 0 |

|---------|---|------|-------|---|---|----|----|---|

| Field   |   | Rese | erved |   |   | SS | ST |   |

| RESET   | 0 |      |       |   | 1 | 1  | 1  | 1 |

| R/W     |   | F    | र     |   |   | R/ | W  |   |

| Address |   | F74H |       |   |   |    |    |   |

## Table 66. Sample Settling Time (ADCSST)

| Bit          | Description                                                                          |

|--------------|--------------------------------------------------------------------------------------|

| [7:4]        | Reserved<br>These bits are reserved and must be programmed to 0000.                  |

| [3:0]<br>SST | 0h–Fh: Sample settling time in number of system clock periods to meet 0.5µs minimum. |

# **OCD Status Register**

The OCD Status Register reports status information about the current state of the debugger and the system.

| Table 98. OCD Status Register (OCDSTAT) | Table 98. | OCD | Status | Register | (OCDSTAT) |

|-----------------------------------------|-----------|-----|--------|----------|-----------|

|-----------------------------------------|-----------|-----|--------|----------|-----------|

| Bit   | 7   | 6    | 5      | 4        | 3 | 2 | 1 | 0 |  |  |

|-------|-----|------|--------|----------|---|---|---|---|--|--|

| Field | DBG | HALT | FRPENB | Reserved |   |   |   |   |  |  |

| RESET | 0   | 0    | 0      | 0        | 0 | 0 | 0 | 0 |  |  |

| R/W   | R   | R    | R      | R        | R | R | R | R |  |  |

|       |     | 1    |        |          | 1 | 1 |   | 1 |  |  |

| Bit           | Description                                                                                                                            |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>DBG    | Debug Status<br>0 = NORMAL Mode.<br>1 = DEBUG Mode.                                                                                    |

| [6]<br>HALT   | HALT Mode<br>0 = Not in HALT Mode.<br>1 = In HALT Mode.                                                                                |

| [5]<br>FRPENB | Flash Read Protect Option Bit Enable<br>0 = FRP bit enabled, that allows disabling of many OCD commands.<br>1 = FRP bit has no effect. |

| [4:0]         | <b>Reserved</b><br>These bits are reserved and must be programmed to 00000.                                                            |

| 155 | 5 |

|-----|---|

|-----|---|

| Bit             | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [5]<br>WDTEN    | Watchdog Timer Oscillator Enable1 = Watchdog Timer Oscillator is enabled.0 = Watchdog Timer Oscillator is disabled.                                                                                                                                                                                                                                                                                                                                            |

| [4]<br>POFEN    | <ul> <li>Primary Oscillator Failure Detection Enable</li> <li>1 = Failure detection and recovery of primary oscillator is enabled.</li> <li>0 = Failure detection and recovery of primary oscillator is disabled.</li> </ul>                                                                                                                                                                                                                                   |

| [3]<br>WDFEN    | Watchdog Timer Oscillator Failure Detection Enable1 = Failure detection of Watchdog Timer Oscillator is enabled.0 = Failure detection of Watchdog Timer Oscillator is disabled.                                                                                                                                                                                                                                                                                |

| [2:0]<br>SCKSEL | System Clock Oscillator Select<br>000 = Internal precision oscillator functions as system clock at 20MHz.<br>001 = Internal precision oscillator functions as system clock at 119kHz.<br>010 = Crystal oscillator or external RC oscillator functions as system clock.<br>011 = Watchdog Timer Oscillator functions as system clock.<br>100 = External clock signal on PB3 functions as system clock.<br>101 = Reserved.<br>110 = Reserved.<br>111 = Reserved. |

# **Internal Precision Oscillator**

The internal precision oscillator (IPO) is designed for use without external components. You can either manually trim the oscillator for a nonstandard frequency or use the automatic factory trimmed version to achieve a 20MHz frequency with  $\pm 4\%$  accuracy and 45%-55% duty cycle over the operating temperature and supply voltage of the device. Maximum startup time of IPO is  $25\mu$ s. IPO features include:

- On-chip RC oscillator that does not require external components

- Output frequency of either 20MHz or 119kHz (contains both a FAST and a SLOW mode)

- Trimming possible through Flash option bits with user override

- Elimination of crystals or ceramic resonators in applications where high timing accuracy is not required

# Operation

The internal oscillator is an RC relaxation oscillator with minimized sensitivity to power supply variation. By using ratio tracking thresholds, the effect of power supply voltage is cancelled out. The dominant source of oscillator error is the absolute variance of chip level fabricated components, such as capacitors. An 8-bit trimming register, incorporated into the design, compensates for absolute variation of oscillator frequency. Once trimmed the oscillator frequency is stable and does not require subsequent calibration. Trimming was performed during manufacturing and is not necessary for the user to repeat unless a frequency other than 20MHz (FAST Mode) or 119kHz (SLOW Mode) is required.

Power-down this block for minimum system power.

By default, the oscillator is configured through the Flash option bits. However, the user code overrides these trim values as described in *the* <u>Trim Bit Address Space</u> *section on page 129*.

Select one of two frequencies for the oscillator: 20MHz and 119kHz, using the OSCSEL bits in *the* <u>Oscillator Control</u> *chapter on page 151*.

| Assembly      |                                                                                                                        |     | dress<br>ode | Op<br>Code(s) | Flags |   |   |   |   |   | - Fetch | Instr. |

|---------------|------------------------------------------------------------------------------------------------------------------------|-----|--------------|---------------|-------|---|---|---|---|---|---------|--------|

| Mnemonic      | Symbolic Operation                                                                                                     | dst | src          | (Hex)         | С     | Ζ | S | V | D | н | Cycles  |        |

| SWAP dst      | $dst[7:4] \leftrightarrow dst[3:0]$                                                                                    | R   |              | F0            | Х     | * | * | Х | _ | _ | 2       | 2      |

|               |                                                                                                                        | IR  |              | F1            | -     |   |   |   |   |   | 2       | 3      |

| TCM dst, src  | (NOT dst) AND src                                                                                                      | r   | r            | 62            | —     | * | * | 0 | _ | _ | 2       | 3      |

|               |                                                                                                                        | r   | lr           | 63            | -     |   |   |   |   |   | 2       | 4      |

|               |                                                                                                                        | R   | R            | 64            | -     |   |   |   |   |   | 3       | 3      |

|               |                                                                                                                        | R   | IR           | 65            | -     |   |   |   |   |   | 3       | 4      |

|               |                                                                                                                        | R   | IM           | 66            | -     |   |   |   |   |   | 3       | 3      |

|               |                                                                                                                        | IR  | IM           | 67            | -     |   |   |   |   |   | 3       | 4      |

| TCMX dst, src | (NOT dst) AND src                                                                                                      | ER  | ER           | 68            | _     | * | * | 0 | _ | _ | 4       | 3      |

|               |                                                                                                                        | ER  | IM           | 69            | -     |   |   |   |   |   | 4       | 3      |

| TM dst, src   | dst AND src                                                                                                            | r   | r            | 72            | _     | * | * | 0 | _ | _ | 2       | 3      |

|               |                                                                                                                        | r   | lr           | 73            | -     |   |   |   |   |   | 2       | 4      |

|               |                                                                                                                        | R   | R            | 74            | -     |   |   |   |   |   | 3       | 3      |

|               |                                                                                                                        | R   | IR           | 75            | -     |   |   |   |   |   | 3       | 4      |

|               |                                                                                                                        | R   | IM           | 76            | _     |   |   |   |   |   | 3       | 3      |

|               |                                                                                                                        | IR  | IM           | 77            | _     |   |   |   |   |   | 3       | 4      |

| TMX dst, src  | dst AND src                                                                                                            | ER  | ER           | 78            | _     | * | * | 0 | _ | _ | 4       | 3      |

|               |                                                                                                                        | ER  | IM           | 79            | -     |   |   |   |   |   | 4       | 3      |

| TRAP Vector   | $SP \leftarrow SP - 2$<br>@SP \leftarrow PC<br>$SP \leftarrow SP - 1$<br>@SP \leftarrow FLAGS<br>PC \leftarrow @Vector |     | Vector       | F2            | _     | _ | _ | _ | _ | _ | 2       | 6      |

| WDT           |                                                                                                                        |     |              | 5F            | _     | _ | _ | _ | _ | _ | 1       | 2      |

### Table 114. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 = Set to 1.

Z8 Encore!<sup>®</sup> F083A Series Product Specification

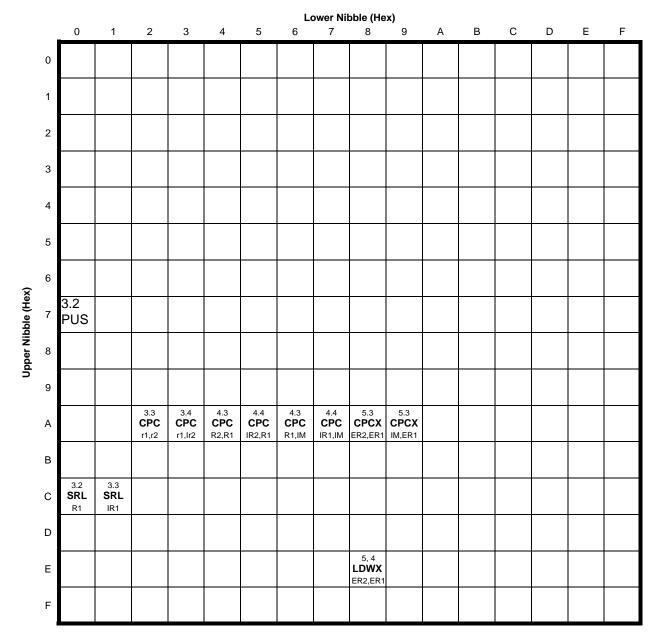

Figure 27. Second Op Code Map after 1FH

183

## Hex Address: F01

#### Table 132. Timer 0 Low Byte Register (T0L)

| Bit     | 7             | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |  |

|---------|---------------|-----|-----|-----|-----|-----|-----|-----|--|--|--|--|

| Field   | TL            |     |     |     |     |     |     |     |  |  |  |  |

| RESET   | 0 0 0 0 0 0 1 |     |     |     |     |     |     |     |  |  |  |  |

| R/W     | R/W           | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |  |  |  |

| Address |               |     |     | F0  | 1H  |     |     |     |  |  |  |  |

## Hex Address: F02

#### Table 133. Timer 0 Reload High Byte Register (T0RH)

| Bit     | 7   | 6    | 5   | 4   | 3   | 2   | 2 1 ( |     |  |  |  |  |

|---------|-----|------|-----|-----|-----|-----|-------|-----|--|--|--|--|

| Field   | TRH |      |     |     |     |     |       |     |  |  |  |  |

| RESET   | 1   | 1    | 1   | 1   | 1   | 1   | 1     | 1   |  |  |  |  |

| R/W     | R/W | R/W  | R/W | R/W | R/W | R/W | R/W   | R/W |  |  |  |  |

| Address |     | F02H |     |     |     |     |       |     |  |  |  |  |

## Hex Address: F03

#### Table 134. Timer 0 Reload Low Byte Register (T0RL)

| Bit     | 7 6 5 4 3 2 1 0 |      |     |     |     |     |     |     |  |  |  |  |

|---------|-----------------|------|-----|-----|-----|-----|-----|-----|--|--|--|--|

| Field   | TRL             |      |     |     |     |     |     |     |  |  |  |  |

| RESET   | 1 1 1 1 1 1 1 1 |      |     |     |     |     |     |     |  |  |  |  |

| R/W     | R/W             | R/W  | R/W | R/W | R/W | R/W | R/W | R/W |  |  |  |  |

| Address |                 | F03H |     |     |     |     |     |     |  |  |  |  |

#### Hex Address: F04

#### Table 135. Timer 0 PWM High Byte Register (T0PWMH)

| Bit     | 7    | 6         5         4         3         2         1         0 |     |     |     |     |     |     |  |  |  |  |

|---------|------|---------------------------------------------------------------|-----|-----|-----|-----|-----|-----|--|--|--|--|

| Field   | PWMH |                                                               |     |     |     |     |     |     |  |  |  |  |

| RESET   | 0    | 0 0 0 0 0 0 0 0                                               |     |     |     |     |     |     |  |  |  |  |

| R/W     | R/W  | R/W                                                           | R/W | R/W | R/W | R/W | R/W | R/W |  |  |  |  |

| Address |      | F04H                                                          |     |     |     |     |     |     |  |  |  |  |

## Hex Address: F05

#### Table 136. Timer 0 PWM Low Byte Register (T0PWML)

| Bit     | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|-----|-----|-----|-----|-----|-----|-----|-----|

| Field   |     |     |     | PW  | ′ML |     |     |     |

| RESET   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W     | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Address |     |     |     | F0  | 5H  |     |     |     |

## Hex Address: F06

#### Table 137. Timer 0 Control Register 0 (T0CTL0)

| Bit     | 7       | 6    | 5    | 4        | 3   | 2    | 1   | 0      |  |  |

|---------|---------|------|------|----------|-----|------|-----|--------|--|--|

| Field   | TMODEHI | TICO | NFIG | Reserved |     | PWMD |     | INPCAP |  |  |

| RESET   | 0       | 0    | 0    | 0        | 0   | 0    | 0   | 0      |  |  |

| R/W     | R/W     | R/W  | R/W  | R/W      | R/W | R/W  | R/W | R/W    |  |  |

| Address |         | F06H |      |          |     |      |     |        |  |  |

## Hex Address: F07

#### Table 138. Timer 0 Control Register 1 (T0CTL1)

| Bit     | 7   | 6    | 5    | 4   | 3   | 2     | 1   | 0   |

|---------|-----|------|------|-----|-----|-------|-----|-----|

| Field   | TEN | TPOL | PRES |     |     | TMODE |     |     |

| RESET   | 0   | 0    | 0    | 0   | 0   | 0     | 0   | 0   |

| R/W     | R/W | R/W  | R/W  | R/W | R/W | R/W   | R/W | R/W |

| Address |     | F07H |      |     |     |       |     |     |

#### Hex Address: F08

#### Table 139. Timer 1 High Byte Register (T1H)

| Bit     | 7   | 6    | 5   | 4   | 3   | 2   | 1   | 0   |  |

|---------|-----|------|-----|-----|-----|-----|-----|-----|--|

| Field   |     |      |     | Т   | Н   |     |     |     |  |

| RESET   | 0   | 0    | 0   | 0   | 0   | 0   | 0   | 0   |  |

| R/W     | R/W | R/W  | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Address |     | F08H |     |     |     |     |     |     |  |

# Hex Address: FC1

#### Table 160. IRQ0 Enable High Bit Register (IRQ0ENH)

| Bit     | 7        | 6     | 5     | 4        | 3        | 2        | 1        | 0      |  |

|---------|----------|-------|-------|----------|----------|----------|----------|--------|--|

| Field   | Reserved | T1ENH | T0ENH | Reserved | Reserved | Reserved | Reserved | ADCENH |  |

| RESET   | 0        | 0     | 0     | 0        | 0        | 0        | 0        | 0      |  |

| R/W     | R/W      | R/W   | R/W   | R/W      | R/W      | R/W      | R/W      | R/W    |  |

| Address |          | FC1H  |       |          |          |          |          |        |  |

## Hex Address: FC2

#### Table 161. IRQ0 Enable Low Bit Register (IRQ0ENL)

| Bit     | 7        | 6     | 5            | 4        | 3        | 2        | 1        | 0      |  |

|---------|----------|-------|--------------|----------|----------|----------|----------|--------|--|

| Field   | Reserved | T1ENL | <b>T0ENL</b> | Reserved | Reserved | Reserved | Reserved | ADCENL |  |

| RESET   | 0        | 0     | 0            | 0        | 0        | 0        | 0        | 0      |  |

| R/W     | R        | R/W   | R/W          | R/W      | R/W      | R        | R        | R/W    |  |

| Address |          | FC2H  |              |          |          |          |          |        |  |

## Hex Address: FC3

#### Table 162. Interrupt Request 1 Register (IRQ1)

| Bit     | 7    | 6     | 5    | 4    | 3    | 2    | 1    | 0    |  |  |

|---------|------|-------|------|------|------|------|------|------|--|--|

| Field   | PA7I | PA6CI | PA5I | PA4I | PA3I | PA2I | PA1I | PA0I |  |  |

| RESET   | 0    | 0     | 0    | 0    | 0    | 0    | 0    | 0    |  |  |

| R/W     | R/W  | R/W   | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |  |  |

| Address |      | FC3H  |      |      |      |      |      |      |  |  |

#### Hex Address: FC4

#### Table 163. IRQ1 Enable High Bit Register (IRQ1ENH)

| Bit     | 7      | 6       | 5      | 4      | 3             | 2      | 1      | 0      |  |  |

|---------|--------|---------|--------|--------|---------------|--------|--------|--------|--|--|

| Field   | PA7ENH | PA6CENH | PA5ENH | PA4ENH | <b>PA3ENH</b> | PA2ENH | PA1ENH | PA0ENH |  |  |

| RESET   | 0      | 0       | 0      | 0      | 0             | 0      | 0      | 0      |  |  |

| R/W     | R/W    | R/W     | R/W    | R/W    | R/W           | R/W    | R/W    | R/W    |  |  |

| Address |        | FC4H    |        |        |               |        |        |        |  |  |

## Hex Address: FDF

| Table 185. | Port D | Output | Data | Register | (PDOUT) |

|------------|--------|--------|------|----------|---------|

|            | IOIUD  | Output | Dutu | Register |         |

| Bit     | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |  |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|--|

| Field   | POUT7 | POUT6 | POUT5 | POUT4 | POUT3 | POUT2 | POUT1 | POUT0 |  |

| RESET   | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |  |

| R/W     | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |  |

| Address |       | FDFH  |       |       |       |       |       |       |  |

#### Hex Addresses: FE0–FEF

This address range is reserved.

# Watchdog Timer (WDT)

For more information about the Watchdog Timer registers, see the <u>Watchdog Timer Con-</u> trol Register Definitions section on page 95.

#### Hex Address: FF0

This register address is shared with the read-only Reset Status Register.

Table 186. Watchdog Timer Control Register (WDTCTL)

| Bit     | 7 | 6 | 5 | 4   | 3    | 2 | 1 | 0 |

|---------|---|---|---|-----|------|---|---|---|

| Field   |   |   |   | WDT | UNLK |   |   |   |

| RESET   | Х | Х | Х | Х   | Х    | Х | Х | Х |

| R/W     | W | W | W | W   | W    | W | W | W |

| Address |   | * |   | FF  | ОH   | * | · |   |

| Bit     | 7                              | 6     | 5   | 4   | 3        | 2 | 1 | 0 |  |

|---------|--------------------------------|-------|-----|-----|----------|---|---|---|--|

| Field   | POR                            | STOP  | WDT | EXT | Reserved |   |   |   |  |

| RESET   | See <u>Table 12</u> on page 29 |       |     | 0   | 0        | 0 | 0 | 0 |  |

| R/W     | R                              | R R R |     |     | R R R    |   |   | R |  |

| Address |                                | FF0H  |     |     |          |   |   |   |  |

#### Table 187. Reset Status Register (RSTSTAT)

## Hex Address: FF1

#### Table 188. Watchdog Timer Reload Upper Byte Register (WDTU)

| Bit        | 7            | 6             | 5            | 4             | 3              | 2              | 1         | 0    |  |

|------------|--------------|---------------|--------------|---------------|----------------|----------------|-----------|------|--|

| Field      | WDTU         |               |              |               |                |                |           |      |  |

| RESET      | 0            | 0             | 0            | 0             | 0              | 0              | 0         | 0    |  |

| R/W        | R/W*         | R/W*          | R/W*         | R/W*          | R/W*           | R/W*           | R/W*      | R/W* |  |

| Address    | FF1H         |               |              |               |                |                |           |      |  |

| Note: *R = | Read returns | s the current | WDT count va | alue; W = Wri | te sets the ap | propriate relo | ad value. |      |  |

## Hex Address: FF2

#### Table 189. Watchdog Timer Reload High Byte Register (WDTH)

| Bit                                                                                               | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------------------------------------------------------------------------------------------------|------|------|------|------|------|------|------|------|

| Field                                                                                             | WDTH |      |      |      |      |      |      |      |

| RESET                                                                                             | 0    | 0    | 0    | 0    | 0    | 1    | 0    | 0    |

| R/W                                                                                               | R/W* |

| Address                                                                                           | FF2H |      |      |      |      |      |      |      |

| Note: *R = Read returns the current WDT count value; W = Write sets the appropriate reload value. |      |      |      |      |      |      |      |      |

## Hex Address: FF3

#### Table 190. Watchdog Timer Reload Low Byte Register (WDTL)

| Bit                                                                                               | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------------------------------------------------------------------------------------------------|------|------|------|------|------|------|------|------|

| Field                                                                                             | WDTL |      |      |      |      |      |      |      |

| RESET                                                                                             | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| R/W                                                                                               | R/W* |

| Address                                                                                           | FF3H |      |      |      |      |      |      |      |

| Note: *R = Read returns the current WDT count value; W = Write sets the appropriate reload value. |      |      |      |      |      |      |      |      |

# Hex Addresses: FF4–FF5

This address range is reserved.

#### Z8 Encore!<sup>®</sup> F083A Series Product Specification

234

high and low byte registers 84, 86 TM 167 TMX 167 TRAP 169

## U

UART 4

# V

vector 165 voltage brown-out reset (VBR) 24 voltage measurement timing diagram 100

# W

watch-dog timer approximate time-out delay 92 approximate time-out delays 92, 108, 151, 161 CNTL 24 control register 95, 154 electrical characteristics and timing 193 interrupt in noromal operation 93 interrupt in stop mode 93 operation 92, 108, 151, 161 refresh 93, 168 reload unlock sequence 94 reload upper, high and low registers 96 reset 25 reset in normal operation 94 reset in Stop mode 94 time-out response 93 WDTCTL register 29, 95, 109, 154, 213, 214, 222 WDTH register 96, 223 WDTL register 97, 223 working register 164 working register pair 165 WTDU register 96, 223

# Χ

X 165

XOR 169 XORX 169

# Ζ

Z8 Encore! block diagram 3 features 1 part selection guide 2