Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Active                                                    |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | -                                                         |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 17                                                        |

| Program Memory Size        | 4KB (4K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 7x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 20-VQFN Exposed Pad                                       |

| Supplier Device Package    | 20-QFN (5x5)                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f043aqh020sg |

# **Table of Contents**

| Revision Historyii                 |

|------------------------------------|

| List of Figures                    |

| List of Tables                     |

| Overview                           |

| Features                           |

| Part Selection Guide               |

| Block Diagram                      |

| CPU and Peripheral Overview        |

| General Purpose Input/Output       |

| Flash Controller                   |

| Nonvolatile Data Storage           |

| Internal Precision Oscillator      |

| External Crystal Oscillator        |

| 10-Bit Analog-to-Digital Converter |

| Analog Comparator                  |

| Timers                             |

| Interrupt Controller               |

| Reset Controller                   |

| On-Chip Debugger                   |

| Acronyms and Expansions            |

| Pin Description                    |

| Available Packages                 |

| Pin Configurations                 |

| Signal Descriptions                |

| Pin Characteristics                |

|                                    |

| Address Space                      |

| Register File                      |

| Program Memory                     |

| Data Memory                        |

| Flash Information Area             |

| Register Map                       |

| Reset and Stop Mode Recovery       |

| Reset Types                        |

| Reset Sources                      |

| Power-On Reset 2                   |

| Table 89.  | VBO Trim Definition                           | 132 |

|------------|-----------------------------------------------|-----|

| Table 90.  | Trim Option Bits at 0006H (TCLKFLT)           | 132 |

| Table 91.  | ClkFlt Delay Control Definition               | 133 |

| Table 92.  | Write Status Byte                             | 135 |

| Table 93.  | Read Status Byte                              | 136 |

| Table 94.  | NVDS Read Time                                | 137 |

| Table 95.  | OCD Baud-Rate Limits                          | 142 |

| Table 96.  | On-Chip Debugger Command Summary              | 144 |

| Table 97.  | OCD Control Register (OCDCTL)                 | 149 |

| Table 98.  | OCD Status Register (OCDSTAT)                 | 150 |

| Table 99.  | Oscillator Configuration and Selection        | 152 |

| Table 100. | Oscillator Control Register (OSCCTL)          | 154 |

| Table 101. | Recommended Crystal Oscillator Specifications | 158 |

| Table 102. | Assembly Language Syntax Example 1            | 163 |

| Table 103. | Assembly Language Syntax Example 2            | 164 |

| Table 104. | Notational Shorthand                          | 164 |

| Table 105. | Additional Symbols                            | 165 |

| Table 106. | Arithmetic Instructions                       | 166 |

| Table 107. | Bit Manipulation Instructions                 | 167 |

| Table 108. | Block Transfer Instructions                   | 167 |

| Table 109. | CPU Control Instructions                      | 168 |

| Table 110. | Load Instructions                             | 168 |

| Table 111. | Logical Instructions                          | 169 |

| Table 112. | Program Control Instructions                  | 169 |

| Table 113. | Rotate and Shift Instructions                 | 170 |

| Table 114. | eZ8 CPU Instruction Summary                   | 171 |

| Table 115. | Op Code Map Abbreviations                     | 181 |

| Table 116. | Absolute Maximum Ratings                      | 184 |

| Table 117. | DC Characteristics                            | 185 |

| Table 118. | AC Characteristics                            | 188 |

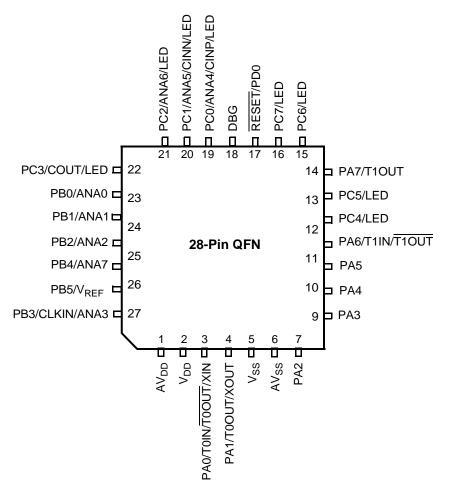

Figure 5. Z8F083A Series in 28-Pin QFN Package

# Low-Power Modes

The Z8 Encore! F083A Series products contain power saving features. The highest level of power reduction is provided by the STOP Mode. The next level of power reduction is provided by the HALT Mode.

Further power savings are implemented by disabling the individual peripheral blocks while in NORMAL Mode.

**Caution:** The user must not enable the pull-up register bits for unused GPIO pins, because these ports output by default to V<sub>SS</sub>. Unused GPIO pins include those missing on 20-pin packages and ADC-enabled 28-pin packages.

# **STOP Mode**

Executing the eZ8 CPU's STOP instruction places the device into STOP Mode. In STOP Mode, the operating characteristics are:

- Primary crystal oscillator and internal precision oscillator are stopped; XIN and XOUT (if previously enabled) are disabled and PAO/PA1 revert to the states programmed by the GPIO registers

- System clock is stopped

- eZ8 CPU is stopped

- Program counter (PC) stops incrementing

- WDT's internal RC oscillator continues to operate if enabled by the Oscillator Control Register

- If enabled, the WDT logic continues to operate

- If enabled for operation in STOP Mode by the associated Flash option bit, the VBO protection circuit continues to operate

- All other on-chip peripherals are idle

To minimize the current in STOP Mode, all GPIO pins that are configured as digital inputs must be driven to  $V_{DD}$  when the pull-up register bit is enabled or to one of power rail ( $V_{DD}$  or GND) when the pull-up register bit is disabled. The device is brought out of STOP Mode using Stop Mode Recovery. For more information about Stop Mode Recovery, see the Reset and Stop Mode Recovery chapter on page 21.

# Port A-D Output Control Subregisters

The Port A–D output control subregister is accessed through the Port A–D Control Register by writing 03H to the Port A–D Address Register. See Table 23. Setting the bits in the Port A–D output control subregisters to 1, configures the specified port pins for opendrain operation. These subregisters affect the pins directly and, as a result, alternate functions are also affected.

Table 23. Port A-D Output Control Subregisters (PxOC)

| Bit     | 7         | 6            | 5           | 4             | 3            | 2            | 1            | 0        |

|---------|-----------|--------------|-------------|---------------|--------------|--------------|--------------|----------|

| Field   | POC7      | POC6         | POC5        | POC4          | POC3         | POC2         | POC1         | POC0     |

| RESET   | 0         | 0            | 0           | 0             | 0            | 0            | 0            | 0        |

| R/W     | R/W       | R/W          | R/W         | R/W           | R/W          | R/W          | R/W          | R/W      |

| Address | If 03H ir | n Port A–D A | Address Reg | jister, acces | sible throug | h the Port A | –D Control F | Register |

| Bit     | Description                                                                                                                                                                                                |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0]   | Port Output Control                                                                                                                                                                                        |

| POCx    | These bits function independently of the alternate function bit and always disable the drains, if set to 1.  0 = The drains are enabled for any output mode (unless overridden by the alternate function). |

|         | 1 = The drain of the associated pin is disabled (OPEN-DRAIN mode).                                                                                                                                         |

| Note: x | indicates the specific GPIO port pin number (7–0).                                                                                                                                                         |

# **Interrupt Control Register**

The Interrupt Control (IRQCTL) Register, shown in Table 49, contains the master enable bit for all interrupts.

**Table 49. Interrupt Control Register (IRQCTL)**

| Bit     | 7    | 6    | 5 | 4 | 3        | 2 | 1 | 0 |

|---------|------|------|---|---|----------|---|---|---|

| Field   | IRQE |      |   |   | Reserved |   |   |   |

| RESET   | 0    | 0    | 0 | 0 | 0        | 0 | 0 | 0 |

| R/W     | R/W  | R    | R | R | R        | R | R | R |

| Address |      | FCFH |   |   |          |   |   |   |

| Bit         | Description                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>IRQE | Interrupt Request Enable This bit is set to 1 by executing an EI (enable interrupts) or IRET (interrupt return) instruction or by a direct register write of 1 to this bit. It is reset to 0 by executing a DI instruction, eZ8 CPU acknowledgement of an interrupt request, reset or by a direct register write of a 0 to this bit. 0 = Interrupts are disabled. 1 = Interrupts are enabled. |

| [6:0]       | Reserved These bits are reserved and must be programmed to 0000000.                                                                                                                                                                                                                                                                                                                           |

PWM Output High Time Ratio (%) =

$$\frac{\text{Reload Value} - \text{PWM Value}}{\text{Reload Value}} \times 100$$

If TPOL bit is set to 1, the ratio of the PWM output high time to the total period is represented by:

PWM Output High Time Ratio (%) =

$$\frac{\text{PWM Value}}{\text{Reload Value}} \times 100$$

### **CAPTURE Mode**

In CAPTURE Mode, the current timer count value is recorded when the appropriate external timer input transition occurs. The capture count value is written to the timer PWM High and Low Byte registers. The timer input is the system clock. The TPOL bit in the Timer Control Register determines if a capture event occurs on a rising edge or a falling edge of the timer input signal.

When a capture event occurs, an interrupt is generated and the timer continues counting. The INPCAP bit in the TxCTL1 Register is set to indicate the timer interrupt because of an input capture event.

The timer continues counting up to the 16-bit reload value stored in the Timer Reload High and Low Byte registers. Upon reaching the reload value, the timer generates an interrupt and continues counting. The INPCAP bit in the TxCTL1 Register clears, indicating that the timer interrupt has not occurred because of an input capture event.

Observe the following steps to configure a timer for CAPTURE Mode and initiating the count.

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for CAPTURE Mode

- Set the prescale value

- Set the capture edge (rising or falling) for the timer input

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. Clear the timer PWM High and Low Byte registers to 0000H. Clearing these registers allows user software to determine if interrupts were generated either by a capture event or by a reload. If the PWM High and Low Byte registers still contain 0000H after the interrupt, the interrupt were generated by a reload.

## Bit Description (Continued)

#### [6] Timer Input/Output Polarity

TPOL Operation of this bit is a function of the current operating mode of the timer.

#### **ONE-SHOT Mode**

When the timer is disabled, the timer output signal is set to the value of this bit. When the timer is enabled, the timer output signal is complemented on timer reload.

#### **CONTINUOUS Mode**

When the timer is disabled, the timer output signal is set to the value of this bit. When the timer is enabled and reloaded, the timer output signal is complemented.

#### **COUNTER Mode**

If the timer is disabled, the timer output signal is set to the value of this bit.

If the timer is enabled the timer output signal is complemented after timer reload.

- 0 = Count occurs on the rising edge of the timer input signal.

- 1 = Count occurs on the falling edge of the timer input signal.

#### **PWM SINGLE OUTPUT Mode**

- 0 = Timer output is forced low (0), when the timer is disabled. The timer output is forced high (1), when the timer is enabled and the PWM count matches and the timer output is forced low (0), when the timer is enabled and reloaded.

- 1 = Timer output is forced high (1), when the timer is disabled. The timer output is forced low(0), when the timer is enabled and the PWM count matches and forced high (1) when the timer is enabled and reloaded.

#### **CAPTURE Mode**

- 0 = Count is captured on the rising edge of the timer input signal.

- 1 = Count is captured on the falling edge of the timer input signal.

#### **COMPARE Mode**

When the timer is disabled, the timer output signal is set to the value of this bit. When the timer is enabled and reloaded, the timer output signal is complemented.

#### **GATED Mode**

- 0 = Timer counts when the timer input signal is high (1) and interrupts are generated on the falling edge of the timer input.

- 1 = Timer counts when the timer input signal is low (0) and interrupts are generated on the rising edge of the timer input.

#### **CAPTURE/COMPARE Mode**

- 0 = Counting is started on the first rising edge of the timer input signal. The current count is captured on subsequent rising edges of the timer input signal.

- 1 = Counting is started on the first falling edge of the timer input signal. The current count is captured on subsequent falling edges of the timer input signal.

Table 62. Watchdog Timer Reload Low Byte Register (WDTL)

| Bit                                                                                           | 7            | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|-----------------------------------------------------------------------------------------------|--------------|------|------|------|------|------|------|------|

| Field                                                                                         |              |      |      | WE   | DTL  |      |      |      |

| RESET                                                                                         | 0            | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| R/W                                                                                           | R/W*         | R/W* | R/W* | R/W* | R/W* | R/W* | R/W* | R/W* |

| Address                                                                                       | Address FF3H |      |      |      |      |      |      |      |

| Note: *A read returns the current WDT count value; a write sets the appropriate reload value. |              |      |      |      |      |      |      |      |

| Bit   | Description                                    |

|-------|------------------------------------------------|

| [7:0] | WDT Reload Low Byte                            |

| WDTL  | LSB, bits[7:0] of the 24-bit WDT reload value. |

| Bit      |                                                                |

|----------|----------------------------------------------------------------|

| Position | Description (Continued)                                        |

| [2:0]    | Analog Input Select                                            |

| ANAIN    | 000 = ANA0 input is selected for analog-to-digital conversion. |

|          | 001 = ANA1 input is selected for analog-to-digital conversion. |

|          | 010 = ANA2 input is selected for analog-to-digital conversion. |

|          | 011 = ANA3 input is selected for analog-to-digital conversion. |

|          | 100 = ANA4 input is selected for analog-to-digital conversion. |

|          | 101 = ANA5 input is selected for analog-to-digital conversion. |

|          | 110 = ANA6 input is selected for analog-to-digital conversion. |

|          | 111 = ANA7 input is selected for analog-to-digital conversion. |

# **ADC Data High Byte Register**

The ADC Data High Byte Register, shown in Table 64, contains the upper eight bits of the ADC output. Access to the ADC Data High Byte Register is read-only. Reading the ADC Data High Byte Register latches data in the ADC Low Bits Register.

Table 64. ADC Data High Byte Register (ADCD\_H)

| Bit     | 7 | 6     | 5 | 4   | 3  | 2 | 1 | 0 |

|---------|---|-------|---|-----|----|---|---|---|

| Field   |   | ADCDH |   |     |    |   |   |   |

| RESET   | X |       |   |     |    |   |   |   |

| R/W     | R |       |   |     |    |   |   |   |

| Address |   |       |   | F7: | 2H |   |   |   |

| Bit<br>Position | Value<br>(H) | Description                                                                                                         |

|-----------------|--------------|---------------------------------------------------------------------------------------------------------------------|

| [7:0]           | 00h–FFh      | ADC high byte  The last conversion output is held in the data registers until the next ADC conversion is completed. |

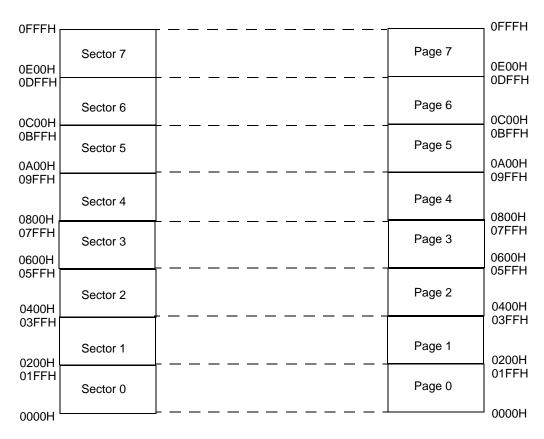

Figure 14. 4K Flash with NVDS

| Bit                  | Description                                                                           |

|----------------------|---------------------------------------------------------------------------------------|

| [7:3]<br>ADCREF_TRIM | ADC Reference Voltage Trim Byte Contains trimming bits for the ADC reference voltage. |

| [2:0]                | Reserved These bits are reserved and must be programmed to 111.                       |

**)**

**Note:** The bit values indicated in Table 85 are set at the factory; no calibration is required.

# **Trim Bit Address 0001H**

Table 86. Trim Option Bits at 0001H (TADC\_COMP)

| Bit       | 7                                               | 6        | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

|-----------|-------------------------------------------------|----------|-----|-----|-----|-----|-----|-----|--|--|

| Field     |                                                 | Reserved |     |     |     |     |     |     |  |  |

| RESET     | U                                               | U        | U   | U   | U   | U   | U   | U   |  |  |

| R/W       | R/W                                             | R/W      | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| Address   | Information Page Memory 0021H                   |          |     |     |     |     |     |     |  |  |

| Note: U = | Note: U = Unchanged by Reset; R/W = Read/Write. |          |     |     |     |     |     |     |  |  |

| Bit   | Description                                                                              |

|-------|------------------------------------------------------------------------------------------|

| [7:0] | Reserved                                                                                 |

|       | These bits are reserved. Altering this register can result in incorrect device operation |

**Note:** The bit values used in Table 86 are set at the factory; no calibration is required.

| Bit        | Description (Continued)                           |

|------------|---------------------------------------------------|

| [2]        | Reserved                                          |

|            | This bit is reserved and must be programmed to 1. |

| [1:0]      | Filter Selection                                  |

| FilterSely | 2-bit Clock Filter Mode selection.                |

|            | 00 = No filter.                                   |

|            | 01 = Filter low level noise on high level signal. |

|            | 10 = Filter high level noise on low level signal. |

|            | 11 = Filter both.                                 |

**)**

**Note:** The bit values used in Table 90 are set at the factory; no calibration is required.

**Table 91. ClkFlt Delay Control Definition**

| DlyCtl3, DlyCtl2, DlyCtl1        | Low-Noise Pulse on High Signal (ns) | High-Noise Pulse on<br>Low Signal (ns) |

|----------------------------------|-------------------------------------|----------------------------------------|

| 000                              | 5                                   | 5                                      |

| 001                              | 7                                   | 7                                      |

| 010                              | 9                                   | 9                                      |

| 011                              | 11                                  | 11                                     |

| 100                              | 13                                  | 13                                     |

| 101                              | 17                                  | 17                                     |

| 110                              | 20                                  | 20                                     |

| 111                              | 25                                  | 25                                     |

| Note: The variation is about 30% | ).                                  |                                        |

# **Operation**

The following section describes the operation of the On-Chip Debugging function.

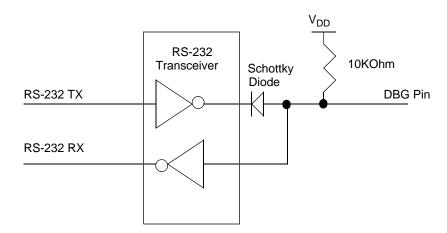

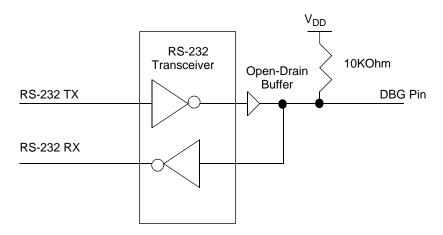

## **OCD** Interface

The On-Chip Debugger uses the DBG pin for communication with an external host. This one-pin interface is a bidirectional open-drain interface that transmits and receives data. Data transmission is half-duplex, which means transmission and data retrieval cannot occur simultaneously. The serial data on the DBG pin is sent using the standard asynchronous data format defined in RS-232. This pin creates an interface between the Z8 Encore! F083A Series products and the serial port of a host PC using minimal external hardware. Two different methods for connecting the DBG pin to an RS-232 interface are displayed in Figures 18 and 19. The recommended method is the buffered implementation depicted in Figure 19. The DBG pin must always be connected to V<sub>DD</sub> through an external pull-up resistor.

**Caution:** For operation of the On-Chip Debugger, all power pins (V<sub>DD</sub> and AV<sub>DD</sub>) must be supplied with power and all ground pins (V<sub>SS</sub> and AV<sub>SS</sub>) must be properly grounded. The DBG pin is open-drain and must always be connected to V<sub>DD</sub> through an external pull-up resistor to ensure proper operation.

Figure 18. Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface, # 1 of 2

Figure 19. Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface, #2 of 2

## **DEBUG Mode**

F083A Series devices, when in DEBUG Mode, feature the following operating characteristics:

- The eZ8 CPU fetch unit stops, idling the eZ8 CPU, unless directed by the OCD to execute specific instructions

- The system clock operates, unless the device is in STOP Mode

- All enabled on-chip peripherals operate, unless the device is in STOP Mode

- Automatically exits HALT Mode

- Constantly refreshes the Watchdog Timer, if enabled

# **Entering DEBUG Mode**

- The device enters DEBUG Mode after the eZ8 CPU executes a Breakpoint (BRK) instruction

- If the DBG pin is held Low during the most recent system reset clock cycle, the device enters DEBUG Mode upon exiting system reset

## **Exiting DEBUG Mode**

The device exits DEBUG Mode upon any of the following operations:

- Clearing the DBGMODE bit in the OCD Control Register to 0

- Power-On Reset

- Voltage Brown-Out reset

If the OCD receives a serial break (nine or more continuous bits low), the autobaud detector/generator resets. Reconfigure the autobaud detector/generator by sending 80H.

## **OCD Serial Errors**

The On-Chip Debugger detects any of the following error conditions on the DBG pin:

- Serial break (a minimum of nine continuous bits Low)

- Framing error (received Stop bit is Low)

- Transmit collision (simultaneous transmission by OCD and host detected by the OCD)

When the OCD detects one of these errors, it aborts any command currently in progress, transmits a four character long serial break back to the host and resets the autobaud detector/generator. A framing error or transmit collision may be caused by the host sending a serial break to the OCD. As a result of the open-drain nature of the interface, returning a serial break back to the host only extends the length of the serial break if the host releases the serial break early.

The host transmits a serial break on the DBG pin when first connecting to the Z8 Encore! F083A Series devices or when recovering from an error. A serial break from the host resets the autobaud generator/detector, but does not reset the OCD Control Register. A serial break leaves the device in DEBUG Mode, if that is the current mode. The OCD is held in reset until the end of the serial break when the DBG pin returns high. Because of the open-drain nature of the DBG pin, the host sends a serial break to the OCD even if the OCD is transmitting a character.

# **Breakpoints**

Execution breakpoints are generated using the BRK instruction (Opcode 00H). When the eZ8 CPU decodes a BRK instruction, it signals the On-Chip Debugger. If breakpoints are enabled, the OCD enters DEBUG Mode and idles the eZ8 CPU. If breakpoints are not enabled, the OCD ignores the BRK signal and the BRK instruction operates as an NOP instruction.

# **Breakpoints in Flash Memory**

The BRK instruction is Opcode 00H, which corresponds to the fully programmed state of a byte in Flash memory. To implement a breakpoint, write 00H to the required break address overwriting the current instruction. To remove a breakpoint, the corresponding page of Flash memory must be erased and reprogrammed with the original data.

**Hex Address: FC5**

Table 164. IRQ1 Enable Low Bit Register (IRQ1ENL)

| Bit     | 7      | 6       | 5      | 4      | 3      | 2      | 1      | 0      |

|---------|--------|---------|--------|--------|--------|--------|--------|--------|

| Field   | PA7ENL | PA6CENL | PA5ENL | PA4ENL | PA3ENL | PA2ENL | PA1ENL | PA0ENL |

| RESET   | 0      | 0       | 0      | 0      | 0      | 0      | 0      | 0      |

| R/W     | R/W    | R/W     | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |

| Address |        | FC5H    |        |        |        |        |        |        |

**Hex Address: FC6**

Table 165. Interrupt Request 2 Register (IRQ2)

| Bit     | 7   | 6        | 5   | 4   | 3   | 2    | 1    | 0    |

|---------|-----|----------|-----|-----|-----|------|------|------|

| Field   |     | Reserved |     |     |     | PC2I | PC1I | PC0I |

| RESET   | 0   | 0        | 0   | 0   | 0   | 0    | 0    | 0    |

| R/W     | R/W | R/W      | R/W | R/W | R/W | R/W  | R/W  | R/W  |

| Address |     | FC6H     |     |     |     |      |      |      |

**Hex Address: FC7**

Table 166. IRQ2 Enable High Bit Register (IRQ2ENH)

| Bit     | 7   | 6    | 5     | 4   | 3     | 2     | 1     | 0     |

|---------|-----|------|-------|-----|-------|-------|-------|-------|

| Field   |     | Rese | erved |     | C3ENH | C2ENH | C1ENH | C0ENH |

| RESET   | 0   | 0    | 0     | 0   | 0     | 0     | 0     | 0     |

| R/W     | R/W | R/W  | R/W   | R/W | R/W   | R/W   | R/W   | R/W   |

| Address |     |      |       | FC  | 7H    |       |       |       |

**Hex Address: FC8**

Table 167. IRQ2 Enable Low Bit Register (IRQ2ENL)

| Bit     | 7   | 6        | 5   | 4   | 3   | 2     | 1     | 0     |

|---------|-----|----------|-----|-----|-----|-------|-------|-------|

| Field   |     | Reserved |     |     |     | C2ENL | C1ENL | C0ENL |

| RESET   | 0   | 0        | 0   | 0   | 0   | 0     | 0     | 0     |

| R/W     | R/W | R/W      | R/W | R/W | R/W | R/W   | R/W   | R/W   |

| Address |     | FC8H     |     |     |     |       |       |       |

**Hex Addresses: FC9-FCC**

This address range is reserved.

**Hex Address: FCD**

Table 168. Interrupt Edge Select Register (IRQES)

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|------|

| Field   | IES7 | IES6 | IES5 | IES4 | IES3 | IES2 | IES1 | IES0 |

| RESET   | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| R/W     | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |

| Address |      | FCDH |      |      |      |      |      |      |

**Hex Address: FCE**

Table 169. Shared Interrupt Select Register (IRQSS)

| Bit     | 7        | 6     | 5        | 4   | 3   | 2   | 1   | 0   |

|---------|----------|-------|----------|-----|-----|-----|-----|-----|

| Field   | Reserved | PA6CS | Reserved |     |     |     |     |     |

| RESET   | 0        | 0     | 0        | 0   | 0   | 0   | 0   | 0   |

| R/W     | R/W      | R/W   | R/W      | R/W | R/W | R/W | R/W | R/W |

| Address |          | FCEH  |          |     |     |     |     |     |

**Hex Address: FCF**

Table 170. Interrupt Control Register (IRQCTL)

| Bit     | 7    | 6    | 5           | 4 | 3 | 2 | 1 | 0 |  |

|---------|------|------|-------------|---|---|---|---|---|--|

| Field   | IRQE |      | Reserved    |   |   |   |   |   |  |

| RESET   | 0    | 0    | 0           | 0 | 0 | 0 | 0 | 0 |  |

| R/W     | R/W  | R    | R R R R R R |   |   |   |   |   |  |

| Address |      | FCFH |             |   |   |   |   |   |  |

| G                                                | indirect register pair 164         |

|--------------------------------------------------|------------------------------------|

| gated mode 89                                    | indirect working register 164      |

| general-purpose I/O 33                           | indirect working register pair 164 |

| GPIO 4, 33                                       | instruction set, ez8 CPU 162       |

| alternate functions 34                           | instructions                       |

| architecture 33                                  | ADC 166                            |

| control register definitions 39                  | ADCX 166                           |

| input data sample timing 194                     | ADD 166                            |

| interrupts 39                                    | ADDX 166                           |

| port A-C pull-up enable sub-registers 46, 47, 48 | AND 169                            |

| port A-H address registers 40                    | ANDX 169                           |

| port A-H alternate function sub-registers 42     | arithmetic 166                     |

| port A-H control registers 41                    | BCLR 167                           |

| port A-H data direction sub-registers 41         | BIT 167                            |

| port A-H high drive enable sub-registers 44      | bit manipulation 167               |

| port A-H input data registers 49                 | block transfer 167                 |

| port A-H output control sub-registers 43         | BRK 169                            |

| port A-H output data registers 50, 51            | BSET 167                           |

| port A-H stop mode recovery sub-registers 45     | BSWAP 167, 170                     |

| port availability by device 33                   | BTJ 169                            |

| port input timing 194                            | BTJNZ 166, 169                     |

| port output timing 195                           | BTJZ 169                           |

|                                                  | CALL 169                           |

|                                                  | CCF 167, 168                       |

| Н                                                | CLR 168                            |

| H 165                                            | COM 169                            |

| HALT 168                                         | CP 166                             |

| halt mode 31, 168                                | CPC 166                            |

| hexadecimal number prefix/suffix 165             | CPCX 166                           |

| r                                                | CPU control 168                    |

|                                                  | CPX 166                            |

|                                                  | DA 166                             |

| I2C 4                                            | DEC 166                            |

| IM 164                                           | DECW 166                           |

| immediate data 164                               | DI 168                             |

| immediate operand prefix 165                     | DJNZ 169                           |

| INC 166                                          | EI 168                             |

| increment 166                                    | HALT 168                           |

| increment word 166                               | INC 166                            |

| INCW 166                                         | INCW 166                           |

| indexed 165                                      | IRET 169                           |

| indirect address prefix 165                      | JP 169                             |

| indirect register 164                            | LD 168                             |

|                                                  | LDC 168                            |

| ADC channel 1 102                        | using a GPIO port pin transition 27, 28          |

|------------------------------------------|--------------------------------------------------|

| ADC data high byte 103                   | using watch-dog timer time-out 27                |

| ADC data low bit 104, 105, 106, 107, 211 | SUB 167                                          |

| reset                                    | subtract 167                                     |

| and stop mode characteristics 22         | subtract - extended addressing 167               |

| and stop mode recovery 21                | subtract with carry 167                          |

| carry flag 167                           | subtract with carry - extended addressing 167    |

| sources 23                               | SUBX 167                                         |

| RET 169                                  | SWAP 170                                         |

| return 169                               | swap nibbles 170                                 |

| RL 170                                   | symbols, additional 165                          |

| RLC 170                                  |                                                  |

| rotate and shift instuctions 170         | Т                                                |

| rotate left 170                          | -                                                |

| rotate left through carry 170            | Table 134. Power Consumption Reference Table     |

| rotate right 170                         | 196                                              |

| rotate right through carry 170           | TCM 167                                          |

| RP 165                                   | TCMX 167                                         |

| RR 165, 170                              | test complement under mask 167                   |

| rr 165                                   | test complement under mask - extended addressing |

| RRC 170                                  | 167                                              |

|                                          | test under mask 167                              |

| S                                        | test under mask - extended addressing 167        |

|                                          | tiing diagram, voltage measurement 100           |

| SBC 167                                  | timer signals 11                                 |

| SCF 167, 168                             | timers 69                                        |

| second opcode map after 1FH 183          | architecture 69                                  |

| set carry flag 167, 168                  | block diagram 70                                 |

| set register pointer 168                 | capture mode 78, 79, 89, 90                      |

| shift right arithmatic 170               | capture/compare mode 82, 89                      |

| shift right logical 170                  | compare mode 80, 89                              |

| signal descriptions 11                   | continuous mode 71, 89                           |

| software trap 169                        | counter mode 72, 73                              |

| source operand 165                       | counter modes 89                                 |

| SP 165                                   | gated mode 81, 89                                |

| SRA 170                                  | one-shot mode 70, 89                             |

| src 165                                  | operating mode 70                                |

| SRL 170                                  | PWM mode 75, 76, 89, 90                          |

| SRP 168                                  | reading the timer count values 83                |

| stack pointer 165                        | reload high and low byte registers 84            |

| STOP 168                                 | timer control register definitions 83            |

| stop mode 30, 168                        | timer output signal operation 83                 |

| stop mode recovery                       | timers 0-3                                       |

| sources 26                               | control registers 87, 88                         |