Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                           |  |

|----------------------------|-----------------------------------------------------------|--|

| Product Status             | Active                                                    |  |

| Core Processor             | eZ8                                                       |  |

| Core Size                  | 8-Bit                                                     |  |

| Speed                      | 20MHz                                                     |  |

| Connectivity               | -                                                         |  |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |  |

| Number of I/O              | 23                                                        |  |

| Program Memory Size        | 8KB (8K x 8)                                              |  |

| Program Memory Type        | FLASH                                                     |  |

| EEPROM Size                | -                                                         |  |

| RAM Size                   | 256 x 8                                                   |  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |  |

| Data Converters            | A/D 8x10b                                                 |  |

| Oscillator Type            | Internal                                                  |  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |  |

| Mounting Type              | Surface Mount                                             |  |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                            |  |

| Supplier Device Package    | 28-SSOP                                                   |  |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f083ahj020eg |  |

# Z8 Encore!® F083A Series Product Specification

χi

| Figure 27. | Second Op Code Map after 1FH                         | 183 |

|------------|------------------------------------------------------|-----|

| Figure 28. | $I_{CC}$ versus System Clock Frequency (HALT Mode)   | 187 |

| Figure 29. | $I_{CC}$ versus System Clock Frequency (NORMAL Mode) | 187 |

| Figure 30. | Port Input Sample Timing                             | 194 |

| Figure 31. | GPIO Port Output Timing                              | 195 |

| Figure 32. | On-Chip Debugger Timing                              | 196 |

| Figure 33  | Flash Current Diagram                                | 197 |

| Table 89.  | VBO Trim Definition                           | 132 |

|------------|-----------------------------------------------|-----|

| Table 90.  | Trim Option Bits at 0006H (TCLKFLT)           | 132 |

| Table 91.  | ClkFlt Delay Control Definition               | 133 |

| Table 92.  | Write Status Byte                             | 135 |

| Table 93.  | Read Status Byte                              | 136 |

| Table 94.  | NVDS Read Time                                | 137 |

| Table 95.  | OCD Baud-Rate Limits                          | 142 |

| Table 96.  | On-Chip Debugger Command Summary              | 144 |

| Table 97.  | OCD Control Register (OCDCTL)                 | 149 |

| Table 98.  | OCD Status Register (OCDSTAT)                 | 150 |

| Table 99.  | Oscillator Configuration and Selection        | 152 |

| Table 100. | Oscillator Control Register (OSCCTL)          | 154 |

| Table 101. | Recommended Crystal Oscillator Specifications | 158 |

| Table 102. | Assembly Language Syntax Example 1            | 163 |

| Table 103. | Assembly Language Syntax Example 2            | 164 |

| Table 104. | Notational Shorthand                          | 164 |

| Table 105. | Additional Symbols                            | 165 |

| Table 106. | Arithmetic Instructions                       | 166 |

| Table 107. | Bit Manipulation Instructions                 | 167 |

| Table 108. | Block Transfer Instructions                   | 167 |

| Table 109. | CPU Control Instructions                      | 168 |

| Table 110. | Load Instructions                             | 168 |

| Table 111. | Logical Instructions                          | 169 |

| Table 112. | Program Control Instructions                  | 169 |

| Table 113. | Rotate and Shift Instructions                 | 170 |

| Table 114. | eZ8 CPU Instruction Summary                   | 171 |

| Table 115. | Op Code Map Abbreviations                     | 181 |

| Table 116. | Absolute Maximum Ratings                      | 184 |

| Table 117. | DC Characteristics                            | 185 |

| Table 118. | AC Characteristics                            | 188 |

# Z8 Encore!® F083A Series Product Specification

xvii

| TD 11 110  | ADGD A DECEMBER (ADGD T)                 | 210 |

|------------|------------------------------------------|-----|

|            | ADC Data Low Bits Register (ADCD_L)      |     |

|            | ADC Sample Settling Time (ADCSST)        |     |

|            | ADC Sample Time (ADCST)                  |     |

| Table 152. | ADC Clock Prescale Register (ADCCP)      | 211 |

| Table 153. | Power Control Register 0 (PWRCTL0)       | 212 |

| Table 154. | LED Drive Enable (LEDEN)                 | 212 |

| Table 155. | LED Drive Level High Register (LEDLVLH)  | 213 |

| Table 156. | LED Drive Level Low Register (LEDLVLL)   | 213 |

| Table 157. | Oscillator Control Register (OSCCTL)     | 213 |

| Table 158. | Comparator Control Register (CMP0)       | 214 |

| Table 159. | Interrupt Request 0 Register (IRQ0)      | 214 |

| Table 160. | IRQ0 Enable High Bit Register (IRQ0ENH)  | 215 |

| Table 161. | IRQ0 Enable Low Bit Register (IRQ0ENL)   | 215 |

| Table 162. | Interrupt Request 1 Register (IRQ1)      | 215 |

| Table 163. | IRQ1 Enable High Bit Register (IRQ1ENH)  | 215 |

| Table 164. | IRQ1 Enable Low Bit Register (IRQ1ENL)   | 216 |

| Table 165. | Interrupt Request 2 Register (IRQ2)      | 216 |

| Table 166. | IRQ2 Enable High Bit Register (IRQ2ENH)  | 216 |

| Table 167. | IRQ2 Enable Low Bit Register (IRQ2ENL)   | 216 |

| Table 168. | Interrupt Edge Select Register (IRQES)   | 217 |

| Table 169. | Shared Interrupt Select Register (IRQSS) | 217 |

| Table 170. | Interrupt Control Register (IRQCTL)      | 217 |

| Table 171. | Port A GPIO Address Register (PAADDR)    | 218 |

| Table 172. | Port A Control Registers (PACTL)         | 218 |

| Table 173. | Port A Input Data Registers (PAIN)       | 218 |

| Table 174. | Port A Output Data Register (PAOUT)      | 219 |

| Table 175. | Port B GPIO Address Register (PBADDR)    | 219 |

|            | Port B Control Registers (PBCTL)         |     |

|            | Port B Input Data Registers (PBIN)       |     |

|            | Port B Output Data Register (PBOUT)      |     |

# Address Space

The eZ8 CPU accesses three distinct address spaces as follows:

- The Register File addresses access for the general purpose registers and the eZ8 CPU, peripheral and GPIO port control registers

- Program Memory addresses access for all of the memory locations having executable code and/or data

- The Data Memory addresses access for all of the memory locations containing only the data

The following sections describe these three address spaces. For more detailed information about the eZ8 CPU and its address space, refer to the eZ8 CPU Core User Manual (UM0128), available for download on www.zilog.com.

# **Register File**

The Register File address space in the Z8 Encore! MCU is 4KB (4096 bytes). The Register File consists of two sections: control registers and general purpose registers. When instructions are executed, registers defined as source are read and registers defined as destinations are written. The architecture of the eZ8 CPU allows all general purpose registers to function as accumulators, address pointers, index registers, stack areas or scratch pad memory.

The upper 256 bytes of the 4KB Register File address space are reserved for control of the eZ8 CPU, on-chip peripherals and the I/O ports. These registers are located at addresses from F00H to FFFH. Some of the addresses within the 256 B Control Register section are reserved (unavailable). Reading from a reserved Register File address returns an undefined value. Writing to reserved Register File addresses is not recommended and produces unpredictable results.

The on-chip RAM always begins at address 000H in the Register File address space. The Z8 Encore! F083A Series devices contain up to 256 B of on-chip RAM. Reading from Register File addresses outside the available RAM addresses (and not within the Control Register address space), returns an undefined value. Writing to these Register File addresses has no effect.

Table 9. Reset and Stop Mode Recovery Characteristics and Latency

|                                                    | Reset Characteristics and Latency                      |            |                                                  |  |  |  |  |

|----------------------------------------------------|--------------------------------------------------------|------------|--------------------------------------------------|--|--|--|--|

| Reset Type                                         | Control Registers                                      | eZ8<br>CPU | Reset Latency (Delay)                            |  |  |  |  |

| System Reset                                       | Reset (as applicable)                                  | Reset      | About 66 internal precision oscillator cycles.   |  |  |  |  |

| System Reset with<br>Crystal Oscillator<br>Enabled | Reset (as applicable)                                  | Reset      | About 5000 internal precision oscillator cycles. |  |  |  |  |

| Stop Mode Recovery                                 | Unaffected, except<br>WDT_CTL and<br>OSC_CTL registers | Reset      | About 66 internal precision oscillator cycles.   |  |  |  |  |

| Stop Mode Recovery with crystal oscillator enabled | Unaffected, except<br>WDT_CTL and<br>OSC_CTL registers | Reset      | About 5000 internal precision oscillator cycles. |  |  |  |  |

During a system Reset or Stop Mode Recovery, the Z8 Encore! F083A Series device is held in reset for about 66 cycles of the internal precision oscillator. If the crystal oscillator is enabled in the Flash option bits, the reset period is increased to about 5000 IPO cycles. When a reset occurs because of a low voltage condition or POR, the reset delay is measured from the time the supply voltage first exceeds the POR level (discussed later in this chapter). If the external pin reset remains asserted at the end of the reset period, the device remains in reset until the pin is deasserted.

At the beginning of reset, all GPIO pins are configured as inputs with pull-up resistor disabled, except PD0 which is shared with the reset pin. On Reset, the Port D0 pin is configured as a bidirectional open-drain reset. This pin is internally driven low during port reset, after which the user code reconfigures this pin as a general purpose output.

During reset, the eZ8 CPU and on-chip peripherals are idle; however, the on-chip crystal oscillator and Watchdog Timer Oscillator continues to run.

On reset, control registers within the Register File that have a defined reset value are loaded with their reset values. Other control registers (including the Stack Pointer, Register Pointer and Flags) and general purpose RAM are undefined following the reset. The eZ8 CPU fetches the reset vector at program memory addresses 0002H and 0003H and loads that value into the program counter. Program execution begins at the reset vector address.

Because the control registers are reinitialized by a system reset, the system clock after reset is always the IPO. User software must reconfigure the oscillator control block, to enable and select the correct system clock source.

#### **HALT Mode**

Executing the eZ8 CPU HALT instruction places the device into HALT Mode. In HALT Mode, the operating characteristics are:

- Primary oscillator is enabled and continues to operate

- System clock is enabled and continues to operate

- eZ8 CPU is stopped

- Program counter (PC) stops incrementing

- WDT's internal RC oscillator continues to operate

- If enabled, the WDT continues to operate

- All other on-chip peripherals continue to operate

The eZ8 CPU is brought out of HALT Mode by any one of the following operations:

- Interrupt

- WDT time-out (interrupt or reset)

- POR

- VBO reset

- External RESET pin assertion

To minimize current in HALT Mode, all GPIO pins that are configured as digital inputs must be driven to  $V_{DD}$  when pull-up register bit is enabled or to one of power rail ( $V_{DD}$  or GND) when pull-up register bit is disabled.

#### **Peripheral Level Power Control**

In addition to the STOP and HALT modes, it is possible to disable each peripheral on each of the Z8 Encore! F083A Series devices. Disabling a given peripheral minimizes its power consumption.

# **Power Control Register Definitions**

The following sections describe the power control registers.

**Table 16. Port Alternate Function Mapping**

| Port   | Pin | Mnemonic   | Alternate Function Description          | Alternate<br>Function Set<br>Register AFS1 |

|--------|-----|------------|-----------------------------------------|--------------------------------------------|

| Port A | PA0 | T0IN/T0OUT | Timer 0 input/Timer 0 output complement | N/A                                        |

|        |     | Reserved   |                                         | _                                          |

|        | PA1 | T0OUT      | Timer 0 output                          | _                                          |

|        |     | Reserved   |                                         | _                                          |

|        | PA2 | Reserved   | Reserved                                | _                                          |

|        |     | Reserved   |                                         | _                                          |

|        | PA3 | Reserved   | Reserved                                | _                                          |

|        |     | Reserved   |                                         | _                                          |

|        | PA4 | Reserved   | Reserved                                | _                                          |

|        |     | Reserved   |                                         | _                                          |

|        | PA5 | Reserved   | Reserved                                | _                                          |

|        |     | Reserved   |                                         | _                                          |

|        | PA6 | T1IN/T1OUT | Timer 1 input/Timer 1 output complement | _                                          |

|        |     | Reserved   |                                         | =                                          |

|        | PA7 | T1OUT      | Timer 1 output                          | _                                          |

|        |     | Reserved   |                                         | =                                          |

Note: Because there is only a single alternate function for each Port A and Port D (PD0) pin, the Alternate Function Set registers are not implemented for Port A and Port D (PD0). Enabling alternate function selections (as described in the <a href="Port A-D Alternate Function Subregisters">Port A and Port D (PD0)</a>. Enabling alternate function selections (as described in the <a href="Port A-D Alternate Function Subregisters">Port A and Port D (PD0)</a>. Enabling alternate function selections (as described in the <a href="Port A-D Alternate Function Subregisters">Port A and Port D (PD0)</a>. Enabling alternate function selections (as described in the <a href="Port A-D Alternate Function Subregisters">Port A and Port D (PD0)</a>. Enabling alternate function selections (as described in the <a href="Port A-D Alternate Function Subregisters">Port A and Port D (PD0)</a>. Enabling alternate function selections (as described in the <a href="Port A-D Alternate Function Subregisters">Port A and Port D (PD0)</a>. Enabling alternate function selections (as described in the <a href="Port A-D Alternate Function Subregisters">Port A and Port D (PD0)</a>. Enabling alternate function selections (as described in the <a href="Port A-D Alternate Function Subregisters">Port A and Port D (PD0)</a>. Enabling alternate function selections (as described in the <a href="Port A-D Alternate Function Subregisters">Port A and Port D (PD0)</a>. Enabling alternate function selections (as described in the <a href="Port A-D Alternate Function Subregisters">Port A and Port D (PD0)</a>. Enabling alternate function selections (as described in the <a href="Port A-D Alternate Function Subregisters">Port A and Port D (PD0)</a>. Enabling alternate function selections (as described in the <a href="Port A-D Alternate Function Subregisters">Port A and Port D (PD0)</a>. Enabling alternate function selections (as described in the <a href="Port A-D Alternate Function Subregisters">Port A and Port D (PD0)</a>. Enabling alternate function selections (as des

#### Port A-D Stop Mode Recovery Source Enable Subregisters

The Port A–D Stop Mode Recovery Source Enable Subregister, shown in Table 25, is accessed through the Port A–D Control Register by writing 05H to the Port A–D Address Register. Setting the bits in the Port A–D Stop Mode Recovery Source Enable subregisters to 1, configures the specified port pins as a Stop Mode Recovery source. During STOP Mode, any logic transition on a port pin enabled as a Stop Mode Recovery source initiates Stop Mode Recovery.

Table 25. Port A-D Stop Mode Recovery Source Enable Subregisters (PxSMRE)

| Bit     | 7         | 6                                                                                     | 5      | 4      | 3      | 2      | 1      | 0      |

|---------|-----------|---------------------------------------------------------------------------------------|--------|--------|--------|--------|--------|--------|

| Field   | PSMRE7    | PSMRE6                                                                                | PSMRE5 | PSMRE4 | PSMRE3 | PSMRE2 | PSMRE1 | PSMRE0 |

| RESET   | 0         | 0                                                                                     | 0      | 0      | 0      | 0      | 0      | 0      |

| R/W     | R/W       | R/W                                                                                   | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |

| Address | If 05H ir | If 05H in Port A–D Address Register, accessible through the Port A–D Control Register |        |        |        |        |        |        |

#### Bit Description

#### [7:0] Port Stop Mode Recovery Source Enable

PSMREx 0 = The port pin is not configured as a Stop Mode Recovery source. Transitions on this pin during STOP Mode do not initiate Stop Mode Recovery.

1 = The port pin is configured as a Stop Mode Recovery source. Any logic transition on this pin during STOP Mode initiates Stop Mode Recovery.

Note: x indicates the specific GPIO port pin number (7–0).

#### **Interrupt Request 0 Register**

The Interrupt Request 0 (IRQ0) Register, shown in Table 35, stores the interrupt requests for both vectored and polled interrupts. When a request is sent to the Interrupt Controller, the corresponding bit in the IRQ0 Register becomes 1. If interrupts are globally enabled (vectored interrupts), the Interrupt Controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU reads the Interrupt Request 0 Register to determine if any interrupt requests are pending.

Table 35. Interrupt Request 0 Register (IRQ0)

| Bit     | 7        | 6   | 5   | 4    | 3    | 2     | 1   | 0    |

|---------|----------|-----|-----|------|------|-------|-----|------|

| Field   | Reserved | T1I | TOI |      | Rese | erved |     | ADCI |

| RESET   | 0        | 0   | 0   | 0    | 0    | 0     | 0   | 0    |

| R/W     | R/W      | R/W | R/W | R/W  | R/W  | R/W   | R/W | R/W  |

| Address |          |     |     | FC0H |      |       |     |      |

| Bit         | Description                                                                                                                             |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| [7]         | Reserved This bit is reserved and must be programmed to 0.                                                                              |

| [6]<br>T1I  | Timer 1 Interrupt Request  0 = No interrupt request is pending for Timer 1.  1 = An interrupt request from timer 1 is awaiting service. |

| [5]<br>T0I  | Timer 0 Interrupt Request 0 = No interrupt request is pending for Timer 0. 1 = An interrupt request from timer 0 is awaiting service.   |

| [4:1]       | Reserved These bits are reserved and must be programmed to 0000.                                                                        |

| [0]<br>ADCI | ADC Interrupt Request 0 = No interrupt request is pending for the ADC. 1 = An interrupt request from the ADC is awaiting service.       |

### **Interrupt Edge Select Register**

The Interrupt Edge Select (IRQES) Register, shown in Table 47, determines whether an interrupt is generated for the rising edge or falling edge on the selected GPIO Port A or Port D input pin.

Table 47. Interrupt Edge Select Register (IRQES)

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|------|

| Field   | IES7 | IES6 | IES5 | IES4 | IES3 | IES2 | IES1 | IES0 |

| RESET   | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| R/W     | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |

| Address |      |      |      | FC   | DH   |      |      |      |

| Bit          | Description                                                                            |

|--------------|----------------------------------------------------------------------------------------|

| [7:0]        | Interrupt Edge Select                                                                  |

| <b>IES</b> x | 0 = An interrupt request is generated on the falling edge of the PAx input or PDx.     |

|              | 1 = An interrupt request is generated on the rising edge of the $PAx$ input or $PDx$ . |

| Note:        | x indicates register bits 7–0.                                                         |

Upon reaching the reload value stored in the Timer Reload High and Low Byte registers, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. Additionally, if the timer output alternate function is enabled, the timer output pin changes state (from Low to High or from High to Low) at timer reload.

Observe the following steps to configure a timer for COUNTER Mode and to initiate the count.

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for COUNTER Mode

- Select either the rising edge or falling edge of the timer input signal for the count.

This selection also sets the initial logic level (High or Low) for the timer output alternate function. However, the timer output function is not required to be enabled

- 2. Write to the Timer High and Low Byte registers to set the starting count value. This only affects the first pass in COUNTER Mode. After the first timer reload in COUNTER Mode, counting always begins at the reset value 0001H. In COUNTER Mode, the Timer High and Low Byte registers must be written with the value 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. Configure the associated GPIO port pin for the timer input alternate function.

- 6. If using the timer output function, configure the associated GPIO port pin for the timer output alternate function.

- 7. Write to the Timer Control Register to enable the timer.

In COUNTER Mode, the number of timer input transitions is given by the following equation:

Counter Mode Timer Input Transitions = Current Count Value – Start Value

#### **COMPARATOR COUNTER Mode**

In COMPARATOR COUNTER Mode, the timer counts the input transitions from the analog comparator output. The TPOL bit in the Timer Control Register determines whether the count occurs on the rising edge or the falling edge of the comparator output signal. In COMPARATOR COUNTER Mode, the prescaler is disabled.

| Bit          | Description (Continued)                                                                   |

|--------------|-------------------------------------------------------------------------------------------|

| [2:0]        | TIMER Mode                                                                                |

| <b>TMODE</b> | This field along with the TMODEHI bit in TxCTL0 register determines the operating mode of |

|              | the timer. TMODEHI is the most significant bit of the timer mode selection value.         |

|              | 0000 = ONE-SHOT Mode.                                                                     |

|              | 0001 = CONTINUOUS Mode.                                                                   |

|              | 0010 = COUNTER Mode.                                                                      |

|              | 0011 = PWM SINGLE OUTPUT Mode.                                                            |

|              | 0100 = CAPTURE Mode.                                                                      |

|              | 0101 = COMPARE Mode.                                                                      |

|              | 0110 = GATED Mode.                                                                        |

|              | 0111 = CAPTURE/COMPARE Mode.                                                              |

|              | 1000 = PWM DUAL OUTPUT Mode.                                                              |

|              | 1001 = CAPTURE RESTART Mode.                                                              |

|              | 1010 = COMPARATOR COUNTER Mode.                                                           |

Table 71 describes the Flash information area. This 128-byte information area is accessed by setting the bit 7 of the Flash Page Select Register to 1. When access is enabled, the Flash information area is mapped into program memory and overlays the 128-bytes at the addresses FE00H to FE7FH. When the information area access is enabled, all reads from these program memory addresses return the information area data rather than the program memory data. Access to the Flash information area is read-only.

The trim bits are handled differently than the other Zilog Flash option bits. The trim bits are the hybrid of the user option bits and the standard Zilog option bits. These trim bits must be user accessible for reading at all times using external registers, regardless of the state of bit 7 in the Flash Page Select Register. Writes to the trim space change the value of the option bit holding register, but does not affect the Flash bits, which remain as read-only.

Program Memory

Address (Hex)

Function

FE00–FE3F

Zilog option bits

FE40–FE53

Part number

20-character ASCII alphanumeric code

Left-justified and filled with FH

FE54–FE5F

Reserved

FE60–FE7F

Zilog calibration data

Table 71. Z8F083 Flash Memory Area Map

# **Operation**

The Flash Controller programs and erases Flash memory, and provides the proper Flash controls and timing for the byte programming, page erase and mass erase operations performed in Flash memory.

The Flash Controller contains several protection mechanisms to prevent accidental programming or erasure. These mechanism operate on the page, sector and full-memory levels.

The flow chart in Figure 16 displays basic Flash Controller operation. The subsections that follow provide details about the various operations (Lock, Unlock, Byte Programming, Page Protect, Page Unprotect, Page Select Page Erase and Mass Erase) shown in Figure 16.

# Flash Option Bits

Programmable Flash option bits allow users to configure certain aspects of Z8 Encore! F083A Series operation. The configuration data is stored in Flash program memory and read during reset. These Flash option bits control the following functions:

- Watchdog Timer time-out response selection at interrupt or system reset

- Watchdog Timer enable at reset

- The ability to prevent unwanted read access to user code in program memory

- The ability to prevent accidental programming and erasure of all or a portion of the user code in program memory

- VBO configuration, which is always enabled or disabled during STOP Mode to reduce STOP Mode power consumption

- OSCILLATOR mode selection for high, medium and low power crystal oscillators or external RC oscillator

- Factory trimming information for the internal precision oscillator and VBO voltage

# **Operation**

This section describes the type and configuration of the programmable Flash option bits.

# **Option Bit Configuration by Reset**

Each time the Flash option bits are programmed or erased, the device must be reset for the change to be effective. During any Reset operation (system reset or Stop Mode Recovery), the Flash option bits are automatically read from the Flash program memory and written to option configuration registers. The option configuration registers, control the operation of the devices within the Z8 Encore! F083A Series. Option bit control is established before the device exits reset and the eZ8 CPU begins code execution. The option configuration registers are not part of the Register File and are not accessible for read or write access.

#### **Option Bit Types**

This section describes the two types of Flash option bits offered in the F083A Series.

#### **User Option Bits**

The user option bits are contained in the first two bytes of program memory. User access to these bits is provided because these locations contain application-specific device con-

Table 114. eZ8 CPU Instruction Summary (Continued)

| Assembly      |                                             |      | ress<br>ode | Op<br>Code(s) |   |   | Fla | ags |   |   | _ Fetch | Instr. |

|---------------|---------------------------------------------|------|-------------|---------------|---|---|-----|-----|---|---|---------|--------|

| Mnemonic      | Symbolic Operation                          | dst  | src         | (Hex)         | С | Z | S   | ٧   | D | Н | Cycles  |        |

| JR dst        | PC ← PC + X                                 | DA   |             | 8B            | _ | - | _   | -   | - | _ | 2       | 2      |

| JR cc, dst    | if cc is true $PC \leftarrow PC + X$        | DA   |             | 0B-FB         | - | - | -   | -   | - | - | 2       | 2      |

| LD dst, rc    | dst ← src                                   | r    | IM          | 0C-FC         | _ | - | _   | -   | - | _ | 2       | 2      |

|               |                                             | r    | X(r)        | C7            |   |   |     |     |   |   | 3       | 3      |

|               |                                             | X(r) | r           | D7            |   |   |     |     |   |   | 3       | 4      |

|               |                                             | r    | Ir          | E3            |   |   |     |     |   |   | 2       | 3      |

|               |                                             | R    | R           | E4            |   |   |     |     |   |   | 3       | 2      |

|               |                                             | R    | IR          | E5            |   |   |     |     |   |   | 3       | 4      |

|               |                                             | R    | IM          | E6            |   |   |     |     |   |   | 3       | 2      |

|               |                                             | IR   | IM          | E7            | _ |   |     |     |   |   | 3       | 3      |

|               |                                             | lr   | r           | F3            |   |   |     |     |   |   | 2       | 3      |

|               |                                             | IR   | R           | F5            |   |   |     |     |   |   | 3       | 3      |

| LDC dst, src  | dst ← src                                   | r    | Irr         | C2            | _ | _ | _   | _   | _ | _ | 2       | 5      |

|               |                                             | lr   | Irr         | C5            |   |   |     |     |   |   | 2       | 9      |

|               |                                             | Irr  | r           | D2            |   |   |     |     |   |   | 2       | 5      |

| LDCI dst, src | dst ← src                                   | lr   | Irr         | C3            | _ | _ | _   | _   | _ | _ | 2       | 9      |

|               | $r \leftarrow r + 1$ $rr \leftarrow rr + 1$ | Irr  | Ir          | D3            | _ |   |     |     |   |   | 2       | 9      |

| LDE dst, src  | dst ← src                                   | r    | Irr         | 82            | _ | - | -   | -   | - | - | 2       | 5      |

|               |                                             | Irr  | r           | 92            | _ |   |     |     |   |   | 2       | 5      |

| LDEI dst, src | dst ← src                                   | lr   | Irr         | 83            | - | - | _   | -   | - | _ | 2       | 9      |

|               | $r \leftarrow r + 1$ $rr \leftarrow rr + 1$ | Irr  | lr          | 93            | _ |   |     |     |   |   | 2       | 9      |

| LDWX dst, src | dst ← src                                   | ER   | ER          | 1FE8          | - | - | _   | -   | - | _ | 5       | 4      |

Note: Flags Notation:

<sup>\* =</sup> Value is a function of the result of the operation.

<sup>-</sup> = Unaffected.

X = Undefined.

<sup>0 =</sup> Reset to 0.

<sup>1 =</sup> Set to 1.

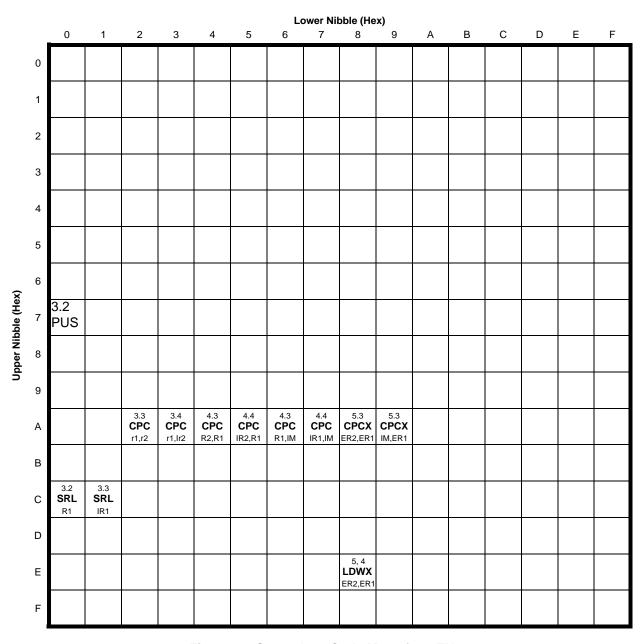

Figures 26 and 27 provide operation code mapping information about each of the eZ8 CPU instructions.

|                    |          |                   |                   |                   |                   |                   |                   | Lo                | ower Nil          | ble (He           | x)                 |                    |            |             |                  |           |                    |

|--------------------|----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--------------------|--------------------|------------|-------------|------------------|-----------|--------------------|

|                    |          | 0                 | 1                 | 2                 | 3                 | 4                 | 5                 | 6                 | 7                 | 8                 | 9                  | Α                  | В          | С           | D                | Е         | F                  |

|                    | _        | 1.1<br>DDV        | 2.2               | 2.3               | 2.4               | 3.3<br>ADD        | 3.4<br>ADD        | 3.3<br>ADD        | 3.4               | 4.3               | 4.3                | 2.3<br><b>DJNZ</b> | 2.2        | 2.2         | 3.2<br><b>JP</b> | 1.2       | 1.2                |

|                    | 0        | BRK               | SRP<br>IM         | ADD<br>r1,r2      | ADD<br>r1,lr2     | ADD<br>R2,R1      | ADD<br>IR2,R1     | ADD<br>R1,IM      | ADD<br>IR1,IM     | ADDX<br>ER2,ER1   | ADDX<br>IM,ER1     | r1,X               | JR<br>cc,X | LD<br>r1,IM | cc,DA            | INC<br>r1 | NOP                |

|                    |          | 2.2               | 2.3               | 2.3               | 2.4               | 3.3               | 3.4               | 3.3               | 3.4               | 4.3               | 4.3                | i                  | ĺ          | Ī           | li               | Ī         | See 2nd            |

|                    | 1        | RLC               | RLC               | ADC               | ADC               | ADC               | ADC               | ADC               | ADC               | ADCX              | ADCX               |                    |            |             |                  |           | Op Code            |

|                    |          | R1<br>2.2         | IR1<br>2.3        | r1,r2<br>2.3      | r1,lr2<br>2.4     | R2,R1<br>3.3      | IR2,R1<br>3.4     | R1,IM<br>3.3      | IR1,IM<br>3.4     | ER2,ER1<br>4.3    | IM,ER1<br>4.3      |                    |            |             |                  |           | Мар                |

|                    | 2        | INC               | INC               | SUB               | SUB               | SUB               | SUB               | SUB               | SUB               | SUBX              | SUBX               |                    |            |             |                  |           |                    |

|                    |          | R1                | IR1               | r1,r2             | r1,lr2            | R2,R1             | IR2,R1            | R1,IM             | IR1,IM            | ER2,ER1           | IM,ER1             |                    |            |             |                  |           |                    |

|                    | 3        | 2.2<br><b>DEC</b> | 2.3<br><b>DEC</b> | 2.3<br><b>SBC</b> | 2.4<br><b>SBC</b> | 3.3<br><b>SBC</b> | 3.4<br><b>SBC</b> | 3.3<br><b>SBC</b> | 3.4<br><b>SBC</b> | 4.3<br>SBCX       | 4.3<br>SBCX        |                    |            |             |                  |           |                    |

|                    | Ĭ        | R1                | IR1               | r1,r2             | r1,lr2            | R2,R1             | IR2,R1            | R1,IM             | IR1,IM            | ER2,ER1           | IM,ER1             |                    |            |             |                  |           |                    |

|                    |          | 2.2               | 2.3               | 2.3               | 2.4               | 3.3               | 3.4               | 3.3               | 3.4               | 4.3               | 4.3                |                    |            |             |                  |           |                    |

|                    | 4        | <b>DA</b><br>R1   | DA<br>IR1         | <b>OR</b> r1,r2   | OR<br>r1,lr2      | OR<br>R2,R1       | OR<br>IR2,R1      | OR<br>R1,IM       | OR<br>IR1,IM      | ORX<br>ER2,ER1    | ORX<br>IM,ER1      |                    |            |             |                  |           |                    |

|                    |          | 2.2               | 2.3               | 2.3               | 2.4               | 3.3               | 3.4               | 3.3               | 3.4               | 4.3               | 4.3                |                    |            |             |                  |           | 1.2                |

|                    | 5        | POP               | POP               | AND               | AND               | AND               | AND               | AND               | AND               | ANDX              | ANDX               |                    |            |             |                  |           | WDT                |

|                    |          | R1<br>2.2         | IR1<br>2.3        | r1,r2<br>2.3      | r1,lr2<br>2.4     | R2,R1<br>3.3      | IR2,R1<br>3.4     | R1,IM<br>3.3      | IR1,IM<br>3.4     | 4.3               | IM,ER1<br>4.3      |                    |            |             |                  |           | 1.2                |

|                    | 6        | COM               | COM               | TCM               | TCM               | TCM               | TCM               | TCM               | TCM               | TCMX              | TCMX               |                    |            |             |                  |           | STOP               |

| ×                  |          | R1                | IR1               | r1,r2             | r1,lr2            | R2,R1             | IR2,R1            | R1,IM             | IR1,IM            | ER2,ER1           | IM,ER1             |                    |            |             |                  |           |                    |

| Ĕ                  | 7        | 2.2<br>PUSH       | 2.3<br>PUSH       | 2.3<br><b>TM</b>  | 2.4<br><b>TM</b>  | 3.3<br><b>TM</b>  | 3.4<br><b>TM</b>  | 3.3<br><b>TM</b>  | 3.4<br><b>TM</b>  | 4.3<br><b>TMX</b> | 4.3<br><b>TMX</b>  |                    |            |             |                  |           | 1.2<br><b>HALT</b> |

| ple                | <b>'</b> | R2                | IR2               | r1,r2             | r1,lr2            | R2,R1             | IR2,R1            | R1,IM             | IR1,IM            | ER2,ER1           | IM,ER1             |                    |            |             |                  |           | IIALI              |

| Upper Nibble (Hex) |          | 2.5               | 2.6               | 2.5               | 2.9               | 3.2               | 3.3               | 3.4               | 3.5               | 3.4               | 3.4                |                    |            |             |                  |           | 1.2                |

| per                | 8        | DECW<br>RR1       | DECW<br>IRR1      | LDE<br>r1,lrr2    | LDEI<br>lr1,lrr2  | LDX<br>r1,ER2     | LDX<br>Ir1,ER2    | LDX<br>IRR2,R1    | LDX<br>IRR2,IR1   | LDX<br>r1,rr2,X   | LDX<br>rr1,r2,X    |                    |            |             |                  |           | DI                 |

| ੂ                  |          | 2.2               | 2.3               | 2.5               | 2.9               | 3.2               | 3.3               | 3.4               | 3.5               | 3.3               | 3.5                |                    |            |             |                  |           | 1.2                |

|                    | 9        | RL                | RL                | LDE               | LDEI              | LDX               | LDX               | LDX               | LDX               | LEA               | LEA                |                    |            |             |                  |           | EI                 |

|                    |          | R1                | IR1               | r2,Irr1           | lr2,lrr1          | r2,ER1            | Ir2,ER1           | R2,IRR1           |                   | r1,r2,X           | rr1,rr2,X          |                    |            |             |                  |           |                    |

|                    | Α        | 2.5<br>INCW       | 2.6<br>INCW       | 2.3<br><b>CP</b>  | 2.4<br><b>CP</b>  | 3.3<br><b>CP</b>  | 3.4<br><b>CP</b>  | 3.3<br><b>CP</b>  | 3.4<br><b>CP</b>  | 4.3<br><b>CPX</b> | 4.3<br><b>CPX</b>  |                    |            |             |                  |           | 1.4<br>RET         |

|                    |          | RR1               | IRR1              | r1,r2             | r1,lr2            | R2,R1             | IR2,R1            | R1,IM             | IR1,IM            | ER2,ER1           | IM,ER1             |                    |            |             |                  |           |                    |

|                    | _        | 2.2               | 2.3               | 2.3               | 2.4               | 3.3               | 3.4               | 3.3               | 3.4               | 4.3               | 4.3<br><b>YORY</b> |                    |            |             |                  |           | 1.5                |

|                    | В        | CLR<br>R1         | CLR<br>IR1        | XOR<br>r1,r2      | XOR<br>r1,lr2     | XOR<br>R2,R1      | XOR<br>IR2,R1     | XOR<br>R1,IM      | XOR<br>IR1,IM     | XORX<br>ER2,ER1   | XORX<br>IM,ER1     |                    |            |             |                  |           | IRET               |

|                    |          | 2.2               | 2.3               | 2.5               | 2.9               | 2.3               | 2.9               |                   | 3.4               | 3.2               |                    |                    |            |             |                  |           | 1.2                |

|                    | С        | RRC               | RRC               | LDC               | LDCI              | JP                | LDC               |                   | LD                | PUSHX             |                    |                    |            |             |                  |           | RCF                |

|                    |          | R1<br>2.2         | IR1<br>2.3        | r1,lrr2<br>2.5    | lr1,lrr2<br>2.9   | IRR1<br>2.6       | lr1,lrr2<br>2.2   | 3.3               | r1,r2,X<br>3.4    | ER2<br>3.2        |                    |                    |            |             |                  |           | 1.2                |

|                    | D        | SRA               | SRA               | LDC               | LDCI              | CALL              | BSWAP             | CALL              | LD                | POPX              |                    |                    |            |             |                  |           | SCF                |

|                    |          | R1                | IR1               | r2,Irr1           | lr2,lrr1          | IRR1              | R1                | DA                | r2,r1,X           | ER1               |                    |                    |            |             |                  |           |                    |

|                    | Е        | 2.2<br><b>RR</b>  | 2.3<br><b>RR</b>  | 2.2<br><b>BIT</b> | 2.3<br><b>LD</b>  | 3.2<br><b>LD</b>  | 3.3<br><b>LD</b>  | 3.2<br><b>LD</b>  | 3.3<br><b>LD</b>  | 4.2<br><b>LDX</b> | 4.2<br><b>LDX</b>  |                    |            |             |                  |           | 1.2<br><b>CCF</b>  |

|                    | -        | R1                | IR1               | p,b,r1            | r1,lr2            | R2,R1             | IR2,R1            | R1,IM             | IR1,IM            | ER2,ER1           | IM,ER1             |                    |            |             |                  |           | 00.                |

|                    | _        | 2.2               | 2.3               | 2.6               | 2.3               | 2.8               | 3.3               | 3.3               | 3.4               |                   | -                  | <u> </u>           | Ţ          | ⊥           | <u> </u>         | T         |                    |

|                    | F        | SWAP<br>R1        | SWAP<br>IR1       | TRAP<br>Vector    | LD<br>lr1,r2      | MULT<br>RR1       | LD<br>R2,IR1      | BTJ<br>p,b,r1,X   | BTJ               |                   |                    | ▼                  | <b>V</b>   | ▮           | ▼                | ▮         |                    |

|                    |          | IVI               | IIXI              | VECTOI            | 111,12            | IVIXI             | 114,111           | א,וו,ט,ק          | א,ו וו,ט,אן       |                   |                    | •                  |            | <u>'</u>    |                  |           |                    |

Figure 26. First Op Code Map

Figure 27. Second Op Code Map after 1FH

In Table 130, a "√" mark indicates F083A Series package availability by pin count.

Table 130. Package and Pin Count Description

|         | Pin Count |           |  |  |  |  |

|---------|-----------|-----------|--|--|--|--|

| Package | 20        | 28        |  |  |  |  |

| PDIP    | V         |           |  |  |  |  |

| QFN     | $\sqrt{}$ | $\sqrt{}$ |  |  |  |  |

| SOIC    | $\sqrt{}$ | $\sqrt{}$ |  |  |  |  |

| SSOP    | √         | √         |  |  |  |  |

**Hex Address: FC5**

Table 164. IRQ1 Enable Low Bit Register (IRQ1ENL)

| Bit     | 7      | 6       | 5      | 4      | 3      | 2      | 1      | 0      |  |  |

|---------|--------|---------|--------|--------|--------|--------|--------|--------|--|--|

| Field   | PA7ENL | PA6CENL | PA5ENL | PA4ENL | PA3ENL | PA2ENL | PA1ENL | PA0ENL |  |  |

| RESET   | 0      | 0       | 0      | 0      | 0      | 0      | 0      | 0      |  |  |

| R/W     | R/W    | R/W     | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |  |  |

| Address | FC5H   |         |        |        |        |        |        |        |  |  |

**Hex Address: FC6**

Table 165. Interrupt Request 2 Register (IRQ2)

| Bit     | 7   | 6    | 5     | 4   | 3    | 2    | 1    | 0    |  |  |  |

|---------|-----|------|-------|-----|------|------|------|------|--|--|--|

| Field   |     | Rese | erved |     | PC3I | PC2I | PC1I | PC0I |  |  |  |

| RESET   | 0   | 0    | 0     | 0   | 0    | 0    | 0    | 0    |  |  |  |

| R/W     | R/W | R/W  | R/W   | R/W | R/W  | R/W  | R/W  | R/W  |  |  |  |

| Address |     | FC6H |       |     |      |      |      |      |  |  |  |

**Hex Address: FC7**

Table 166. IRQ2 Enable High Bit Register (IRQ2ENH)

| Bit     | 7   | 6    | 5     | 4   | 3     | 2     | 1     | 0     |  |  |  |  |

|---------|-----|------|-------|-----|-------|-------|-------|-------|--|--|--|--|

| Field   |     | Rese | erved |     | C3ENH | C2ENH | C1ENH | C0ENH |  |  |  |  |

| RESET   | 0   | 0    | 0     | 0   | 0     | 0     | 0     | 0     |  |  |  |  |

| R/W     | R/W | R/W  | R/W   | R/W | R/W   | R/W   | R/W   | R/W   |  |  |  |  |

| Address |     | FC7H |       |     |       |       |       |       |  |  |  |  |

**Hex Address: FC8**

Table 167. IRQ2 Enable Low Bit Register (IRQ2ENL)

| Bit     | 7   | 6    | 5     | 4   | 3     | 2     | 1     | 0     |  |  |  |

|---------|-----|------|-------|-----|-------|-------|-------|-------|--|--|--|

| Field   |     | Rese | erved |     | C3ENL | C2ENL | C1ENL | C0ENL |  |  |  |

| RESET   | 0   | 0    | 0     | 0   | 0     | 0     | 0     | 0     |  |  |  |

| R/W     | R/W | R/W  | R/W   | R/W | R/W   | R/W   | R/W   | R/W   |  |  |  |

| Address |     | FC8H |       |     |       |       |       |       |  |  |  |

**Hex Address: FD3**

**Table 174. Port A Output Data Register (PAOUT)**

| Bit     | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |  |  |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|--|--|

| Field   | POUT7 | POUT6 | POUT5 | POUT4 | POUT3 | POUT2 | POUT1 | POUT0 |  |  |

| RESET   | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |  |  |

| R/W     | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |  |  |

| Address | FD3H  |       |       |       |       |       |       |       |  |  |

**Hex Address: FD4**

Table 175. Port B GPIO Address Register (PBADDR)

| Bit     | 7   | 6                           | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |  |

|---------|-----|-----------------------------|---|---|---|---|---|---|--|--|--|--|

| Field   |     | PADDR[7:0]                  |   |   |   |   |   |   |  |  |  |  |

| RESET   |     | 00H                         |   |   |   |   |   |   |  |  |  |  |

| R/W     | R/W | R/W R/W R/W R/W R/W R/W R/W |   |   |   |   |   |   |  |  |  |  |

| Address |     | FD4H                        |   |   |   |   |   |   |  |  |  |  |

**Hex Address: FD5**

**Table 176. Port B Control Registers (PBCTL)**

| Bit     | 7   | 6                           | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |  |

|---------|-----|-----------------------------|---|---|---|---|---|---|--|--|--|--|

| Field   |     | PCTL                        |   |   |   |   |   |   |  |  |  |  |

| RESET   |     | 00H                         |   |   |   |   |   |   |  |  |  |  |

| R/W     | R/W | R/W R/W R/W R/W R/W R/W R/W |   |   |   |   |   |   |  |  |  |  |

| Address |     | FD5H                        |   |   |   |   |   |   |  |  |  |  |

**Hex Address: FD6**

Table 177. Port B Input Data Registers (PBIN)

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |  |  |  |

|---------|------|------|------|------|------|------|------|------|--|--|--|

| Field   | PIN7 | PIN6 | PIN5 | PIN4 | PIN3 | PIN2 | PIN1 | PIN0 |  |  |  |

| RESET   | Х    | Х    | Х    | Х    | Х    | Х    | Х    | Х    |  |  |  |

| R/W     | R    | R    | R    | R    | R    | R    | R    | R    |  |  |  |

| Address |      | FD6H |      |      |      |      |      |      |  |  |  |