Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | -                                                         |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 17                                                        |

| Program Memory Size        | 8KB (8K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 7x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                   |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f083aph020sg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# List of Tables

| Table 1.  | Z8 Encore! F083A Series Family Part Selection Guide 2              |

|-----------|--------------------------------------------------------------------|

| Table 2.  | Acronyms and Expansions                                            |

| Table 3.  | Z8 Encore! F083A Series Package Options                            |

| Table 4.  | Signal Descriptions                                                |

| Table 5.  | Pin Characteristics (20- and 28-pin Devices) 13                    |

| Table 6.  | Z8 Encore! F083A Series Program Memory Maps 15                     |

| Table 7.  | Z8 Encore! F083A Series Flash Memory Information Area Map 16       |

| Table 8.  | Register File Address Map 17                                       |

| Table 9.  | Reset and Stop Mode Recovery Characteristics and Latency 22        |

| Table 10. | Reset Sources and Resulting Reset Type                             |

| Table 11. | Stop Mode Recovery Sources and Resulting Action 27                 |

| Table 12. | POR Indicator Values                                               |

| Table 13. | Reset Status Register (RSTSTAT)                                    |

| Table 14. | Power Control Register 0 (PWRCTL0)                                 |

| Table 15. | Port Availability by Device and Package Type                       |

| Table 16. | Port Alternate Function Mapping                                    |

| Table 17. | GPIO Port Registers and Subregisters                               |

| Table 18. | Port A–D GPIO Address Registers (PxADDR)                           |

| Table 19. | Port Control Subregister Access                                    |

| Table 20. | Port A–D Control Registers (PxCTL)                                 |

| Table 21. | Port A–D Data Direction Subregisters (PxDD) 41                     |

| Table 22. | Port A–D Alternate Function Subregisters (PxAF)                    |

| Table 23. | Port A–D Output Control Subregisters (PxOC)                        |

| Table 24. | Port A–D High Drive Enable Subregisters (PxHDE)                    |

| Table 25. | Port A–D Stop Mode Recovery Source Enable Subregisters (PxSMRE) 45 |

| Table 26. | Port A–D Pull-Up Enable Subregisters (PxPUE)                       |

| Table 27. | Port A–D Alternate Function Set 1 Subregisters (PxAFS1) 47         |

| Table 28. | Port A–D Alternate Function Set 2 Subregisters (PxAFS2) 48         |

# **Pin Description**

The Z8 Encore! F083A Series products are available in variety of package styles and pin configurations. This chapter describes the signals and the pin configurations for each of the package styles. For information about the physical package specifications, see the <u>Packaging</u> chapter on page 198.

## **Available Packages**

Table 3 lists the package styles that are available for each device in the Z8 Encore! F083A Series product line.

| Part Number | ADC | 20-pin<br>QFN | 20-pin<br>SOIC | 20-pin<br>SSOP | 20-pin<br>PDIP | 28-pin<br>QFN | 28-pin<br>SOIC | 28-pin<br>SSOP |

|-------------|-----|---------------|----------------|----------------|----------------|---------------|----------------|----------------|

| Z8F083A     | Yes | Х             | Х              | Х              | Х              | Х             | Х              | Х              |

| Z8F043A     | Yes | Х             | Х              | Х              | Х              | Х             | Х              | Х              |

Table 3. Z8 Encore! F083A Series Package Options

## **Pin Configurations**

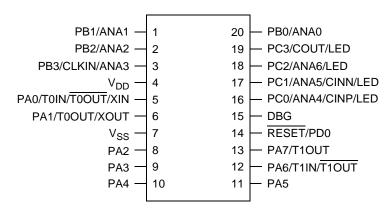

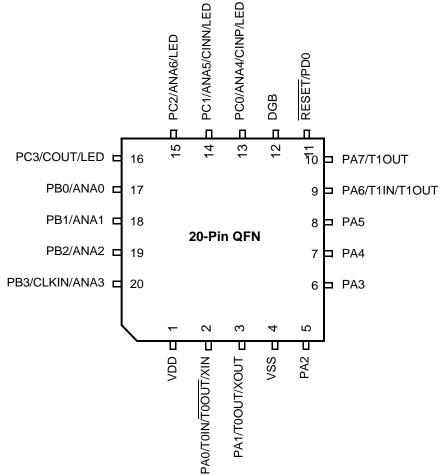

Figures 2 through 5 display the pin configurations of all of the packages available in the Z8 Encore! F083A Series. For the description of the signals, see <u>Table 4</u> on page 11.

The pin configurations listed are preliminary and subject to change based on manufacturing limitations.

Figure 2. Z8F083A Series in 20-Pin SOIC, SSOP, PDIP Package

#### Z8 Encore!<sup>®</sup> F083A Series Product Specification

Figure 4. Z8F083A Series in 20-Pin QFN Package

9

## **Signal Descriptions**

Table 4 describes the Z8 Encore! F083A Series signals. To determine the signals available for a specific package style, see the <u>Pin Configurations</u> section on page 7.

| Signal Mnemonic    | I/O     | Description                                                                                                                                                                                                                                                               |

|--------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General-Purpose In | nput/Ou | tput Ports A–D                                                                                                                                                                                                                                                            |

| PA[7:0]            | I/O     | Port A. These pins are used for GPIO.                                                                                                                                                                                                                                     |

| PB[5:0]            | I/O     | Port B. These pins are used for GPIO.                                                                                                                                                                                                                                     |

| PC[7:0]            | I/O     | Port C. These pins are used for GPIO.                                                                                                                                                                                                                                     |

| PD[0]              | I/O     | Port D. This pin is used for general purpose output only.                                                                                                                                                                                                                 |

| Timers             |         |                                                                                                                                                                                                                                                                           |

| T0OUT/T1OUT        | 0       | Timer output 0–1. These signals are the output from the timers.                                                                                                                                                                                                           |

| T0OUT/T1OUT        | 0       | Timer complement output 0–1. These signals are output from the timers in PWM DUAL OUTPUT mode.                                                                                                                                                                            |

| T0IN/T1IN          | I       | Timer Input 0–1. These signals are used as the capture, gating and counter inputs. The T0IN signal is multiplexed T0OUT signals.                                                                                                                                          |

| Comparator         |         |                                                                                                                                                                                                                                                                           |

| CINP/CINN          | Ι       | Comparator inputs. These signals are the positive and negative inputs to the comparator.                                                                                                                                                                                  |

| COUT               | 0       | Comparator output. This is the output of the comparator.                                                                                                                                                                                                                  |

| Analog             |         |                                                                                                                                                                                                                                                                           |

| ANA[7:0]           | Ι       | Analog port. These signals are used as inputs to the Analog-to-Digital Con verter (ADC).                                                                                                                                                                                  |

| VREF               | I/O     | ADC reference voltage input.<br>Note: When configuring ADC using external Vref, PB5 is used as VREF in 28-pin package.                                                                                                                                                    |

| Oscillators        |         |                                                                                                                                                                                                                                                                           |

| XIN                | Ι       | External crystal input. This is the input pin to the crystal oscillator. A crystal is connected between it and the <b>XOUT</b> pin to form the oscillator. In addition, this pin is used with external RC networks or external clock drivers to provide the system clock. |

| XOUT               | 0       | External crystal output. This pin is the output of the crystal oscillator. A crystal is connected between it and the <b>XIN</b> pin to form the oscillator.                                                                                                               |

| Clock Input        |         |                                                                                                                                                                                                                                                                           |

| CLKIN              | I       | Clock input signal. This pin can be used to input a TTL-level signal to be used as the system clock.                                                                                                                                                                      |

|                                                          | Reset Characteristics and Latency                      |            |                                                  |  |  |  |  |

|----------------------------------------------------------|--------------------------------------------------------|------------|--------------------------------------------------|--|--|--|--|

| Reset Type                                               | Control Registers                                      | eZ8<br>CPU | Reset Latency (Delay)                            |  |  |  |  |

| System Reset                                             | Reset (as applicable)                                  | Reset      | About 66 internal precision oscillator cycles.   |  |  |  |  |

| System Reset with<br>Crystal Oscillator<br>Enabled       | Reset (as applicable)                                  | Reset      | About 5000 internal precision oscillator cycles. |  |  |  |  |

| Stop Mode Recovery                                       | Unaffected, except<br>WDT_CTL and<br>OSC_CTL registers | Reset      | About 66 internal precision oscillator cycles.   |  |  |  |  |

| Stop Mode Recovery<br>with crystal oscillator<br>enabled | Unaffected, except<br>WDT_CTL and<br>OSC_CTL registers | Reset      | About 5000 internal precision oscillator cycles. |  |  |  |  |

#### Table 9. Reset and Stop Mode Recovery Characteristics and Latency

During a system Reset or Stop Mode Recovery, the Z8 Encore! F083A Series device is held in reset for about 66 cycles of the internal precision oscillator. If the crystal oscillator is enabled in the Flash option bits, the reset period is increased to about 5000 IPO cycles. When a reset occurs because of a low voltage condition or POR, the reset delay is measured from the time the supply voltage first exceeds the POR level (discussed later in this chapter). If the external pin reset remains asserted at the end of the reset period, the device remains in reset until the pin is deasserted.

At the beginning of reset, all GPIO pins are configured as inputs with pull-up resistor disabled, except PDO which is shared with the reset pin. On Reset, the Port DO pin is configured as a bidirectional open-drain reset. This pin is internally driven low during port reset, after which the user code reconfigures this pin as a general purpose output.

During reset, the eZ8 CPU and on-chip peripherals are idle; however, the on-chip crystal oscillator and Watchdog Timer Oscillator continues to run.

On reset, control registers within the Register File that have a defined reset value are loaded with their reset values. Other control registers (including the Stack Pointer, Register Pointer and Flags) and general purpose RAM are undefined following the reset. The eZ8 CPU fetches the reset vector at program memory addresses 0002H and 0003H and loads that value into the program counter. Program execution begins at the reset vector address.

Because the control registers are reinitialized by a system reset, the system clock after reset is always the IPO. User software must reconfigure the oscillator control block, to enable and select the correct system clock source.

#### Port A–D High Drive Enable Subregisters

The Port A–D High Drive Enable Subregister, shown in Table 24, is accessed through the Port A–D Control Register by writing 04H to the Port A–D Address Register. Setting the bits in the Port A–D High Drive Enable subregisters to 1 configures the specified port pins for high-output current drive operation. The Port A–D High Drive Enable Subregister affects the pins directly and, as a result, alternate functions are also affected.

#### Table 24. Port A–D High Drive Enable Subregisters (PxHDE)

| Bit     | 7         | 6                                                                                     | 5     | 4     | 3     | 2     | 1     | 0     |  |

|---------|-----------|---------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|--|

| Field   | PHDE7     | PHDE6                                                                                 | PHDE5 | PHDE4 | PHDE3 | PHDE2 | PHDE1 | PHDE0 |  |

| RESET   | 0         | 0                                                                                     | 0     | 0     | 0     | 0     | 0     | 0     |  |

| R/W     | R/W       | R/W                                                                                   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |  |

| Address | If 04H ir | If 04H in Port A–D Address Register, accessible through the Port A–D Control Register |       |       |       |       |       |       |  |

#### Bit Description

[7:0] Port High Drive Enable

PHDEx 0 = The port pin is configured for standard output current drive.

1 = The port pin is configured for high output current drive.

Note: x indicates the specific GPIO port pin number (7–0).

#### 45

#### Port A–D Stop Mode Recovery Source Enable Subregisters

The Port A–D Stop Mode Recovery Source Enable Subregister, shown in Table 25, is accessed through the Port A–D Control Register by writing 05H to the Port A–D Address Register. Setting the bits in the Port A–D Stop Mode Recovery Source Enable subregisters to1, configures the specified port pins as a Stop Mode Recovery source. During STOP Mode, any logic transition on a port pin enabled as a Stop Mode Recovery source initiates Stop Mode Recovery.

#### Table 25. Port A–D Stop Mode Recovery Source Enable Subregisters (PxSMRE)

| Bit     | 7         | 6                           | 5           | 4             | 3            | 2            | 1            | 0        |  |  |  |

|---------|-----------|-----------------------------|-------------|---------------|--------------|--------------|--------------|----------|--|--|--|

| Field   | PSMRE7    | PSMRE6                      | PSMRE5      | PSMRE4        | PSMRE3       | PSMRE2       | PSMRE1       | PSMRE0   |  |  |  |

| RESET   | 0         | 0                           | 0           | 0             | 0            | 0            | 0            | 0        |  |  |  |

| R/W     | R/W       | R/W R/W R/W R/W R/W R/W R/W |             |               |              |              |              |          |  |  |  |

| Address | If 05H ir | n Port A–D A                | Address Reg | jister, acces | sible throug | h the Port A | –D Control F | Register |  |  |  |

#### Bit Description

#### [7:0] **Port Stop Mode Recovery Source Enable**

PSMREx 0 = The port pin is not configured as a Stop Mode Recovery source. Transitions on this pin during STOP Mode do not initiate Stop Mode Recovery.

1 = The port pin is configured as a Stop Mode Recovery source. Any logic transition on this pin during STOP Mode initiates Stop Mode Recovery.

Note: x indicates the specific GPIO port pin number (7-0).

#### Z8 Encore!<sup>®</sup> F083A Series Product Specification

## Architecture

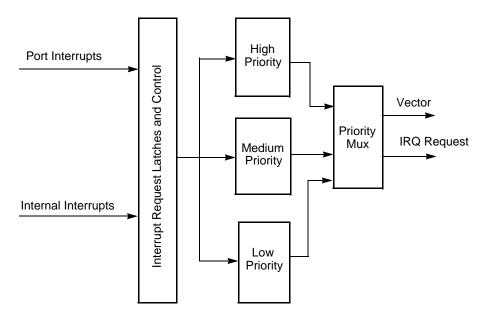

Figure 9 displays the Interrupt Controller block diagram.

Figure 9. Interrupt Controller Block Diagram

## Operation

This section describes the operational aspects of the following functions.

Master Interrupt Enable: see page 56

Interrupt Vectors and Priority: see page 57

Interrupt Assertion: see page 57

Software Interrupt Assertion: see page 58

## **Master Interrupt Enable**

The master interrupt enable bit (IRQE) in the Interrupt Control Register globally enables and disables the interrupts.

Interrupts are globally enabled by any of the following actions:

- Execution of an enable interrupt (EI) instruction

- Execution of an return from interrupt (IRET) instruction

## **Interrupt Request 0 Register**

The Interrupt Request 0 (IRQ0) Register, shown in Table 35, stores the interrupt requests for both vectored and polled interrupts. When a request is sent to the Interrupt Controller, the corresponding bit in the IRQ0 Register becomes 1. If interrupts are globally enabled (vectored interrupts), the Interrupt Controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU reads the Interrupt Request 0 Register to determine if any interrupt requests are pending.

| Bit         | 7                                                                                                                                                  | 6                                                                                                                                                  | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|--|--|--|

| Field       | Reserved T1I T0I Reserved ADCI                                                                                                                     |                                                                                                                                                    |     |     |     |     |     |     |  |  |  |

| RESET       | 0                                                                                                                                                  | 0                                                                                                                                                  | 0   | 0   | 0   | 0   | 0   | 0   |  |  |  |

| R/W         | R/W                                                                                                                                                | R/W                                                                                                                                                | R/W | R/W | R/W | R/W | R/W | R/W |  |  |  |

| Address     |                                                                                                                                                    | FC0H                                                                                                                                               |     |     |     |     |     |     |  |  |  |

| Bit         | Description                                                                                                                                        |                                                                                                                                                    |     |     |     |     |     |     |  |  |  |

| [7]         | Reserved<br>This bit is reserved and must be programmed to 0.                                                                                      |                                                                                                                                                    |     |     |     |     |     |     |  |  |  |

| [6]<br>T1I  | <b>Timer 1 Interrupt Request</b><br>0 = No interrupt request is pending for Timer 1.<br>1 = An interrupt request from timer 1 is awaiting service. |                                                                                                                                                    |     |     |     |     |     |     |  |  |  |

| [5]<br>TOI  | 0 = No inter                                                                                                                                       | <b>Timer 0 Interrupt Request</b><br>0 = No interrupt request is pending for Timer 0.<br>1 = An interrupt request from timer 0 is awaiting service. |     |     |     |     |     |     |  |  |  |

| [4:1]       | <b>Reserved</b><br>These bits are reserved and must be programmed to 0000.                                                                         |                                                                                                                                                    |     |     |     |     |     |     |  |  |  |

| [0]<br>ADCI | ADC Interr<br>0 = No inter<br>1 = An inter                                                                                                         | rupt reques                                                                                                                                        |     |     |     |     |     |     |  |  |  |

#### Table 35. Interrupt Request 0 Register (IRQ0)

## Interrupt Edge Select Register

The Interrupt Edge Select (IRQES) Register, shown in Table 47, determines whether an interrupt is generated for the rising edge or falling edge on the selected GPIO Port A or Port D input pin.

| Field         IES7         IES6         IES5         IES4         IES3         IES2         IES1         IES0           RESET         0         0         0         0         0         0         0         0         0           R/W                                                                                                                                                          | Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|------|------|------|------|------|------|------|--|--|

| R/W         R/W <th>Field</th> <th>IES7</th> <th>IES6</th> <th>IES5</th> <th>IES4</th> <th>IES3</th> <th>IES2</th> <th>IES1</th> <th>IES0</th> | Field   | IES7 | IES6 | IES5 | IES4 | IES3 | IES2 | IES1 | IES0 |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | RESET   | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |  |  |

| Address FCDH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | R/W     | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Address |      | FCDH |      |      |      |      |      |      |  |  |

#### Table 47. Interrupt Edge Select Register (IRQES)

## Bit Description

| [7:0] | Interrupt Edge Select                                                              |   |

|-------|------------------------------------------------------------------------------------|---|

| IESx  | 0 = An interrupt request is generated on the falling edge of the PAx input or PDx. |   |

|       | 1 = An interrupt request is generated on the rising edge of the PAx input or PDx.  |   |

| NI (  |                                                                                    | - |

Note: x indicates register bits 7–0.

- 4. Enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. If using the timer output function, configure the associated GPIO port pin for the timer output alternate function.

- 6. Write to the Timer Control Register to enable the timer and initiate counting.

In COMPARE Mode, the system clock always provides the timer input. The compare time is calculated by the following equation:

Compare Mode Time (s) =  $\frac{(Compare Value - Start Value) \times Prescale}{System Clock Frequency (Hz)}$

#### **GATED Mode**

In GATED Mode, the timer counts only when the timer input signal is in its active state (asserted), as determined by the TPOL bit in the Timer Control Register. When the timer input signal is asserted, counting begins. A timer interrupt is generated when the timer input signal is deasserted or a timer reload occurs. To determine whether the timer input signal deassertion generated the interrupt, read the associated GPIO input value and compare to the value stored in the TPOL bit.

The timer counts up to the 16-bit reload value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. Upon reaching the reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes (assuming the timer input signal remains asserted). Additionally, if the timer output alternate function is enabled, the timer output pin changes state (from Low to High or from High to Low) at timer reset.

Observe the following steps to configure a timer for GATED Mode and to initiate the count.

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for GATED Mode

- Set the prescale value

- 2. Write to the Timer High and Low Byte registers to set the starting count value. Writing these registers only affects the first pass in GATED Mode. After the first timer reset in GATED Mode, counting always begins at the reset value of 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. Enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers. By default, the timer interrupt is generated for both input deasser-

tion and reload events. Therefore, configure the timer interrupt to be generated only at the input deassertion event or the reload event by setting TICONFIG bit of the TxCTL1 Register.

- 5. Configure the associated GPIO port pin for the timer input alternate function.

- 6. Write to the Timer Control Register to enable the timer.

- 7. Assert the timer input signal to initiate the counting.

#### CAPTURE/COMPARE Mode

In CAPTURE/COMPARE Mode, the timer begins counting on the first external timer input transition. The acceptable transition (rising edge or falling edge) is set by the TPOL bit in the Timer Control Register. The timer input is the system clock.

Every subsequent acceptable transition (after the first) of the timer input signal, captures the current count value. The capture value is written to the timer PWM High and Low Byte registers. When a capture event occurs, an interrupt is generated, the count value in the Timer High and Low Byte registers is reset to 0001H and the counting resumes. The INPCAP bit in the TxCTL1 Register is set to indicate that the timer interrupt is caused by an input capture event.

If no capture event occurs, the timer counts up to the 16-bit compare value stored in the Timer Reload High and Low Byte registers. Upon reaching the compare value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in the TxCTL1 Register is cleared to indicate that the timer interrupt is not caused by an input capture event.

Observe the following steps to configure a timer for CAPTURE/COMPARE Mode and to initiate the count.

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for CAPTURE/COMPARE Mode

- Set the prescale value

- Set the capture edge (rising or falling) for the timer input

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

- 3. Write to the Timer Reload High and Low Byte registers to set the compare value.

- 4. Enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.By default, the timer interrupt is generated for both input capture and reload events. The user must configure the timer interrupt to be generated only at the input capture event or the reload event by setting TICONFIG bit of the TxCTL1 Register.

#### 96

### Watchdog Timer Reload Upper, High and Low Byte Registers

The Watchdog Timer Reload Upper, High and Low Byte (WDTU, WDTH, WDTL) registers, shown in Tables 60 through 62, form the 24-bit reload value{WDTU[7:0], WDTH[7:0], WDTL[7:0]} that is loaded into the Watchdog Timer when a WDT instruction is executed. Writing to these registers sets the appropriate reload value; reading from these registers returns the current Watchdog Timer count value.

**Caution:** The 24-bit WDT reload value must not be set to a value less than 000004H.

| Bit        | 7                                                                                                   | 6    | 5    | 4    | 3    | 2    | 1    | 0    |  |  |

|------------|-----------------------------------------------------------------------------------------------------|------|------|------|------|------|------|------|--|--|

| Field      | WDTU                                                                                                |      |      |      |      |      |      |      |  |  |

| RESET      | 0 0 0 0 0 0 0                                                                                       |      |      |      |      |      |      |      |  |  |

| R/W        | R/W*                                                                                                | R/W* | R/W* | R/W* | R/W* | R/W* | R/W* | R/W* |  |  |

| Address    | FF1H                                                                                                |      |      |      |      |      |      |      |  |  |

| Note: *R/W | Note: *R/W = A read returns the current WDT count value; a write sets the appropriate reload value. |      |      |      |      |      |      |      |  |  |

#### Table 60. Watchdog Timer Reload Upper Byte Register (WDTU)

# Bit Description [7:0] WDT Reload Upper Byte WDTH NSR\_Bite[22:46] of the 24 bit WDT relead uplue

WDTU MSB, Bits[23:16], of the 24-bit WDT reload value.

| Bit        | 7                                                                                                   | 6    | 5    | 4    | 3    | 2    | 1    | 0    |  |  |

|------------|-----------------------------------------------------------------------------------------------------|------|------|------|------|------|------|------|--|--|

| Field      | WDTH                                                                                                |      |      |      |      |      |      |      |  |  |

| RESET      | 0                                                                                                   | 0    | 0    | 0    | 0    | 1    | 0    | 0    |  |  |

| R/W        | R/W*                                                                                                | R/W* | R/W* | R/W* | R/W* | R/W* | R/W* | R/W* |  |  |

| Address    | FF2H                                                                                                |      |      |      |      |      |      |      |  |  |

| Note: *R/V | Note: *R/W = A read returns the current WDT count value; a write sets the appropriate reload value. |      |      |      |      |      |      |      |  |  |

#### Table 61. Watchdog Timer Reload High Byte Register (WDTH)

| Bit   | Description                                             |

|-------|---------------------------------------------------------|

| [7:0] | WDT Reload High Byte                                    |

| WDTH  | Middle byte, bits[15:8] of the 24-bit WDT reload value. |

| Bit           | Description (Continued)                                                                                                                  |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------|

| [1]<br>IGADDR | <b>Illegal Address</b><br>When NVDS byte reads from invalid addresses occur (those exceeding the NVDS array size), this bit is set to 1. |

| [0]           | <b>Reserved</b><br>This bit is reserved and must be programmed to 0.                                                                     |

## **Power Failure Protection**

The NVDS routines employ error-checking mechanisms to ensure that any power failure will only endanger the most recently written byte. Bytes previously written to the array are not perturbed. For this protection to function, the VBO must be enabled (See *the* Low-Power Modes chapter on page 30) and configured for a threshold voltage of 2.4V or greater (See *the* Trim Bit Address Space section on page 129).

A system reset (such as a pin reset or Watchdog Timer reset) that occurs during a write operation also perturbs the byte currently being written. All other bytes in the array are unperturbed.

## **Optimizing NVDS Memory Usage for Execution Speed**

As Table 94 shows, NVDS read times vary drastically, this discrepancy being a trade-off for minimizing the frequency of writes that require post-write page erases. The NVDS read time of address N is a function of the number of writes to addresses other than N since the most recent write to address N, as well as the number of writes since the most recent page erase. Neglecting effects caused by page erases and results caused by the initial condition in which the NVDS is blank, a rule of thumb is that every write since the most recent page erase causes read times of unwritten addresses to increase by  $0.8\mu$ s, up to a maximum of  $258\mu$ s.

| Operation     | Minimum<br>Latency (µs) | Maximum<br>Latency (µs) |

|---------------|-------------------------|-------------------------|

| Read          | 71                      | 258                     |

| Write         | 126                     | 136                     |

| Illegal Read  | 6                       | 6                       |

| Illegal Write | 7                       | 7                       |

| Table | 94.   | NVDS | Read  | Time |

|-------|-------|------|-------|------|

| and   | • • • |      | 11044 |      |

```

DBG \leftarrow Size[15:8]

DBG \leftarrow Size[7:0]

DBG \leftarrow 1-65536 data bytes

```

**Read Program Memory (0BH).** The read program memory command, reads data from program memory. This command is equivalent to the LDC and LDCI instructions. Data is read 1–65536 bytes at a time (65536 bytes are read by setting size to 0). If the device is not in DEBUG Mode or if the Flash read protect option bit is enabled, this command returns FFH for the data.

```

DBG \leftarrow 0BH

DBG \leftarrow Program Memory Address[15:8]

DBG \leftarrow Program Memory Address[7:0]

DBG \leftarrow Size[15:8]

DBG \leftarrow Size[7:0]

DBG \rightarrow 1-65536 data bytes

```

Write Data Memory (0CH). The write data memory command, writes data to data memory. This command is equivalent to the LDE and LDEI instructions. Data is written 1–65536 bytes at a time (65536 bytes are written by setting size to 0). If the device is not in DEBUG Mode or if the Flash read protect option bit is enabled, the data is discarded.

```

DBG \leftarrow 0CH

DBG \leftarrow Data Memory Address[15:8]

DBG \leftarrow Data Memory Address[7:0]

DBG \leftarrow Size[15:8]

DBG \leftarrow Size[7:0]

DBG \leftarrow 1-65536 data bytes

```

• **Read Data Memory (0DH)**—The read data memory command, reads from data memory. This command is equivalent to the LDE and LDEI instructions. Data is read from 1 to 65536 bytes at a time (65536 bytes are read by setting size to 0). If the device is not in DEBUG Mode, this command returns FFH for the data.

```

DBG \leftarrow 0DH

DBG \leftarrow Data Memory Address[15:8]

DBG \leftarrow Data Memory Address[7:0]

DBG \leftarrow Size[15:8]

DBG \leftarrow Size[7:0]

DBG \rightarrow 1-65536 data bytes

```

**Read Program Memory CRC (0EH).** The read program memory CRC command, computes and returns the cyclic redundancy check (CRC) of program memory using the 16-bit CRC-CCITT polynomial. If the device is not in DEBUG Mode, this command returns FFFFH for the CRC value. Unlike the other OCD read commands, there is a delay from issuing of the command until the OCD returns the data. The OCD reads program memory, calculates the CRC value and returns the result. The delay is a function of program memory size and is approximately equal to the system clock period multiplied by the number of bytes in program memory.

#### Assembly Language Source Program Example

| JP START      | ; Everything after the semicolon is a comment.                                                                                                                                                                                                                                      |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| START:        | A label called "START". The first instruction (JP START) in this ; example causes program execution to jump to the point within the ; program where the START label occurs.                                                                                                         |

| LD R4, R7     | ; A Load (LD) instruction with two operands. The first operand,<br>; Working register R4, is the destination. The second operand,<br>; Working register R7, is the source. The contents of R7 is<br>; written into R4.                                                              |

| LD 234H, #%01 | ; Another Load (LD) instruction with two operands.<br>; The first operand, extended mode register Address 234H,<br>; identifies the destination. The second operand, immediate data<br>; value 01H, is the source. The 01H value is written into the<br>; register at address 234H. |

## **Assembly Language Syntax**

For proper instruction execution, eZ8 CPU assembly language syntax requires that the operands be written as 'destination, source'. After assembly, the object code usually has the operands in the order 'source, destination', but ordering is op code-dependent. The following instruction examples display the format of some basic assembly instructions and the resulting object code produced by the assembler. This binary format must be followed by users that prefer manual program coding or intend to implement their own assembler.

#### **Example 1**

If the contents of registers 43H and 08H are added and the result is stored in 43H, the assembly syntax and resulting object code is:

| Table 102. | Assembly | Language | Syntax | Example 1 |

|------------|----------|----------|--------|-----------|

|------------|----------|----------|--------|-----------|

| Assembly Language Code | ADD | 43H, | 08H | (ADD dst, | src) |

|------------------------|-----|------|-----|-----------|------|

| Object Code            | 04  | 08   | 43  | (OPC src, | dst) |

#### Example 2

In general, when an instruction format requires an 8-bit register address, the address specify any register location in the range 0–255 or, using escaped mode addressing, a working register R0–R15. If the contents of register 43H and working register R8 are added and the result is stored in 43H, the assembly syntax and resulting object code is:

|   |                         |                          |                              |                                |                             |                              | Lo                           |                               | ble (He                       | x)                             |                            |                          |                           |                           |                         |                           |

|---|-------------------------|--------------------------|------------------------------|--------------------------------|-----------------------------|------------------------------|------------------------------|-------------------------------|-------------------------------|--------------------------------|----------------------------|--------------------------|---------------------------|---------------------------|-------------------------|---------------------------|

|   | 0                       | 1                        | 2                            | 3                              | 4                           | 5                            | 6                            | 7                             | 8                             | 9                              | A                          | В                        | С                         | D                         | E                       | F                         |

| 0 | 1.1<br>BRK              | 2.2<br>SRP<br>IM         | 2.3<br><b>ADD</b><br>r1,r2   | 2.4<br><b>ADD</b><br>r1,lr2    | 3.3<br><b>ADD</b><br>R2,R1  | 3.4<br>ADD<br>IR2,R1         | 3.3<br><b>ADD</b><br>R1,IM   | 3.4<br>ADD<br>IR1,IM          | 4.3<br>ADDX<br>ER2,ER1        | 4.3<br>ADDX<br>IM,ER1          | 2.3<br><b>DJNZ</b><br>r1,X | 2.2<br><b>JR</b><br>cc,X | 2.2<br><b>LD</b><br>r1,IM | 3.2<br><b>JP</b><br>cc,DA | 1.2<br><b>INC</b><br>r1 | 1.2<br>NOP                |

| 1 | 2.2<br><b>RLC</b><br>R1 | 2.3<br><b>RLC</b><br>IR1 | 2.3<br><b>ADC</b><br>r1,r2   | 2.4<br>ADC<br>r1,lr2           | 3.3<br><b>ADC</b><br>R2,R1  | 3.4<br>ADC<br>IR2,R1         | 3.3<br>ADC<br>R1,IM          | 3.4<br>ADC<br>IR1,IM          | 4.3<br>ADCX<br>ER2,ER1        | 4.3<br>ADCX<br>IM,ER1          |                            |                          |                           |                           |                         | See 2nd<br>Op Code<br>Map |

| 2 | 2.2<br>INC              | 2.3<br>INC               | 2.3<br>SUB                   | 2.4<br>SUB                     | 3.3<br>SUB                  | 3.4<br>SUB                   | 3.3<br>SUB                   | 3.4<br>SUB                    | 4.3<br>SUBX                   | 4.3<br>SUBX                    |                            |                          |                           |                           |                         | map                       |

| 3 | R1<br>2.2<br>DEC        | IR1<br>2.3<br>DEC        | r1,r2<br>2.3<br><b>SBC</b>   | r1,Ir2<br>2.4<br><b>SBC</b>    | 82,R1<br>3.3<br><b>SBC</b>  | 3.4<br><b>SBC</b>            | R1,IM<br>3.3<br><b>SBC</b>   | 3.4<br><b>SBC</b>             | 4.3<br><b>SBCX</b>            | 4.3<br><b>SBCX</b>             |                            |                          |                           |                           |                         |                           |

| 4 | R1<br>2.2<br><b>DA</b>  | IR1<br>2.3<br><b>DA</b>  | r1,r2<br>2.3<br><b>OR</b>    | r1,Ir2<br>2.4<br><b>OR</b>     | R2,R1<br>3.3<br><b>OR</b>   | IR2,R1<br>3.4<br><b>OR</b>   | R1,IM<br>3.3<br><b>OR</b>    | IR1,IM<br>3.4<br><b>OR</b>    | 4.3<br><b>ORX</b>             | 4.3<br><b>ORX</b>              |                            |                          |                           |                           |                         |                           |

| 5 | R1<br>2.2<br><b>POP</b> | IR1<br>2.3<br><b>POP</b> | r1,r2<br>2.3<br><b>AND</b>   | r1,Ir2<br>2.4<br><b>AND</b>    | R2,R1<br>3.3<br><b>AND</b>  | IR2,R1<br>3.4<br><b>AND</b>  | R1,IM<br>3.3<br><b>AND</b>   | IR1,IM<br>3.4<br><b>AND</b>   | ER2,ER1<br>4.3<br><b>ANDX</b> | IM,ER1<br>4.3<br><b>ANDX</b>   |                            |                          |                           |                           |                         | 1.2<br>WDT                |

| - | R1<br>2.2               | IR1<br>2.3               | r1,r2<br>2.3                 | r1,lr2<br>2.4                  | R2,R1<br>3.3                | IR2,R1<br>3.4                | R1,IM<br>3.3                 | IR1,IM<br>3.4                 | ER2,ER1<br>4.3                | IM,ER1<br>4.3                  |                            |                          |                           |                           |                         | 1.2                       |

| 6 | <b>COM</b><br>R1<br>2.2 | COM<br>IR1<br>2.3        | TCM<br>r1,r2<br>2.3          | TCM<br>r1,lr2<br>2.4           | TCM<br>R2,R1<br>3.3         | TCM<br>IR2,R1<br>3.4         | TCM<br>R1,IM<br>3.3          | <b>TCM</b><br>IR1,IM<br>3.4   | <b>TCMX</b><br>ER2,ER1<br>4.3 | TCMX<br>IM,ER1<br>4.3          |                            |                          |                           |                           |                         | <b>STOP</b>               |

| 7 | PUSH<br>R2              | PUSH<br>IR2              | <b>TM</b><br>r1,r2           | <b>TM</b><br>r1,lr2            | <b>TM</b><br>R2,R1          | <b>TM</b><br>IR2,R1          | TM<br>R1,IM                  | TM<br>IR1,IM                  | TMX<br>ER2,ER1                | TMX<br>IM,ER1                  |                            |                          |                           |                           |                         | HALT                      |

| 8 | 2.5<br>DECW<br>RR1      | 2.6<br>DECW<br>IRR1      | 2.5<br><b>LDE</b><br>r1,Irr2 | 2.9<br>LDEI<br>Ir1,Irr2        | 3.2<br><b>LDX</b><br>r1,ER2 | 3.3<br><b>LDX</b><br>Ir1,ER2 | 3.4<br><b>LDX</b><br>IRR2,R1 | 3.5<br><b>LDX</b><br>IRR2,IR1 | 3.4<br><b>LDX</b><br>r1,rr2,X | 3.4<br><b>LDX</b><br>rr1,r2,X  |                            |                          |                           |                           |                         | 1.2<br>DI                 |

| 9 | 2.2<br><b>RL</b><br>R1  | 2.3<br><b>RL</b><br>IR1  | 2.5<br><b>LDE</b><br>r2,Irr1 | 2.9<br><b>LDEI</b><br>lr2,lrr1 | 3.2<br><b>LDX</b><br>r2,ER1 | 3.3<br><b>LDX</b><br>Ir2,ER1 | 3.4<br><b>LDX</b><br>R2,IRR1 | 3.5<br><b>LDX</b><br>IR2,IRR1 | 3.3<br><b>LEA</b><br>r1,r2,X  | 3.5<br><b>LEA</b><br>rr1,rr2,X |                            |                          |                           |                           |                         | 1.2<br>EI                 |

| A | 2.5<br>INCW<br>RR1      | 2.6<br>INCW<br>IRR1      | 2.3<br><b>CP</b><br>r1,r2    | 2.4<br><b>CP</b><br>r1,lr2     | 3.3<br><b>CP</b><br>R2,R1   | 3.4<br><b>CP</b><br>IR2,R1   | 3.3<br><b>CP</b><br>R1,IM    | 3.4<br><b>CP</b><br>IR1,IM    | 4.3<br><b>CPX</b><br>ER2,ER1  | 4.3<br><b>CPX</b><br>IM,ER1    |                            |                          |                           |                           |                         | 1.4<br>RET                |

| В | 2.2<br>CLR<br>R1        | 2.3<br>CLR<br>IR1        | 2.3<br>XOR<br>r1,r2          | 2.4<br>XOR<br>r1,lr2           | 3.3<br><b>XOR</b><br>R2,R1  | 3.4<br>XOR<br>IR2,R1         | 3.3<br><b>XOR</b><br>R1,IM   | 3.4<br>XOR<br>IR1,IM          | 4.3<br><b>XORX</b><br>ER2,ER1 | 4.3<br><b>XORX</b><br>IM,ER1   |                            |                          |                           |                           |                         | 1.5<br>IRET               |

| С | 2.2<br><b>RRC</b><br>R1 | 2.3<br><b>RRC</b><br>IR1 | 2.5<br>LDC<br>r1,lrr2        | 2.9<br><b>LDCI</b><br>lr1,lrr2 | 2.3<br><b>JP</b><br>IRR1    | 2.9<br>LDC<br>lr1,lrr2       | ,                            | 3.4<br><b>LD</b><br>r1,r2,X   | 3.2<br>PUSHX<br>ER2           | ,                              |                            |                          |                           |                           |                         | 1.2<br>RCF                |

| D | 2.2<br>SRA<br>R1        | 2.3<br>SRA<br>IR1        | 2.5<br>LDC<br>r2,Irr1        | 2.9<br>LDCI<br>Ir2,Irr1        | 2.6                         | 2.2<br>BSWAP<br>R1           | 3.3<br>CALL<br>DA            | 3.4<br>LD<br>r2,r1,X          | 3.2<br>POPX<br>ER1            |                                |                            |                          |                           |                           |                         | 1.2<br>SCF                |

| E | 2.2<br>RR<br>R1         | 2.3<br><b>RR</b><br>IR1  | 2.2<br>BIT                   | 2.3<br>LD                      | 3.2<br>LD<br>R2,R1          | 3.3<br>LD                    | 3.2<br>LD                    | 3.3<br>LD                     | 4.2<br>LDX<br>ER2,ER1         | 4.2<br>LDX<br>IM,ER1           |                            |                          |                           |                           |                         | 1.2<br>CCF                |

| F | 2.2<br>SWAP             | 2.3<br>SWAP              | p,b,r1<br>2.6<br><b>TRAP</b> | r1,lr2<br>2.3<br>LD            | 2.8<br>MULT                 | 1R2,R1<br>3.3<br>LD          | 81,IM<br>3.3<br><b>BTJ</b>   | 3.4<br>BTJ                    | UKZ,EK1                       | iivi,⊂K I                      |                            | V                        |                           |                           | V                       |                           |

|   | R1                      | IR1                      | Vector                       | lr1,r2                         | RR1                         | R2,IR1                       | p,b,r1,X                     | p,b,lr1,X                     |                               |                                | 1                          | ۲                        | 1                         | 1                         | ۲                       |                           |

Figures 26 and 27 provide operation code mapping information about each of the eZ8 CPU instructions.

Figure 26. First Op Code Map

|          |                        | Power Consumption                                                                                                                                                                            |         |  |  |

|----------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--|--|

| Category | Block                  | Typical         Maxim           5mA         12m.           4mA         4.5m           350μA         400μ           330μA         450μ           120μA         150μ           2μA         3μA | Maximum |  |  |

| Logic    | CPU/Peripherals @20MHz | 5mA                                                                                                                                                                                          |         |  |  |

| Flash    | Flash@20MHz            |                                                                                                                                                                                              | 12mA    |  |  |

| Analog   | ADC@20MHz              | 4mA                                                                                                                                                                                          | 4.5mA   |  |  |

|          | IPO@20MHz              | 350µA                                                                                                                                                                                        | 400µA   |  |  |

|          | Comparator@10MHz       | 330µA                                                                                                                                                                                        | 450µA   |  |  |

|          | POR & VBO              | 120µA                                                                                                                                                                                        | 150µA   |  |  |

|          | WDT OSC                | 2µA                                                                                                                                                                                          | ЗµА     |  |  |

|          | OSC@20MHz              | 600µA                                                                                                                                                                                        | 900µA   |  |  |

|          | Clock Filter           | 120µA                                                                                                                                                                                        | 150µA   |  |  |

#### Table 128. Power Consumption Reference Table

Figure 33. Flash Current Diagram

#### Hex Address: FC5

| Bit     | 7      | 6       | 5      | 4      | 3             | 2      | 1      | 0      |  |  |  |  |

|---------|--------|---------|--------|--------|---------------|--------|--------|--------|--|--|--|--|

| Field   | PA7ENL | PA6CENL | PA5ENL | PA4ENL | <b>PA3ENL</b> | PA2ENL | PA1ENL | PA0ENL |  |  |  |  |

| RESET   | 0      | 0       | 0      | 0      | 0             | 0      | 0      | 0      |  |  |  |  |

| R/W     | R/W    | R/W     | R/W    | R/W    | R/W           | R/W    | R/W    | R/W    |  |  |  |  |

| Address |        | FC5H    |        |        |               |        |        |        |  |  |  |  |

#### Hex Address: FC6

#### Table 165. Interrupt Request 2 Register (IRQ2)

| Bit     | 7        | 6   | 5   | 4   | 3    | 2    | 1    | 0    |

|---------|----------|-----|-----|-----|------|------|------|------|

| Field   | Reserved |     |     |     | PC3I | PC2I | PC1I | PC0I |

| RESET   | 0        | 0   | 0   | 0   | 0    | 0    | 0    | 0    |

| R/W     | R/W      | R/W | R/W | R/W | R/W  | R/W  | R/W  | R/W  |

| Address | FC6H     |     |     |     |      |      |      |      |

#### Hex Address: FC7

#### Table 166. IRQ2 Enable High Bit Register (IRQ2ENH)

| Bit     | 7        | 6   | 5   | 4   | 3     | 2     | 1     | 0     |

|---------|----------|-----|-----|-----|-------|-------|-------|-------|

| Field   | Reserved |     |     |     | C3ENH | C2ENH | C1ENH | C0ENH |

| RESET   | 0        | 0   | 0   | 0   | 0     | 0     | 0     | 0     |

| R/W     | R/W      | R/W | R/W | R/W | R/W   | R/W   | R/W   | R/W   |

| Address | FC7H     |     |     |     |       |       |       |       |

#### Hex Address: FC8

#### Table 167. IRQ2 Enable Low Bit Register (IRQ2ENL)

| Bit     | 7        | 6   | 5   | 4   | 3     | 2     | 1     | 0     |

|---------|----------|-----|-----|-----|-------|-------|-------|-------|

| Field   | Reserved |     |     |     | C3ENL | C2ENL | C1ENL | C0ENL |

| RESET   | 0        | 0   | 0   | 0   | 0     | 0     | 0     | 0     |

| R/W     | R/W      | R/W | R/W | R/W | R/W   | R/W   | R/W   | R/W   |

| Address | FC8H     |     |     |     |       |       |       |       |

# **Customer Support**

To share comments, get your technical questions answered or report issues you may be experiencing with our products, please visit Zilog's Technical Support page at <u>http://support.zilog.com</u>.

To learn more about this product, find additional documentation or to discover other facets about Zilog product offerings, please visit the Zilog Knowledge Base at <u>http://zilog.com/</u><u>kb</u> or consider participating in the Zilog Forum at <u>http://zilog.com/forum</u>.

This publication is subject to replacement by a later edition. To determine whether a later edition exists, please visit the Zilog website at <u>http://www.zilog.com</u>.