Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Active                                                    |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | -                                                         |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 17                                                        |

| Program Memory Size        | 8KB (8K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 7x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 20-VQFN Exposed Pad                                       |

| Supplier Device Package    | 20-QFN (5x5)                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f083aqh020eg |

| Assembly Language Programming Introduction              | 162 |

|---------------------------------------------------------|-----|

| Assembly Language Syntax                                | 163 |

| eZ8 CPU Instruction Notation                            | 164 |

| eZ8 CPU Instruction Classes                             | 166 |

| eZ8 CPU Instruction Summary                             | 171 |

| Op Code Maps                                            | 181 |

| Electrical Characteristics                              | 184 |

| Absolute Maximum Ratings                                | 184 |

| DC Characteristics                                      | 185 |

| AC Characteristics                                      | 188 |

| On-Chip Peripheral AC and DC Electrical Characteristics | 189 |

| General Purpose I/O Port Input Data Sample Timing       | 194 |

| GPIO Port Output Timing                                 | 195 |

| On-Chip Debugger Timing                                 | 196 |

| Packaging                                               | 198 |

| Ordering Information                                    | 199 |

| Part Number Suffix Designations                         |     |

| Appendix A. Register Tables                             | 203 |

| General Purpose RAM                                     |     |

| Timer 0                                                 |     |

| Analog-to-Digital Converter (ADC)                       | 208 |

| Low Power Control                                       |     |

| LED Controller                                          | 212 |

| Oscillator Control                                      | 213 |

| Comparator 0                                            | 214 |

| Interrupt Controller                                    | 214 |

| GPIO Port A                                             | 218 |

| Watchdog Timer (WDT)                                    | 222 |

| Trim Bit Control                                        | 224 |

| Flash Memory Controller                                 | 224 |

| Index                                                   | 227 |

| Customer Support                                        |     |

# List of Figures

| Figure 1.  | Z8 Encore! F083A Series Block Diagram                                                                  |

|------------|--------------------------------------------------------------------------------------------------------|

| Figure 2.  | Z8F083A Series in 20-Pin SOIC, SSOP, PDIP Package                                                      |

| Figure 3.  | Z8F083A Series in 28-Pin SOIC and SSOP Packages                                                        |

| Figure 4.  | Z8F083A Series in 20-Pin QFN Package                                                                   |

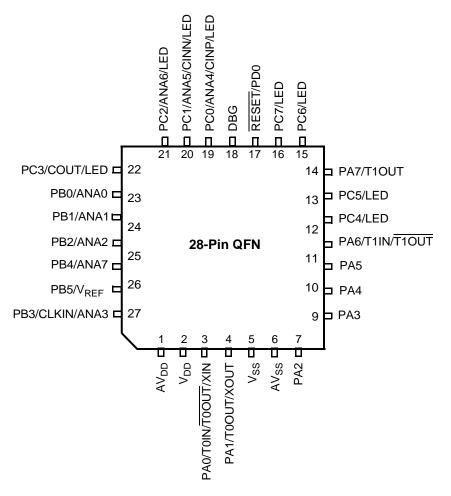

| Figure 5.  | Z8F083A Series in 28-Pin QFN Package                                                                   |

| Figure 6.  | Power-On Reset Operation                                                                               |

| Figure 7.  | Voltage Brown-Out Reset Operation                                                                      |

| Figure 8.  | GPIO Port Pin Block Diagram                                                                            |

| Figure 9.  | Interrupt Controller Block Diagram                                                                     |

| Figure 10. | Timer Block Diagram                                                                                    |

| Figure 11. | Analog-to-Digital Converter Block Diagram                                                              |

| Figure 12. | ADC Timing Diagram                                                                                     |

| Figure 13. | ADC Convert Timing                                                                                     |

| Figure 14. | 4K Flash with NVDS                                                                                     |

| Figure 15. | 8K Flash with NVDS                                                                                     |

| Figure 16. | Flash Controller Operation Flow Chart                                                                  |

| Figure 17. | On-Chip Debugger Block Diagram                                                                         |

| Figure 18. | Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface, # 1 of 2                          |

| Figure 19. | Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface, #2 of 2                           |

| Figure 20. | OCD Data Format                                                                                        |

| Figure 21. | Oscillator Control Clock Switching Flow Chart                                                          |

| Figure 22. | Recommended 20 MHz Crystal Oscillator Configuration                                                    |

| Figure 23. | Connecting the On-Chip Oscillator to an External RC Network 159                                        |

| Figure 24. | Typical RC Oscillator Frequency as a Function of the External Capacitance with a 45 <b>KΩ</b> Resistor |

| Figure 25. | Op Code Map Cell Description                                                                           |

| Figure 26. | First Op Code Map                                                                                      |

# Z8 Encore!® F083A Series Product Specification

xvii

| TD 11 110  | ADGD A DECEMBER (ADGD T)                 | 210 |

|------------|------------------------------------------|-----|

|            | ADC Data Low Bits Register (ADCD_L)      |     |

|            | ADC Sample Settling Time (ADCSST)        |     |

|            | ADC Sample Time (ADCST)                  |     |

| Table 152. | ADC Clock Prescale Register (ADCCP)      | 211 |

| Table 153. | Power Control Register 0 (PWRCTL0)       | 212 |

| Table 154. | LED Drive Enable (LEDEN)                 | 212 |

| Table 155. | LED Drive Level High Register (LEDLVLH)  | 213 |

| Table 156. | LED Drive Level Low Register (LEDLVLL)   | 213 |

| Table 157. | Oscillator Control Register (OSCCTL)     | 213 |

| Table 158. | Comparator Control Register (CMP0)       | 214 |

| Table 159. | Interrupt Request 0 Register (IRQ0)      | 214 |

| Table 160. | IRQ0 Enable High Bit Register (IRQ0ENH)  | 215 |

| Table 161. | IRQ0 Enable Low Bit Register (IRQ0ENL)   | 215 |

| Table 162. | Interrupt Request 1 Register (IRQ1)      | 215 |

| Table 163. | IRQ1 Enable High Bit Register (IRQ1ENH)  | 215 |

| Table 164. | IRQ1 Enable Low Bit Register (IRQ1ENL)   | 216 |

| Table 165. | Interrupt Request 2 Register (IRQ2)      | 216 |

| Table 166. | IRQ2 Enable High Bit Register (IRQ2ENH)  | 216 |

| Table 167. | IRQ2 Enable Low Bit Register (IRQ2ENL)   | 216 |

| Table 168. | Interrupt Edge Select Register (IRQES)   | 217 |

| Table 169. | Shared Interrupt Select Register (IRQSS) | 217 |

| Table 170. | Interrupt Control Register (IRQCTL)      | 217 |

| Table 171. | Port A GPIO Address Register (PAADDR)    | 218 |

| Table 172. | Port A Control Registers (PACTL)         | 218 |

| Table 173. | Port A Input Data Registers (PAIN)       | 218 |

| Table 174. | Port A Output Data Register (PAOUT)      | 219 |

| Table 175. | Port B GPIO Address Register (PBADDR)    | 219 |

|            | Port B Control Registers (PBCTL)         |     |

|            | Port B Input Data Registers (PBIN)       |     |

|            | Port B Output Data Register (PBOUT)      |     |

### Z8 Encore!® F083A Series Product Specification

xviii

| Table 179. | Port C GPIO Address Register (PCADDR)            | 220 |

|------------|--------------------------------------------------|-----|

| Table 180. | Port C Control Registers (PCCTL)                 | 220 |

| Table 181. | Port C Input Data Registers (PCIN)               | 220 |

| Table 182. | Port C Output Data Register (PCOUT)              | 221 |

| Table 183. | Port D GPIO Address Register (PDADDR)            | 221 |

| Table 184. | Port D Control Registers (PDCTL)                 | 221 |

| Table 185. | Port D Output Data Register (PDOUT)              | 222 |

| Table 186. | Watchdog Timer Control Register (WDTCTL)         | 222 |

| Table 187. | Reset Status Register (RSTSTAT)                  | 222 |

| Table 188. | Watchdog Timer Reload Upper Byte Register (WDTU) | 223 |

| Table 189. | Watchdog Timer Reload High Byte Register (WDTH)  | 223 |

| Table 190. | Watchdog Timer Reload Low Byte Register (WDTL)   | 223 |

| Table 191. | Trim Bit Address Register (TRMADR)               | 224 |

| Table 192. | Trim Bit Data Register (TRMDR)                   | 224 |

| Table 193. | Flash Control Register (FCTL)                    | 224 |

| Table 194. | Flash Status Register (FSTAT)                    | 225 |

| Table 195. | Flash Page Select Register (FPS)                 | 225 |

| Table 196. | Flash Sector Protect Register (FPROT)            | 225 |

| Table 197. | Flash Frequency High Byte Register (FFREQH)      | 226 |

| Table 198. | Flash Frequency Low Byte Register (FFREQL)       | 226 |

#### **Reset Controller**

The Z8 Encore! F083A Series products are reset using any one of the following: the RESET pin, POR, WDT time-out, STOP Mode exit or VBO warning signal. The RESET pin is bidirectional, that is, it functions as reset source as well as a reset indicator.

#### **On-Chip Debugger**

The Z8 Encore! F083A Series products feature an integrated OCD. The OCD provides a rich set of debugging capabilities, such as reading and writing registers, programming Flash memory, setting breakpoints and executing code. The OCD uses one single-pin interface for communication with an external host.

### **Acronyms and Expansions**

This document references a number of acronyms; each is expanded in Table 2 for the reader's understanding.

**Table 2. Acronyms and Expansions**

| Acronyms | Expansions                        |

|----------|-----------------------------------|

| ADC      | Analog-to-Digital Converter       |

| NVDS     | Nonvolatile Data Storage          |

| WDT      | Watchdog Timer                    |

| GPIO     | General-Purpose Input/Output      |

| OCD      | On-Chip Debugger                  |

| POR      | Power-On Reset                    |

| VBO      | Voltage Brownout                  |

| IPO      | Internal Precision Ocsillator     |

| PDIP     | Plastic Dual Inline Package       |

| SOIC     | Small Outline Integrated Circuit  |

| SSOP     | Small Shrink Outline Package      |

| QFN      | Quad Flat No Lead                 |

| IRQ      | Interrupt request                 |

| ISR      | Interrupt service routine         |

| MSB      | Most significant byte             |

| LSB      | Least significant byte            |

| PWM      | Pulse Width Modulation            |

| SAR      | Successive Approximation Register |

Figure 5. Z8F083A Series in 28-Pin QFN Package

### **Program Memory**

The eZ8 CPU supports 64KB of program memory address space. The Z8 Encore! F083A Series devices contain 1KB to 12KB of on-chip Flash memory in the program memory address space, depending on the device. Reading from program memory addresses outside the available Flash memory addresses returns FFH. Writing to these unimplemented program memory addresses produces no effect. Table 6 describes the program memory maps for the Z8 Encore! F083A Series products.

Table 6. Z8 Encore! F083A Series Program Memory Maps

| Program Memory<br>Address (Hex) | Function                                 |

|---------------------------------|------------------------------------------|

| Z8F083A Products                |                                          |

| 0000–0001                       | Flash Option Bits                        |

| 0002-0003                       | Reset Vector                             |

| 0004-003D                       | Interrupt Vectors*                       |

| 003E-1FFF                       | Program Memory                           |

| Z8F043A Products                |                                          |

| 0000-0001                       | Flash Option Bits                        |

| 0002-0003                       | Reset Vector                             |

| 0004-003D                       | Interrupt Vectors*                       |

| 003E-0FFF                       | Program Memory                           |

| Note: *See <u>Table 34</u> on p | page 55 for a list of interrupt vectors. |

### **Data Memory**

The Z8 Encore! F083A Series does not use the eZ8 CPU's 64KB data memory address space.

### **Flash Information Area**

Table 7 indicates the Z8 Encore! F083A Series MCUs' Flash information area. This 128-byte information area is accessed by setting bit 7 of the Flash Page Select Register to 1. When access is enabled, the Flash information area is mapped into program memory and overlays the 128 bytes at addresses FE00H to FE7FH. When information area access is enabled, all reads from these program memory addresses return information area data rather than program memory data. Access to the Flash information area is read-only.

Table 8. Register File Address Map (Continued)

| Address (Hex   | ) Register Description                | Mnemonic | Reset (Hex) | Page #              |

|----------------|---------------------------------------|----------|-------------|---------------------|

| Trim Bit Cont  | rol                                   |          |             |                     |

| FF6            | Trim Bit Address                      | TRMADR   | 00          | 126                 |

| FF7            | Trim Data                             | TRMDR    | XX          | 127                 |

| Flash Memory   | / Controller                          |          |             |                     |

| FF8            | Flash Control                         | FCTL     | 00          | 120                 |

| FF8            | Flash Status                          | FSTAT    | 00          | 121                 |

| FF9            | Flash Page Select                     | FPS      | 00          | 122                 |

|                | Flash Sector Protect                  | FPROT    | 00          | 122                 |

| FFA            | Flash Programming Frequency High Byte | FFREQH   | 00          | 123                 |

| FFB            | Flash Programming Frequency Low Byte  | FFREQL   | 00          | 123                 |

| eZ8 CPU        |                                       |          |             |                     |

| FFC            | Flags                                 | _        | XX          | Refer to the        |

| FFD            | Register Pointer                      | RP       | XX          | eZ8 CPU             |

| FFE            | Stack Pointer High Byte               | SPH      | XX          | Core User<br>Manual |

| FFF            | Stack Pointer Low Byte                | SPL      | XX          | (UM0128)            |

| Note: XX = Uno | defined.                              |          |             |                     |

Writing 1 to the IRQE bit in the Interrupt Control Register

Interrupts are globally disabled by any of the following actions:

- Execution of a DI (disable interrupt) instruction

- eZ8 CPU acknowledgement of an interrupt service request from the Interrupt Controller

- Writing a 0 to the IRQE bit in the Interrupt Control Register

- Reset

- Execution of a trap instruction

- Illegal instruction trap

- Primary oscillator fail trap

- Watchdog oscillator fail trap

#### **Interrupt Vectors and Priority**

The Interrupt Controller supports three levels of interrupt priority. Level 3 is the highest priority, level 2 is the second highest priority and level 1 is the lowest priority. If all of the interrupts are enabled with identical interrupt priority (all as level 2 interrupts, for example), the interrupt priority is assigned from highest to lowest as specified in <u>Table 34</u> on page 55. Level 3 interrupts are always assigned higher priority than level 2 interrupts and level 2 interrupts are assigned higher priority than level 1 interrupts. Within each interrupt priority level (level 1, level 2 or level 3), priority is assigned as specified in Table 34. Reset, Watchdog Timer interrupts (if enabled), primary oscillator fail traps, Watchdog oscillator fail traps and illegal instruction traps always have highest (level 3) priority.

#### **Interrupt Assertion**

Interrupt sources assert their interrupt requests for only a single system clock period (single pulse). When the interrupt request is acknowledged by the eZ8 CPU, the corresponding bit in the interrupt request register is cleared. Writing 0 to the corresponding bit in the interrupt request register clears the interrupt request.

**Caution:** Zilog recommends not using a coding style that clears bits in the Interrupt Request registers. All incoming interrupts received between execution of the first LDX command and the final LDX command are lost. See Example 1, which follows.

**Example 1.** A poor coding style that can result in lost interrupt requests:

| Bit    | Description (Continued)                                                                              |

|--------|------------------------------------------------------------------------------------------------------|

| [0]    | Input Capture Event                                                                                  |

| INPCAP | This bit indicates whether the most recent timer interrupt is caused by a timer input capture event. |

|        | 0 = Previous timer interrupt is not caused by timer input capture event.                             |

|        | 1 = Previous timer interrupt is caused by timer input capture event .                                |

#### Timer 0–1 Control Register 1

The Timer 0–1 Control (TxCTL1) Register, shown in Table 57, enables/disables the timers, set the prescaler value and determines the timer operating mode.

Table 57. Timer 0–1 Control Register 1 (TxCTL1)

| Bit     | 7   | 6          | 5   | 4    | 3   | 2   | 1     | 0   |

|---------|-----|------------|-----|------|-----|-----|-------|-----|

| Field   | TEN | TPOL       |     | PRES |     |     | TMODE |     |

| RESET   | 0   | 0          | 0   | 0    | 0   | 0   | 0     | 0   |

| R/W     | R/W | R/W        | R/W | R/W  | R/W | R/W | R/W   | R/W |

| Address |     | F07H, F0FH |     |      |     |     |       |     |

| Bit | Description                 |

|-----|-----------------------------|

| [7] | Timer Enable                |

| TEN | 0 = Timer is disabled.      |

|     | 1 = Timer enabled to count. |

#### **ADC Interrupt**

The ADC generates an interrupt request when a conversion has been completed. An interrupt request that is pending when the ADC is disabled is not cleared automatically.

#### Reference Buffer

The reference buffer, RBUF, supplies the reference voltage for the ADC. When enabled, the internal voltage reference generator supplies the ADC. When RBUF is disabled, the ADC must have the reference voltage supplied externally through the  $V_{REF}$  pin in 28-pin package. RBUF is controlled by the REFEN bit in the ADC Control Register.

#### **Internal Voltage Reference Generator**

The internal voltage reference generator provides the RBUF voltage, VR2; this VR2 value is 2 V.

#### **Calibration and Compensation**

The user can perform calibration and store the values into Flash; conversely, the user code can perform a manual offset calibration. There is no provision for manual gain calibration.

### **ADC Control Register Definitions**

The ADC control registers are defined in this section.

#### **ADC Control Register 0**

The ADC Control Register 0, shown in Table 63, initiates the A/D conversion and provides ADC status information.

Table 63. ADC Control Register 0 (ADCCTL0)

| Bit     | 7     | 6        | 5     | 4     | 3        | 2   | 1          | 0   |

|---------|-------|----------|-------|-------|----------|-----|------------|-----|

| Field   | START | Reserved | REFEN | ADCEN | Reserved |     | ANAIN[2:0] |     |

| RESET   | 0     | 0        | 0     | 0     | 0        | 0   | 0          | 0   |

| R/W     | R/W1  | R/W      | R/W   | R/W   | R/W      | R/W | R/W        | R/W |

| Address | F70h  |          |       |       |          |     |            |     |

## Bit Position Description

|       | <u>-</u>                                                                                                           |

|-------|--------------------------------------------------------------------------------------------------------------------|

|       |                                                                                                                    |

| [7]   | ADC Start/Busy                                                                                                     |

| START | 0 = Writing to 0 has no effect. Reading a 0 indicates that the ADC is available to begin a conversion.             |

|       | 1 = Writing to 1 starts a conversion. Reading a 1 indicates that a conversion is currently in<br>progress.         |

| [6]   | Reserved                                                                                                           |

|       | This bit is reserved and must be programmed to 0.                                                                  |

| [5]   | Reference Enable                                                                                                   |

| REFEN | 0 = Internal reference voltage is disabled allowing an external reference voltage to be used by the ADC.           |

|       | 1 = Internal reference voltage for the ADC is enabled. The internal reference voltage is measured on the VREF pin. |

| [4]   | ADC Enable                                                                                                         |

| ADCEN | 0 = ADC is disabled for Low Power operation.                                                                       |

|       | 1 = ADC is enabled for normal use.                                                                                 |

| [3]   | Reserved                                                                                                           |

|       | This bit is reserved and must be programmed to 0.                                                                  |

| Bit           | Description (Continued)                                                                                                        |

|---------------|--------------------------------------------------------------------------------------------------------------------------------|

| [1]<br>IGADDR | Illegal Address When NVDS byte reads from invalid addresses occur (those exceeding the NVDS array size), this bit is set to 1. |

| [0]           | Reserved This bit is reserved and must be programmed to 0.                                                                     |

#### **Power Failure Protection**

The NVDS routines employ error-checking mechanisms to ensure that any power failure will only endanger the most recently written byte. Bytes previously written to the array are not perturbed. For this protection to function, the VBO must be enabled (See *the* Low-Power Modes chapter on page 30) and configured for a threshold voltage of 2.4V or greater (See *the* Trim Bit Address Space section on page 129).

A system reset (such as a pin reset or Watchdog Timer reset) that occurs during a write operation also perturbs the byte currently being written. All other bytes in the array are unperturbed.

#### **Optimizing NVDS Memory Usage for Execution Speed**

As Table 94 shows, NVDS read times vary drastically, this discrepancy being a trade-off for minimizing the frequency of writes that require post-write page erases. The NVDS read time of address N is a function of the number of writes to addresses other than N since the most recent write to address N, as well as the number of writes since the most recent page erase. Neglecting effects caused by page erases and results caused by the initial condition in which the NVDS is blank, a rule of thumb is that every write since the most recent page erase causes read times of unwritten addresses to increase by  $0.8 \, \mu s$ , up to a maximum of  $258 \, \mu s$ .

Table 94, NVDS Read Time

| Operation     | Minimum<br>Latency (µs) | Maximum<br>Latency (µs) |

|---------------|-------------------------|-------------------------|

| Read          | 71                      | 258                     |

| Write         | 126                     | 136                     |

| Illegal Read  | 6                       | 6                       |

| Illegal Write | 7                       | 7                       |

Table 97. OCD Control Register (OCDCTL)

| Bit   | 7       | 6     | 5      | 4 | 3   | 2 | 1 | 0   |

|-------|---------|-------|--------|---|-----|---|---|-----|

| Field | DBGMODE | BRKEN | DBGACK |   | RST |   |   |     |

| RESET | 0       | 0     | 0      | 0 | 0   | 0 | 0 | 0   |

| R/W   | R/W     | R/W   | R/W    | R | R   | R | R | R/W |

| Bit            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>DBGMODE | DEBUG Mode The device enters DEBUG Mode when this bit is 1. When in DEBUG Mode, the eZ8 CPU stops fetching new instructions. Clearing this bit causes the eZ8 CPU to restart. This bit is automatically set when a BRK instruction is decoded and breakpoints are enabled. If the Flash read protect option bit is enabled, this bit is cleared only by resetting the device. It cannot be written to 0.  0 = The Z8 Encore! F083A Series device is operating in NORMAL Mode.  1 = The Z8 Encore! F083A Series device is in DEBUG Mode. |

| [6]<br>BRKEN   | Breakpoint Enable This bit controls the behavior of the BRK instruction (Opcode 00H). By default, breakpoints are disabled and the BRK instruction behaves similar to an NOP instruction. If this bit is 1 when a BRK instruction is decoded, the DBGMODE bit of the OCDCTL register is automatically set to 1.  0 = Breakpoints are disabled.  1 = Breakpoints are enabled.                                                                                                                                                            |

| [5]<br>DBGACK  | Debug Acknowledge This bit enables the debug acknowledge feature. If this bit is set to 1, the OCD sends a Debug acknowledge character (FFH) to the host when a breakpoint occurs.  0 = Debug acknowledge is disabled.  1 = Debug acknowledge is enabled.                                                                                                                                                                                                                                                                               |

| [4:1]          | Reserved These bits are reserved and must be programmed to 0000.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| [0]<br>RST     | Reset Setting this bit to 1 resets the Z8F04xA family device. The device goes through a normal POR sequence with the exception that the On-Chip Debugger is not reset. This bit is automatically cleared to 0 at the end of reset.  0 = No effect.  1 = Reset the Flash read protect option bit device.                                                                                                                                                                                                                                 |

### Oscillator Control

The Z8 Encore! F083A Series device uses five possible clocking schemes; each one of these clocking schemes is user-selectable.

- On-chip precision trimmed RC oscillator

- On-chip oscillator using off-chip crystal or resonator

- On-chip oscillator using external RC network

- External clock drive

- On-chip low precision Watchdog Timer Oscillator

In addition, Z8 Encore! F083A Series devices contain clock failure detection and recovery circuitry to allow continued operation despite any potential failure of the primary oscillator.

### **Operation**

This chapter discusses the logic used to select the system clock and handle primary oscillator failures. A description of the specific operation of each oscillator is outlined elsewhere in this document: see the <u>Watchdog Timer</u> chapter on page 92 and the <u>Crystal Oscillator</u> chapter on page 157.

#### **System Clock Selection**

The oscillator control block selects from the available clocks. Table 99 describes each clock source and its usage.

Table 114. eZ8 CPU Instruction Summary (Continued)

| Assembly      |                      |     | ress<br>ode | Op<br>Code(s) |   |   | Fla | ags |   |   | - Fetch | Instr. |

|---------------|----------------------|-----|-------------|---------------|---|---|-----|-----|---|---|---------|--------|

| Mnemonic      | Symbolic Operation   | dst | src         | (Hex)         | С | Z | s   | ٧   | D | Н | Cycles  |        |

| CALL dst      | SP ← SP -2           | IRR |             | D4            | - | - | -   | -   | - | - | 2       | 6      |

|               | @SP ← PC<br>PC ← dst | DA  |             | D6            | _ |   |     |     |   |   | 3       | 3      |

| CCF           | C ← ~C               |     |             | EF            | * | - | -   | -   | - |   | 1       | 2      |

| CLR dst       | dst ← 00H            | R   |             | В0            | - | - | -   | -   | - | - | 2       | 2      |

|               |                      | IR  |             | B1            |   |   |     |     |   |   | 2       | 3      |

| COM dst       | dst ← ~dst           | R   |             | 60            | _ | * | *   | 0   | _ | _ | 2       | 2      |

|               |                      | IR  |             | 61            |   |   |     |     |   |   | 2       | 3      |

| CP dst, src   | dst - src            | r   | r           | A2            | * | * | *   | *   | _ | - | 2       | 3      |

|               |                      | r   | Ir          | А3            |   |   |     |     |   |   | 2       | 4      |

|               |                      | R   | R           | A4            |   |   |     |     |   |   | 3       | 3      |

|               |                      | R   | IR          | A5            |   |   |     |     |   |   | 3       | 4      |

|               |                      | R   | IM          | A6            |   |   |     |     |   |   | 3       | 3      |

|               |                      | IR  | IM          | A7            |   |   |     |     |   |   | 3       | 4      |

| CPC dst, src  | dst - src - C        | r   | r           | 1F A2         | * | * | *   | *   | _ | _ | 3       | 3      |

|               |                      | r   | lr          | 1F A3         |   |   |     |     |   |   | 3       | 4      |

|               |                      | R   | R           | 1F A4         |   |   |     |     |   |   | 4       | 3      |

|               |                      | R   | IR          | 1F A5         |   |   |     |     |   |   | 4       | 4      |

|               |                      | R   | IM          | 1F A6         |   |   |     |     |   |   | 4       | 3      |

|               |                      | IR  | IM          | 1F A7         |   |   |     |     |   |   | 4       | 4      |

| CPCX dst, src | dst - src - C        | ER  | ER          | 1F A8         | * | * | *   | *   | _ | _ | 5       | 3      |

|               |                      | ER  | IM          | 1F A9         | _ |   |     |     |   |   | 5       | 3      |

| CPX dst, src  | dst - src            | ER  | ER          | A8            | * | * | *   | *   | _ | _ | 4       | 3      |

|               |                      | ER  | IM          | A9            | _ |   |     |     |   |   | 4       | 3      |

Note: Flags Notation:

<sup>\* =</sup> Value is a function of the result of the operation.

<sup>-</sup> = Unaffected.

X = Undefined.

<sup>0 =</sup> Reset to 0.

<sup>1 =</sup> Set to 1.

Table 114. eZ8 CPU Instruction Summary (Continued)

| Assembly      |                    | Address<br>Mode |     | Op<br>Code(s) | Flags |   |   |   |   | - Fetch | Instr. |   |

|---------------|--------------------|-----------------|-----|---------------|-------|---|---|---|---|---------|--------|---|

| Mnemonic      | Symbolic Operation | dst             | src | (Hex)         | С     | Z | S | ٧ | D | Н       | Cycles |   |

| XOR dst, src  | dst ← dst XOR src  | r               | r   | B2            | -     | * | * | 0 | _ | _       | 2      | 3 |

|               |                    | r               | lr  | В3            | _     |   |   |   |   |         | 2      | 4 |

|               |                    | R               | R   | B4            | _     |   |   |   |   |         | 3      | 3 |

|               |                    | R               | IR  | B5            | _     |   |   |   |   |         | 3      | 4 |

|               |                    | R               | IM  | B6            | _     |   |   |   |   |         | 3      | 3 |

|               |                    | IR              | IM  | B7            | _     |   |   |   |   |         | 3      | 4 |

| XORX dst, src | dst ← dst XOR src  | ER              | ER  | B8            | _     | * | * | 0 | _ | _       | 4      | 3 |

|               |                    | ER              | IM  | В9            | _     |   |   |   |   |         | 4      | 3 |

Note: Flags Notation:

\* = Value is a function of the result of the operation.

<sup>-</sup> = Unaffected.

X = Undefined.

<sup>0 =</sup> Reset to 0.

<sup>1 =</sup> Set to 1.

**Table 120. Flash Memory Electrical Characteristics and Timing**

|                                                  | V <sub>DD</sub> = 2.7V to 3.6V<br>T <sub>A</sub> = 0°C to +70°C |     |     |        | 2.7V to |     |        |                                                                                                                                                    |

|--------------------------------------------------|-----------------------------------------------------------------|-----|-----|--------|---------|-----|--------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                                        | Min                                                             | Тур | Max | Min    | Тур     | Max | Units  | Notes                                                                                                                                              |

| Flash Byte Read<br>Time                          |                                                                 |     |     | 50     | -       | -   | ns     |                                                                                                                                                    |

| Flash Byte Program Time                          |                                                                 |     |     | 20     | -       | _   | μs     |                                                                                                                                                    |

| Flash Page Erase<br>Time                         |                                                                 |     |     | 50     | -       | _   | ms     |                                                                                                                                                    |

| Flash Mass Erase<br>Time                         |                                                                 |     |     | 50     | -       | _   | ms     |                                                                                                                                                    |

| Writes to Single<br>Address Before<br>Next Erase |                                                                 |     |     | _      | -       | 2   |        |                                                                                                                                                    |

| Flash Row<br>Program Time                        |                                                                 |     |     | -      | -       | 8   | ms     | Cumulative program time for single row cannot exceed limit before next erase. This parameter is only an issue when bypassing the Flash Controller. |

| Data Retention                                   |                                                                 |     |     | 10     | -       | -   | years  | 25°C                                                                                                                                               |

| Endurance                                        |                                                                 |     |     | 10,000 | _       | _   | cycles | Program/erase cycles                                                                                                                               |

Table 121. Watchdog Timer Electrical Characteristics and Timing

|                  |                          | $V_{DD} = 2.7 \text{V to } 3.6 \text{V}$<br>$T_A = 0^{\circ}\text{C to } +70^{\circ}\text{C}$ |     |     | $V_{DD} = 2.7 \text{V to } 3.6 \text{V}$<br>$T_A = -40 ^{\circ}\text{C to } +105 ^{\circ}\text{C}$ |     |     |       |            |

|------------------|--------------------------|-----------------------------------------------------------------------------------------------|-----|-----|----------------------------------------------------------------------------------------------------|-----|-----|-------|------------|

| Symbol           | Parameter                | Min                                                                                           | Тур | Max | Min                                                                                                | Тур | Max | Units | Conditions |

|                  | Active power consumption |                                                                                               |     |     |                                                                                                    | 2   | 3   | μΑ    |            |

| F <sub>WDT</sub> | WDT oscillator frequency |                                                                                               |     |     | 2.5                                                                                                | 5   | 7.5 | kHz   |            |

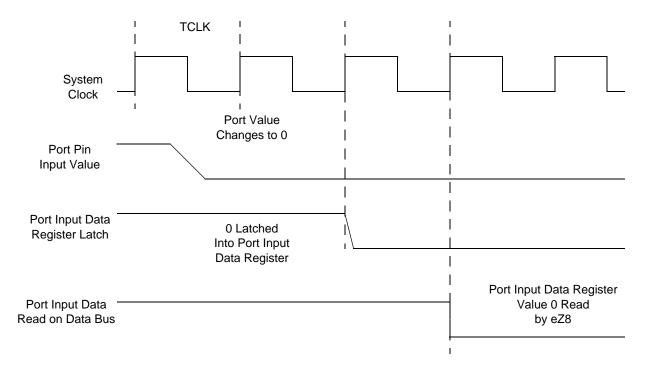

#### **General Purpose I/O Port Input Data Sample Timing**

Figure 30 and Table 125 display timing data for the GPIO port input sampling operation. The input value on a GPIO port pin is sampled on the rising edge of the system clock. The port value is available to the eZ8 CPU on the second rising clock edge following the change of the port value.

Figure 30. Port Input Sample Timing

**Table 125. GPIO Port Input Timing**

|                     |                                                                                                    | Delay (ns) |         |  |  |

|---------------------|----------------------------------------------------------------------------------------------------|------------|---------|--|--|

| Parameter           | Abbreviation                                                                                       | Minimum    | Maximum |  |  |

| T <sub>S_PORT</sub> | Port Input Transition to XIN Rise Setup Time (not pictured)                                        | 5          | _       |  |  |

| T <sub>H_PORT</sub> | X <sub>IN</sub> Rise to Port Input Transition Hold Time (not pictured)                             | 0          | _       |  |  |

| T <sub>SMR</sub>    | GPIO Port Pin Pulse Width to ensure Stop Mode Recovery (for GPIO Port Pins enabled as SMR sources) | 1µs        |         |  |  |

**Hex Address: F09**

Table 140. Timer 1 Low Byte Register (T1L)

| Bit     | 7   | 6    | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |  |

|---------|-----|------|-----|-----|-----|-----|-----|-----|--|--|--|--|

| Field   | TL  |      |     |     |     |     |     |     |  |  |  |  |

| RESET   | 0   | 0    | 0   | 0   | 0   | 0   | 0   | 1   |  |  |  |  |

| R/W     | R/W | R/W  | R/W | R/W | R/W | R/W | R/W | R/W |  |  |  |  |

| Address |     | F09H |     |     |     |     |     |     |  |  |  |  |

**Hex Address: F0A**

Table 141. Timer 1 Reload High Byte Register (T1RH)

| Bit     | 7   | 6    | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |  |

|---------|-----|------|-----|-----|-----|-----|-----|-----|--|--|--|--|

| Field   | TRH |      |     |     |     |     |     |     |  |  |  |  |

| RESET   | 1   | 1    | 1   | 1   | 1   | 1   | 1   | 1   |  |  |  |  |

| R/W     | R/W | R/W  | R/W | R/W | R/W | R/W | R/W | R/W |  |  |  |  |

| Address |     | F0AH |     |     |     |     |     |     |  |  |  |  |

Hex Address: F0B

Table 142. Timer 1 Reload Low Byte Register (T1RL)

| Bit     | 7    | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

|---------|------|-----|-----|-----|-----|-----|-----|-----|--|--|

| Field   | TRL  |     |     |     |     |     |     |     |  |  |

| RESET   | 1    | 1   | 1   | 1   | 1   | 1   | 1   | 1   |  |  |

| R/W     | R/W  | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| Address | F0BH |     |     |     |     |     |     |     |  |  |

**Hex Address: F0C**

Table 143. Timer 1 PWM High Byte Register (T1PWMH)

| Bit     | 7    | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

|---------|------|-----|-----|-----|-----|-----|-----|-----|--|--|

| Field   | PWMH |     |     |     |     |     |     |     |  |  |

| RESET   | 0    | 0   | 0   | 0   | 0   | 0   | 0   | 0   |  |  |

| R/W     | R/W  | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| Address | FOCH |     |     |     |     |     |     |     |  |  |