Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Active                                                    |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | -                                                         |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 17                                                        |

| Program Memory Size        | 8KB (8K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 7x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                            |

| Supplier Device Package    | 20-SOIC                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f083ash020sg |

### Z8 Encore!® F083A Series Product Specification

viii

| Trim Bit Address Space Trim Bit Address 0000H Trim Bit Address 0001H                                                                                  | 129                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| Trim Bit Address 0002H  Trim Bit Address 0003H  Trim Bit Address 0006H                                                                                | 131                             |

| Nonvolatile Data Storage Operation NVDS Code Interface Byte Write Byte Read Power Failure Protection Optimizing NVDS Memory Usage for Execution Speed | 134<br>134<br>135<br>136<br>137 |

| On-Chip Debugger  Architecture  Operation  OCD Interface  DEBUG Mode  OCD Data Format  OCD Autobaud Detector/Generator  OCD Serial Errors             | 139<br>140<br>141<br>142        |

| Breakpoints Runtime Counter On-Chip Debugger Commands On-Chip Debugger Control Register Definitions OCD Control Register OCD Status Register          | 144<br>144<br>148               |

| Oscillator Control Operation System Clock Selection Clock Failure Detection and Recovery Oscillator Control Register Definitions                      | 151<br>151<br>153               |

| Crystal Oscillator Operating Modes Crystal Oscillator Operation Oscillator Operation with an External RC Network                                      | 157                             |

| Internal Precision Oscillator                                                                                                                         |                                 |

| eZ8 CPU Instruction Set                                                                                                                               | 162                             |

### Z8 Encore!® F083A Series Product Specification

xiv

| Table 59. | Watchdog Timer Control Register (WDTCTL)            | 95    |

|-----------|-----------------------------------------------------|-------|

| Table 60. | Watchdog Timer Reload Upper Byte Register (WDTU)    | 96    |

| Table 61. | Watchdog Timer Reload High Byte Register (WDTH)     | 96    |

| Table 62. | Watchdog Timer Reload Low Byte Register (WDTL)      | 97    |

| Table 63. | ADC Control Register 0 (ADCCTL0)                    | . 102 |

| Table 64. | ADC Data High Byte Register (ADCD_H)                | . 103 |

| Table 65. | ADC Data Low Bits Register (ADCD_L)                 | . 104 |

| Table 66. | Sample Settling Time (ADCSST)                       | . 105 |

| Table 67. | Sample Time (ADCST)                                 | . 106 |

| Table 68. | ADC Clock Prescale Register (ADCCP)                 | . 107 |

| Table 69. | Comparator Control Register (CMP0)                  | . 109 |

| Table 70. | Z8 Encore! F083A Series Flash Memory Configurations | . 110 |

| Table 71. | Z8F083 Flash Memory Area Map                        | . 113 |

| Table 72. | Flash Code Protection Using Flash Option Bits       | . 116 |

| Table 73. | Flash Control Register (FCTL)                       | . 120 |

| Table 74. | Flash Status Register (FSTAT)                       | . 121 |

| Table 75. | Flash Page Select Register (FPS)                    | . 122 |

| Table 76. | Flash Sector Protect Register (FPROT)               | . 122 |

| Table 77. | Flash Frequency High Byte Register (FFREQH)         | . 123 |

| Table 78. | Flash Frequency Low Byte Register (FFREQL)          | . 123 |

| Table 79. | Trim Bit Address Register (TRMADR)                  | . 126 |

| Table 80. | Trim Bit Address Map                                | . 126 |

| Table 81. | Trim Bit Data Register (TRMDR)                      | . 127 |

| Table 82. | Flash Option Bits at Program Memory Address 0000H   | . 127 |

| Table 83. | Flash Options Bits at Program Memory Address 0001H  | . 128 |

| Table 84. | Trim Bit Address Space                              | . 129 |

| Table 85. | Trim Option Bits at 0000H (ADCREF)                  | . 129 |

| Table 86. | Trim Option Bits at 0001H (TADC_COMP)               | . 130 |

| Table 87. | Trim Option Bits at 0002H (TIPO)                    | . 131 |

| Table 88. | Trim Option Bits at 0003H (TVBO)                    | . 131 |

#### **CPU and Peripheral Overview**

Zilog's 8-bit eZ8 CPU meets the continuing demand for faster and more code-efficient microcontrollers. The eZ8 CPU executes a superset of the original Z8 instruction set. The eZ8 CPU features include:

- Direct register-to-register architecture allows each register to function as an accumulator, improving execution time and decreasing the required program memory

- Software stack allows much greater depth in subroutine calls and interrupts than hardware stacks

- Compatible with existing Z8 CPU code

- Expanded internal Register File allows access up to 4KB

- New instructions improve execution efficiency for code developed using high-level programming languages, including C

- Pipelined instruction fetch and execute

- New instructions for improved performance including BIT, BSWAP, BTJ, CPC, LDC, LDCI, LEA, MULT and SRL

- New instructions support 12-bit linear addressing of the Register File

- Up to 10 MIPS operation

- C Compiler-friendly

- Two to nine clock cycles per instruction

For more information regarding the eZ8 CPU, refer to <u>eZ8 CPU Core User Manual (UM0128)</u>, available for download on <u>www.zilog.com</u>.

#### **General Purpose Input/Output**

The Z8 Encore! F083A Series features up to 23 port pins (Ports A–D) for general purpose input/output (GPIO). The number of GPIO pins available is a function of package. Each pin is individually programmable.

#### Flash Controller

The Flash Controller programs and erases Flash memory. It also supports protection against accidental programming and erasure.

#### **Pin Characteristics**

Table 5 provides detailed characteristics of each pin available on the Z8 Encore! F083A Series 20- and 28-pin devices. The data in Table 5 are sorted alphabetically by the pin symbol mnemonic.

Table 5. Pin Characteristics (20- and 28-pin Devices)

| Symbol<br>Mnemonic | Direction | Reset<br>Direction            | Active<br>Low or<br>Active<br>High | Tristate<br>Output   | Internal<br>Pull-up or<br>Pull-down                  | Schmitt<br>Trigger<br>Input | Open Drain<br>Output                                 | 5V<br>Tolerance |

|--------------------|-----------|-------------------------------|------------------------------------|----------------------|------------------------------------------------------|-----------------------------|------------------------------------------------------|-----------------|

| AV <sub>DD</sub>   | N/A       | N/A                           | N/A                                | N/A                  | N/A                                                  | N/A                         | N/A                                                  | N/A             |

| AV <sub>SS</sub>   | N/A       | N/A                           | N/A                                | N/A                  | N/A                                                  | N/A                         | N/A                                                  | NA              |

| DBG                | I/O       | I                             | N/A                                | Yes                  | No                                                   | Yes                         | Yes                                                  | Yes             |

| PA[7:0]            | I/O       | I                             | N/A                                | Yes                  | Programma-<br>ble<br>pull-up                         | Yes                         | Yes,<br>programma-<br>ble                            | PA[7:2]<br>only |

| PB[5:0]            | I/O       | I                             | N/A                                | Yes                  | Programma-<br>ble<br>pull-up                         | Yes                         | Yes,<br>programma-<br>ble                            | No              |

| PC[7:0]            | I/O       | I                             | N/A                                | Yes                  | Programma-<br>ble<br>pull-up                         | Yes                         | Yes,<br>programma-<br>ble                            | PC[7:3]<br>only |

| RESET/<br>PD0      | I/O       | I/O<br>(defaults<br>to RESET) | Low (in<br>RESET<br>mode)          | Yes<br>(PD0<br>only) | Programma-<br>ble for PD0;<br>always on for<br>RESET | Yes                         | Programma-<br>ble for PD0;<br>always on for<br>RESET | Yes             |

| $V_{DD}$           | N/A       | N/A                           | N/A                                | N/A                  |                                                      |                             | N/A                                                  | N/A             |

| V <sub>SS</sub>    | N/A       | N/A                           | N/A                                | N/A                  |                                                      |                             | N/A                                                  | N/A             |

## Address Space

The eZ8 CPU accesses three distinct address spaces as follows:

- The Register File addresses access for the general purpose registers and the eZ8 CPU, peripheral and GPIO port control registers

- Program Memory addresses access for all of the memory locations having executable code and/or data

- The Data Memory addresses access for all of the memory locations containing only the data

The following sections describe these three address spaces. For more detailed information about the eZ8 CPU and its address space, refer to the eZ8 CPU Core User Manual (UM0128), available for download on www.zilog.com.

#### **Register File**

The Register File address space in the Z8 Encore! MCU is 4KB (4096 bytes). The Register File consists of two sections: control registers and general purpose registers. When instructions are executed, registers defined as source are read and registers defined as destinations are written. The architecture of the eZ8 CPU allows all general purpose registers to function as accumulators, address pointers, index registers, stack areas or scratch pad memory.

The upper 256 bytes of the 4KB Register File address space are reserved for control of the eZ8 CPU, on-chip peripherals and the I/O ports. These registers are located at addresses from F00H to FFFH. Some of the addresses within the 256 B Control Register section are reserved (unavailable). Reading from a reserved Register File address returns an undefined value. Writing to reserved Register File addresses is not recommended and produces unpredictable results.

The on-chip RAM always begins at address 000H in the Register File address space. The Z8 Encore! F083A Series devices contain up to 256 B of on-chip RAM. Reading from Register File addresses outside the available RAM addresses (and not within the Control Register address space), returns an undefined value. Writing to these Register File addresses has no effect.

#### Interrupt Request 2 Register

The Interrupt Request 2 (IRQ2) Register, shown in Table 37, stores interrupt requests for both vectored and polled interrupts. When a request is sent to the Interrupt Controller, the corresponding bit in the IRQ2 Register becomes 1. If interrupts are globally enabled (i.e., vectored interrupts), the Interrupt Controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (i.e., polled interrupts), the eZ8 CPU reads the Interrupt Request 2 Register to determine if any interrupt requests are pending.

Table 37. Interrupt Request 2 Register (IRQ2)

| Bit     | 7    | 6    | 5     | 4   | 3    | 2    | 1    | 0    |

|---------|------|------|-------|-----|------|------|------|------|

| Field   |      | Rese | erved |     | PC3I | PC2I | PC1I | PC0I |

| RESET   | 0    | 0    | 0     | 0   | 0    | 0    | 0    | 0    |

| R/W     | R/W  | R/W  | R/W   | R/W | R/W  | R/W  | R/W  | R/W  |

| Address | FC6H |      |       |     |      |      |      |      |

| Bit     | Description                                                          |  |

|---------|----------------------------------------------------------------------|--|

| [7:4]   | Reserved                                                             |  |

|         | These bits are reserved and must be programmed to 0000.              |  |

| [3:0]   | Port C pin x Interrupt Request                                       |  |

| PCxI    | 0 = No interrupt request is pending for GPIO Port C pin x.           |  |

|         | 1 = An interrupt request from GPIO Port C pin x is awaiting service. |  |

| Note: x | x indicates the specific GPIO port pin number (3–0).                 |  |

#### IRQ0 Enable High and Low Bit Registers

Table 38 indicates priority control for the IRQ0 Register. The IRQ0 Enable High and Low Bit registers, shown in Tables 39 and 40, form a priority-encoded enabling service for interrupts in the Interrupt Request 0 Register. Priority is generated by setting the appropriate bits in each register.

Table 38. IRQ0 Enable and Priority Encoding

| IRQ0ENH[x]                           | IRQ0ENL[x] | Priority | Description |  |  |  |  |  |

|--------------------------------------|------------|----------|-------------|--|--|--|--|--|

| 0                                    | 0          | Disabled | Disabled    |  |  |  |  |  |

| 0                                    | 1          | Level 1  | Low         |  |  |  |  |  |

| 1                                    | 0          | Level 2  | Nominal     |  |  |  |  |  |

| 1                                    | 1          | Level 3  | High        |  |  |  |  |  |

| Note: x indicates register bits 7–0. |            |          |             |  |  |  |  |  |

Table 39. IRQ0 Enable High Bit Register (IRQ0ENH)

| Bit     | 7        | 6     | 5     | 4    | 3    | 2     | 1   | 0      |

|---------|----------|-------|-------|------|------|-------|-----|--------|

| Field   | Reserved | T1ENH | T0ENH |      | Rese | erved |     | ADCENH |

| RESET   | 0        | 0     | 0     | 0    | 0    | 0     | 0   | 0      |

| R/W     | R/W      | R/W   | R/W   | R/W  | R/W  | R/W   | R/W | R/W    |

| Address |          |       |       | FC1H |      |       |     |        |

| Bit           | Description                                                     |

|---------------|-----------------------------------------------------------------|

| [7]           | Reserved This bit is reserved and must be programmed to 0.      |

| [6]<br>T1ENH  | Timer 1 Interrupt Request Enable High Bit                       |

| [5]<br>T0ENH  | Timer 0 Interrupt Request Enable High Bit                       |

| [4:1]         | Reserved These bits are reserved and must be programmed to 000. |

| [0]<br>ADCENH | ADC Interrupt Request Enable High Bit                           |

Table 40. IRQ0 Enable Low Bit Register (IRQ0ENL)

| Bit     | 7        | 6     | 5     | 4   | 3    | 2     | 1 | 0      |

|---------|----------|-------|-------|-----|------|-------|---|--------|

| Field   | Reserved | T1ENL | T0ENL |     | Rese | erved |   | ADCENL |

| RESET   | 0        | 0     | 0     | 0   | 0    | 0     | 0 | 0      |

| R/W     | R        | R/W   | R/W   | R/W | R/W  | R     | R | R/W    |

| Address |          |       | FC2H  |     |      |       |   |        |

| Bit           | Description                                            |

|---------------|--------------------------------------------------------|

| [7]           | Reserved                                               |

|               | This bit is reserved and must be programmed to 0.      |

| [6]<br>T1ENL  | Timer 1 Interrupt Request Enable Low Bit               |

| [5]<br>T0ENL  | Timer 0 Interrupt Request Enable Low Bit               |

| [4:1]         | Reserved                                               |

|               | These bits are reserved and must be programmed to 000. |

| [0]<br>ADCENL | ADC Interrupt Request Enable Low Bit                   |

## Watchdog Timer

The Watchdog Timer (WDT) protects from corrupted or unreliable software, power faults and other system-level problems, which may place the Z8 Encore! F083A Series devices into unsuitable operating states. The Watchdog Timer includes the following features:

- On-chip RC oscillator

- A selectable time-out response: reset or interrupt

- 24-bit programmable time-out value

#### **Operation**

The WDT is a retriggerable one-shot timer that resets or interrupts Z8 Encore! F083A Series devices when the WDT reaches its terminal count. The WDT uses a dedicated on-chip RC oscillator as its clock source. The WDT operates only in two modes: ON and OFF. Once enabled, it always counts and must be refreshed to prevent a time-out. Perform an enable by executing the WDT instruction or by setting the WDT\_AO Flash option bit. The WDT\_AO bit forces the WDT to operate immediately upon reset, even if a WDT instruction has not been executed.

The WDT is a 24-bit reloadable downcounter that uses three 8-bit registers in the eZ8 CPU register space to set the reload value. The nominal WDT time-out period is calculated by the following equation:

WDT Time-out Period (ms) =

$$\frac{\text{WDT Reload Value}}{10}$$

where the WDT reload value is the 24-bit decimal value furnished by {WDTU[7:0], WDTH[7:0], WDTL[7:0]} and the typical Watchdog Timer RC oscillator frequency is 10kHz. The Watchdog Timer cannot be refreshed after it reaches 000002H. The WDT reload value must not be set to values below 000004H. Table 58 provides information about approximate time-out delays for the minimum and maximum WDT reload values.

Table 58. Watchdog Timer Approximate Time-Out Delays

| WDT Reload Value | WDT Reload Value | Approximate Time-Out Delay (with 10kHz Typical WDT Oscillator Freque |                        |  |  |  |

|------------------|------------------|----------------------------------------------------------------------|------------------------|--|--|--|

| (Hex)            | (Decimal)        | Typical                                                              | Description            |  |  |  |

| 000004           | 4                | 400µs                                                                | Minimum time-out delay |  |  |  |

| 000400           | 1024             | 102 ms                                                               | Default time-out delay |  |  |  |

| FFFFF            | 16,777,215       | 28 minutes                                                           | Maximum time-out delay |  |  |  |

#### **ADC Data Low Bits Register**

The ADC Data Low Bits Register, shown in Table 65, contain the lower bits of the ADC output as well as an overflow status bit. Access to the ADC Data Low Bits Register is read-only. Reading the ADC Data High Byte Register latches lower bits of the ADC in the ADC Low Bits Register.

Table 65. ADC Data Low Bits Register (ADCD\_L)

| Bit     | 7   | 6   | 5 | 4        | 3  | 2 | 2 1 |  |  |  |  |  |  |

|---------|-----|-----|---|----------|----|---|-----|--|--|--|--|--|--|

| Field   | ADO | CDL |   | Reserved |    |   |     |  |  |  |  |  |  |

| RESET   | >   | X   |   |          | >  | < |     |  |  |  |  |  |  |

| R/W     | F   | ₹   |   |          | F  | ₹ |     |  |  |  |  |  |  |

| Address |     |     |   | F7       | 3H |   |     |  |  |  |  |  |  |

| Bit   | Description                                                                                                                                                                                                                          |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:6] | ADC Low Bits  00–11b = These bits are the two least significant bits of the 10-bit ADC output. These bits are undefined after a reset. The low bits are latched into this register whenever the ADC Data High Byte Register is read. |

| [5:0] | Reserved These bits are reserved and must be programmed to 000000.                                                                                                                                                                   |

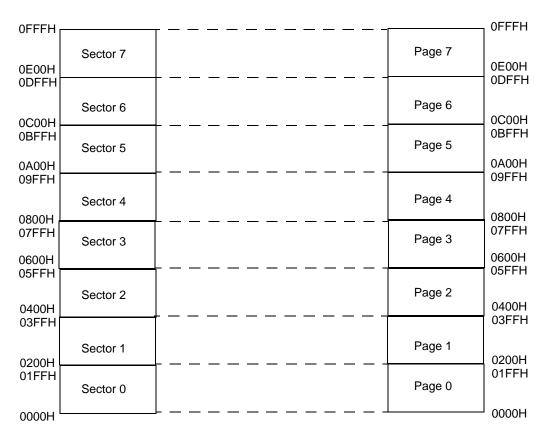

Figure 14. 4K Flash with NVDS

Table 81. Trim Bit Data Register (TRMDR)

| Bit     | 7   | 6                       | 5 | 4         | 3           | 2 | 1   | 0 |  |  |  |

|---------|-----|-------------------------|---|-----------|-------------|---|-----|---|--|--|--|

| Field   |     |                         |   | TRMDR: Tr | im Bit Data |   |     |   |  |  |  |

| RESET   | 0   | 0                       | 0 | 0         | 0           | 0 | 0 0 |   |  |  |  |

| R/W     | R/W | R/W R/W R/W R/W R/W R/W |   |           |             |   |     |   |  |  |  |

| Address |     |                         |   | FF        | 7H          |   |     |   |  |  |  |

### Flash Option Bit Address Space

The first two bytes of Flash program memory at addresses 0000H and 0001H are reserved for the user-programmable Flash option bits.

#### Flash Program Memory Address 0000H

Table 82. Flash Option Bits at Program Memory Address 0000H

| Bit       | 7                                               | 6      | 5     | 4       | 3      | 2   | 1        | 0   |  |  |

|-----------|-------------------------------------------------|--------|-------|---------|--------|-----|----------|-----|--|--|

| Field     | WDT_RES                                         | WDT_AO | OSC_S | EL[1:0] | VBO_AO | FRP | Reserved | FWP |  |  |

| RESET     | U                                               | U      | U     | U       | U      | U   | U        | U   |  |  |

| R/W       | R/W                                             | R/W    | R/W   | R/W     | R/W    | R/W | R/W      | R/W |  |  |

| Address   | dress Program Memory 0000H                      |        |       |         |        |     |          |     |  |  |

| Note: U = | Note: U = Unchanged by Reset; R/W = Read/Write. |        |       |         |        |     |          |     |  |  |

| Bit            | Description                                                                                                                                                                                                                                                                                                                                                                  |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>WDT_RES | Watchdog Timer Reset  0 = Watchdog Timer time-out generates an interrupt request. Interrupts must be globally enabled for the eZ8 CPU to acknowledge the interrupt request.  1 = Watchdog Timer time-out causes a system reset. This is the default setting for unprogrammed (erased) Flash.                                                                                 |

| [6]<br>WDT_AO  | <ul> <li>Watchdog Timer Always On</li> <li>0 = On application of system power, Watchdog Timer is automatically enabled. Watchdog Timer cannot be disabled.</li> <li>1 = Watchdog Timer is enabled on execution of the WDT instruction. Once enabled, the Watchdog Timer is disabled only by a reset. This is the default setting for unprogrammed (erased) Flash.</li> </ul> |

```

DBG \leftarrow Size[15:8]

DBG \leftarrow Size[7:0]

DBG \leftarrow 1-65536 data bytes

```

**Read Program Memory (0BH).** The read program memory command, reads data from program memory. This command is equivalent to the LDC and LDCI instructions. Data is read 1–65536 bytes at a time (65536 bytes are read by setting size to 0). If the device is not in DEBUG Mode or if the Flash read protect option bit is enabled, this command returns FFH for the data.

```

DBG ← 0BH

DBG ← Program Memory Address[15:8]

DBG ← Program Memory Address[7:0]

DBG ← Size[15:8]

DBG ← Size[7:0]

DBG → 1-65536 data bytes

```

**Write Data Memory (0CH).** The write data memory command, writes data to data memory. This command is equivalent to the LDE and LDEI instructions. Data is written 1–65536 bytes at a time (65536 bytes are written by setting size to 0). If the device is not in DEBUG Mode or if the Flash read protect option bit is enabled, the data is discarded.

```

DBG ← 0CH

DBG ← Data Memory Address[15:8]

DBG ← Data Memory Address[7:0]

DBG ← Size[15:8]

DBG ← Size[7:0]

DBG ← 1-65536 data bytes

```

• Read Data Memory (0DH)—The read data memory command, reads from data memory. This command is equivalent to the LDE and LDEI instructions. Data is read from 1 to 65536 bytes at a time (65536 bytes are read by setting size to 0). If the device is not in DEBUG Mode, this command returns FFH for the data.

```

DBG ← 0DH

DBG ← Data Memory Address[15:8]

DBG ← Data Memory Address[7:0]

DBG ← Size[15:8]

DBG ← Size[7:0]

DBG → 1-65536 data bytes

```

Read Program Memory CRC (0EH). The read program memory CRC command, computes and returns the cyclic redundancy check (CRC) of program memory using the 16-bit CRC-CCITT polynomial. If the device is not in DEBUG Mode, this command returns FFFFH for the CRC value. Unlike the other OCD read commands, there is a delay from issuing of the command until the OCD returns the data. The OCD reads program memory, calculates the CRC value and returns the result. The delay is a function of program memory size and is approximately equal to the system clock period multiplied by the number of bytes in program memory.

Table 97. OCD Control Register (OCDCTL)

| Bit   | 7       | 6     | 5      | 4 | 3        | 2 | 1 | 0   |  |  |  |

|-------|---------|-------|--------|---|----------|---|---|-----|--|--|--|

| Field | DBGMODE | BRKEN | DBGACK |   | Reserved |   |   |     |  |  |  |

| RESET | 0       | 0     | 0      | 0 | 0        | 0 | 0 | 0   |  |  |  |

| R/W   | R/W     | R/W   | R/W    | R | R        | R | R | R/W |  |  |  |

| Bit            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>DBGMODE | DEBUG Mode The device enters DEBUG Mode when this bit is 1. When in DEBUG Mode, the eZ8 CPU stops fetching new instructions. Clearing this bit causes the eZ8 CPU to restart. This bit is automatically set when a BRK instruction is decoded and breakpoints are enabled. If the Flash read protect option bit is enabled, this bit is cleared only by resetting the device. It cannot be written to 0.  0 = The Z8 Encore! F083A Series device is operating in NORMAL Mode.  1 = The Z8 Encore! F083A Series device is in DEBUG Mode. |

| [6]<br>BRKEN   | Breakpoint Enable This bit controls the behavior of the BRK instruction (Opcode 00H). By default, breakpoints are disabled and the BRK instruction behaves similar to an NOP instruction. If this bit is 1 when a BRK instruction is decoded, the DBGMODE bit of the OCDCTL register is automatically set to 1.  0 = Breakpoints are disabled.  1 = Breakpoints are enabled.                                                                                                                                                            |

| [5]<br>DBGACK  | Debug Acknowledge This bit enables the debug acknowledge feature. If this bit is set to 1, the OCD sends a Debug acknowledge character (FFH) to the host when a breakpoint occurs.  0 = Debug acknowledge is disabled.  1 = Debug acknowledge is enabled.                                                                                                                                                                                                                                                                               |

| [4:1]          | Reserved These bits are reserved and must be programmed to 0000.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| [0]<br>RST     | Reset Setting this bit to 1 resets the Z8F04xA family device. The device goes through a normal POR sequence with the exception that the On-Chip Debugger is not reset. This bit is automatically cleared to 0 at the end of reset.  0 = No effect.  1 = Reset the Flash read protect option bit device.                                                                                                                                                                                                                                 |

| -               |                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit             | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                                       |

| [5]<br>WDTEN    | Watchdog Timer Oscillator Enable  1 = Watchdog Timer Oscillator is enabled.  0 = Watchdog Timer Oscillator is disabled.                                                                                                                                                                                                                                                                                                       |

| [4]<br>POFEN    | Primary Oscillator Failure Detection Enable  1 = Failure detection and recovery of primary oscillator is enabled.  0 = Failure detection and recovery of primary oscillator is disabled.                                                                                                                                                                                                                                      |

| [3]<br>WDFEN    | Watchdog Timer Oscillator Failure Detection Enable  1 = Failure detection of Watchdog Timer Oscillator is enabled.  0 = Failure detection of Watchdog Timer Oscillator is disabled.                                                                                                                                                                                                                                           |

| [2:0]<br>SCKSEL | System Clock Oscillator Select  000 = Internal precision oscillator functions as system clock at 20MHz.  001 = Internal precision oscillator functions as system clock at 119kHz.  010 = Crystal oscillator or external RC oscillator functions as system clock.  011 = Watchdog Timer Oscillator functions as system clock.  100 = External clock signal on PB3 functions as system clock.  101 = Reserved.  110 = Reserved. |

Table 114. eZ8 CPU Instruction Summary (Continued)

| Assembly      |                      |     | ress<br>ode | Op<br>Code(s) |             |   | Fla | ags |   |   | - Fetch | Instr. |

|---------------|----------------------|-----|-------------|---------------|-------------|---|-----|-----|---|---|---------|--------|

| Mnemonic      | Symbolic Operation   | dst | src         | (Hex)         | C Z S V D H |   |     |     |   |   |         |        |

| CALL dst      | SP ← SP -2           | IRR |             | D4            | -           | - | -   | -   | - | - | 2       | 6      |

|               | @SP ← PC<br>PC ← dst | DA  |             | D6            | _           |   |     |     |   |   | 3       | 3      |

| CCF           | C ← ~C               |     |             | EF            | *           | - | -   | -   | - |   | 1       | 2      |

| CLR dst       | dst ← 00H            | R   |             | В0            | -           | - | -   | -   | - | - | 2       | 2      |

|               |                      | IR  |             | B1            |             |   |     |     |   |   | 2       | 3      |

| COM dst       | dst ← ~dst           | R   |             | 60            | _           | * | *   | 0   | _ | _ | 2       | 2      |

|               |                      | IR  |             | 61            |             |   |     |     |   |   | 2       | 3      |

| CP dst, src   | dst - src            | r   | r           | A2            | *           | * | *   | *   | _ | - | 2       | 3      |

|               |                      | r   | Ir          | А3            |             |   |     |     |   |   | 2       | 4      |

|               |                      | R   | R           | A4            |             |   |     |     |   |   | 3       | 3      |

|               |                      | R   | IR          | A5            |             |   |     |     |   |   | 3       | 4      |

|               |                      | R   | IM          | A6            |             |   |     |     |   |   | 3       | 3      |

|               |                      | IR  | IM          | A7            |             |   |     |     |   |   | 3       | 4      |

| CPC dst, src  | dst - src - C        | r   | r           | 1F A2         | *           | * | *   | *   | _ | _ | 3       | 3      |

|               |                      | r   | lr          | 1F A3         |             |   |     |     |   |   | 3       | 4      |

|               |                      | R   | R           | 1F A4         |             |   |     |     |   |   | 4       | 3      |

|               |                      | R   | IR          | 1F A5         |             |   |     |     |   |   | 4       | 4      |

|               |                      | R   | IM          | 1F A6         |             |   |     |     |   |   | 4       | 3      |

|               |                      | IR  | IM          | 1F A7         |             |   |     |     |   |   | 4       | 4      |

| CPCX dst, src | dst - src - C        | ER  | ER          | 1F A8         | *           | * | *   | *   | _ | _ | 5       | 3      |

|               |                      | ER  | IM          | 1F A9         | _           |   |     |     |   |   | 5       | 3      |

| CPX dst, src  | dst - src            | ER  | ER          | A8            | *           | * | *   | *   | _ | _ | 4       | 3      |

|               |                      | ER  | IM          | A9            | _           |   |     |     |   |   | 4       | 3      |

Note: Flags Notation:

<sup>\* =</sup> Value is a function of the result of the operation.

<sup>-</sup> = Unaffected.

X = Undefined.

<sup>0 =</sup> Reset to 0.

<sup>1 =</sup> Set to 1.

# Op Code Maps

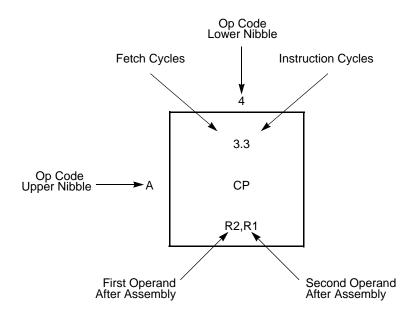

A description of the opcode map data and the abbreviations are provided in Figure 25. Table 115 lists op code map abbreviations.

Figure 25. Op Code Map Cell Description

**Table 115. Op Code Map Abbreviations**

| Abbreviation | Description                        | Abbreviation                                   | Description            |

|--------------|------------------------------------|------------------------------------------------|------------------------|

| b            | Bit position                       | IRR                                            | Indirect Register Pair |

| СС           | Condition code                     | р                                              | Polarity (0 or 1)      |

| X            | 8-bit signed index or displacement | r                                              | 4-bit Working Register |

| DA           | Destination address                | R                                              | 8-bit register         |

| ER           | Extended addressing register       | r1, R1, Ir1, Irr1, IR1,<br>rr1, RR1, IRR1, ER1 | Destination address    |

| IM           | Immediate data value               | r2, R2, Ir2, Irr2, IR2,<br>rr2, RR2, IRR2, ER2 | Source address         |

| Ir           | Indirect Working Register          | RA                                             | Relative               |

| IR           | Indirect register                  | rr                                             | Working Register Pair  |

| Irr          | Indirect Working Register Pair     | RR                                             | Register Pair          |

Table 119. Power-On Reset and Voltage Brown-Out Electrical Characteristics and Timing

|                   |                                                                                                                   | T <sub>A</sub> = ( | $T_A = -40^{\circ}C \text{ to}$<br>$T_A = 0^{\circ}C \text{ to} +70^{\circ}C$ +105°C |     |      |                  |     |       |                                                         |

|-------------------|-------------------------------------------------------------------------------------------------------------------|--------------------|--------------------------------------------------------------------------------------|-----|------|------------------|-----|-------|---------------------------------------------------------|

| Symbol            | Parameter                                                                                                         | Min                | Тур                                                                                  | Max | Min  | Typ <sup>1</sup> | Max | Units | Conditions                                              |

| T <sub>POR</sub>  | POR Digital Delay                                                                                                 |                    |                                                                                      |     | TBD  | 13               | TBD | μs    | 66 Internal Precision Oscillator cycles                 |

| T <sub>POR</sub>  | POR Digital Delay                                                                                                 |                    |                                                                                      |     | TBD  | 8                | TBD | ms    | 5000 Internal Precision Oscillator cycles               |

| T <sub>SMR</sub>  | Stop Mode<br>Recovery with<br>crystal oscillator<br>disabled                                                      |                    |                                                                                      |     | TBD  | 13               | TBD | μs    | 66 Internal Precision Oscillator cycles                 |

| T <sub>SMR</sub>  | Stop Mode<br>Recovery with<br>crystal oscillator<br>enabled                                                       |                    |                                                                                      |     | TBD  | 8                | TBD | ms    | 5000 Internal Precision Oscillator cycles               |

| $T_{VBO}$         | Voltage Brown-<br>Out Pulse Rejec-<br>tion Period                                                                 |                    |                                                                                      |     | -    | 10               | _   | μs    | V <sub>DD</sub> < V <sub>VBO</sub> to generate a Reset. |

| T <sub>RAMP</sub> | Time for V <sub>DD</sub> to<br>transition from<br>V <sub>SS</sub> to V <sub>POR</sub> to<br>ensure valid<br>Reset |                    |                                                                                      |     | 0.10 | -                | 100 | ms    |                                                         |

#### Note:

<sup>1.</sup> Data in the typical column is from characterization at 3.3 V and 0°C. These values are provided for design guidance only and are not tested in production.

**Hex Address: F05**

Table 136. Timer 0 PWM Low Byte Register (T0PWML)

| Bit     | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|-----|-----|-----|-----|-----|-----|-----|-----|

| Field   |     |     |     | PW  | ML  |     |     |     |

| RESET   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W     | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Address |     |     |     | F0  | 5H  |     |     |     |

**Hex Address: F06**

Table 137. Timer 0 Control Register 0 (T0CTL0)

| Bit     | 7       | 6    | 5    | 4        | 3   | 2      | 1   | 0   |  |  |  |

|---------|---------|------|------|----------|-----|--------|-----|-----|--|--|--|

| Field   | TMODEHI | TICO | NFIG | Reserved |     | INPCAP |     |     |  |  |  |

| RESET   | 0       | 0    | 0    | 0        | 0   | 0      | 0   | 0   |  |  |  |

| R/W     | R/W     | R/W  | R/W  | R/W      | R/W | R/W    | R/W | R/W |  |  |  |

| Address |         | F06H |      |          |     |        |     |     |  |  |  |

**Hex Address: F07**

Table 138. Timer 0 Control Register 1 (T0CTL1)

| Bit     | 7   | 6    | 5          | 4                 | 3 | 2 | 1 | 0 |  |  |

|---------|-----|------|------------|-------------------|---|---|---|---|--|--|

| Field   | TEN | TPOL | PRES TMODE |                   |   |   |   |   |  |  |

| RESET   | 0   | 0    | 0          | 0                 | 0 | 0 | 0 | 0 |  |  |

| R/W     | R/W | R/W  | R/W        | R/W R/W R/W R/W F |   |   |   |   |  |  |

| Address |     | F07H |            |                   |   |   |   |   |  |  |

**Hex Address: F08**

Table 139. Timer 1 High Byte Register (T1H)

| Bit     | 7   | 6    | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |

|---------|-----|------|-----|-----|-----|-----|-----|-----|--|--|--|

| Field   |     | TH   |     |     |     |     |     |     |  |  |  |

| RESET   | 0   | 0    | 0   | 0   | 0   | 0   | 0   | 0   |  |  |  |

| R/W     | R/W | R/W  | R/W | R/W | R/W | R/W | R/W | R/W |  |  |  |

| Address |     | F08H |     |     |     |     |     |     |  |  |  |

**Hex Addresses: FC9-FCC**

This address range is reserved.

**Hex Address: FCD**

Table 168. Interrupt Edge Select Register (IRQES)

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |  |  |

|---------|------|------|------|------|------|------|------|------|--|--|

| Field   | IES7 | IES6 | IES5 | IES4 | IES3 | IES2 | IES1 | IES0 |  |  |

| RESET   | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |  |  |

| R/W     | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |  |  |

| Address |      | FCDH |      |      |      |      |      |      |  |  |

**Hex Address: FCE**

Table 169. Shared Interrupt Select Register (IRQSS)

| Bit     | 7        | 6     | 5        | 4                   | 3 | 2 | 1 | 0 |  |  |

|---------|----------|-------|----------|---------------------|---|---|---|---|--|--|

| Field   | Reserved | PA6CS | Reserved |                     |   |   |   |   |  |  |

| RESET   | 0        | 0     | 0        | 0                   | 0 | 0 | 0 | 0 |  |  |

| R/W     | R/W      | R/W   | R/W      | R/W R/W R/W R/W R/W |   |   |   |   |  |  |

| Address |          | FCEH  |          |                     |   |   |   |   |  |  |

**Hex Address: FCF**

Table 170. Interrupt Control Register (IRQCTL)

| Bit     | 7    | 6    | 5         | 4 | 3 | 2 | 1 | 0 |  |  |

|---------|------|------|-----------|---|---|---|---|---|--|--|

| Field   | IRQE |      | Reserved  |   |   |   |   |   |  |  |

| RESET   | 0    | 0    | 0         | 0 | 0 | 0 | 0 | 0 |  |  |

| R/W     | R/W  | R    | R R R R R |   |   |   |   |   |  |  |

| Address |      | FCFH |           |   |   |   |   |   |  |  |

**Hex Address: FD7**

Table 178. Port B Output Data Register (PBOUT)

| Bit     | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |  |  |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|--|--|

| Field   | POUT7 | POUT6 | POUT5 | POUT4 | POUT3 | POUT2 | POUT1 | POUT0 |  |  |

| RESET   | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |  |  |

| R/W     | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |  |  |

| Address |       | FD7H  |       |       |       |       |       |       |  |  |

**Hex Address: FD8**

Table 179. Port C GPIO Address Register (PCADDR)

| Bit     | 7   | 6                           | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|---------|-----|-----------------------------|---|---|---|---|---|---|--|--|--|

| Field   |     | PADDR[7:0]                  |   |   |   |   |   |   |  |  |  |

| RESET   |     | 00H                         |   |   |   |   |   |   |  |  |  |

| R/W     | R/W | R/W R/W R/W R/W R/W R/W R/W |   |   |   |   |   |   |  |  |  |

| Address |     | FD8H                        |   |   |   |   |   |   |  |  |  |

**Hex Address: FD9**

**Table 180. Port C Control Registers (PCCTL)**

| Bit     | 7    | 6                           | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|---------|------|-----------------------------|---|---|---|---|---|---|--|--|--|

| Field   | PCTL |                             |   |   |   |   |   |   |  |  |  |

| RESET   |      | 00H                         |   |   |   |   |   |   |  |  |  |

| R/W     | R/W  | R/W R/W R/W R/W R/W R/W R/W |   |   |   |   |   |   |  |  |  |

| Address |      | FD9H                        |   |   |   |   |   |   |  |  |  |

**Hex Address: FDA**

Table 181. Port C Input Data Registers (PCIN)

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |  |  |

|---------|------|------|------|------|------|------|------|------|--|--|

| Field   | PIN7 | PIN6 | PIN5 | PIN4 | PIN3 | PIN2 | PIN1 | PIN0 |  |  |

| RESET   | Х    | Х    | Х    | Х    | Х    | Х    | Х    | Х    |  |  |

| R/W     | R    | R    | R    | R    | R    | R    | R    | R    |  |  |

| Address |      | FDAH |      |      |      |      |      |      |  |  |