Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | -                                                         |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 23                                                        |

| Program Memory Size        | 8KB (8K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 8x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f083asj020eg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# List of Figures

| Figure 1.  | Z8 Encore! F083A Series Block Diagram                                                                  |

|------------|--------------------------------------------------------------------------------------------------------|

| Figure 2.  | Z8F083A Series in 20-Pin SOIC, SSOP, PDIP Package                                                      |

| Figure 3.  | Z8F083A Series in 28-Pin SOIC and SSOP Packages                                                        |

| Figure 4.  | Z8F083A Series in 20-Pin QFN Package                                                                   |

| Figure 5.  | Z8F083A Series in 28-Pin QFN Package 10                                                                |

| Figure 6.  | Power-On Reset Operation                                                                               |

| Figure 7.  | Voltage Brown-Out Reset Operation                                                                      |

| Figure 8.  | GPIO Port Pin Block Diagram                                                                            |

| Figure 9.  | Interrupt Controller Block Diagram                                                                     |

| Figure 10. | Timer Block Diagram                                                                                    |

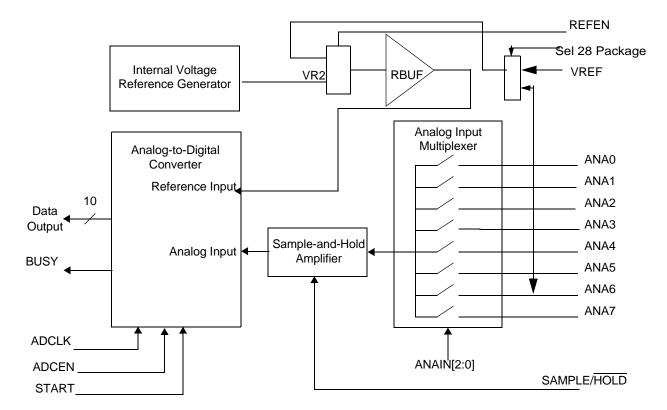

| Figure 11. | Analog-to-Digital Converter Block Diagram                                                              |

| Figure 12. | ADC Timing Diagram                                                                                     |

| Figure 13. | ADC Convert Timing                                                                                     |

| Figure 14. | 4K Flash with NVDS 111                                                                                 |

| Figure 15. | 8K Flash with NVDS 112                                                                                 |

| Figure 16. | Flash Controller Operation Flow Chart 114                                                              |

| Figure 17. | On-Chip Debugger Block Diagram                                                                         |

| Figure 18. | Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface,<br># 1 of 2                       |

| Figure 19. | Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface,<br>#2 of 2                        |

| Figure 20. | OCD Data Format                                                                                        |

| Figure 21. | Oscillator Control Clock Switching Flow Chart                                                          |

| Figure 22. | Recommended 20MHz Crystal Oscillator Configuration 158                                                 |

| Figure 23. | Connecting the On-Chip Oscillator to an External RC Network 159                                        |

| Figure 24. | Typical RC Oscillator Frequency as a Function of the External Capacitance with a 45 <b>KΩ</b> Resistor |

| Figure 25. | Op Code Map Cell Description                                                                           |

| Figure 26. | First Op Code Map                                                                                      |

## 23

# **Reset Sources**

Table 10 lists the possible sources of a system reset.

#### Table 10. Reset Sources and Resulting Reset Type

| Operating<br>Mode       | Reset Source                                           | Special Conditions                                                  |

|-------------------------|--------------------------------------------------------|---------------------------------------------------------------------|

| NORMAL or<br>HALT modes | Power-On Reset / Voltage Brown-Out.                    | Reset delay begins after supply voltage exceeds POR level.          |

|                         | WDT time-out when configured for reset.                | None.                                                               |

|                         | RESET pin assertion.                                   | All reset pulses less than four system clocks in width are ignored. |

|                         | On-Chip Debugger initiated reset (OCDCTL[0] set to 1). | System, except the On-Chip Debugger is unaffected by the reset.     |

| STOP Mode               | Power-On Reset / Voltage Brown-Out.                    | Reset delay begins after supply voltage exceeds POR level.          |

|                         | RESET pin assertion.                                   | All reset pulses less than 12 ns are ignored.                       |

|                         | DBG pin driven Low.                                    | None.                                                               |

# **Power-On Reset**

Each device in the Z8 Encore! F083A Series contains an internal POR circuit. The POR circuit monitors the digital supply voltage and holds the device in the Reset state until the digital supply voltage reaches a safe operating level. After the supply voltage exceeds the POR voltage threshold ( $V_{POR}$ ), the device is held in the Reset state until the POR counter has timed out. If the crystal oscillator is enabled by the option bits, the time-out is longer.

After the Z8 Encore! F083A Series device exits the POR state, the eZ8 CPU fetches the reset vector. Following the POR, the POR status bit in the Reset Status (RSTSTAT) Register is set to 1.

Figure 6 displays POR operation. For POR threshold voltage ( $V_{POR}$ ), see the <u>Electrical</u> <u>Characteristics</u> chapter on page 184.

reset pulse of three clock cycles in duration might trigger a reset and a reset pulse of four cycles in duration always triggers a reset.

While the RESET input pin is asserted low, the Z8 Encore! F083A Series devices remain in the Reset state. If the RESET pin is held low beyond the system reset time-out, the device exits the Reset state on the system clock rising edge following RESET pin deassertion. Following a system reset initiated by the external RESET pin, the EXT status bit in the Reset Status (RSTSTAT) Register is set to 1.

## **External Reset Indicator**

During system reset or when enabled by the GPIO logic, the RESET pin functions as an open-drain (active low) RESET mode indicator in addition to the input functionality. This reset output feature allows an Z8 Encore! F083A Series device to reset other components to which it is connected, even if that reset is caused by internal sources such as POR, VBO or WDT events. See the Port A–D Control Registers section on page 41.

After an internal Reset event occurs, the internal circuitry begins driving the **RESET** pin low. The **RESET** pin is held low by the internal circuitry until the appropriate delay listed in <u>Table 9</u> on page 22 has elapsed.

# **On-Chip Debugger Initiated Reset**

A POR is initiated using the On-Chip Debugger by setting the RST bit in the OCD Control Register. The On-Chip Debugger block is not reset, but the remainder of the chip goes through a normal system reset. The RST bit automatically clears during the system reset. Following the system reset, the POR bit in the reset status (RSTSTAT) Register is set.

# Stop Mode Recovery

The device enters the STOP Mode when the STOP instruction is executed by the eZ8 CPU. For more details about STOP Mode, see the <u>Low-Power Modes</u> chapter on page 30. During Stop Mode Recovery, the CPU is held in reset for about 66 IPO cycles if the crystal oscillator is disabled or about 5000 cycles if it is enabled.

Stop Mode Recovery does not affect the on-chip registers other than the Reset Status (RSTSTAT) Register and the Oscillator Control Register (OSCCTL). After any Stop Mode Recovery, the IPO is enabled and selected as the system clock. If another system clock source is required or IPO disabling is required, the Stop Mode Recovery code must reconfigure the oscillator control block such that the correct system clock source is enabled and selected.

The eZ8 CPU fetches the reset vector at program memory addresses 0002H and 0003H and loads that value into the program counter. Program execution begins at the reset vector

# Port A–C Input Data Registers

Reading from the Port A–C Input Data registers, shown in Table 29, returns the sampled values from the corresponding port pins. The Port A–C Input Data registers are read-only. The value returned for any unused ports is 0. Unused ports include those missing on the 8-and 28-pin packages, as well as those missing on the ADC-enabled 28-pin packages.

| Bit     | 7    | 6    | 5    | 4        | 3        | 2    | 1    | 0    |

|---------|------|------|------|----------|----------|------|------|------|

| Field   | PIN7 | PIN6 | PIN5 | PIN4     | PIN3     | PIN2 | PIN1 | PIN0 |

| RESET   | Х    | Х    | Х    | Х        | Х        | Х    | Х    | Х    |

| R/W     | R    | R    | R    | R        | R        | R    | R    | R    |

| Address |      |      |      | FD2H, FD | 6H, FDAH |      |      |      |

Table 29. Port A–C Input Data Registers (PxIN)

| Bit   | Description                                          |

|-------|------------------------------------------------------|

| [7:0] | Port Input Data                                      |

| PxIN  | Sampled data from the corresponding port pin input.  |

|       | 0 = Input data is logical 0 (Low).                   |

|       | 1 = Input data is logical 1 (High).                  |

| Note: | x indicates the specific GPIO port pin number (7–0). |

# **Interrupt Request 2 Register**

The Interrupt Request 2 (IRQ2) Register, shown in Table 37, stores interrupt requests for both vectored and polled interrupts. When a request is sent to the Interrupt Controller, the corresponding bit in the IRQ2 Register becomes 1. If interrupts are globally enabled (i.e., vectored interrupts), the Interrupt Controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (i.e., polled interrupts), the eZ8 CPU reads the Interrupt Request 2 Register to determine if any interrupt requests are pending.

| Bit           | 7                      | 6            | 5                           | 4                           | 3            | 2        | 1    | 0    |

|---------------|------------------------|--------------|-----------------------------|-----------------------------|--------------|----------|------|------|

| Field         |                        | Rese         | erved                       |                             | PC3I         | PC2I     | PC1I | PC0I |

| RESET         | 0                      | 0            | 0                           | 0                           | 0            | 0        | 0    | 0    |

| R/W           | R/W                    | R/W          | R/W                         | R/W                         | R/W          | R/W      | R/W  | R/W  |

| Address       |                        |              |                             | FC                          | 6H           |          | I    |      |

| Bit           | Descriptio             | n            |                             |                             |              |          |      |      |

| [7:4]         | Reserved<br>These bits | are reserved | d and must b                | be programm                 | ned to 0000. |          |      |      |

| [3:0]<br>PCxI | 0 = No inter           |              | t is pending                | for GPIO Po<br>Port C pin 2 | •            | service. |      |      |

| PCxI          | 0 = No inter           | rrupt reques | t is pending<br>t from GPIO | Port C pin 2                | •            | service. |      |      |

#### Table 37. Interrupt Request 2 Register (IRQ2)

# **IRQ0 Enable High and Low Bit Registers**

Table 38 indicates priority control for the IRQ0 Register. The IRQ0 Enable High and Low Bit registers, shown in Tables 39 and 40, form a priority-encoded enabling service for interrupts in the Interrupt Request 0 Register. Priority is generated by setting the appropriate bits in each register.

|                   |                    | •        | •           |

|-------------------|--------------------|----------|-------------|

| IRQ0ENH[x]        | IRQ0ENL[x]         | Priority | Description |

| 0                 | 0                  | Disabled | Disabled    |

| 0                 | 1                  | Level 1  | Low         |

| 1                 | 0                  | Level 2  | Nominal     |

| 1                 | 1                  | Level 3  | High        |

| Note: x indicates | register bits 7–0. |          |             |

Table 38. IRQ0 Enable and Priority Encoding

PWM Output High Time Ratio (%) =  $\frac{\text{Reload Value} - \text{PWM Value}}{\text{Reload Value}} \times 100$

If TPOL bit is set to 1, the ratio of the PWM output high time to the total period is represented by:

PWM Output High Time Ratio (%) =  $\frac{\text{PWM Value}}{\text{Reload Value}} \times 100$

#### **CAPTURE Mode**

In CAPTURE Mode, the current timer count value is recorded when the appropriate external timer input transition occurs. The capture count value is written to the timer PWM High and Low Byte registers. The timer input is the system clock. The TPOL bit in the Timer Control Register determines if a capture event occurs on a rising edge or a falling edge of the timer input signal.

When a capture event occurs, an interrupt is generated and the timer continues counting. The INPCAP bit in the TxCTL1 Register is set to indicate the timer interrupt because of an input capture event.

The timer continues counting up to the 16-bit reload value stored in the Timer Reload High and Low Byte registers. Upon reaching the reload value, the timer generates an interrupt and continues counting. The INPCAP bit in the TxCTL1 Register clears, indicating that the timer interrupt has not occurred because of an input capture event.

Observe the following steps to configure a timer for CAPTURE Mode and initiating the count.

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for CAPTURE Mode

- Set the prescale value

- Set the capture edge (rising or falling) for the timer input

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. Clear the timer PWM High and Low Byte registers to 0000H. Clearing these registers allows user software to determine if interrupts were generated either by a capture event or by a reload. If the PWM High and Low Byte registers still contain 0000H after the interrupt, the interrupt were generated by a reload.

Figure 11. Analog-to-Digital Converter Block Diagram

# Operation

The ADC converts the analog input,  $ANA_X$ , to a 10-bit digital representation. The equation for calculating the digital value is represented by:

ADCOutput =  $1024 \times (ANA_x \div V_{REF})$

Assuming zero gain and offset errors, any voltage outside the ADC input limits of  $AV_{SS}$  and  $V_{REF}$  returns all 0s or 1s, respectively. A new conversion is initiated by a software to the ADC Control Register's start bit.

Initiating a new conversion stops any conversion currently in progress and begins a new conversion. To avoid disrupting a conversion already in progress, the START bit is read to determine ADC operation status (i.e., busy or available).

99

# Flash Memory

The products in the Z8 Encore! F083A Series features either 4KB (4096 bytes with NVDS) or 8KB (8192 bytes with NVDS) of nonvolatile Flash memory with read/write/ erase capability. The Flash memory is programmed and erased in-circuit by either user code or through the On-Chip Debugger.

The Flash memory array is arranged in pages with 512-bytes per page. The 512-byte page is the minimum Flash block size that is erased. Each page is divided into eight rows of 64 bytes.

For program/data protection, Flash memory is also divided into sectors. In the Z8 Encore! F083A Series, each sector maps to one page for 4KB devices and two pages for 8KB devices.

The first two bytes of the Flash program memory are used as Flash option bits. For details, see *the* <u>Flash Option Bits</u> chapter on page 124.

Table 70 describes the Flash memory configuration for each device in the Z8 Encore! F083A Series. Figures 14 and 15 display the Flash memory arrangement.

| Part Number | Flash Size<br>KB (Bytes) | Flash<br>Pages | Program Memory<br>Addresses | Flash Sector<br>Size (bytes) |

|-------------|--------------------------|----------------|-----------------------------|------------------------------|

| Z8F083A     | 8 (8196)                 | 16             | 0000H–1FFFH                 | 1024                         |

| Z8F043A     | 4 (4096)                 | 8              | 0000H-0FFFH                 | 512                          |

#### Table 70. Z8 Encore! F083A Series Flash Memory Configurations

# Nonvolatile Data Storage

Z8 Encore! F083A Series devices contain a Nonvolatile Data Storage (NVDS) element of up to 100 bytes. This type of memory can perform over 100,000 write cycles.

# Operation

The NVDS is implemented by special-purpose Zilog software, which is stored in areas of program memory that are not accessible to the user. These special-purpose routines use Flash memory to store data. These routines incorporate a dynamic addressing scheme to maximize the write/erase endurance of Flash memory.

**Note:** Different members of the Z8 Encore! F083A Series feature multiple NVDS array sizes. For more details, see the <u>Z8 Encore! F083A Series Family Part Selection Guide</u> section on page 2.

# **NVDS Code Interface**

Two routines are required to access the NVDS: a write routine and a read routine. Both of these routines are accessed with a CALL instruction to a predefined address outside of program memory that is accessible to the user. Both the NVDS address and data are single-byte values. In order to not disturb the user code, these routines save the working register set before using it; therefore, 16 bytes of stack space are required to preserve the site. After finishing the call to these routines, the working register set of the user code is recovered.

During both read and write accesses to the NVDS, interrupt service is not disabled. Any interrupts that occur during NVDS execution must not disturb the working register and existing stack contents; otherwise, the array can become corrupted. Zilog recommends the user disable interrupts before executing NVDS operations.

Use of the NVDS requires 16 bytes of available stack space. The contents of the working register set are saved before calling NVDS read or write routines.

For correct NVDS operation, the Flash Frequency registers must be programmed based on the system clock frequency. See the <u>Flash Operation Timing Using the Flash Frequency</u><u>Registers</u> section on page 115.

# **Byte Read**

To read a byte from the NVDS array, user code must first push the address onto the stack. User code issues a CALL instruction to the address of the byte-read routine ( $0 \times 2000$ ). At the return from the sub-routine, the read byte resides in working register R0 and the read status byte resides in working register R1. The bit fields of this status byte are defined in Table 93. Additionally, the user code should pop the address byte off the stack.

The read routine uses 16 bytes of stack space in addition to the one byte of address pushed by the user code. Sufficient memory must be available for this stack usage.

Because of the Flash memory architecture, NVDS reads exhibit a nonuniform execution time. A read operation takes between 71  $\mu$ s and 258  $\mu$ s (assuming a 20MHz system clock). Slower system clock speeds result in proportionally higher execution times.

NVDS byte reads from invalid addresses (those exceeding the NVDS array size) return  $0 \times ff$ . Illegal read operations have a 6  $\mu$ s execution time.

The status byte returned by the NVDS read routine is zero for successful read. If the status byte is nonzero, there is a corrupted value in the NVDS array at the location being read. In this case, the value returned in R0 is the byte most recently written to the array that does not have an error.

| Bit              | 7 | 6        | 5 | 4  | 3        | 2  | 1      | 0        |

|------------------|---|----------|---|----|----------|----|--------|----------|

| Field            |   | Reserved |   | DE | Reserved | FE | IGADDR | Reserved |

| Default<br>Value | 0 | 0        | 0 | 0  | 0        | 0  | 0      | 0        |

| Table | 93. | Read | Status | Byte |

|-------|-----|------|--------|------|

|-------|-----|------|--------|------|

| Bit       | Description                                                                                                                                                                                                                   |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:5]     | <b>Reserved</b><br>These bits are reserved and must be programmed to 000.                                                                                                                                                     |

| [4]<br>DE | Data Error<br>When reading a NVDS address, if an error is found in the latest data corresponding to this<br>NVDS address, this bit is set to 1. NVDS source code steps forward until finding a valid data at<br>this address. |

| [3]       | <b>Reserved</b> This bit is reserved and must be programmed to 0.                                                                                                                                                             |

| [2]<br>FE | Flash Error<br>If a Flash error is detected, this bit is set to 1.                                                                                                                                                            |

| Debug Command           | Command<br>Byte | Enabled when not<br>in DEBUG Mode? | Disabled by Flash Read Protect<br>Option Bit |

|-------------------------|-----------------|------------------------------------|----------------------------------------------|

| Read Program Memory CRC | 0EH             | _                                  | -                                            |

| Reserved                | 0FH             | _                                  | -                                            |

| Step Instruction        | 10H             | _                                  | Disabled                                     |

| Stuff Instruction       | 11H             | _                                  | Disabled                                     |

| Execute Instruction     | 12H             | _                                  | Disabled                                     |

| Reserved                | 13H–FFH         | _                                  | -                                            |

Table 96. On-Chip Debugger Command Summary (Continued)

In the following list of OCD commands, data and commands sent from the host to the On-Chip Debugger are identified by DBG  $\leftarrow$  Command/Data. Data sent from the On-Chip Debugger back to the host is identified by DBG  $\rightarrow$  Data.

**Read OCD Revision (00H).** The read OCD revision command determines the version of the On-Chip Debugger. If OCD commands are added, removed or changed, this revision number changes.

```

DBG \leftarrow 00H

DBG \rightarrow OCDRev[15:8] (Major revision number)

DBG \rightarrow OCDRev[7:0] (Minor revision number)

```

**Read OCD Status Register (02H).** The read OCD Status Register command reads the OCDSTAT register.

```

DBG \leftarrow 02H

DBG \rightarrow OCDSTAT[7:0]

```

**Read Runtime Counter (03H).** The runtime counter counts system clock cycles in between breakpoints. The 16-bit runtime counter counts from 0000H and stops at the maximum count of FFFFH. The runtime counter is overwritten during the write memory, read memory, write register, read register, read memory CRC, step instruction, stuff instruction and execute instruction commands.

```

DBG \leftarrow 03H

DBG \rightarrow RuntimeCounter[15:8]

DBG \rightarrow RuntimeCounter[7:0]

```

Write OCD Control Register (04H). The write OCD Control Register command writes the data that follows to the OCDCTL register. When the Flash read protect option bit is enabled, the DBGMODE bit (OCDCTL[7]) is set to 1 only, it cannot be cleared to 0. To return the device to normal operating mode, the device must be reset.

```

DBG \leftarrow 04H

DBG \leftarrow OCDCTL[7:0]

```

**Read OCD Control Register (05H).** The read OCD Control Register command reads the value of the OCDCTL register.

```

DBG \leftarrow 0EH

DBG \rightarrow CRC[15:8]

DBG \rightarrow CRC[7:0]

```

**Step Instruction (10H).** The step instruction command, steps one assembly instruction at the current program counter (PC) location. If the device is not in DEBUG Mode or the Flash read protect option bit is enabled, the OCD ignores this command.

DBG  $\leftarrow$  10H

**Stuff Instruction (11H).** The stuff instruction command, steps one assembly instruction and allows specification of the first byte of the instruction. The remaining 0-4 bytes of the instruction are read from program memory. This command is useful for stepping over instructions where the first byte of the instruction has been overwritten by a breakpoint. If the device is not in DEBUG Mode or the Flash read protect option bit is enabled, the OCD ignores this command.

DBG  $\leftarrow$  11H DBG  $\leftarrow$  opcode[7:0]

**Execute Instruction (12H).** The execute instruction command allows sending an entire instruction to be executed to the eZ8 CPU. This command also steps over breakpoints. The number of bytes to send for the instruction depends on the Opcode. If the device is not in DEBUG Mode or the Flash read protect option bit is enabled, this command reads and discards one byte.

```

DBG \leftarrow 12H

DBG \leftarrow 1-5 byte opcode

```

# **On-Chip Debugger Control Register Definitions**

This section describes the features of the On-Chip Debugger Control and Status registers.

# **OCD Control Register**

The OCD Control Register controls the state of the On-Chip Debugger. This register is used to enter or exit DEBUG Mode and to enable the BRK instruction. It also resets the Z8 Encore! F083A Series device.

A reset and stop function is achieved by writing 81H to this register. A reset and Go function is achieved by writing 41H to this register. If the device is in DEBUG Mode, a run function is implemented by writing 40H to this register.

| Table 97. OCD Control Register (OCDC | ΓL) |

|--------------------------------------|-----|

|--------------------------------------|-----|

|                |                                                                      |                                                                                          | •                                             |                                                               |                                                         | ·                                        |                                                |             |

|----------------|----------------------------------------------------------------------|------------------------------------------------------------------------------------------|-----------------------------------------------|---------------------------------------------------------------|---------------------------------------------------------|------------------------------------------|------------------------------------------------|-------------|

| Bit            | 7                                                                    | 6                                                                                        | 5                                             | 4                                                             | 3                                                       | 2                                        | 1                                              | 0           |

| Field          | DBGMODE                                                              | BRKEN                                                                                    | DBGACK                                        |                                                               | Res                                                     | erved                                    |                                                | RST         |

| RESET          | 0                                                                    | 0                                                                                        | 0                                             | 0                                                             | 0                                                       | 0                                        | 0                                              | 0           |

| R/W            | R/W                                                                  | R/W                                                                                      | R/W                                           | R                                                             | R                                                       | R                                        | R                                              | R/W         |

| Bit            | Descriptio                                                           | on                                                                                       |                                               |                                                               |                                                         |                                          |                                                |             |

| [7]<br>DBGMODI | stops fetch<br>automatica<br>Flash read<br>not be writ<br>0 = The Z8 | e enters DE<br>ning new ins<br>ally set whe<br>protect opti<br>ten to 0.<br>B Encore! F( | structions. C<br>n a BRK ins<br>on bit is ena | learing this<br>truction is d<br>bled, this bi<br>device is o | bit causes<br>ecoded and<br>t is cleared<br>perating in | NORMAL N                                 | U to restart.<br>is are enabl<br>etting the de | This bit is |

| [6]<br>BRKEN   | are disable<br>when a BR<br>cally set to<br>0 = Breakp               | ntrols the bo<br>ed and the E<br>K instructio                                            | BRK instructi<br>n is decode<br>sabled.       | on behaves                                                    | similar to a                                            | code 00н). E<br>an NOP inst<br>he OCDCTL | ruction. If th                                 | is bit is 1 |

| [5]<br>DBGACK  | This bit en<br>Debug ack<br>0 = Debug                                | nowledge o<br>acknowled                                                                  | ebug acknov                                   | FH) to the he                                                 |                                                         | oit is set to 1<br>breakpoint o          |                                                | sends a     |

| [4:1]          | Reserved<br>These bits                                               | are reserve                                                                              | ed and must                                   | be program                                                    | nmed to 00                                              | 00.                                      |                                                |             |

| [0]<br>RST     | POR sequ<br>matically c<br>0 = No effe                               | ence with th<br>leared to 0<br>ect.                                                      |                                               | that the Or<br>f reset.                                       | n-Chip Deb                                              | ne device go<br>ugger is not             |                                                |             |

## Z8 Encore!<sup>®</sup> F083A Series Product Specification

igure 24. Typical RC Oscillator Frequency as a Function of the External Capacitance with a  $45 K\Omega$  Resistor

**Caution:** When operating in external RC OSCILLATOR Mode, the oscillator stops oscillating if the power supply drops below 2.7V, but before the power supply drops to the VBO threshold. The oscillator resumes oscillation when the supply voltage exceeds 2.7V.

160

| Mnemonic | Operands | Instruction                                    |

|----------|----------|------------------------------------------------|

| AND      | dst, src | Logical AND                                    |

| ANDX     | dst, src | Logical AND using extended addressing          |

| СОМ      | dst      | Complement                                     |

| OR       | dst, src | Logical OR                                     |

| ORX      | dst, src | Logical OR using extended addressing           |

| XOR      | dst, src | Logical Exclusive OR                           |

| XORX     | dst, src | Logical Exclusive OR using extended addressing |

### Table 112. Program Control Instructions

| Mnemonic | Operands        | Instruction                   |

|----------|-----------------|-------------------------------|

| BRK      |                 | On-Chip Debugger Break        |

| BTJ      | p, bit, src, DA | Bit Test and Jump             |

| BTJNZ    | bit, src, DA    | Bit Test and Jump if Non-Zero |

| BTJZ     | bit, src, DA    | Bit Test and Jump if Zero     |

| CALL     | dst             | Call Procedure                |

| DJNZ     | dst, src, RA    | Decrement and Jump Non-Zero   |

| IRET     | _               | Interrupt Return              |

| JP       | dst             | Jump                          |

| JP cc    | dst             | Jump Conditional              |

| JR       | DA              | Jump Relative                 |

| JR cc    | DA              | Jump Relative Conditional     |

| RET      | _               | Return                        |

| TRAP     | vector          | Software Trap                 |

| 1 | 74 |

|---|----|

|---|----|

| Assembly     |                                                                                                                   |         | ress<br>de | Op<br>Code(s) | Flags |   |   |      |   |   | - Fetch | Instr. |

|--------------|-------------------------------------------------------------------------------------------------------------------|---------|------------|---------------|-------|---|---|------|---|---|---------|--------|

| Mnemonic     | Symbolic Operation                                                                                                | dst src |            | (Hex)         | С     | Ζ | S | SVDH |   | Н |         |        |

| DA dst       | $dst \gets DA(dst)$                                                                                               | R       |            | 40            | *     | * | * | Х    | _ | _ | 2       | 2      |

|              |                                                                                                                   | IR      |            | 41            | _     |   |   |      |   |   | 2       | 3      |

| DEC dst      | dst ← dst - 1                                                                                                     | R       |            | 30            | _     | * | * | *    | - | - | 2       | 2      |

|              |                                                                                                                   | IR      |            | 31            | _     |   |   |      |   |   | 2       | 3      |

| DECW dst     | dst ← dst - 1                                                                                                     | RR      |            | 80            | _     | * | * | *    | _ | _ | 2       | 5      |

|              |                                                                                                                   | IRR     |            | 81            | _     |   |   |      |   |   | 2       | 6      |

| DI           | $IRQCTL[7] \leftarrow 0$                                                                                          |         |            | 8F            | _     | _ | _ | _    | _ | _ | 1       | 2      |

| DJNZ dst, RA | $dst \leftarrow dst - 1$<br>if dst $\neq 0$<br>PC $\leftarrow$ PC + X                                             | r       |            | 0A-FA         | -     | _ | _ | _    | _ | _ | 2       | 3      |

| El           | IRQCTL[7] ← 1                                                                                                     |         |            | 9F            | _     | _ | _ | _    | _ | _ | 1       | 2      |

| HALT         | HALT Mode                                                                                                         |         |            | 7F            | _     | _ | _ | -    | _ | _ | 1       | 2      |

| INC dst      | dst ← dst + 1                                                                                                     | R       |            | 20            | _     | * | * | _    | _ | _ | 2       | 2      |

|              |                                                                                                                   | IR      |            | 21            | -     |   |   |      |   |   | 2       | 3      |

|              |                                                                                                                   | r       |            | 0E-FE         | _     |   |   |      |   |   | 1       | 2      |

| INCW dst     | dst ← dst + 1                                                                                                     | RR      |            | A0            | _     | * | * | *    | _ | _ | 2       | 5      |

|              |                                                                                                                   | IRR     |            | A1            | _     |   |   |      |   |   | 2       | 6      |

| IRET         | $FLAGS \leftarrow @SP$ $SP \leftarrow SP + 1$ $PC \leftarrow @SP$ $SP \leftarrow SP + 2$ $IRQCTL[7] \leftarrow 1$ |         |            | BF            | *     | * | * | *    | * | * | 1       | 5      |

| JP dst       | $PC \gets dst$                                                                                                    | DA      |            | 8D            | -     | _ | _ | -    | _ | _ | 3       | 2      |

|              |                                                                                                                   | IRR     |            | C4            |       |   |   |      |   |   | 2       | 3      |

| JP cc, dst   | if cc is true<br>PC ← dst                                                                                         | DA      |            | 0D-FD         | -     | - | - | -    | _ | _ | 3       | 2      |

### Table 114. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 =Set to 1.

| 177 |  |

|-----|--|

|-----|--|

| Assembly             |                                                                          |         | ress<br>ode | Op<br>₋ Code(s) | Flags  |   |   |   |   | Fetch | Instr. |   |

|----------------------|--------------------------------------------------------------------------|---------|-------------|-----------------|--------|---|---|---|---|-------|--------|---|

| Mnemonic             | Symbolic Operation                                                       | dst src |             | (Hex)           | CZSVDI |   |   | Н |   |       |        |   |

| ORX dst, src         | $dst \gets dst \ OR \ src$                                               | ER      | ER          | 48              | -      | * | * | 0 | _ | _     | 4      | 3 |

|                      | -                                                                        | ER      | IM          | 49              | _      |   |   |   |   |       | 4      | 3 |

| POP dst              | dst ← @SP                                                                | R       |             | 50              | _      | _ | _ | _ | _ | _     | 2      | 2 |

|                      | $SP \leftarrow SP + 1$                                                   | IR      |             | 51              | _      |   |   |   |   |       | 2      | 3 |

| POPX dst             | dst $\leftarrow @SP$<br>SP $\leftarrow$ SP + 1                           | ER      |             | D8              | -      | _ | _ | _ | _ | _     | 3      | 2 |

| PUSH src             | $SP \leftarrow SP - 1$                                                   | R       |             | 70              | _      | _ | _ | _ | _ | _     | 2      | 2 |

| $@SP \leftarrow src$ | $@SP \leftarrow src$                                                     | IR      |             | 71              | _      |   |   |   |   |       | 2      | 3 |

|                      | -                                                                        | IM      |             | IF70            | -      |   |   |   |   |       | 3      | 2 |

|                      |                                                                          |         |             |                 |        |   |   |   |   |       |        |   |

| PUSHX src            | $SP \leftarrow SP - 1$<br>@SP ← src                                      | ER      |             | C8              | -      | - | _ | - | - | -     | 3      | 2 |

| RCF                  | C ← 0                                                                    |         |             | CF              | 0      | _ | _ | - | _ | _     | 1      | 2 |

| RET                  | $\begin{array}{l} PC \leftarrow @SP \\ SP \leftarrow SP + 2 \end{array}$ |         |             | AF              | -      | _ | _ | - | _ | _     | 1      | 4 |

| RL dst               |                                                                          | R       |             | 90              | *      | * | * | * | _ | _     | 2      | 2 |

|                      | C D7 D6 D5 D4 D3 D2 D1 D0<br>dst                                         | IR      |             | 91              | _      |   |   |   |   |       | 2      | 3 |

| RLC dst              |                                                                          | R       |             | 10              | *      | * | * | * | _ | _     | 2      | 2 |

|                      | C T D7 D6 D5 D4 D3 D2 D1 D0                                              | IR      |             | 11              | _      |   |   |   |   |       | 2      | 3 |

| RR dst               |                                                                          | R       |             | E0              | *      | * | * | * | _ | _     | 2      | 2 |

|                      | $\blacktriangleright D7 D6 D5 D4 D3 D2 D1 D0 \rightarrow C$ dst          | IR      |             | E1              | _      |   |   |   |   |       | 2      | 3 |

| RRC dst              |                                                                          | R       |             | C0              | *      | * | * | * | - | _     | 2      | 2 |

|                      | ► D7 D6 D5 D4 D3 D2 D1 D0 ► C<br>dst                                     | IR      |             | C1              | _      |   |   |   |   |       | 2      | 3 |

### Table 114. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 = Set to 1.

# **Electrical Characteristics**

The data in this chapter represents all known data prior to qualification and characterization of the F083A Series of products, and is therefore subject to change. Additional electrical characteristics may be found in the individual chapters of this document.

# **Absolute Maximum Ratings**

Stresses greater than those listed in *Table 116* may cause permanent damage to the device. These ratings are stress ratings only. Operation of the device at any condition outside those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. For improved reliability, tie unused inputs to one of the supply voltages ( $V_{DD}$  or  $V_{SS}$ ).

| Parameter                                                      | Minimum | Maximum | Units | Notes |

|----------------------------------------------------------------|---------|---------|-------|-------|

| Ambient temperature under bias                                 | 0       | +105    | °C    |       |

| Storage temperature                                            | -65     | +150    | °C    |       |

| Voltage on any pin with respect to V <sub>SS</sub>             | -0.3    | +5.5    | V     |       |

| Voltage on $V_{DD}$ pin with respect to $V_{SS}$               | -0.3    | +3.6    | V     |       |

| Maximum current on input and/or inactive output pin            | -5      | +5      | μA    |       |

| Maximum output current from active output pin                  | -25     | +25     | mA    |       |

| 20-pin Packages Maximum Ratings at 0°C to 70°C                 |         |         |       |       |

| Total power dissipation                                        |         | 430     | mW    |       |

| Maximum current into $V_{DD}$ or out of $V_{SS}$               |         | 120     | mA    |       |

| 28-pin Packages Maximum Ratings at 0°C to 70°C                 |         |         |       |       |

| Total power dissipation                                        |         | 450     | mW    |       |

| Maximum current into V <sub>DD</sub> or out of V <sub>SS</sub> |         | 125     | mA    |       |

#### Table 116. Absolute Maximum Ratings

|                   |                                  |                                  |     |     |                                     | (                |      | ,     |                                              |  |

|-------------------|----------------------------------|----------------------------------|-----|-----|-------------------------------------|------------------|------|-------|----------------------------------------------|--|

|                   |                                  | T <sub>A</sub> = 0°C to<br>+70°C |     |     | T <sub>A</sub> = -40°C to<br>+105°C |                  |      |       |                                              |  |

| Symbol            | Parameter                        | Min                              | Тур | Max | Min                                 | Тур              | Max  | Units | Conditions                                   |  |

| I <sub>TL</sub>   | Tristate Leakage<br>Current      |                                  |     |     | -5                                  | _                | +5   | μΑ    | V <sub>DD</sub> = 3.6V                       |  |

| I <sub>LED</sub>  | Controlled Cur-                  |                                  |     |     | 1.5                                 | 3                | 4.5  | mA    | See GPIO section on                          |  |

|                   | rent Drive                       |                                  |     |     | 2.8                                 | 7                | 10.5 | mA    | LED description                              |  |

|                   |                                  |                                  |     |     | 7.8                                 | 13               | 19.5 | mA    | _                                            |  |

|                   |                                  |                                  |     |     | 12                                  | 20               | 30   | mA    | _                                            |  |

| C <sub>PAD</sub>  | GPIO Port Pad<br>Capacitance     |                                  |     |     | _                                   | 8.0 <sup>2</sup> | _    | pF    | TBD                                          |  |

| C <sub>XIN</sub>  | XIN Pad Capaci-<br>tance         |                                  |     |     | -                                   | 8.0 <sup>2</sup> | -    | pF    | TBD                                          |  |

| C <sub>XOUT</sub> | XOUT Pad<br>Capacitance          |                                  |     |     | _                                   | 9.5 <sup>2</sup> | _    | pF    | TBD                                          |  |

| I <sub>PU</sub>   | Weak Pull-up<br>Current          |                                  |     |     | 50                                  | 120              | 220  | μA    | V <sub>DD</sub> = 2.7 - 3.6V                 |  |

| ICC               | Supply Current in<br>ACTIVE Mode |                                  |     |     |                                     | 8                |      | mA    | $V_{DD} = 2.7 - 3.6 V^{3,4}$                 |  |

| ICCH              | Supply Current in<br>HALT Mode   |                                  |     |     |                                     | 2                |      | mA    | $V_{DD} = 2.7 - 3.6 V^{3,4}$                 |  |

| ICCS              | Supply Current in STOP Mode      |                                  |     | 2   |                                     |                  | 8    | μA    | Without Watchdog Time running <sup>3,4</sup> |  |

|                   |                                  |                                  |     |     |                                     |                  |      |       |                                              |  |

#### Table 117. DC Characteristics (Continued)

Notes:

1. This condition excludes all pins that have on-chip pull-ups, when driven Low.

2. These values are provided for design guidance only and are not tested in production.

3. See <u>Figure 28</u> on page 187 on page 187 for HALT Mode current and <u>Figure 29</u> on page 187 for ACTIVE (Normal) Mode current. The typical values are taken from the chart at 20MHz.

4. Inputs are at V<sub>DD</sub>, AV<sub>DD</sub>, V<sub>ss</sub> or AV<sub>ss</sub> power rails and outputs are floating. Pull-up enabled inputs are driven to V<sub>DD</sub> or floating.

5. Typicals are at 3.3 V and 27°C.

186

### Hex Address: F01

#### Table 132. Timer 0 Low Byte Register (T0L)

| Bit     | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|-----|-----|-----|-----|-----|-----|-----|-----|

| Field   |     |     |     | Т   | L   |     |     |     |

| RESET   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   |

| R/W     | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Address |     |     |     | F0  | 1H  |     |     |     |

## Hex Address: F02

#### Table 133. Timer 0 Reload High Byte Register (T0RH)

| Bit     | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|-----|-----|-----|-----|-----|-----|-----|-----|

| Field   |     |     |     | TF  | RH  |     |     |     |

| RESET   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   |

| R/W     | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Address |     |     |     | F0  | 2H  |     |     |     |

## Hex Address: F03

#### Table 134. Timer 0 Reload Low Byte Register (T0RL)

| Bit     | 7    | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

|---------|------|-----|-----|-----|-----|-----|-----|-----|--|--|

| Field   | TRL  |     |     |     |     |     |     |     |  |  |

| RESET   | 1    | 1   | 1   | 1   | 1   | 1   | 1   | 1   |  |  |

| R/W     | R/W  | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| Address | F03H |     |     |     |     |     |     |     |  |  |

#### Hex Address: F04

#### Table 135. Timer 0 PWM High Byte Register (T0PWMH)

| Bit     | 7    | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

|---------|------|-----|-----|-----|-----|-----|-----|-----|--|--|

| Field   | PWMH |     |     |     |     |     |     |     |  |  |

| RESET   | 0    | 0   | 0   | 0   | 0   | 0   | 0   | 0   |  |  |

| R/W     | R/W  | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| Address | F04H |     |     |     |     |     |     |     |  |  |