# E·XFL

# STMicroelectronics - STPCI2HEYC Datasheet

Welcome to E-XFL.COM

#### Embedded - Microcontrollers - Application Specific: Tailored Solutions for Precision and Performance

# Embedded - Microcontrollers - Application Specific

represents a category of microcontrollers designed with unique features and capabilities tailored to specific application needs. Unlike general-purpose microcontrollers, application-specific microcontrollers are optimized for particular tasks, offering enhanced performance, efficiency, and functionality to meet the demands of specialized applications.

#### What Are <u>Embedded - Microcontrollers -</u> <u>Application Specific</u>?

Application enacific microcontrollars are analyzared to

#### Details

| Details                 |                                                                    |

|-------------------------|--------------------------------------------------------------------|

| Product Status          | Obsolete                                                           |

| Applications            | Graphics Controller                                                |

| Core Processor          | x86                                                                |

| Program Memory Type     | External Program Memory                                            |

| Controller Series       | STPC® Atlas                                                        |

| RAM Size                | External                                                           |

| Interface               | EBI/EMI, IDE, ISA, Local Bus, Monitor, PCMCIA, Serial, USB, Video  |

| Number of I/O           | -                                                                  |

| Voltage - Supply        | 2.45V ~ 3.6V                                                       |

| Operating Temperature   | 0°C ~ 85°C                                                         |

| Mounting Type           | Surface Mount                                                      |

| Package / Case          | 516-BBGA                                                           |

| Supplier Device Package | 516-PBGA (35x35)                                                   |

| Purchase URL            | https://www.e-xfl.com/product-detail/stmicroelectronics/stpci2heyc |

|                         |                                                                    |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- PCMCIA interface

- Support one PCMCIA 68-pin standard PC Card Socket.

- Power Management support.

- Support PCMCIA/ATA specifications.

- Support I/O PC Card with pulse-mode interrupts.

# USB Interface

- USB 1.1 compatible.

- Open HCI 1.0 compliant.

- User configurable RootHub.

- Support for both LowSpeed and HighSpeed USB devices.

- No bi-directionnal or Tri-state busses.

- No level sensitive latches.

- System Management Interrupt pin support

- Hooks for legacy device support.

- Keyboard interface

- Fully PC/AT+ compatible

- Mouse interface

- Fully PS/2 compatible

- Serial interface

- 16550 compatible

- Programmable word length, stop bits, parity.

- 16-bit programmable baud rate generator.

**ExCA** is a trademark of PCMCIA / JEIDA.

- Interrupt generator.

- Loop-back mode.

- 8-bit scratch register.

- Two 16-bit FIFOs.

- Two DMA handshake lines.

- Parallel port

- All IEEE Standard 1284 protocols supported: Compatibility, Nibble, Byte, EPP, and ECP modes.

- 16 bytes FIFO for ECP.

# Power Management

- Four power saving modes: On, Doze, Standby, Suspend.

- Programmable system activity detector

- Supports Intel & Cyrix SMM and APM.

- Supports STOPCLK.

- Supports IO trap & restart.

- Independent peripheral time-out timer to monitor hard disk, serial & parallel port.

- 128K SM\_RAM address space from 0xA0000 to 0xB0000

- JTAG

- Boundary Scan compatible IEEE1149.1.

- Scan Chain control.

- Bypass register compatible IEEE1149.1.

- ID register compatible IEEE1149.1.

- RAM BIST control.

PanelLink is a trademark of SiliconImage, Inc

**47**/

# **Table of Contents**

| 6.6. DEBUG METHODOLOGY 10     | 3 |

|-------------------------------|---|

| 6.6.1. Power Supplies 10      |   |

| 6.6.2. Boot sequence          |   |

| 6.6.3. ISA mode               |   |

| 6.6.4. Local Bus mode 10-     | 4 |

| 6.6.5. Summary 10-            | 4 |

| 6.6.6. PCMCIA mode            |   |

| 7 ORDERING DATA               | 8 |

| 7.1. ORDERING CODES           | 8 |

| 7.2 AVAILABLE PART NUMBERS 10 | 8 |

| 8 REVISION HISTORY            | 9 |

controls for 3.3V suspend with Modem Ring Resume Detection.

The STPC Atlas implements a multi-function parallel port. The standard PC/AT compatible logical address assignments for LPT1, LPT2 and LPT3 are supported. It can be configured for any of the following three modes and supports the IEEE Standard 1284 parallel interface protocol standards, as follows:

- Compatibility Mode (Forward channel, standard)

- Nibble Mode (Reverse channel, PC compatible)

- Byte Mode (Reverse channel, PS/2 compatible)

The General Purpose Input/Output (GPIO) interface provides a 16-bit I/O facility, using 16 dedicated device pins. It is organised using two blocks of 8-bit Registers, one for lines 0 to 7, the other for lines 8 to 15.

Each GPIO port can be configured as an input or an output simply by programming the associated port direction control register. All GPIO ports are configured as inputs at reset, which also latches the input levels into the Strap Registers. The input states of the ports are thus recorded automatically at reset, and this can be used as a strap register anywhere in the system.

## **1.4. FEATURE MULTIPLEXING**

The STPC Atlas BGA package has 516 balls. This however is not sufficient for all of the integrated functions available; some features therefore share the same balls and cannot thus be used at the same time. The STPC Atlas configuration is done by 'strap options'. This is a set of pull-up or pulldown resistors on the memory data bus, checked on reset, which auto-configure the STPC Atlas.

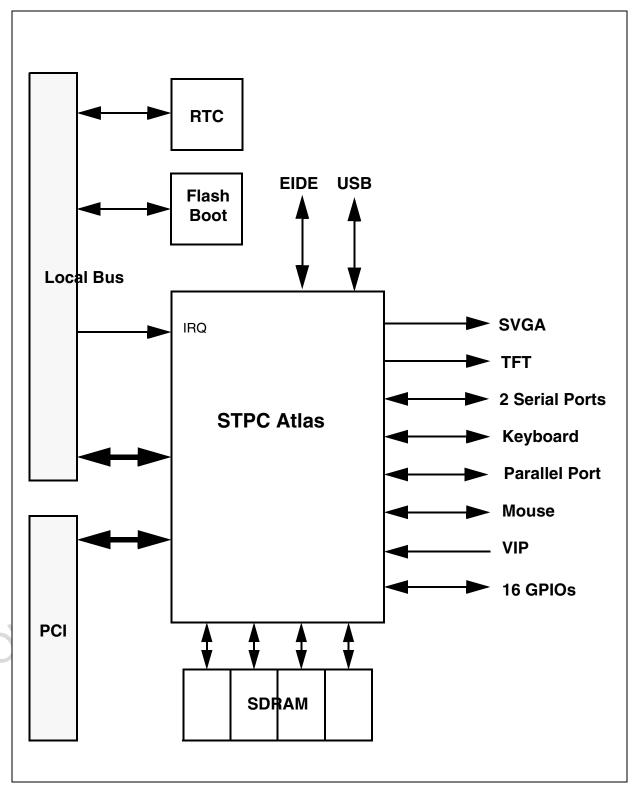

There 3 multiplexed functions are the external ISA bus, the Local Bus and the PCMCIA interface.

#### **1.5. POWER MANAGEMENT**

The STPC Atlas core is compliant with the Advanced Power Management (APM) specification to provide a standard method by which the BIOS can control the power used by personal computers. The Power Management Unit (PMU) module controls the power consumption, providing a comprehensive set of features that power and controls the usage supports compliance with the United States Environmental Protection Agency's Energy Star Computer Program. The PMU provides the following hardware structures to assist the software in managing the system power consumption:

- System Activity Detection.

- 3 power-down timers detecting system inactivity: - Doze timer (short durations).

- Stand-by timer (medium durations).

- Suspend timer (long durations).

- House-keeping activity detection.

- House-keeping timer to cope with short bursts of house-keeping activity while dozing or in stand-by state.

- Peripheral activity detection.

- Peripheral timer detecting peripheral inactivity

- SUSP# modulation to adjust the system performance in various power down states of the system including full power-on state.

- Power control outputs to disable power from different planes of the board.

Lack of system activity for progressively longer periods of time is detected by the three power down timers. These timers can generate SMI interrupts to CPU so that the SMM software can put the system in decreasing states of power consumption. Alternatively, system activity in a power down state can generate an SMI interrupt to allow the software to bring the system back up to full power-on state. The chip-set supports up to three power down states described above; these correspond to decreasing levels of power savings.

Power down puts the STPC Atlas into suspend mode. The processor completes execution of the current instruction, any pending decoded instructions and associated bus cycles. During the suspend mode, internal clocks are stopped. Removing power-down, the processor resumes instruction fetching and begins execution in the instruction stream at the point it had stopped. Because of the static nature of the core, no internal data is lost.

## 1.6. JTAG

JTAG stands for Joint Test Action Group and is the popular name for IEEE Std. 1149.1, Standard Test Access Port and Boundary-Scan Architec-ture. This built-in circuitry is used to assist in the test, maintenance and support of functional circuit blocks. The circuitry includes a standard interface through which instructions and test data are communicated. A set of test features is defined, including a boundary-scan register so that a component is able to respond to a minimum set of test instructions.

# Table 2-2. Definition of Signal Pins

| Signal Name                                        | Dir                                                                                                                | Buffer Type <sup>1</sup> | Description                            | Qty |

|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|--------------------------|----------------------------------------|-----|

|                                                    |                                                                                                                    |                          |                                        |     |

| USB INTERFACE                                      |                                                                                                                    | TLCHTU_TC                | Over Current Detect                    | 1   |

| USBDPLS[0] <sup>1</sup>                            | -                                                                                                                  |                          |                                        |     |

| USBDMNS[0] <sup>1</sup>                            | I/O                                                                                                                | USBDS_2V5                | Universal Serial Bus Port 0            | 2   |

| USBDPLS[1] <sup>1</sup><br>USBDMNS[1] <sup>1</sup> | I/O                                                                                                                | USBDS_2V5                | Universal Serial Bus Port 1            | 2   |

| POWERON <sup>1</sup>                               | 0                                                                                                                  | BT4CRP                   | USB power supply lines                 | 1   |

| SERIAL CONTROLL                                    |                                                                                                                    |                          |                                        |     |

| CTS0#, CTS1#                                       |                                                                                                                    | TLCHT_FT                 | Clear to send, MSR[4] status bit       | 2   |

| DCD0#, DCD1#                                       |                                                                                                                    | TLCHT_FT                 | Data Carrier detect, MSR[7] status bit | 2   |

| DCD0#, DCD1#<br>DSR0#, DSR1#                       |                                                                                                                    | TLCHT_FT                 |                                        | 2   |

| -                                                  |                                                                                                                    | _                        | Data set ready, MSR[5] status bit.     |     |

| DTR0#, DTR1#                                       | 0                                                                                                                  | BD4STRP_TC               | Data terminal ready, MSR[0] status bit | 2   |

| RI0#, RI1#                                         |                                                                                                                    | TLCHT_FT                 | Ring indicator, MSR[6] status bit      | 2   |

|                                                    | SO#, RTS1# O BD4STRP_TC Request to send, MSR[1] status bit   (D0, RXD1 I TLCHT_FT Receive data, Input Serial Input |                          |                                        |     |

|                                                    |                                                                                                                    |                          |                                        | 2   |

| TXD0, TXD1                                         | 0                                                                                                                  | BD4STRP_TC               | Transmit data, Serial Output           | 2   |

| KEYBOARD & MOU                                     | SE IN                                                                                                              | TERFACE                  |                                        |     |

| KBCLK                                              |                                                                                                                    | BD4STRP_TC               | Keyboard Clock Line                    | 1   |

| KBDATA                                             |                                                                                                                    | BD4STRP_TC               | Keyboard Data Line                     | 1   |

| MCLK                                               |                                                                                                                    | BD4STRP_TC               | Mouse Clock Line                       | 1   |

| MDATA                                              |                                                                                                                    | BD4STRP TC               | Mouse Data Line                        | 1   |

|                                                    | 1/0                                                                                                                |                          |                                        |     |

| PARALLEL PORT                                      |                                                                                                                    |                          |                                        |     |

| PE                                                 |                                                                                                                    | BD14STARP_FT             | Paper End                              | 1   |

| SLCT                                               | I                                                                                                                  | BD14STARP_FT             | SELECT                                 | 1   |

| BUSY#                                              | I                                                                                                                  | BD14STARP_FT             | BUSY                                   | 1   |

| ERR#                                               | I                                                                                                                  | BD14STARP_FT             | ERROR                                  | 1   |

| ACK#                                               | I                                                                                                                  | BD14STARP_FT             | Acknowledge                            | 1   |

| PDIR#                                              | 0                                                                                                                  | BD14STARP_FT             | Parallel Device Direction              | 1   |

| STROBE#                                            | 0                                                                                                                  | BD14STARP_FT             | PCS / STROBE#                          | 1   |

| INIT#                                              | 0                                                                                                                  | BD14STARP_FT             | INIT                                   | 1   |

| AUTOFD#                                            | 0                                                                                                                  | BD14STARP_FT             | Automatic Line Feed                    | 1   |

| SLCTIN#                                            | 0                                                                                                                  | BD14STARP_FT             | SELECT IN                              | 1   |

| PPD[7:0]                                           | I/O                                                                                                                | BD14STARP_FT             | Data Bus                               | 8   |

|                                                    |                                                                                                                    |                          |                                        |     |

| GPIO SIGNALS                                       |                                                                                                                    | <u> </u>                 |                                        | I   |

| GPIO[15:0]                                         | I/O                                                                                                                | BD4STRP_FT               | General Purpose IOs                    | 16  |

| JTAG                                               |                                                                                                                    |                          |                                        |     |

| TCLK                                               |                                                                                                                    | TLCHT_FT                 | Test Clock                             | l 1 |

| TRST                                               |                                                                                                                    |                          | Test Reset                             |     |

|                                                    |                                                                                                                    | TLCHT_FT                 |                                        | 1   |

| TDI                                                |                                                                                                                    | TLCHTD_FT                | Test Data Input                        |     |

| TMS                                                |                                                                                                                    | TLCHT_FT                 | Test Mode Set                          | 1   |

| TDO                                                | 0                                                                                                                  | BT8TRP_TC                | Test Data output                       | 1   |

| MISCELLANEOUS                                      |                                                                                                                    |                          |                                        |     |

| SCAN_ENABLE                                        |                                                                                                                    | TLCHTD_FT                | Test Pin - Reserved                    | 1   |

|                                                    | for h                                                                                                              | uffer type description   |                                        | I . |

**IOCHRDY** *IO Channel Ready.* IOCHRDY is the IO channel ready signal of the ISA bus and is driven as an output in response to an ISA master cycle targeted to the host bus or an internal register of the STPC Atlas. The STPC Atlas monitors this signal as an input when performing an ISA cycle on behalf of the host CPU, DMA master or refresh. ISA masters which do not monitor IOCHRDY are not guaranteed to work with the STPC Atlas since the access to the system memory can be considerably delayed due to CRT refresh or a write back cycle.

ALE Address Latch Enable. This is the address latch enable output of the ISA bus and is asserted by the STPC Atlas to indicate that LA23-17, SA19-0, AEN and SBHE# signals are valid. The ALE is driven high during refresh, DMA master or an ISA master cycles by the STPC Atlas. ALE is driven low after reset.

**BHE#** System Bus High Enable. This signal, when asserted, indicates that a data Byte is being transferred on SD15-8 lines. It is used as an input when an ISA master owns the bus and is an output at all other times.

**MEMR#** *Memory Read.* This is the memory read command signal of the ISA bus. It is used as an input when an ISA master owns the bus and is an output at all other times.

The MEMR# signal is active during refresh.

**MEMW#** *Memory Write.* This is the memory write command signal of the ISA bus. It is used as an input when an ISA master owns the bus and is an output at all other times.

**SMEMR#** System Memory Read. The STPC Atlas generates SMEMR# signal of the ISA bus only when the address is below one MByte or the cycle is a refresh cycle.

**SMEMW#** System Memory Write. The STPC Atlas generates SMEMW# signal of the ISA bus only when the address is below one MByte.

**IOR#** *I/O Read.* This is the IO read command signal of the ISA bus. It is an input when an ISA master owns the bus and is an output at all other times.

**IOW#** *I/O Write.* This is the IO write command signal of the ISA bus. It is an input when an ISA master owns the bus and is an output at all other times.

**MASTER#** Add On Card Owns Bus. This signal is active when an ISA device has been granted bus ownership.

**MCS16#** *Memory Chip Select16.* This is the decode of LA23-17 address pins of the ISA address bus without any qualification of the command signal lines. MCS16# is always an input. The STPC Atlas ignores this signal during IO and refresh cycles.

**IOCS16#** *IO Chip Select16.* This signal is the decode of SA15-0 address pins of the ISA address bus without any qualification of the command signals. The STPC Atlas does not drive IOCS16# (similar to PC-AT design). An ISA master access to an internal register of the STPC Atlas is executed as an extended 8-bit IO cycle.

**REF#** *Refresh Cycle.* This is the refresh command signal of the ISA bus. It is driven as an output when the STPC Atlas performs a refresh cycle on the ISA bus. It is used as an input when an ISA master owns the bus and is used to trigger a refresh cycle.

The STPC Atlas performs a pseudo hidden refresh. It requests the host bus for two host clocks to drive the refresh address and capture it in external buffers. The host bus is then relinquished while the refresh cycle continues on the ISA bus.

**AEN** Address Enable. Address Enable is enabled when the DMA controller is the bus owner to indicate that a DMA transfer will occur. The enabling of the signal indicates to IO devices to ignore the IOR#/IOW# signal during DMA transfers.

**IOCHCK#** *IO Channel Check.* IO Channel Check is enabled by any ISA device to signal an error condition that can not be corrected. NMI signal becomes active upon seeing IOCHCK# active if the corresponding bit in Port B is enabled.

**GPIOCS#** *I/O General Purpose Chip Select* 1. This output signal is used by the external latch on ISA bus to latch the data on the SD[7:0] bus. The latch can be use by PMU unit to control the external peripheral devices to power down or any other desired function.

**RTCRW#** *Real Time Clock RW#.* This pin is used as RTCRW#. This signal is asserted for any I/O write to port 71h.

**RTCDS#** *Real Time Clock DS.* This pin is used as RTCDS#. This signal is asserted for any I/O read to port 71h. Its polarity complies with the DS pin of the MT48T86 RTC device when configured with Intel timings.

**RTCAS** *Real time clock address strobe.* This signal is asserted for any I/O write to port 70h.

CTS0#, CTS1# Input Clear to send.

RTS0#, RTS1# Output Request to send.

DTR0#, DTR1# Output Data terminal read.

2.2.14. KEYBOARD/MOUSE INTERFACE

**KBCLK**, *Keyboard Clock line*. Keyboard data is latched by the controller on each negative clock edge produced on this pin. The keyboard can be disabled by pulling this pin low by software control.

**KBDATA**, *Keyboard Data Line.* 11-bits of data are shifted serially through this line when data is being transferred. Data is synchronised to KBCLK.

**MCLK**, *Mouse Clock line*. Mouse data is latched by the controller on each negative clock edge produced on this pin. The mouse can be disabled by pulling this pin low by software control.

**MDATA,** *Mouse Data Line.* 11-bits of data are shifted serially through this line when data is being transferred. Data is synchronised to MCLK.

2.2.15. PARALLEL PORT

**PE** Paper End. Input status signal from printer.

**SLCT** *Printer Select.* Printer selected input.

**BUSY#** *Printer Busy.* Input status signal from printer.

**ERR#** *Error*. Input status signal from printer.

**ACK#** Acknowledge. Input status signal from printer.

**PDDIR#** *Parallel Device Direction.* Bidirectional control line output.

**STROBE#** *PCS/Strobe#.* Data transfer strobe line to printer.

#### Table 2-4. Multiplexed Signals (on the same pin)

**INIT#** *Initialize Printer.* This output sends an initialize command to the connected printer.

**AUTOFD#** *Automatic Line feed.* This output sends a command to the connected printer to automatically generate line feed on received carriage returns.

SLCTIN# Select In. Printer select output.

**PPD[7-0]** *Parallel Port Data Lines* Data transfer lines to printer. Bidirectional depending on modes.

2.2.16. MISCELLANEOUS

**SPKRD** Speaker Drive. This is the output to the speaker and is the AND of the counter 2 output with bit 1 of Port 61h and drives an external speaker driver. This output should be connected to a 7407 type high voltage driver.

**SCAN\_ENABLE** *Reserved.* This pin is reserved for Test and Miscellaneous functions. It has to be set to '0' or connected to ground in normal operation.

2.2.17. **COL\_SEL** Colour Select. JTAG INTERFACE

TCLK Test clock

**TDI** Test data input

**TMS** *Test mode input*

**TDO** Test data output

TRST Test reset input

#### 2.3 SIGNAL DETAIL

The muxing between ISA, LOCAL BUS and PCMCIA is performed by external strap options.

The resulting interface is then dynamically muxed with the IDE Interface.

| IDE Pin Name | ISA Pin Name   | PCMCIA Pin Names | Local Bus Pin Name |

|--------------|----------------|------------------|--------------------|

| DIORDY       | IOCHRDY        | -                |                    |

| DA[2]        | LA[19]         | = 0              |                    |

| DA[1:0]      | LA[18:17]      | A[25:24]         |                    |

| SCS3,SCS1    | LA[23:22]      | A[23:22]         |                    |

| PCS3,PCS1    | LA[21:20]      | A[21:20]         |                    |

| DD[15]       | RMRTCCS#       | ROMCS#           |                    |

| DD[14]       | KBCS#          | Hi-Z             |                    |

| DD[13:12]    | RTCRW#, RTCDS# | Hi-Z             |                    |

| DD[11:0]     | SA[19:8]       | A[19:8]          |                    |

# Table 2-5. Signal value on Reset

| Signal Name                       | SYSRSTI# active | SYSRSTI# inactive<br>SYSRSTO# active | release of SYSRSTO#           |

|-----------------------------------|-----------------|--------------------------------------|-------------------------------|

| CS#[0]                            | High            | Ļ                                    |                               |

| MA[10:0], BA[0]                   | 0x00            |                                      | SDRAM init sequence:          |

| RAS#[1:0], CAS#[1:0]              | High            |                                      | Write Cycles                  |

| MWE#, DQM[7:0]                    | High            |                                      | White Cycles                  |

| MD[63:0]                          | Input           |                                      |                               |

| PCI INTERFACE                     |                 |                                      | •                             |

| AD[31:0]                          | 0x0000          |                                      |                               |

| CBE[3:0], PAR                     | Low             |                                      | First prefetch cycles         |

| FRAME#, TRDY#, IRDY#              | Input           |                                      | when not in Local Bus mode.   |

| STOP#, DEVSEL#                    | Input           |                                      | when not in Local Dus mode.   |

| PERR#, SERR#                      | Input           |                                      |                               |

| PCI_GNT#[2:0]                     | High            |                                      | •                             |

| ISA BUS INTERFACE                 |                 |                                      |                               |

| ISAOE#                            | High            |                                      | Low                           |

| RMRTCCS#                          | Hi-Z            |                                      |                               |

| LA[23:17]                         | Unknown         | 0x00                                 | First prefetch cycles         |

| SA[19:0]                          | 0xFFFXX         | 0xFFF03                              | when in ISA or PCMCIA mode.   |

| SD[15:0]                          | Unknown         | 0xFF                                 | Address start is 0xFFFFF0     |

| BHE#, MEMR#                       | Unknown         | High                                 |                               |

| MEMW#, SMEMR#, SMEMW#, IOR#, IOW# | Unknown         | High                                 | L                             |

| REF#                              | Unknown         | High                                 |                               |

| ALE, AEN                          | Low             |                                      |                               |

| DACK_ENC[2:0]                     | Input           |                                      | 0x04                          |

| TC                                | Input           |                                      | Low                           |

| GPIOCS#                           | Hi-Z            |                                      | High                          |

| RTCDS#, RTCRW#, KBCS#             | Hi-Z            |                                      | -                             |

| RTCAS                             | Unknown         | Low                                  |                               |

| PCMCIA INTERFACE                  |                 |                                      |                               |

| RESET                             | Unknown         | High                                 |                               |

| A[23:0]                           | Unknown         | 0x00                                 | First prefetch cycles         |

| D[15:0]                           | Unknown         | 0xFF                                 | using RMRTCCS#                |

| IORD#, IOWR#, OE#                 | Unknown         | High                                 |                               |

| WE#, REG#                         | High            |                                      |                               |

| CE2#, CE1#, VCC5_EN, VCC3_EN      | High            |                                      |                               |

| VPP_PGM, VPP_VCC                  | Low             |                                      |                               |

| LOCAL BUS INTERFACE               |                 |                                      |                               |

| PA[24:0]                          | Unknown         |                                      |                               |

| PD[15:0]                          | Unknown         | 0xFF                                 | -<br>First and fatale south a |

| PRD#                              | Unknown         | High                                 | First prefetch cycles         |

| PBE#[1:0], FCS0#, FCS_0H#         | High            |                                      | -                             |

| FCS_0L#, FCS1#, FCS_1H#, FCS_1L#  | High            |                                      | 1                             |

| PWR#, IOCS#[7:0]                  | High            |                                      |                               |

| IDE CONTROLLER                    | 1               |                                      |                               |

| DD[15:0]                          | 0xFF            |                                      |                               |

| DA[2:0]                           | Unknown         | Low                                  |                               |

| PCS1, PCS3, SCS1, SCS3            | Unknown         | Low                                  |                               |

| PDACK#, SDACK#                    | High            |                                      |                               |

| PDIOR#, PDIOW#, SDIOR#, SDIOW#    | High            |                                      |                               |

| VGA CONTROLLER                    | -               |                                      |                               |

| RED, GREEN, BLUE                  | Black           |                                      |                               |

| TED, GITELIN, DEOL                |                 |                                      |                               |

# Table 2-6. Pinout

| Pin#      | Pin Name                  |

|-----------|---------------------------|

| Y3        | CS#[2]/MA[11]             |

| Y4        | CS#[3]/MA[12]/BA[1]       |

| T2        | DQM[0]                    |

| T4        | DQM[1]                    |

| Y5        | DQM[2]                    |

| AA2       | DQM[3]                    |

| Т3        | DQM[4]                    |

| T5        | DQM[5]                    |

| AA1       | DQM[6]                    |

| AA3       | DQM[7]                    |

|           |                           |

| B3        | AD[0]                     |

| A3        | AD[1]                     |

| C4        | AD[2]                     |

| B4        | AD[3]                     |

| A4        | AD[4]                     |

| D5        | AD[5]                     |

| C5        | AD[6]                     |

| B5        | AD[7]                     |

| A5        | AD[8]                     |

| D6        | AD[9]                     |

| C6        | AD[10]                    |

| B6        | AD[11]                    |

| A6        | AD[12]                    |

| E7        | AD[13]                    |

| D7        | AD[14]                    |

| C7        | AD[15]                    |

| A9        | AD[16]                    |

| E10       | AD[17]                    |

| C10       | AD[18]                    |

| B10       | AD[19]                    |

| A10       | AD[20]                    |

| E11       | AD[21]                    |

| D11       | AD[22]                    |

| C11       | AD[23]                    |

| A11       | AD[24]                    |

| E12       | AD[25]                    |

| D12       | AD[26]                    |

| C12       | AD[27]                    |

| B12       | AD[28]                    |

| A12       | AD[29]                    |

| E13       | AD[30]                    |

| D13       | AD[31]                    |

| E6        | CBE[0]                    |

| B7        | CBE[1]                    |

| B9        | CBE[2]                    |

| B11       | CBE[3]                    |

| C9        | FRAME#                    |

| E9        | TRDY#                     |

| D9        | IRDY#                     |

|           | nis signal is multiplexed |

| see Table | e 2-4                     |

|           |                           |

## Table 2-6. Pinout

| Pin#       | Pin Name                     |

|------------|------------------------------|

| B8         | STOP#                        |

| A8         | DEVSEL#                      |

| A7         | PAR                          |

| D8         | PERR#                        |

| E8         | SERR#                        |

| C8         | LOCK#                        |

| C14        | PCI_REQ#[0]                  |

| B14        | PCI_REQ#[1]                  |

| A14        | PCI_REQ#[2]                  |

| A13        | PCI_GNT#[0]                  |

| B13        | PCI_GNT#[1]                  |

| C13        | PCI_GNT#[2]                  |

|            |                              |

| C20        | LA[17] <sup>1</sup>          |

| B21        | LA[18] <sup>1</sup>          |

| B20        | LA[19] <sup>1</sup>          |

| E19        | LA[19]                       |

| E19<br>E18 | LA[20]                       |

| C21        | LA[22] <sup>1</sup>          |

| D19        | LA[22]                       |

| P22        | SA[0] <sup>1</sup>           |

|            |                              |

| P23        | SA[1] <sup>1</sup>           |

| P24        | SA[2] <sup>1</sup>           |

| P25        | SA[3]                        |

| P26        | SA[4] <sup>1</sup>           |

| N26        | SA[5]                        |

| N25        | SA[6] <sup>1</sup>           |

| N24        | SA[7]                        |

| N23        | SA[8]                        |

| N22        | SA[9] <sup>1</sup>           |

| M26        | SA[10]                       |

| M25        | SA[11] <sup>1</sup>          |

| M24        | SA[12]                       |

| M23        | SA[13] <sup>1</sup>          |

| M22        | SA[14] <sup>1</sup>          |

| L26        | SA[15] <sup>1</sup>          |

| L25        | SA[16] <sup>1</sup>          |

| L24        | SA[17] <sup>1</sup>          |

| L23        | SA[18] <sup>1</sup>          |

| L22        | SA[19] <sup>1</sup>          |

| K24        | SD[0] <sup>1</sup>           |

| J26        | SD[1] <sup>1</sup>           |

| J25        | SD[2] <sup>1</sup>           |

| J24        | SD[3] <sup>1</sup>           |

| K23        | SD[4] <sup>1</sup>           |

| K22        | SD[5] <sup>1</sup>           |

| H26        | SD[6] <sup>1</sup>           |

| H25        | SD[7] <sup>1</sup>           |

| H24        | SD[7]<br> SD[8] <sup>1</sup> |

| G26        | SD[9] <sup>1</sup>           |

|            | his signal is multiplexed    |

| see Tab    |                              |

| See 1 ab   | 10 L-4                       |

38/108

# 3.1 STRAP OPTION

# **REGISTER DESCRIPTION**

3.1.1. STRAP REGISTER 0

This register is read only.

| STRAP0 |                                                                         |       | Access = 0022 | 2h/0023h |       | Re    | egoffset =04Ah |

|--------|-------------------------------------------------------------------------|-------|---------------|----------|-------|-------|----------------|

| 7      | 6                                                                       | 5     | 4             | 3        | 2     | 1     | 0              |

| MD[7]  | MD[6]                                                                   | MD[9] | MD[8]         | RSV      | MD[5] | MD[4] | MD[17]         |

|        | This register defaults to the values sampled on the MD pins after reset |       |               |          |       |       |                |

| Bit Number Sampled | Mnemonic      | Description                                                                                                                                                                                                                              |  |

|--------------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Bits 7-6           | MD[7:6]       | PCICLK PLL set-up: The value sampled on MD[7:6] controls the PC<br>PLL programming according to the PCICLK frequency.<br>MD7 MD6<br>0 0 PCICLK frequency between 16 & 32 MHz<br>0 1 PCICLK frequency between 32 & 64 MHz<br>1 X Reserved |  |

| Bits 5-4           | MD[9:8]       | Mode selection:MD9 MD800 ISA mode: ISA enabled, PCMCIA & Local Bus disabled01 PCMCIA mode: PCMCIA enabled, ISA & Local Bus disabled10 Local Bus mode: Local Bus enabled, ISA & PCMCIA disabled11 Reserved                                |  |

| Bit 3              | Rsv           | Reserved                                                                                                                                                                                                                                 |  |

| Bit 2              | MD[5]         | Host Memory synchronization. This bit reflects the value sampled on [MD5] and controls the MCLK/HCLK synchronization.<br>0: MCLK and HCLK not synchronized<br>1: MCLK and HCLK synchronized.                                             |  |

| Bits 1-0           | MD[4], MD[17] | PCICLK division: These bits reflect the values sampled on [MD4] and<br>MD[17] to select the PCICLK frequency.<br>MD4 MD17<br>0 X PCI Clock output = HCLK / 4<br>1 0 PCI Clock output = HCLK / 3<br>1 1 PCI Clock output = HCLK / 2       |  |

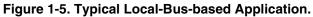

# 4.5. AC CHARACTERISTICS

This section lists the AC characteristics of the STPC interfaces including output delays, input setup requirements, input hold requirements and output float delays. These measurements are based on the measurement points identified in Figure 4-1 and Figure 4-2. The rising clock edge reference level VREF and other reference levels are shown in Table 4-9 below. Input or output signals must cross these levels during testing.

Figure 4-1 shows output delay (A and B) and input setup and hold times (C and D). Input setup and hold times (C and D) are specified minimums, defining the smallest acceptable sampling window a synchronous input signal must be stable for correct operation.

#### Table 4-9. Drive Level and Measurement Points for Switching Characteristics

| Symbol           | Value | Units |

|------------------|-------|-------|

| V <sub>REF</sub> | 1.5   | V     |

| V <sub>IHD</sub> | 2.5   | V     |

| V <sub>ILD</sub> | 0.0   | V     |

Note: Refer to Figure 4-1.

57/

#### Figure 4-1. Drive Level and Measurement Points for Switching Characteristics

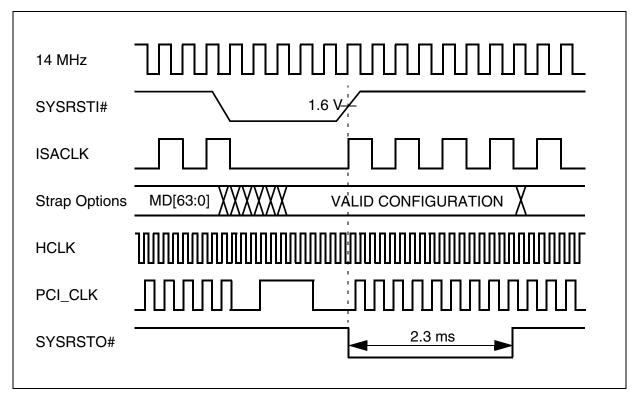

# 4.5.2 RESET SEQUENCE

Figure 4-4 describes the reset sequence of the STPC, also called warm reset.

The constraints on the strap options and the bus activities are the same as for the cold reset.

The SYSRSTI# pulse duration must be long enough to have all the strap options stabilized and must be adjusted depending on resistor values.

#### Figure 4-4. Reset timing diagram

It is mandatory to have a clean reset pulse without glitches as the STPC could then sample invalid strap option setting and enter into an umpredictable mode.

While SYSRSTI# is active, the PCI clock PLL runs in open loop mode at a speed of few 100's KHz.

<u>ل کا</u>

# 4.5.3. SDRAM INTERFACE

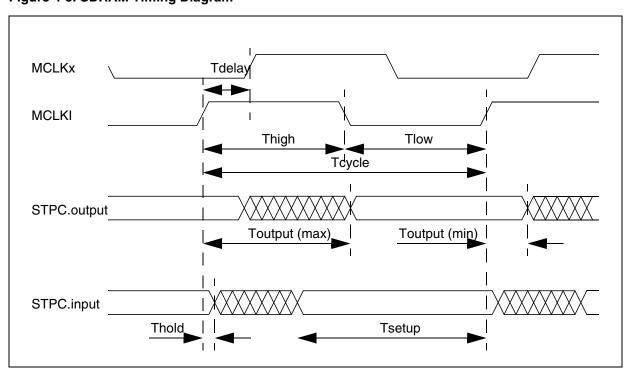

Figure 4-5, Table 4-10, Table 4-11 lists the AC characteristics of the SDRAM interface. The Figure 4-5. SDRAM Timing Diagram

MCLKx clocks are the input clock of the SDRAM devices.

# Table 4-10. SDRAM Bus AC Timings - Commercial Temperature Range

| Name        | Parameter                                                        | Min          | Тур       | Max  | Unit |

|-------------|------------------------------------------------------------------|--------------|-----------|------|------|

| Tcycle      | MCLKI Cycle Time                                                 | 11           |           |      | ns   |

| Thigh       | MCLKI High Time                                                  | 4            |           |      | ns   |

| Tlow        | MCLKI Low Time                                                   | 4            |           |      | ns   |

|             | MCLKI Rising Time                                                |              |           | 1    | ns   |

|             | MCLKI Falling Time                                               |              |           | 1    | ns   |

| Tdelay      | MCLKx to MCLKI delay                                             | 0.5          | 1         | 1.5  | ns   |

|             | MCLKI to RAS# Valid                                              | 1.6          |           | 5.2  | ns   |

|             | MCLKI to CAS# Valid                                              | 1.6          |           | 5.2  | ns   |

|             | MCLKI to CS# Valid                                               | 1.6          |           | 5.2  | ns   |

| Toutput     | MCLKI to DQM[ ] Outputs Valid                                    | 1.35         |           | 5.2  | ns   |

|             | MCLKI to MD[] Outputs Valid                                      | 1.35         |           | 5.2  | ns   |

|             | MCLKI to MA[] Outputs Valid                                      | 1.6          |           | 5.2  | ns   |

|             | MCLKI to MWE# Valid                                              | 1.6          |           | 5.2  | ns   |

| Tsetup      | MD[63:0] setup to MCKLI                                          | 4.7          |           |      | ns   |

| Thold       | MD[63:0] hold from MCKLI                                         | -0.36        |           | 2.3  | ns   |

| Note: These | timings are for a load of 50pF, part running at 100MHz and ReadC | LK activated | d and set | to 0 | 1    |

The PC100 memory is recommended to reach 90MHz operation.

**\$7**

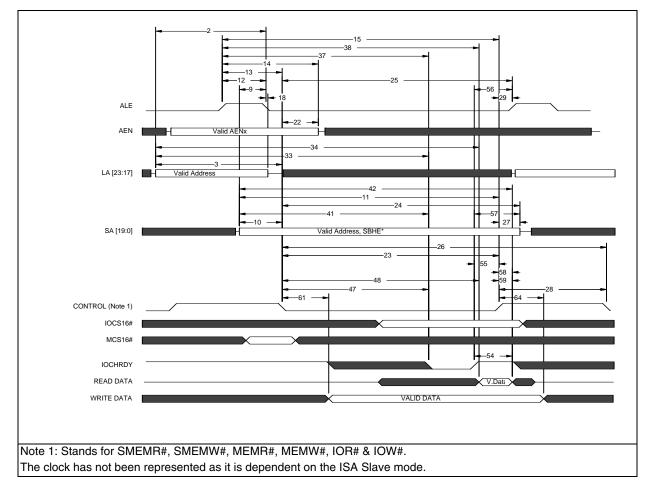

# 4.5.6 ISA INTERFACE AC TIMING CHARACTERISTICS

Figure 4-8 and Table 4-14 list the AC characteristics of the ISA interface.

# Figure 4-8. ISA Cycle (ref Table 4-14.)

## Table 4-14. ISA Bus AC Timing

**\$7**

| Name         | Parameter                                       | Min    | Max | Units  |

|--------------|-------------------------------------------------|--------|-----|--------|

| 2            | LA[23:17] valid before ALE# negated             | 5T     |     | Cycles |

| 3            | LA[23:17] valid before MEMR#, MEMW# asserted    |        | •   |        |

|              | 3a Memory access to 16-bit ISA Slave            | 5T     |     | Cycles |

|              | 3b Memory access to 8-bit ISA Slave             | 5T     |     | Cycles |

| 9            | SA[19:0] & SBHE valid before ALE# negated       | 1T     |     | Cycles |

| 10           | SA[19:0] & SBHE valid before MEMR#, MEMW# asser | ted    |     |        |

|              | 10a Memory access to 16-bit ISA Slave           | 2T     |     | Cycles |

|              | 10b Memory access to 8-bit ISA Slave            | 2T     |     | Cycles |

| 10           | SA[19:0] & SHBE valid before SMEMR#, SMEMW# as  | serted | •   | •      |

| Note: The si | gnal numbering refers to Figure 4-8             |        |     |        |

| Paran | neter                                                                        | Min | Max                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Units                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------|------------------------------------------------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 61e   | I/O access to 16-bit ISA Slave                                               | 2T  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Cycles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 61f   | I/O access to 8-bit ISA Slave                                                | 2T  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Cycles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| MEMV  | V# negated to write data invalid - 16-bit                                    | 1T  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Cycles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| MEMV  | V# negated to write data invalid - 8-bit                                     | 1T  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Cycles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| SMEN  | 1W# negated to write data invalid - 16-bit                                   | 1T  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Cycles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| SMEN  | 1W# negated to write data invalid - 8-bit                                    | 1T  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Cycles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| IOW#  | negated to write data invalid                                                | 1T  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Cycles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|       |                                                                              | 1T  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Cycles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|       |                                                                              | 1T  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Cycles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|       | 61e<br>61f<br>MEMV<br>SMEM<br>SMEM<br>SMEM<br>IOW#<br>MEMV<br>by ISA<br>IOW# |     | 61e   I/O access to 16-bit ISA Slave   2T     61f   I/O access to 8-bit ISA Slave   2T     MEMW# negated to write data invalid - 16-bit   1T     MEMW# negated to write data invalid - 8-bit   1T     SMEMW# negated to write data invalid - 16-bit   1T     SMEMW# negated to write data invalid - 16-bit   1T     SMEMW# negated to write data invalid - 8-bit   1T     IOW# negated to write data invalid   1T     MEMW# negated to write data invalid   1T     IOW# negated to copy data float, 8-bit ISA Slave, odd Byte   1T     IOW# negated to copy data float, 8-bit ISA Slave, odd Byte by   1T | 61e   I/O access to 16-bit ISA Slave   2T     61f   I/O access to 8-bit ISA Slave   2T     MEMW# negated to write data invalid - 16-bit   1T     MEMW# negated to write data invalid - 8-bit   1T     SMEMW# negated to write data invalid - 16-bit   1T     SMEMW# negated to write data invalid - 8-bit   1T     IOW# negated to write data invalid - 8-bit   1T     IOW# negated to write data invalid   1T     IOW# negated to write data invalid   1T     IOW# negated to copy data float, 8-bit ISA Slave, odd Byte   1T     IOW# negated to copy data float, 8-bit ISA Slave, odd Byte by   1T |

# Table 4-14. ISA Bus AC Timing

# **5 MECHANICAL DATA**

57

# 5.1. 516-PIN PACKAGE DIMENSION

The pin numbering for the STPC 516-pin Plastic BGA package is shown in Figure 5-1.

Figure 5-1. 516-Pin PBGA Package - Top View

|    | 1 |   | 3 |   | 5 |   | 7 |   | 9 |    | 11 |    | 13 |    | 15 |    | 17 | ,  | 19 | )  | 21 |    | 23 | 3  | 25 | 5  |    |

|----|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

|    |   | 2 |   | 4 |   | 6 |   | 8 |   | 10 |    | 12 |    | 14 |    | 16 |    | 18 |    | 20 |    | 22 |    | 24 |    | 26 |    |

| А  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | А  |

| В  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | В  |

| С  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | С  |

| D  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | D  |

| Е  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | Е  |

| F  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | F  |

| G  | 0 | 0 | 0 | 0 | 0 | 0 |   |   |   |    |    |    |    |    |    |    |    |    |    |    | 0  | 0  | 0  | 0  | 0  | 0  | G  |

| н  | 0 | 0 | 0 | 0 | 0 | 0 |   |   |   |    |    |    |    |    |    |    |    |    |    |    | 0  | 0  | 0  | 0  | 0  | 0  | Н  |

| J  | 0 | 0 | 0 | 0 | 0 | 0 |   |   |   |    |    |    |    |    |    |    |    |    |    |    | 0  | 0  | 0  | 0  | 0  | 0  | J  |

| K  | 0 | 0 | 0 | 0 | 0 | 0 |   |   |   |    |    |    |    |    |    |    |    |    |    |    | 0  | 0  | 0  | 0  | 0  | 0  | К  |

| L  | 0 | 0 | 0 | 0 | 0 | 0 |   |   |   |    | 0  | 0  | 0  | 0  | 0  | 0  |    |    |    |    | 0  | 0  | 0  | 0  | 0  | 0  | L  |

| М  | 0 | 0 | 0 | 0 | 0 | 0 |   |   |   |    | 0  | 0  | 0  | 0  | 0  | 0  |    |    |    |    | 0  | 0  | 0  | 0  | 0  | 0  | М  |

| Ν  | 0 | 0 | 0 | 0 | 0 | 0 |   |   |   |    | 0  | 0  | 0  | 0  | 0  | 0  |    |    |    |    | 0  | 0  | 0  | 0  | 0  | 0  | Ν  |

| Р  | 0 | 0 | 0 | 0 | 0 | 0 |   |   |   |    | 0  | 0  | 0  | 0  | 0  | 0  |    |    |    |    | 0  | 0  | 0  | 0  | 0  | 0  | Ρ  |

| R  | 0 | 0 | 0 | 0 | 0 | 0 |   |   |   |    | 0  | 0  | 0  | 0  | 0  | 0  |    |    |    |    | 0  | 0  | 0  | 0  | 0  | 0  | R  |

| Т  | 0 | 0 | 0 | 0 | 0 | 0 |   |   |   |    | 0  | 0  | 0  | 0  | 0  | 0  |    |    |    |    | 0  | 0  | 0  | 0  | 0  | 0  | Т  |

| U  | 0 | 0 | 0 | 0 | 0 | 0 |   |   |   |    |    |    |    |    |    |    |    |    |    |    | 0  | 0  | 0  | 0  | 0  | 0  | U  |

| V  | 0 | 0 | 0 | 0 | 0 | 0 |   |   |   |    |    |    |    |    |    |    |    |    |    |    | 0  | 0  | 0  | 0  | 0  | 0  | V  |

| W  | 0 | 0 | 0 | 0 | 0 | 0 |   |   |   |    |    |    |    |    |    |    |    |    |    |    | 0  | 0  | 0  | 0  | 0  | 0  | W  |

| Y  | 0 | 0 | 0 | 0 | 0 | 0 |   |   |   |    |    |    |    |    |    |    |    |    |    |    | 0  | 0  | 0  | 0  | 0  | 0  | Y  |

| AA | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | AA |

| AB | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | AB |

| AC | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | AC |

| AD | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | AD |

| AE | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | AE |

| AF | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | AF |

|    | 1 |   | 3 |   | 5 |   | 7 |   | 9 |    | 11 |    | 13 |    | 15 |    | 17 |    | 19 |    | 21 |    | 23 |    | 25 |    |    |

|    |   | 2 |   | 4 |   | 6 |   | 8 |   | 10 |    | 12 |    | 14 |    | 16 |    | 18 | :  | 20 | :  | 22 |    | 24 | :  | 26 |    |

Dimensions are shown in Figure 5-2, Table 5-1. and Figure 5-3, Table 5-2..

# 6.3.6. IPC

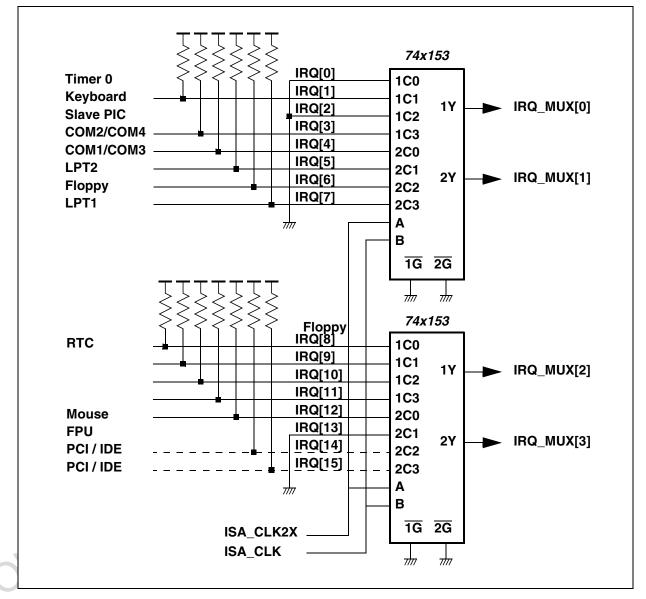

Most of the IPC signals are multiplexed: Interrupt inputs, DMA Request inputs, DMA Acknowledge outputs. The figure below describes a complete implementation of the IRQ[15:0] time-multiplexing.

When an interrupt line is used internally, the corresponding input can be grounded. In most of the embedded designs, only few interrupts lines are necessary and the glue logic can be simplified.

When the interface is integrated into the STPC, the corresponding interrupt line can be grounded as it is connected internally.

For example, if the integrated IDE controller is activated, the IRQ[14] and IRQ[15] inputs can be grounded.

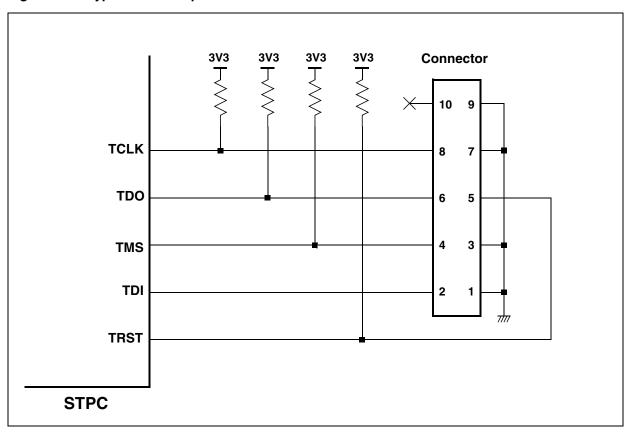

# 6.3.13. JTAG INTERFACE

The STPC integrates a JTAG interface for scanchain and on-board testing. The only external **Figure 6-19. Typical JTAG implementation**  device needed are the pull up resistors. Figure 6-19 describes a typical implementation using these devices.

## **6.4. PLACE AND ROUTE RECOMMENDATIONS**

#### 6.4.1. GENERAL RECOMMENDATIONS

Some STPC Interfaces run at high speed and need to be carefully routed or even shielded like:

- 1) Memory Interface

- 2) PCI bus

- 3) Graphics and video interfaces

- 4) 14 MHz oscillator stage

All clock signals have to be routed first and shielded for speeds of 27MHz or higher. The high speed signals follow the same constraints, as for the memory and PCI control signals.

The next interfaces to be routed are Memory, PCI, and Video/graphics.

All the analog noise-sensitive signals have to be routed in a separate area and hence can be routed indepedently.

#### 6.4.2. PLL DEFINITION AND IMPLIMENTATION

PLLs are analog cells which supply the internal STPC Clocks. To get the cleanest clock, the jitter on the power supply must be reduced as much as possible. This will result in a more stable system.

Each of the integrated PLL has a dedicated power pin so a single power plane for all of these PLLs, or one wire for each, or any solution in between which help the layout of the board can be used.

Powering these pins with one Ferrite + capacitances is enough. We recommend at least 2 capacitances: one 'big' (few uF) for power storage, and one or 2 smalls (100nF + 1nF) for noise filtering.

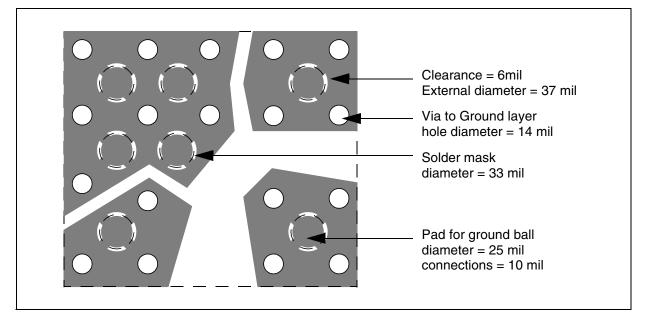

To avoid solder wicking over to the via pads during soldering, it is important to have a solder mask of 4 mil around the pad (NSMD pad). This gives a diameter of 33 mil for a 25 mil ground pad. To obtain the optimum ground layout, place the vias directly under the ball pads. In this case no local board distortion is tolerated.

# Figure 6-34. Optimum Layout for Central Ground Ball - top layer

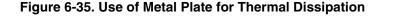

6.5.2.3. Heat dissipation

57/

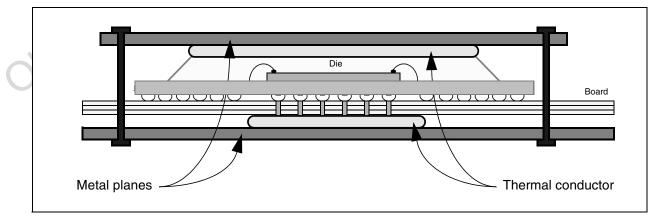

The thickness of the copper on PCB layers is typically 34  $\mu$ m for external layers and 17  $\mu$ m for internal layers. This means that thermal dissipation is not good; high board temperatures are concentrated around the devices and these fall quickly with increased distance.

Where possible, place a metal layer inside the PCB; this improves dramatically the spread of heat and hence the thermal dissipation of the board.

The possibility of using the whole system box for thermal dissipation is very useful in cases of high internal temperatures and low outside temperatures. Bottom side of the PBGA should be thermally connected to the metal chassis in order to propagate the heat flow through the metal. Thermally connecting also the top side will improve furthermore the heat dissipation. Figure 6-35 illustrates such an implementation.

#### 6.6.3.3. POST code

Once the 16 first bytes are fetched and decoded, the CPU core continue its execution depending on the content of these first data. Usually, it corresponds to a JUMP instruction and the code fetching continues, generating read cycles on the ISA bus.

Most of the BIOS and boot loaders are reading the content of the flash, decompressing it in SDRAM, and then continue the execution by jumping to the entry point in RAM. This boot process ends with a JUMP to the entry point of the OS launcher.

These various steps of the booting sequence are codified by the so-called POST codes (Power-On Self-Test). A 8-bit code is written to the port 80H at the beginning of each stage of the booting process (I/O write to address 0080H) and can be displayed on two 7-segment display, enabling a fast visual check of the booting completion level.

Usually, the last POST code is 0x00 and corresponds to the jump into the OS launcher.

When the execution fails or hangs, the lastest written code stays visible on that display, indicating either the piece of code to analyse, either the area of the hardware not working properly.

#### 6.6.4. LOCAL BUS MODE

As the Local Bus controller is located into the Host interface, there is no access to the cycles on the PCI, reducing the amount of signals to check.

#### 6.6.4.1. First code fetches

5/

When booting on the Local Bus, the key signal to check at the very beginning is FCS0#. This signal is a Chip Select for the boot flash and should toggle together with PRD# to fetch the first 16 bytes of code. This corresponds to the loading of the first line of the CPU cache.

In case FCS0# does not toggle, then one of the

previous steps has not been done properly, like HCLK speed and CPU clock multiplier (x1, x2).

#### 6.6.4.2. Boot Flash size

The Local Bus support 8-bit and 16-bit boot memory devices only.

#### 6.6.4.3. POST code

Like in ISA mode, POST codes can be implemented on the Local Bus. The difference is that an IOCS# must be programmed at I/O address 80H prior to writing these code, the POST display being connected to this IOCS# and to the lower 8 bits of the bus.

#### 6.6.5. SUMMARY

Here is a check-list for the STPC board debug from power-on to CPU execution.

For each step, in case of failure, verify first the corresponding balls of the STPC:

- check if the voltage or activity is correct - search for potential shortcuts.

For troubleshooting in steps 5 to 10, verify the related strap options:

- value & connection. Refer to Section 3.

- see Figure 4-3 for timing constraints

Steps 8a and 9a are for debug in ISA mode while steps 8b and 9b are for Local Bus mode.

#### 6.6.6. PCMCIA mode

As the STPC uses the RMRTCCS# signal for booting in that mode, the methodology is the same as for the ISA bus. The PCMCIA cards being 3.3V or 5V, the boot flash device must be 5V tolerant when directly connected on the address and data busses. An other solution is to isolate the flash from the PCMCIA lines using 5V tolerant LVTTL buffers.

|   | Check:                   | How?                                                                                                                                   | Troubleshooting                                                                                                                                    |  |  |  |  |  |  |

|---|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 1 | Power<br>supplies        | Verify that voltage is within specs:<br>- this must include HF & LF noise<br>- avoid full range sweep<br>Refer to Table 4-1 for values | Measure voltage near STPC balls:<br>- use very low GND connection.<br>Add some decoupling capacitor:<br>- the smallest, the nearest to STPC balls. |  |  |  |  |  |  |

| 2 | 14.318 MHz               | Verify OSC14M speed                                                                                                                    | The 2 capacitors used with the quartz must<br>match with the capacitance of the crystal.<br>Try other values.                                      |  |  |  |  |  |  |

| 3 | SYSRSTI#<br>(Power Good) | Measure SYSRSTI# of STPC<br>See Figure 4-3 for waveforms.                                                                              | Verify reset generation circuit:<br>- device reference<br>- components value                                                                       |  |  |  |  |  |  |