Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0                                                        |

| Core Size                  | 32-Bit Single-Core                                                     |

| Speed                      | 48MHz                                                                  |

| Connectivity               | CANbus, HDMI-CEC, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                   |

| Number of I/O              | 23                                                                     |

| Program Memory Size        | 32KB (32K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 6K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 1.95V                                                          |

| Data Converters            | A/D 10x12b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 28-UFQFN                                                               |

| Supplier Device Package    | 28-UFQFPN (4x4)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f048g6u6  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## List of figures

| Block diagram                                                       | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Clock tree                                                          | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

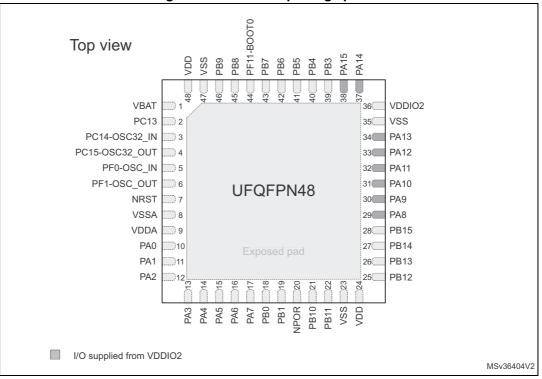

| UFQFPN48 package pinout                                             | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

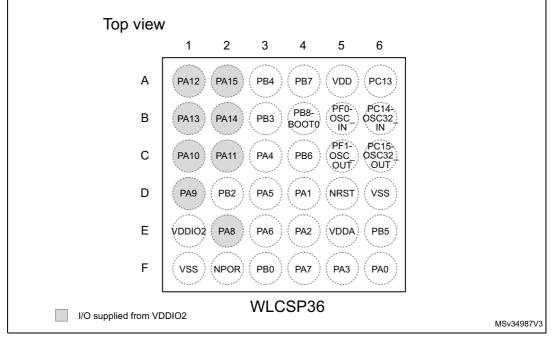

| WLCSP36 package                                                     | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

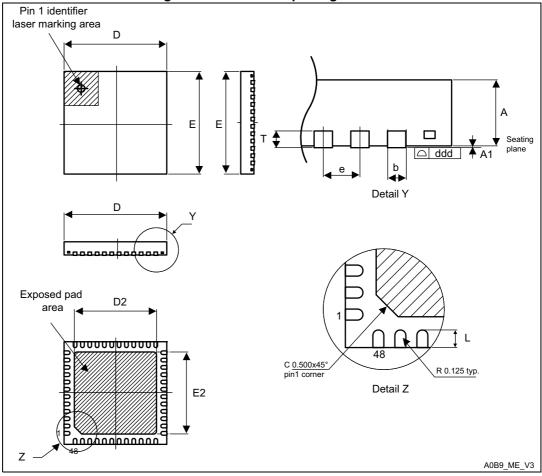

| UFQFPN28 package                                                    | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| STM32F048x6 memory map                                              | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Pin loading conditions                                              | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Pin input voltage                                                   | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Power supply scheme                                                 | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Current consumption measurement scheme                              | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| High-speed external clock source AC timing diagram                  | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Low-speed external clock source AC timing diagram                   | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Typical application with an 8 MHz crystal                           | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Typical application with a 32.768 kHz crystal                       | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| HSI oscillator accuracy characterization results for soldered parts | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| HSI14 oscillator accuracy characterization results                  | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| HSI48 oscillator accuracy characterization results                  | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| TC and TTa I/O input characteristics                                | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Five volt tolerant (FT and FTf) I/O input characteristics           | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

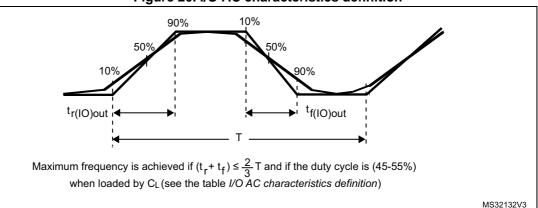

| I/O AC characteristics definition                                   | 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Recommended NRST pin protection                                     | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| ADC accuracy characteristics                                        | 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| SPI timing diagram - slave mode and CPHA = 0                        | 79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| SPI timing diagram - slave mode and CPHA = 1                        | 79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| SPI timing diagram - master mode                                    | 80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| I <sup>2</sup> S slave timing diagram (Philips protocol)            | 81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| I <sup>2</sup> S master timing diagram (Philips protocol)           | 82                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| UFQFPN48 package outline                                            | 84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Recommended footprint for UFQFPN48 package                          | 85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| UFQFPN48 package marking example                                    | 86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Recommended pad footprint for WLCSP36 package                       | 88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| WLCSP36 package marking example                                     | 89                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| UFQFPN28 package marking example                                    | 92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                     | Block diagram.       Clock tree         UFQFPN48 package pinout.       WLCSP36 package         WLCSP36 package       STM32F048x6 memory map         Pin loading conditions.       Pin loading conditions.         Pin input voltage       Power supply scheme         Current consumption measurement scheme       High-speed external clock source AC timing diagram         Low-speed external clock source AC timing diagram.       Current consumption measurement scheme         High-speed external clock source AC timing diagram.       Ypical application with an 8 MHz crystal         Typical application with a 8 MHz crystal       Typical application with a 8 MHz crystal         HSI oscillator accuracy characterization results       HSI4 oscillator accuracy characterization results         HSI4 oscillator accuracy characterization results       Fixe volt tolerant (FT and FTf) I/O input characteristics         I/O AC characteristics definition       Recommended NRST pin protection         ADC accuracy characteristics       SPI timing diagram - slave mode and CPHA = 0         SPI timing diagram - slave mode and CPHA = 0       SPI timing diagram (Philips protocol).         I/2 Salve timing diagram (Philips protocol).       I/2 Salve timing diagram (Philips protocol).         I/2 Salve timing diagram (Philips protocol).       I/2 Salve timing diagram (Philips protocol).         I/2 Shakatage outline.       Recommended footprint for UFQFPN48 |

| Perip               | heral                    | STM32F048G6                                                                                                             | STM32F048T6 | STM32F048C6 |  |  |

|---------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------|-------------|-------------|--|--|

| Flash mem           | ory (Kbyte)              |                                                                                                                         | 32          |             |  |  |

| SRAM (Kbyte)        |                          | 6                                                                                                                       |             |             |  |  |

| Timoro              | Advanced control         |                                                                                                                         | 1 (16-bit)  |             |  |  |

| Timers              | General<br>purpose       | 4 (16-bit)<br>1 (32-bit)                                                                                                |             |             |  |  |

|                     | SPI [I2S] <sup>(1)</sup> | 1 [1] 2 [1]                                                                                                             |             |             |  |  |

|                     | l <sup>2</sup> C         | 1                                                                                                                       |             |             |  |  |

| Comm.<br>interfaces | USART                    | 2                                                                                                                       |             |             |  |  |

|                     | USB                      | 1                                                                                                                       |             |             |  |  |

|                     | CEC                      | 1                                                                                                                       |             |             |  |  |

|                     | t ADC<br>f channels)     | 1<br>(10 ext. + 3 int.)                                                                                                 |             |             |  |  |

| GP                  | IOs                      | 23                                                                                                                      | 29          | 37          |  |  |

| Capacitive ser      | nsing channels           | 10                                                                                                                      | 13          | 13          |  |  |

| Max. CPU            | frequency                | 48 MHz                                                                                                                  |             |             |  |  |

| Operatin            | g voltage                | $V_{DD}$ = 1.8 V ± 8%, $V_{DDA}$ = from $V_{DD}$ to 3.6 V                                                               |             |             |  |  |

| Operating t         | emperature               | Ambient operating temperature: -40°C to 85 °C / -40°C to 105°C<br>Junction temperature: -40°C to 105°C / -40°C to 125°C |             |             |  |  |

| Pack                | ages                     | UFQFPN28                                                                                                                | WLCSP36     | UFQFPN48    |  |  |

Table 1. STM32F048x device features and peripheral counts

1. The SPI1 interface can be used either in SPI mode or in I2S audio mode.

## **3** Functional overview

Figure 1 shows the general block diagram of the STM32F048x6 devices.

## 3.1 ARM<sup>®</sup>-Cortex<sup>®</sup>-M0 core

The ARM<sup>®</sup> Cortex<sup>®</sup>-M0 is a generation of ARM 32-bit RISC processors for embedded systems. It has been developed to provide a low-cost platform that meets the needs of MCU implementation, with a reduced pin count and low-power consumption, while delivering outstanding computational performance and an advanced system response to interrupts.

The ARM<sup>®</sup> Cortex<sup>®</sup>-M0 processors feature exceptional code-efficiency, delivering the high performance expected from an ARM core, with memory sizes usually associated with 8- and 16-bit devices.

The STM32F048x6 devices embed ARM core and are compatible with all ARM tools and software.

## 3.2 Memories

The device has the following features:

- 6 Kbytes of embedded SRAM accessed (read/write) at CPU clock speed with 0 wait states and featuring embedded parity checking with exception generation for fail-critical applications.

- The non-volatile memory is divided into two arrays:

- 32 Kbytes of embedded Flash memory for programs and data

- Option bytes

The option bytes are used to write-protect the memory (with 4 KB granularity) and/or readout-protect the whole memory with the following options:

- Level 0: no readout protection

- Level 1: memory readout protection, the Flash memory cannot be read from or written to if either debug features are connected or boot in RAM is selected

- Level 2: chip readout protection, debug features (Cortex<sup>®</sup>-M0 serial wire) and boot in RAM selection disabled

## 3.3 Boot modes

At startup, the boot pin and boot selector option bits are used to select one of the three boot options:

- boot from User Flash memory

- boot from System Memory

- boot from embedded SRAM

The boot pin is shared with the standard GPIO and can be disabled through the boot selector option bits. The boot loader is located in System Memory. It is used to reprogram the Flash memory by using USART on pins PA14/PA15 or PA9/PA10 or I<sup>2</sup>C on pins PB6/PB7 or through the USB DFU interface.

DocID026007 Rev 6

## 3.4 Cyclic redundancy check calculation unit (CRC)

The CRC (cyclic redundancy check) calculation unit is used to get a CRC code from a 32-bit data word and a CRC-32 (Ethernet) polynomial.

Among other applications, CRC-based techniques are used to verify data transmission or storage integrity. In the scope of the EN/IEC 60335-1 standard, they offer a means of verifying the Flash memory integrity. The CRC calculation unit helps compute a signature of the software during runtime, to be compared with a reference signature generated at link-time and stored at a given memory location.

## 3.5 **Power management**

#### 3.5.1 Power supply schemes

- $V_{DD} = V_{DDIO1} = 1.8 \text{ V} \pm 8\%$ : external power supply for I/Os ( $V_{DDIO1}$ ) and digital logic. It is provided externally through VDD pins.

- $V_{DDA}$  = from  $V_{DD}$  to 3.6 V: external analog power supply for ADC, RCs and PLL (minimum voltage to be applied to  $V_{DDA}$  is 2.4 V when the ADC is used). It is provided externally through VDDA pin. The  $V_{DDA}$  voltage level must be always greater or equal to the  $V_{DD}$  voltage level and must be established first.

- V<sub>DDIO2</sub> = 1.65 to 3.6 V: external power supply for marked I/Os. V<sub>DDIO2</sub> is provided externally through the VDDIO2 pin. The V<sub>DDIO2</sub> voltage level is completely independent from V<sub>DD</sub> or V<sub>DDA</sub>, but it must not be provided without a valid supply on V<sub>DD</sub>. The V<sub>DDIO2</sub> supply is monitored and compared with the internal reference voltage (V<sub>REFINT</sub>). When the V<sub>DDIO2</sub> is below this threshold, all the I/Os supplied from this rail are disabled by hardware. The output of this comparator is connected to EXTI line 31 and it can be used to generate an interrupt. Refer to the pinout diagrams or tables for concerned I/Os list.

- V<sub>BAT</sub> = 1.65 to 3.6 V: power supply for RTC, external clock 32 kHz oscillator and backup registers (through power switch) when V<sub>DD</sub> is not present.

For more details on how to connect power pins, refer to *Figure 9: Power supply scheme*.

#### 3.5.2 Power-on reset

To guarantee a proper power-on reset, the NPOR pin must be held low until  $V_{DD}$  is stable. When  $V_{DD}$  is stable, the reset state can be exited either by:

- putting the NPOR pin in high impedance (NPOR pin has an internal pull-up), or by

- forcing the pin to high level by connecting it to V<sub>DDA</sub>

#### 3.5.3 Low-power modes

The STM32F048x6 microcontrollers support two low-power modes to achieve the best compromise between low power consumption, short startup time and available wakeup sources:

#### Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs.

TIM16 and TIM17 have a complementary output with dead-time generation and independent DMA request generation.

Their counters can be frozen in debug mode.

#### 3.12.3 Independent watchdog (IWDG)

The independent watchdog is based on an 8-bit prescaler and 12-bit downcounter with user-defined refresh window. It is clocked from an independent 40 kHz internal RC and as it operates independently from the main clock, it can operate in Stop mode. It can be used either as a watchdog to reset the device when a problem occurs, or as a free running timer for application timeout management. It is hardware or software configurable through the option bytes. The counter can be frozen in debug mode.

#### 3.12.4 System window watchdog (WWDG)

The system window watchdog is based on a 7-bit downcounter that can be set as free running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the APB clock (PCLK). It has an early warning interrupt capability and the counter can be frozen in debug mode.

#### 3.12.5 SysTick timer

This timer is dedicated to real-time operating systems, but could also be used as a standard down counter. It features:

- a 24-bit down counter

- autoreload capability

- maskable system interrupt generation when the counter reaches 0

- programmable clock source (HCLK or HCLK/8)

#### 3.13 Real-time clock (RTC) and backup registers

The RTC and the five backup registers are supplied through a switch that takes power either on  $V_{DD}$  supply when present or through the  $V_{BAT}$  pin. The backup registers are five 32-bit registers used to store 20 bytes of user application data when  $V_{DD}$  power is not present. They are not reset by a system or power reset.

from the CPU clock, allowing the I2C1 to wake up the MCU from Stop mode on address match.

The I2C peripheral can be served by the DMA controller.

| Table 8. STM32F048x6 I <sup>2</sup> C implementation         |      |  |  |  |

|--------------------------------------------------------------|------|--|--|--|

| I <sup>2</sup> C features <sup>(1)</sup>                     | I2C1 |  |  |  |

| 7-bit addressing mode                                        | Х    |  |  |  |

| 10-bit addressing mode                                       | Х    |  |  |  |

| Standard mode (up to 100 kbit/s)                             | Х    |  |  |  |

| Fast mode (up to 400 kbit/s)                                 | Х    |  |  |  |

| Fast Mode Plus with extra output drive I/Os (up to 1 Mbit/s) | Х    |  |  |  |

| Independent clock                                            | Х    |  |  |  |

| SMBus                                                        | Х    |  |  |  |

| Wakeup from STOP                                             | X    |  |  |  |

1. X = supported.

# 3.15 Universal synchronous/asynchronous receiver/transmitter (USART)

The device embeds two universal synchronous/asynchronous receivers/transmitters (USART1, USART2) which communicate at speeds of up to 6 Mbit/s.

They provide hardware management of the CTS, RTS and RS485 DE signals, multiprocessor communication mode, master synchronous communication and single-wire half-duplex communication mode. USART1 supports also SmartCard communication (ISO 7816), IrDA SIR ENDEC, LIN Master/Slave capability and auto baud rate feature, and has a clock domain independent of the CPU clock, allowing to wake up the MCU from Stop mode.

The USART interfaces can be served by the DMA controller.

| USART modes/features <sup>(1)</sup>         | USART1 | USART2 |  |  |  |  |

|---------------------------------------------|--------|--------|--|--|--|--|

| Hardware flow control for modem             | Х      | Х      |  |  |  |  |

| Continuous communication using DMA          | Х      | Х      |  |  |  |  |

| Multiprocessor communication                | Х      | Х      |  |  |  |  |

| Synchronous mode                            | Х      | Х      |  |  |  |  |

| Smartcard mode                              | Х      | -      |  |  |  |  |

| Single-wire half-duplex communication       | Х      | Х      |  |  |  |  |

| IrDA SIR ENDEC block                        | Х      | -      |  |  |  |  |

| LIN mode                                    | Х      | -      |  |  |  |  |

| Dual clock domain and wakeup from Stop mode | Х      | -      |  |  |  |  |

| Receiver timeout interrupt                  | Х      | -      |  |  |  |  |

Table 9. STM32F048x6 USART implementation

pull-up and also battery charging detection according to Battery Charging Specification Revision 1.2. The USB interface implements a full-speed (12 Mbit/s) function interface with added support for USB 2.0 Link Power Management. It has software-configurable endpoint setting with packet memory up-to 1 KB and suspend/resume support. It requires a precise 48 MHz clock which can be generated from the internal main PLL (the clock source must use an HSE crystal oscillator) or by the internal 48 MHz oscillator in automatic trimming mode. The synchronization for this oscillator can be taken from the USB data stream itself (SOF signalization) which allows crystal-less operation.

## 3.19 Clock recovery system (CRS)

The STM32F048x6 embeds a special block which allows automatic trimming of the internal 48 MHz oscillator to guarantee its optimal accuracy over the whole device operational range. This automatic trimming is based on the external synchronization signal, which could be either derived from USB SOF signalization, from LSE oscillator, from an external signal on CRS\_SYNC pin or generated by user software. For faster lock-in during startup it is also possible to combine automatic trimming with manual trimming action.

## 3.20 Serial wire debug port (SW-DP)

An ARM SW-DP interface is provided to allow a serial wire debugging tool to be connected to the MCU.

## 4 Pinouts and pin descriptions

Figure 3. UFQFPN48 package pinout

<sup>1.</sup> The above figure shows the package in top view, changing from bottom view in the previous document versions.

DocID026007 Rev 6

| Pir      | n numt  | pers     |                                      |             |               |            | n definitions<br>Pin functions                                                     | 5                                          |  |

|----------|---------|----------|--------------------------------------|-------------|---------------|------------|------------------------------------------------------------------------------------|--------------------------------------------|--|

| UFQFPN48 | WLCSP36 | UFQFPN28 | Pin name<br>(function upon<br>reset) | Pin<br>type | I/O structure | Notes      | Alternate function                                                                 | Additional<br>functions                    |  |

| 1        | -       | -        | VBAT                                 | S           | -             | -          | Backup power su                                                                    | pply                                       |  |

| 2        | A6      | -        | PC13                                 | I/O         | тс            | (1)(2)     | -                                                                                  | WKUP2,<br>RTC_TAMP1,<br>RTC_TS,<br>RTC_OUT |  |

| 3        | B6      | -        | PC14-OSC32_IN<br>(PC14)              | I/O         | тс            | (1)<br>(2) | -                                                                                  | OSC32_IN                                   |  |

| 4        | C6      | -        | PC15-OSC32_OUT<br>(PC15)             | I/O         | тс            | (1)<br>(2) | -                                                                                  | OSC32_OUT                                  |  |