Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | ARM® Cortex®-M3                                                              |

| Core Size                  | 32-Bit Single-Core                                                           |

| Speed                      | 67MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                               |

| Peripherals                | CapSense, DMA, LCD, POR, PWM, WDT                                            |

| Number of I/O              | 62                                                                           |

| Program Memory Size        | 64KB (64K x 8)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 2K x 8                                                                       |

| RAM Size                   | 16K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 5.5V                                                                 |

| Data Converters            | A/D 2x12b; D/A 4x8b                                                          |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 100-LQFP                                                                     |

| Supplier Device Package    | 100-TQFP (14x14)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c5666axi-lp004 |

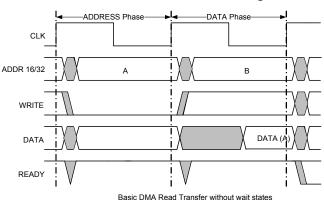

Figure 4-2. DMA Timing Diagram

CLK

ADDR 16/32

WRITE

DATA

READY

В

DATA (A)

### 4.3.4.2 Auto Repeat DMA

Auto repeat DMA is typically used when a static pattern is repetitively read from system memory and written to a peripheral. This is done with a single TD that chains to itself.

### 4.3.4.3 Ping Pong DMA

A ping pong DMA case uses double buffering to allow one buffer to be filled by one client while another client is consuming the data previously received in the other buffer. In its simplest form, this is done by chaining two TDs together so that each TD calls the opposite TD when complete.

### 4.3.4.4 Circular DMA

Circular DMA is similar to ping pong DMA except it contains more than two buffers. In this case there are multiple TDs; after the last TD is complete it chains back to the first TD.

### 4.3.4.5 Indexed DMA

In an indexed DMA case, an external master requires access to locations on the system bus as if those locations were shared memory. As an example, a peripheral may be configured as an SPI or I<sup>2</sup>C slave where an address is received by the external master. That address becomes an index or offset into the internal system bus memory space. This is accomplished with an initial "address fetch" TD that reads the target address location from the peripheral and writes that value into a subsequent TD in the chain. This modifies the TD chain on the fly. When the "address fetch" TD completes it moves on to the next TD, which has the new address information embedded in it. This TD then carries out the data transfer with the address location required by the external master.

### 4.3.4.6 Scatter Gather DMA

In the case of scatter gather DMA, there are multiple noncontiguous sources or destinations that are required to effectively carry out an overall DMA transaction. For example, a packet may need to be transmitted off of the device and the packet elements, including the header, payload, and trailer, exist

in various noncontiguous locations in memory. Scatter gather DMA allows the segments to be concatenated together by using multiple TDs in a chain. The chain gathers the data from the multiple locations. A similar concept applies for the reception of data onto the device. Certain parts of the received data may need to be scattered to various locations in memory for software processing convenience. Each TD in the chain specifies the location for each discrete element in the chain.

### 4.3.4.7 Packet Queuing DMA

ADDRESS Phase

Α

Packet queuing DMA is similar to scatter gather DMA but specifically refers to packet protocols. With these protocols, there may be separate configuration, data, and status phases associated with sending or receiving a packet.

For instance, to transmit a packet, a memory mapped configuration register can be written inside a peripheral, specifying the overall length of the ensuing data phase. The CPU can set up this configuration information anywhere in system memory and copy it with a simple TD to the peripheral. After the configuration phase, a data phase TD (or a series of data phase TDs) can begin (potentially using scatter gather). When the data phase TD(s) finish, a status phase TD can be invoked that reads some memory mapped status information from the peripheral and copies it to a location in system memory specified by the CPU for later inspection. Multiple sets of configuration, data, and status phase "subchains" can be strung together to create larger chains that transmit multiple packets in this way. A similar concept exists in the opposite direction to receive the packets.

### 4.3.4.8 Nested DMA

One TD may modify another TD, as the TD configuration space is memory mapped similar to any other peripheral. For example, a first TD loads a second TD's configuration and then calls the second TD. The second TD moves data as required by the application. When complete, the second TD calls the first TD, which again updates the second TD's configuration. This process repeats as often as necessary.

The central timewheel can be programmed to wake the system periodically and optionally issue an interrupt. This enables flexible, periodic wakeups from low power modes or coarse timing applications. Systems that require accurate timing should use Real Time Clock capability instead of the central timewheel.

The 100-kHz clock (CLK100K) can be used as a low power system clock to run the CPU. It can also generate time intervals using the fast timewheel.

The fast timewheel is a 5-bit counter, clocked by the 100-kHz clock. It features programmable settings and automatically resets when the terminal count is reached. An optional interrupt can be generated each time the terminal count is reached. This enables flexible, periodic interrupts of the CPU at a higher rate than is allowed using the central timewheel.

The 33 kHz clock (CLK33K) comes from a divide-by-3 operation on CLK100K. This output can be used as a reduced accuracy version of the 32.768 kHz ECO clock with no need for a crystal.

### 6.1.2 External Oscillators

Figure 6-1 shows that there are two external oscillators. They can be routed directly or divided. The direct routes may not have a 50% duty cycle. Divided clocks have a 50% duty cycle.

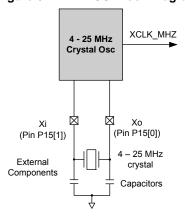

### 6.1.2.1 MHz External Crystal Oscillator

The MHzECO provides high frequency, high precision clocking using an external crystal (see Figure 6-2). It supports a wide variety of crystal types, in the range of 4 to 25 MHz. When used in conjunction with the PLL, it can generate CPU and system clocks up to the device's maximum frequency (see Phase-Locked Loop on page 24). The GPIO pins connecting to the external crystal and capacitors are fixed. MHzECO accuracy depends on the crystal chosen.

Figure 6-2. MHzECO Block Diagram

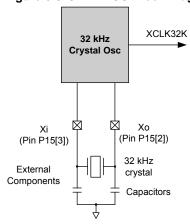

### 6.1.2.2 32.768 kHz ECO

The 32.768 kHz External Crystal Oscillator (32kHzECO) provides precision timing with minimal power consumption using an external 32.768 kHz watch crystal (see Figure 6-3). The 32kHzECO also connects directly to the sleep timer and provides the source for the Real Time Clock (RTC). The RTC uses a 1 second interrupt to implement the RTC functionality in firmware.

The oscillator works in two distinct power modes. This allows users to trade off power consumption with noise immunity from neighboring circuits. The GPIO pins connected to the external crystal and capacitors are fixed.

Figure 6-3. 32kHzECO Block Diagram

It is recommended that the external 32.768-kHz watch crystal have a load capacitance (CL) of 6 pF or 12.5 pF. Check the crystal manufacturer's datasheet. The two external capacitors, CL1 and CL2, are typically of the same value, and their total capacitance, CL1CL2 / (CL1 + CL2), including pin and trace capacitance, should equal the crystal CL value. For more information, refer to application note AN54439: PSoC 3 and PSoC 5 External Oscillators. See also pin capacitance specifications in the "GPIO" section on page 75.

### 6.1.2.3 Digital System Interconnect

The DSI provides routing for clocks taken from external clock oscillators connected to I/O. The oscillators can also be generated within the device in the digital system and UDBs.

While the primary DSI clock input provides access to all clocking resources, up to eight other DSI clocks (internally or externally generated) may be routed directly to the eight digital clock dividers. This is only possible if there are multiple precision clock sources.

### 6.1.3 Clock Distribution

All seven clock sources are inputs to the central clock distribution system. The distribution system is designed to create multiple high precision clocks. These clocks are customized for the design's requirements and eliminate the common problems found with limited resolution prescalers attached to peripherals. The clock distribution system generates several types of clock trees.

- The system clock is used to select and supply the fastest clock in the system for general system clock requirements and clock synchronization of the PSoC device.

- Bus Clock 16-bit divider uses the system clock to generate the system's bus clock used for data transfers and the CPU. The CPU clock is directly derived from the bus clock.

- Eight fully programmable 16-bit clock dividers generate digital system clocks for general use in the digital system, as configured by the design's requirements. Digital system clocks can generate custom clocks derived from any of the seven clock sources for any purpose. Examples include baud rate generators, accurate PWM periods, and timer clocks, and many others. If more than eight digital clock dividers are required, the UDBs and fixed function Timer/Counter/PWMs can also generate clocks.

**Digital Input Path** Naming Convention 'x' = Port Number PRT[x]CTL PRT[x]DBL\_SYNC\_IN 'y' = Pin Number PRT[x]PS Digital System Input PICU[x]INTTYPE[y] Input Buffer Disable PICU[x]INTSTAT Interrupt Pin Interrupt Signal Logic PICU[x]INTSTAT **Digital Output Path** PRT[x]SLW PRT[x]SYNC\_OUT Vddio Vddio PRT[x]DR In Digital System Output Vddio PRT[x]BYP Drive PRT[x]DM2 Slew PIN Logic PRT[x]DM1 Cntl PRT[x]DM0 **Bidirectional Control** OE PRT[x]BIE Analog Capsense Global Control CAPS[x]CFG1 Switches PRT[x]AG Analog Global PRT[x]AMUX Analog Mux LCD Display PRT[x]LCD\_COM\_SEG Logic & MUX PRT[x]LCD\_EN LCD Bias Bus

Figure 6-9. GPIO Block Diagram

### 6.4.13 SIO as Comparator

This section applies only to SIO pins. The adjustable input level feature of the SIOs as explained in the Adjustable Input Level section can be used to construct a comparator. The threshold for the comparator is provided by the SIO's reference generator. The reference generator has the option to set the analog signal routed through the analog global line as threshold for the comparator. Note that a pair of SIO pins share the same threshold.

The digital input path in Figure 6-10 on page 34 illustrates this functionality. In the figure, 'Reference level' is the analog signal routed through the analog global. The hysteresis feature can also be enabled for the input buffer of the SIO, which increases noise immunity for the comparator.

### 6.4.14 Hot Swap

This section applies only to SIO pins. SIO pins support 'hot swap' capability to plug into an application without loading the signals that are connected to the SIO pins even when no power is applied to the PSoC device. This allows the unpowered PSoC to maintain a high impedance load to the external device while also preventing the PSoC from being powered through a SIO pin's protection diode.

Powering the device up or down while connected to an operational I2C bus may cause transient states on the SIO pins. The overall I2C bus design should take this into account.

### 6.4.15 Over Voltage Tolerance

All I/O pins provide an over voltage tolerance feature at any operating VDD.

- There are no current limitations for the SIO pins as they present a high impedance load to the external circuit.

- The GPIO pins must be limited to 100 µA using a current limiting resistor. GPIO pins clamp the pin voltage to approximately one diode above the VDDIO supply.

- In case of a GPIO pin configured for analog input/output, the analog voltage on the pin must not exceed the VDDIO supply voltage to which the GPIO belongs.

A common application for this feature is connection to a bus such as I<sup>2</sup>C where different devices are running from different supply voltages. In the I<sup>2</sup>C case, the PSoC chip is configured into the Open Drain, Drives Low mode for the SIO pin. This allows an external pull up to pull the I<sup>2</sup>C bus voltage above the PSoC pin supply. For example, the PSoC chip could operate at 1.8 V, and an external device could run from 5 V. Note that the SIO pin's VIH and VIL levels are determined by the associated VDDIO supply pin.

The SIO pin must be in one of the following modes: 0 (high impedance analog), 1 (high impedance digital), or 4 (open drain drives low). See Figure 6-12 for details. Absolute maximum ratings for the device must be observed for all I/O pins.

### 6.4.16 Reset Configuration

While reset is active all I/Os are reset to and held in the High Impedance Analog state. After reset is released, the state can be reprogrammed on a port-by-port basis to pull down or pull up. To ensure correct reset operation, the port reset configuration data is stored in special nonvolatile registers. The stored reset data is automatically transferred to the port reset configuration registers at reset release.

### 6.4.17 Low Power Functionality

In all low power modes the I/O pins retain their state until the part is awakened and changed or reset. To awaken the part, use a pin interrupt, because the port interrupt logic continues to function in all low power modes.

### 6.4.18 Special Pin Functionality

Some pins on the device include additional special functionality in addition to their GPIO or SIO functionality. The specific special function pins are listed in "Pinouts" on page 6. The special features are:

### ■ Digital

- 4 to 25 MHz crystal oscillator

- □ 32.768 kHz crystal oscillator

- Wake from sleep on I<sup>2</sup>C address match. Any pin can be used for I<sup>2</sup>C if wake from sleep is not required.

- JTAG interface pins

- □ SWD interface pins

- SWV interface pins

- □ TRACEPORT interface pins

- External reset

### Analog

- Opamp inputs and outputs

- □ High current IDAC outputs

- External reference inputs

### 6.4.19 JTAG Boundary Scan

The device supports standard JTAG boundary scan chains on all pins for board level test.

### 7. Digital Subsystem

The digital programmable system creates application specific combinations of both standard and advanced digital peripherals and custom logic functions. These peripherals and logic are then interconnected to each other and to any pin on the device, providing a high level of design flexibility and IP security.

The features of the digital programmable system are outlined here to provide an overview of capabilities and architecture. You do not need to interact directly with the programmable digital system at the hardware and register level. PSoC Creator provides a high level schematic capture graphical interface to automatically place and route resources similar to PLDs.

The main components of the digital programmable system are:

- Universal Digital Blocks (UDB) These form the core functionality of the digital programmable system. UDBs are a collection of uncommitted logic (PLD) and structural logic (Datapath) optimized to create all common embedded peripherals and customized functionality that are application or design specific.

- Universal Digital Block array UDB blocks are arrayed within a matrix of programmable interconnect. The UDB array structure is homogeneous and allows for flexible mapping of digital functions onto the array. The array supports extensive and flexible routing interconnects between UDBs and the Digital System Interconnect.

Document Number: 001-84935 Rev. \*L Page 38 of 131

The main component blocks of the UDB are:

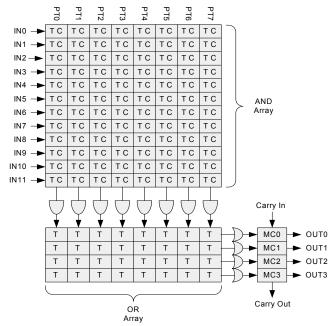

- PLD blocks There are two small PLDs per UDB. These blocks take inputs from the routing array and form registered or combinational sum-of-products logic. PLDs are used to implement state machines, state bits, and combinational logic equations. PLD configuration is automatically generated from graphical primitives.

- Datapath Module This 8-bit wide datapath contains structured logic to implement a dynamically configurable ALU, a variety of compare configurations and condition generation. This block also contains input/output FIFOs, which are the primary parallel data interface between the CPU/DMA system and the UDB.

- Status and Control Module The primary role of this block is to provide a way for CPU firmware to interact and synchronize with UDB operation.

- Clock and Reset Module This block provides the UDB clocks and reset selection and control.

### 7.2.1 PLD Module

The primary purpose of the PLD blocks is to implement logic expressions, state machines, sequencers, look up tables, and decoders. In the simplest use model, consider the PLD blocks as a standalone resource onto which general purpose RTL is synthesized and mapped. The more common and efficient use model is to create digital functions from a combination of PLD and datapath blocks, where the PLD implements only the random logic and state portion of the function while the datapath (ALU) implements the more structured elements.

Figure 7-3. PLD 12C4 Structure

One 12C4 PLD block is shown in Figure 7-3. This PLD has 12 inputs, which feed across eight product terms. Each product term (AND function) can be from 1 to 12 inputs wide, and in a given product term, the true (T) or complement (C) of each input can be selected. The product terms are summed (OR function) to create the PLD outputs. A sum can be from 1 to 8 product terms wide. The 'C' in 12C4 indicates that the width of the OR gate (in this case 8) is constant across all outputs (rather than variable as in a 22V10 device). This PLA like structure gives maximum flexibility and insures that all inputs and outputs are permutable for ease of allocation by the software tools. There are two 12C4 PLDs in each UDB.

### 7.2.2 Datapath Module

The datapath contains an 8-bit single cycle ALU, with associated compare and condition generation logic. This datapath block is optimized to implement embedded functions, such as timers, counters, integrators, PWMs, PRS, CRC, shifters and dead band generators and many others.

### 8.1 Analog Routing

The PSoC 5LP family of devices has a flexible analog routing architecture that provides the capability to connect GPIOs and different analog blocks, and also route signals between different analog blocks. One of the strong points of this flexible routing architecture is that it allows dynamic routing of input and output connections to the different analog blocks.

For information on how to make pin selections for optimal analog routing, refer to the application note, AN58304 - PSoC® 3 and PSoC® 5 - Pin Selection for Analog Designs.

### 8.1.1 Features

- Flexible, configurable analog routing architecture

- 16 Analog globals (AG) and two analog mux buses (AMUXBUS) to connect GPIOs and the analog blocks

- Each GPIO is connected to one analog global and one analog mux bus

- 8 Analog local buses (abus) to route signals between the different analog blocks

- Multiplexers and switches for input and output selection of the analog blocks

### 8.1.2 Functional Description

Analog globals (AGs) and analog mux buses (AMUXBUS) provide analog connectivity between GPIOs and the various analog blocks. There are 16 AGs in the PSoC 5LP family. The analog routing architecture is divided into four quadrants as shown in Figure 8-2. Each quadrant has four analog globals (AGL[0..3], AGL[4..7], AGR[0..3], AGR[4..7]). Each GPIO is connected to the corresponding AG through an analog switch. The analog mux bus is a shared routing resource that connects to every GPIO through an analog switch. There are two AMUXBUS routes in PSoC 5LP, one in the left half (AMUXBUSL) and one in the right half (AMUXBUSR), as shown in Figure 8-2.

Analog local buses (abus) are routing resources located within the analog subsystem and are used to route signals between different analog blocks. There are eight abus routes in PSoC 5LP, four in the left half (abusl [0:3]) and four in the right half (abusr [0:3]) as shown in Figure 8-2. Using the abus saves the analog globals and analog mux buses from being used for interconnecting the analog blocks.

Multiplexers and switches exist on the various buses to direct signals into and out of the analog blocks. A multiplexer can have only one connection on at a time, whereas a switch can have multiple connections on simultaneously. In Figure 8-2, multiplexers are indicated by grayed ovals and switches are indicated by transparent ovals.

### 8.12 Sample and Hold

The main application for a sample and hold, is to hold a value stable while an ADC is performing a conversion. Some applications require multiple signals to be sampled simultaneously, such as for power calculations (V and I). PSoC Creator offers a sample and hold component to support this function.

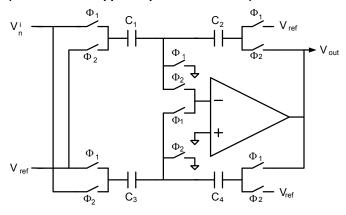

# Figure 8-14. Sample and Hold Topology ( $\Phi$ 1 and $\Phi$ 2 are opposite phases of a clock)

### 8.12.1 Down Mixer

The S+H can be used as a mixer to down convert an input signal. This circuit is a high bandwidth passive sample network that can sample input signals up to 14 MHz. This sampled value is then held using the opamp with a maximum clock rate of 4 MHz. The output frequency is at the difference between the input frequency and the highest integer multiple of the Local Oscillator that is less than the input.

### 8.12.2 First Order Modulator - SC Mode

A first order modulator is constructed by placing the switched capacitor block in an integrator mode and using a comparator to provide a 1-bit feedback to the input. Depending on this bit, a reference voltage is either subtracted or added to the input signal. The block output is the output of the comparator and not the integrator in the modulator case. The signal is downshifted and buffered and then processed by a decimator to make a delta-sigma converter or a counter to make an incremental converter. The accuracy of the sampled data from the first-order modulator is determined from several factors.

The main application for this modulator is for a low frequency ADC with high accuracy. Applications include strain gauges, thermocouples, precision voltage, and current measurement

# 9. Programming, Debug Interfaces, Resources

The Cortex-M3 has internal debugging components, tightly integrated with the CPU, providing the following features:

- JTAG or SWD access

- Flash Patch and Breakpoint (FPB) block for implementing breakpoints and code patches

- Data Watchpoint and Trigger (DWT) block for implementing watchpoints, trigger resources, and system profiling

- Embedded Trace Macrocell (ETM) for instruction trace

- Instrumentation Trace Macrocell (ITM) for support of printf-style debugging

PSoC devices include extensive support for programming, testing, debugging, and tracing both hardware and firmware. Four interfaces are available: JTAG, SWD, SWV, and TRACEPORT. JTAG and SWD support all programming and debug features of the device. JTAG also supports standard JTAG scan chains for board level test and chaining multiple JTAG devices to a single JTAG connection. The SWV and TRACEPORT provide trace output from the DWT, ETM, and ITM. TRACEPORT is faster but uses more pins. SWV is slower but uses only one pin.

For more information on PSoC 5 programming, refer to the application note PSoC 5 Device Programming Specifications.

Cortex-M3 debug and trace functionality enables full device debugging in the final system using the standard production device. It does not require special interfaces, debugging pods, simulators, or emulators. Only the standard programming connections are required to fully support debug.

The PSoC Creator IDE software provides fully integrated programming and debug support for PSoC devices. The low cost MiniProg3 programmer and debugger is designed to provide full programming and debug support of PSoC devices in conjunction with the PSoC Creator IDE. PSoC JTAG, SWD, and SWV interfaces are fully compatible with industry standard third party tools.

All Cortex-M3 debug and trace modules are disabled by default and can only be enabled in firmware. If not enabled, the only way to reenable them is to erase the entire device, clear flash protection, and reprogram the device with new firmware that enables them. Disabling debug and trace features, robust flash protection, and hiding custom analog and digital functionality inside the PSoC device provide a level of security not possible with multichip application solutions. Additionally, all device interfaces can be permanently disabled (Device Security) for applications concerned about phishing attacks due to a maliciously reprogrammed device. Permanently disabling interfaces is not recommended in most applications because the designer then cannot access the device later. Because all programming, debug, and test interfaces are disabled when Device Security is enabled, PSoCs with Device Security enabled may not be returned for failure analysis.

### 9.1 JTAG Interface

The IEEE 1149.1 compliant JTAG interface exists on four or five pins (the nTRST pin is optional). The JTAG clock frequency can be up to 12 MHz, or 1/3 of the CPU clock frequency for 8 and 16-bit transfers, or 1/5 of the CPU clock frequency for 32-bit

transfers, whichever is least. By default, the JTAG pins are enabled on new devices but the JTAG interface can be disabled, allowing these pins to be used as General Purpose I/O (GPIO) instead. The JTAG interface is used for programming the flash memory, debugging, I/O scan chains, and JTAG device chaining.

$V_{\text{DD}}$ Host Programmer PSoC 5  $V_{\text{DDD}}\text{, }V_{\text{DDA}}\text{, }V_{\text{DDIO0}}\text{, }V_{\text{DDIO1}}\text{, }V_{\text{DDIO2}}\text{, }V_{\text{DDIO3}}\text{ }^{1\text{, }2\text{, }3\text{, }4}$  $V_{DD}$ **TCK** TCK (P1[1] TMS (P1[0]) 5 TMS TDO TDI (P1[4]) TDI TDO (P1[3]) nTRST (P1[5]) 6 nTRST 6 **XRFS** XRES 4 GND VSSD, VSSA **GND**

Figure 9-1. JTAG Interface Connections between PSoC 5LP and Programmer

<sup>&</sup>lt;sup>1</sup> The voltage levels of Host Programmer and the PSoC 5 voltage domains involved in Programming should be same. The Port 1 JTAG pins and XRES pin are powered by V<sub>DDIO1</sub>. So, V<sub>DDIO1</sub> of PSoC 5 should be at same voltage level as host V<sub>DD</sub>. Rest of PSoC 5 voltage domains (V<sub>DDD</sub>, V<sub>DDA</sub>, V<sub>DDIO2</sub>, V<sub>DDIO2</sub>, V<sub>DDIO3</sub>) need not be at the same voltage level as host Programmer.

<sup>&</sup>lt;sup>2</sup> Vdda must be greater than or equal to all other power supplies (Vddd, Vddio's) in PSoC 5.

<sup>&</sup>lt;sup>3</sup> For Power cycle mode Programming, XRES pin is not required. But the Host programmer must have the capability to toggle power (Vddd, Vdda, All Vddio's) to PSoC 5. This may typically require external interface circuitry to toggle power which will depend on the programming setup. The power supplies can be brought up in any sequence, however, once stable, VDDA must be greater than or equal to all other supplies.

<sup>&</sup>lt;sup>4</sup> For JTAG Programming, Device reset can also be done without connecting to the XRES pin or Power cycle mode by using the TMS,TCK,TDI, TDO pins of PSoC 5, and writing to a specific register. But this requires that the DPS setting in NVL is not equal to "Debug Ports Disabled".

<sup>&</sup>lt;sup>5</sup> By default, PSoC 5 is configured for 4-wire JTAG mode unless user changes the DPS setting. So the TMS pin is unidirectional. But if the DPS setting is changed to non-JTAG mode, the TMS pin in JTAG is bi-directional as the SWD Protocol has to be used for acquiring the PSoC 5 device initially. After switching from SWD to JTAG mode, the TMS pin will be uni-directional. In such a case, unidirectional buffer should not be used on TMS line.

nTRST JTAG pin (P1[5]) cannot be used to reset the JTAG TAP controlller during first time programming of PSoC 5 as the default setting is 4-wire JTAG (nTRST disabled). Use the TMS, TCK pins to do a reset of JTAG TAP controller.

### Table 11-2. DC Specifications (continued)

| Parameter                       | Description                                                                                                                                                 | Conditions                                                          |            | Min | Тур | Max | Units |

|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|------------|-----|-----|-----|-------|

| I <sub>DD</sub> <sup>[22]</sup> | Sleep Mode <sup>[23]</sup>                                                                                                                                  |                                                                     | •          |     |     |     | •     |

|                                 |                                                                                                                                                             | $V_{DD} = V_{DDIO} = 1$<br>4.5–5.5 V                                | Γ = –40 °C | _   | 1.9 | 3.1 | μΑ    |

|                                 |                                                                                                                                                             | 4.5–5.5 V                                                           | Γ = 25 °C  | _   | 2.4 | 3.6 | 7 1   |

|                                 |                                                                                                                                                             | Т                                                                   | Γ = 85 °C  | _   | 5   | 16  |       |

|                                 | CPU = OFF                                                                                                                                                   |                                                                     | Γ = 105 °C | _   | 5   | 16  |       |

|                                 | RTC = ON (= ECO32K ON, in low-power mode)<br>Sleep timer = ON (= ILO ON at 1 kHz) <sup>[24]</sup>                                                           | $V_{DD} = V_{DDIO} = $ 7 2.7–3.6 V                                  | Γ = –40 °C | _   | 1.7 | 3.1 |       |

|                                 | WDT = OFF                                                                                                                                                   | 2.7–3.6 V                                                           | Γ = 25 °C  | _   | 2   | 3.6 |       |

|                                 | I <sup>2</sup> C Wake = OFF<br>Comparator = OFF                                                                                                             |                                                                     | Γ = 85 °C  | _   | 4.2 | 16  |       |

|                                 | POR' = ON                                                                                                                                                   |                                                                     | Γ = 105 °C | _   | 4.2 | 16  |       |

|                                 | Boost = OFF<br>SIO pins in single ended input, unregulated output mode                                                                                      | V <sub>DD</sub> = V <sub>DDIO</sub> = 1<br>1.71–1.95 V              | Γ = –40 °C | _   | 1.6 | 3.1 |       |

|                                 | pino in origie criaca inpat, arriegalatea output mode                                                                                                       | 1.71–1.95 V                                                         | Γ = 25 °C  | _   | 1.9 | 3.6 |       |

|                                 |                                                                                                                                                             |                                                                     | Γ = 85 °C  | _   | 4.2 | 16  |       |

|                                 |                                                                                                                                                             | 7                                                                   | Γ = 105 °C | _   | 4.2 | 16  |       |

|                                 | Comparator = ON CPU = OFF RTC = OFF Sleep timer = OFF WDT = OFF I2C Wake = OFF POR = ON Boost = OFF SIO pins in single ended input, unregulated output mode | V <sub>DD</sub> = V <sub>DDI</sub> = 2.7–3.6 V <sup>[25]</sup>      | Γ = 25 °C  | -   | 3   | 4.2 | μА    |

|                                 | I2C Wake = ON CPU = OFF RTC = OFF Sleep timer = OFF WDT = OFF Comparator = OFF POR = ON Boost = OFF SIO pins in single ended input, unregulated output mode | V <sub>DD</sub> = V <sub>DDQ</sub> = 1<br>2.7–3.6 V <sup>[29]</sup> | Γ = 25 °C  | -   | 1.7 | 3.6 | μА    |

### Notes

<sup>22.</sup> The current consumption of additional peripherals that are implemented only in programmed logic blocks can be found in their respective datasheets, available in PSoC Creator, the integrated design environment. To estimate total current, find CPU current at frequency of interest and add peripheral currents for your particular system from the device datasheet and component datasheets.

23. If V<sub>CCD</sub> and V<sub>CCA</sub> are externally regulated, the voltage difference between V<sub>CCD</sub> and V<sub>CCA</sub> must be less than 50 mV.

24. Sleep timer generates periodic interrupts to wake up the CPU. This specification applies only to those times that the CPU is off.

<sup>25.</sup> Based on device characterization (Not production tested).

Table 11-11. SIO AC Specifications<sup>[39]</sup>

| Parameter | Description                                                                                | Conditions                               | Min | Тур | Max | Units |

|-----------|--------------------------------------------------------------------------------------------|------------------------------------------|-----|-----|-----|-------|

| TriseF    | Rise time in Fast Strong Mode (90/10%)                                                     | Cload = 25 pF, V <sub>DDIO</sub> = 3.3 V | -   | _   | 12  | ns    |

| TfallF    | Fall time in Fast Strong Mode (90/10%)                                                     | Cload = 25 pF, V <sub>DDIO</sub> = 3.3 V | -   | _   | 12  | ns    |

| TriseS    | Rise time in Slow Strong Mode (90/10%)                                                     | Cload = 25 pF, V <sub>DDIO</sub> = 3.0 V | -   | _   | 75  | ns    |

| TfallS    | Fall time in Slow Strong Mode (90/10%)                                                     | Cload = 25 pF, V <sub>DDIO</sub> = 3.0 V | -   | _   | 60  | ns    |

|           | SIO output operating frequency                                                             |                                          |     |     |     |       |

|           | 2.7 V < V <sub>DDIO</sub> < 5.5 V, Unregulated output (GPIO) mode, fast strong drive mode  | 90/10% V <sub>DDIO</sub> into 25 pF      | -   | _   | 33  | MHz   |

|           | 1.71 V < V <sub>DDIO</sub> < 2.7 V, Unregulated output (GPIO) mode, fast strong drive mode | 90/10% V <sub>DDIO</sub> into 25 pF      | _   | _   | 16  | MHz   |

| Fsioout   | 3.3 V < V <sub>DDIO</sub> < 5.5 V, Unregulated output (GPIO) mode, slow strong drive mode  | 90/10% V <sub>DDIO</sub> into 25 pF      | -   | -   | 5   | MHz   |

| rsioout   | 1.71 V < V <sub>DDIO</sub> < 3.3 V, Unregulated output (GPIO) mode, slow strong drive mode | 90/10% V <sub>DDIO</sub> into 25 pF      | -   | _   | 4   | MHz   |

|           | 2.7 V < V <sub>DDIO</sub> < 5.5 V, Regulated output mode, fast strong drive mode           | Output continuously switching into 25 pF | -   | _   | 20  | MHz   |

|           | 1.71 V < V <sub>DDIO</sub> < 2.7 V, Regulated output mode, fast strong drive mode          | Output continuously switching into 25 pF | -   | _   | 10  | MHz   |

|           | 1.71 V < V <sub>DDIO</sub> < 5.5 V, Regulated output mode, slow strong drive mode          | Output continuously switching into 25 pF | -   | _   | 2.5 | MHz   |

| Fsioin    | SIO input operating frequency                                                              |                                          |     |     |     |       |

| 3011      | 1.71 V ≤ V <sub>DDIO</sub> ≤ 5.5 V                                                         | 90/10% V <sub>DDIO</sub>                 | _   | _   | 33  | MHz   |

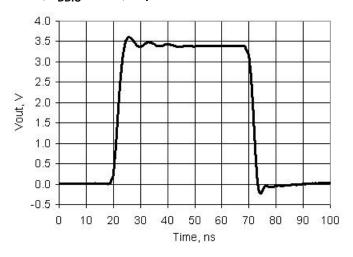

Figure 11-20. SIO Output Rise and Fall Times, Fast Strong Mode,  $V_{DDIO}$  = 3.3 V, 25 pF Load

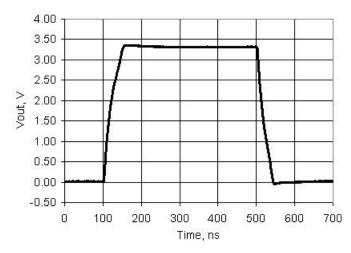

Figure 11-21. SIO Output Rise and Fall Times, Slow Strong Mode,  $V_{DDIO} = 3.3 \text{ V}$ , 25 pF Load

### Note

39. Based on device characterization (Not production tested).

### 11.5.5 Analog Globals

### Table 11-26. Analog Globals DC Specifications

| Parameter                                            | Description                            | Conditions                | Min  | Тур  | Max  | Units |

|------------------------------------------------------|----------------------------------------|---------------------------|------|------|------|-------|

| Rppag                                                | Resistance pin-to-pin through          | V <sub>DDA</sub> = 3.0 V  | _    | 1500 | 2200 | Ω     |

| P2[4], AGL0, DSM INP, AGL1,<br>P2[5] <sup>[50]</sup> | V <sub>DDA</sub> = 1.71 V              | -                         | 1200 | 1700 | Ω    |       |

| Rppmuxbus                                            | Resistance pin-to-pin through          | V <sub>DDA</sub> = 3.0 V  | _    | 700  | 1100 | Ω     |

|                                                      | P2[3], amuxbusL, P2[4] <sup>[50]</sup> | V <sub>DDA</sub> = 1.71 V | _    | 600  | 900  | Ω     |

### Table 11-27. Analog Globals AC Specifications

| Parameter | Description                                                | Conditions                      | Min | Тур | Max | Units |

|-----------|------------------------------------------------------------|---------------------------------|-----|-----|-----|-------|

|           | Inter-pair crosstalk for analog routes <sup>[51, 52]</sup> |                                 | 106 | I   | ı   | dB    |

| BWag      | Analog globals 3 db bandwidth <sup>[52]</sup>              | V <sub>DDA</sub> = 3.0 V, 25 °C | -   | 26  | -   | MHz   |

### 11.5.6 Comparator

# Table 11-28. Comparator DC Specifications<sup>[53]</sup>

| Parameter         | Description                                       | Conditions                                                           | Min              | Тур | Max                        | Units |

|-------------------|---------------------------------------------------|----------------------------------------------------------------------|------------------|-----|----------------------------|-------|

| Vos               | Input offset voltage in fast mode                 | Factory trim, $V_{DDA} > 2.7 \text{ V}$ , $V_{IN} \ge 0.5 \text{ V}$ | -                |     | 10                         | mV    |

|                   | Input offset voltage in slow mode                 | Factory trim, Vin ≥ 0.5 V                                            | _                |     | 9                          | mV    |

| V                 | Input offset voltage in fast mode                 | Custom trim                                                          | _                | -   | 4                          | mV    |

| V <sub>OS</sub>   | Input offset voltage in slow mode <sup>[53]</sup> | Custom trim                                                          | _                | _   | 4                          | mV    |

| V <sub>OS</sub>   | Input offset voltage in ultra low power mode      |                                                                      | -                | ±12 | -                          | mV    |

| TCVos             | Temperature coefficient, input offset             | V <sub>CM</sub> = V <sub>DDA</sub> / 2, fast mode                    | _                | 63  | 85                         | μV/°C |

|                   | voltage                                           | V <sub>CM</sub> = V <sub>DDA</sub> / 2, slow mode                    | _                | 15  | 20                         |       |

| V <sub>HYST</sub> | Hysteresis                                        | Hysteresis enable mode                                               | _                | 10  | 32                         | mV    |

| V <sub>ICM</sub>  | Input common mode voltage                         | High current / fast mode                                             | $V_{SSA}$        | _   | $V_{DDA}$                  | V     |

|                   |                                                   | Low current / slow mode                                              | $V_{SSA}$        | _   | $V_{DDA}$                  | V     |

|                   |                                                   | Ultra low power mode                                                 | V <sub>SSA</sub> | _   | V <sub>DDA</sub> –<br>1.15 | V     |

| CMRR              | Common mode rejection ratio                       |                                                                      | _                | 50  | _                          | dB    |

| I <sub>CMP</sub>  | High current mode/fast mode                       |                                                                      | _                | -   | 400                        | μA    |

|                   | Low current mode/slow mode                        |                                                                      | _                | -   | 100                        | μA    |

|                   | Ultra low power mode                              |                                                                      | _                | 6   | _                          | μΑ    |

# Table 11-29. Comparator AC Specifications<sup>[53]</sup>

| Parameter         | Description                         | Conditions                           | Min | Тур | Max | Units |

|-------------------|-------------------------------------|--------------------------------------|-----|-----|-----|-------|

| T <sub>RESP</sub> | Response time, high current mode    | 50 mV overdrive, measured pin-to-pin | _   | 75  | 110 | ns    |

|                   | Response time, low current mode     | 50 mV overdrive, measured pin-to-pin | _   | 155 | 200 | ns    |

|                   | Response time, ultra low power mode | 50 mV overdrive, measured pin-to-pin | _   | 55  | _   | μs    |

- 50. Based on device characterization (Not production tested).

- 51. This value is calculated, not measured.

<sup>52.</sup> Pin P6[4] to del-sig ADC input; calculated, not measured.

53. The recommended procedure for using a custom trim value for the on-chip comparators are found in the TRM.

Table 11-30. IDAC DC Specifications (continued)

| Parameter       | Description                          | Conditions                                                                                       | Min | Тур  | Max | Units |

|-----------------|--------------------------------------|--------------------------------------------------------------------------------------------------|-----|------|-----|-------|

| DNL             | Differential nonlinearity            | Sink mode, range = 255 $\mu$ A,<br>Rload = 2.4 $k\Omega$ , Cload = 15 pF                         | -   | ±0.3 | ±1  | LSB   |

| 1               |                                      | Source mode, range = 255 $\mu$ A,<br>Rload = 2.4 $k\Omega$ , Cload = 15 pF                       | -   | ±0.3 | ±1  | LSB   |

|                 |                                      | Source mode, range = 31.875 $\mu$ A,<br>Rload = 20 k $\Omega$ , Cload = 15 pF <sup>[55]</sup>    | -   | ±0.2 | ±1  | LSB   |

|                 |                                      | Sink mode, range = 31.875 $\mu$ A,<br>Rload = 20 k $\Omega$ , Cload = 15 pF <sup>[55]</sup>      | -   | ±0.2 | ±1  | LSB   |

|                 |                                      | Source mode, range = 2.0 4 mA,<br>Rload = 600 $\Omega$ , Cload = 15 pF <sup>[55]</sup>           | -   | ±0.2 | ±1  | LSB   |

|                 |                                      | Sink mode, range = 2.0 4 mA,<br>Rload = 600 $\Omega$ , Cload = 15 pF <sup>[55]</sup>             | _   | ±0.2 | ±1  | LSB   |

| Vcompliance     | Dropout voltage, source or sink mode | Voltage headroom at max current, Rload to $V_{DDA}$ or Rload to $V_{SSA}$ , Vdiff from $V_{DDA}$ | 1   | _    | _   | V     |

| I <sub>DD</sub> | Operating current, code = 0          | Slow mode, source mode, range = 31.875 µA                                                        | -   | 44   | 100 | μA    |

|                 |                                      | Slow mode, source mode, range = 255 µA,                                                          | -   | 33   | 100 | μA    |

|                 |                                      | Slow mode, source mode, range = 2.04 mA                                                          | -   | 33   | 100 | μA    |

|                 |                                      | Slow mode, sink mode, range = 31.875 µA                                                          | _   | 36   | 100 | μA    |

|                 |                                      | Slow mode, sink mode, range = 255 μA                                                             | -   | 33   | 100 | μA    |

|                 |                                      | Slow mode, sink mode, range = 2.04 mA                                                            | -   | 33   | 100 | μA    |

|                 |                                      | Fast mode, source mode, range = 31.875 µA                                                        | _   | 310  | 500 | μA    |

|                 |                                      | Fast mode, source mode, range = 255 μA                                                           | _   | 305  | 500 | μA    |

|                 |                                      | Fast mode, source mode, range = 2.04 mA                                                          | _   | 305  | 500 | μA    |

|                 |                                      | Fast mode, sink mode, range = 31.875 µA                                                          | -   | 310  | 500 | μΑ    |

|                 |                                      | Fast mode, sink mode, range = 255 μA                                                             | _   | 300  | 500 | μA    |

|                 |                                      | Fast mode, sink mode, range = 2.04 mA                                                            | _   | 300  | 500 | μA    |

Note 55. Based on device characterization (Not production tested).

# Table 11-50. Fixed I<sup>2</sup>C AC Specifications<sup>[67]</sup>

| Parameter | Description | Conditions | Min | Тур | Max | Units |

|-----------|-------------|------------|-----|-----|-----|-------|

|           | Bit rate    |            | _   | -   | 1   | Mbps  |

### 11.6.5 Controller Area Network

# Table 11-51. CAN DC Specifications<sup>[67, 68]</sup>

| Parameter | Description               | Conditions | Min | Тур | Max | Units |

|-----------|---------------------------|------------|-----|-----|-----|-------|

| $I_{DD}$  | Block current consumption |            | ı   | ı   | 200 | μA    |

# Table 11-52. CAN AC Specifications<sup>[67, 68]</sup>

| Parameter | Description | Conditions          | Min | Тур | Max | Units |

|-----------|-------------|---------------------|-----|-----|-----|-------|

|           | Bit rate    | Minimum 8 MHz clock | -   | _   | 1   | Mbit  |

### 11.6.6 Digital Filter Block

# Table 11-53. DFB DC Specifications<sup>[68]</sup>

| Parameter | Description           | Conditions                     | Min | Тур  | Max  | Units |

|-----------|-----------------------|--------------------------------|-----|------|------|-------|

|           | DFB operating current | 64-tap FIR at F <sub>DFB</sub> |     |      |      |       |

|           |                       | 500 kHz (6.7 ksps)             | _   | 0.16 | 0.27 | mA    |

|           |                       | 1 MHz (13.4 ksps)              | -   | 0.33 | 0.53 | mA    |

|           |                       | 10 MHz (134 ksps)              | _   | 3.3  | 5.3  | mA    |

|           |                       | 48 MHz (644 ksps)              | _   | 15.7 | 25.5 | mA    |

|           |                       | 80 MHz (1.07 Msps)             | _   | 26.0 | 42.5 | mA    |

# Table 11-54. DFB AC Specifications<sup>[68]</sup>

| Parameter        | Description             | Conditions | Min | Тур | Max   | Units |

|------------------|-------------------------|------------|-----|-----|-------|-------|

| F <sub>DFB</sub> | DFB operating frequency |            | DC  | -   | 80.01 | MHz   |

### 11.6.7 USB

### Table 11-55. USB DC Specifications

| Parameter                   | Description                                         | Conditions                                                                                          | Min  | Тур | Max  | Units |

|-----------------------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------|------|-----|------|-------|

| V <sub>USB_5</sub>          | Device supply (V <sub>DDD</sub> ) for USB operation | USB configured, USB regulator enabled                                                               | 4.35 | -   | 5.25 | V     |

| V <sub>USB_3.3</sub>        |                                                     | USB configured, USB regulator bypassed                                                              | 3.15 | -   | 3.6  | V     |

| V <sub>USB_3</sub>          |                                                     | USB configured, USB regulator bypassed <sup>[69]</sup>                                              | 2.85 | -   | 3.6  | V     |

| I <sub>USB_Configured</sub> | Device supply current in device                     | $V_{DDD}$ = 5 V, $F_{CPU}$ = 1.5 MHz                                                                | ı    | 10  | _    | mA    |

|                             | active mode, bus clock and IMO = 24 MHz             | $V_{DDD} = 3.3 \text{ V}, F_{CPU} = 1.5 \text{ MHz}$                                                | _    | 8   | _    | mA    |

| I <sub>USB_Suspended</sub>  | Device supply current in device sleep mode          | V <sub>DDD</sub> = 5 V, connected to USB<br>host, PICU configured to wake on<br>USB resume signal   | _    | 0.5 | _    | mA    |

|                             |                                                     | V <sub>DDD</sub> = 5 V, disconnected from USB host                                                  | -    | 0.3 | _    | mA    |

|                             |                                                     | V <sub>DDD</sub> = 3.3 V, connected to USB<br>host, PICU configured to wake on<br>USB resume signal | _    | 0.5 | _    | mA    |

|                             |                                                     | V <sub>DDD</sub> = 3.3 V, disconnected from USB host                                                | 1    | 0.3 | -    | mA    |

### Notes

<sup>67.</sup> Based on device characterization (Not production tested).

<sup>68.</sup> Refer to ISO 11898 specification for details.

<sup>69.</sup> Rise/fall time matching (TR) not guaranteed, see Table 11-15 on page 82.

### 11.7 Memory

Specifications are valid for –40  $^{\circ}$ C  $\leq$  T<sub>A</sub>  $\leq$  105  $^{\circ}$ C and T<sub>J</sub>  $\leq$  120  $^{\circ}$ C, except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted.

11.7.1 Flash

### Table 11-57. Flash DC Specifications

| Parameter | Description               | Conditions       | Min  | Тур | Max | Units |

|-----------|---------------------------|------------------|------|-----|-----|-------|

|           | Erase and program voltage | $V_{ m DDD}$ pin | 1.71 | _   | 5.5 | V     |

### Table 11-58. Flash AC Specifications

| Parameter          | Description                                                                | Conditions                                                                                                                   | Min | Тур | Max | Units   |

|--------------------|----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|---------|

| T <sub>WRITE</sub> | Row write time (erase + program)                                           |                                                                                                                              | -   | 15  | 20  | ms      |

| T <sub>ERASE</sub> | Row erase time                                                             |                                                                                                                              | -   | 10  | 13  | ms      |

|                    | Row program time                                                           |                                                                                                                              | -   | 5   | 7   | ms      |

| T <sub>BULK</sub>  | Bulk erase time (256 KB)                                                   |                                                                                                                              | _   | _   | 140 | ms      |

|                    | Sector erase time (16 KB)                                                  |                                                                                                                              | _   | -   | 15  | ms      |

| T <sub>PROG</sub>  | Total device programming time                                              | No overhead <sup>[71]</sup>                                                                                                  | -   | 5   | 7.5 | seconds |

|                    | Flash data retention time, retention period measured from last erase cycle | Average ambient temp. T <sub>A</sub> ≤ 55 °C, 100 K erase/program cycles                                                     | 20  | -   | _   | years   |

|                    |                                                                            | Average ambient temp. T <sub>A</sub> ≤ 85 °C, 10 K erase/program cycles                                                      | 10  | -   | -   |         |

|                    |                                                                            | Ambient temp. T <sub>A</sub> ≤ 105 °C,<br>10 K erase/program cycles,<br>≤ one year at T <sub>A</sub> ≥ 75 °C <sup>[72]</sup> | 10  | _   | _   |         |

### 11.7.2 EEPROM

### Table 11-59. EEPROM DC Specifications

| Parameter | Description               | Conditions | Min  | Тур | Max | Units |

|-----------|---------------------------|------------|------|-----|-----|-------|

|           | Erase and program voltage |            | 1.71 | _   | 5.5 | V     |

### Table 11-60. EEPROM AC Specifications

| Parameter          | Description                                                                 | Conditions                                                                                                                 | Min | Тур | Max | Units |

|--------------------|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| T <sub>WRITE</sub> | Single row erase/write cycle time                                           |                                                                                                                            | _   | 10  | 20  | ms    |

|                    | EEPROM data retention time, retention period measured from last erase cycle | Average ambient temp, T <sub>A</sub> ≤ 25 °C, 1M erase/program cycles                                                      | 20  | _   | -   | years |

|                    |                                                                             | Average ambient temp, T <sub>A</sub> ≤ 55 °C, 100 K erase/program cycles                                                   | 20  | _   | -   |       |

|                    |                                                                             | Average ambient temp. T <sub>A</sub> ≤ 85 °C, 10 K erase/program cycles                                                    | 10  | _   | _   |       |

|                    |                                                                             | Ambient temp. T <sub>A</sub> ≤ 105 °C,<br>10K erase/program cycles,<br>≤ one year at T <sub>A</sub> ≥75 °C <sup>[72]</sup> | 10  | _   | -   |       |

### Notes

Document Number: 001-84935 Rev. \*L Page 108 of 131

<sup>71.</sup> See PSoC 5 Device Programming Specifications for a description of a low-overhead method of programming PSoC 5 flash.

72. Cypress provides a retention calculator to calculate the retention lifetime based on customers' individual temperature profiles for operation over the –40 °C to +105 °C ambient temperature range. Contact customercare@cypress.com.

### 11.9.3 MHz External Crystal Oscillator

For more information on crystal or ceramic resonator selection for the MHzECO, refer to application note AN54439: PSoC 3 and PSoC 5 External Oscillators.

### Table 11-79. MHzECO DC Specifications

| Parameter       | Description                       | Conditions        | Min | Тур | Max | Units |

|-----------------|-----------------------------------|-------------------|-----|-----|-----|-------|

| I <sub>CC</sub> | Operating current <sup>[91]</sup> | 13.56 MHz crystal | _   | 3.8 | -   | mA    |

### Table 11-80. MHzECO AC Specifications

| Parameter | Description             | Conditions | Min | Тур | Max | Units |

|-----------|-------------------------|------------|-----|-----|-----|-------|

| F         | Crystal frequency range |            | 4   | -   | 25  | MHz   |

### 11.9.4 kHz External Crystal Oscillator

# Table 11-81. kHzECO DC Specifications<sup>[91]</sup>

| Parameter       | Description       | Conditions                | Min | Тур  | Max | Units |

|-----------------|-------------------|---------------------------|-----|------|-----|-------|

| I <sub>CC</sub> | Operating current | Low power mode; CL = 6 pF | -   | 0.25 | 1.0 | μA    |

| DL              | Drive level       |                           | _   | _    | 1   | μW    |

# Table 11-82. kHzECO AC Specifications<sup>[91]</sup>

| Parameter       | Description  | Conditions      | Min | Тур    | Max | Units |

|-----------------|--------------|-----------------|-----|--------|-----|-------|

| F               | Frequency    |                 | _   | 32.768 | -   | kHz   |

| T <sub>ON</sub> | Startup time | High power mode | _   | 1      | _   | S     |

### 11.9.5 External Clock Reference

# Table 11-83. External Clock Reference AC Specifications<sup>[91]</sup>

| Parameter | Description              | Conditions                         | Min | Тур | Max | Units |

|-----------|--------------------------|------------------------------------|-----|-----|-----|-------|

|           | External frequency range |                                    | 0   | _   | 33  | MHz   |

|           | Input duty cycle range   | Measured at V <sub>DDIO</sub> /2   | 30  | 50  | 70  | %     |

|           | Input edge rate          | V <sub>IL</sub> to V <sub>IH</sub> | 0.5 | _   | _   | V/ns  |

### 11.9.6 Phase–Locked Loop

### Table 11-84. PLL DC Specifications

| Parameter       | Description           | Conditions               | Min | Тур | Max | Units |

|-----------------|-----------------------|--------------------------|-----|-----|-----|-------|

| I <sub>DD</sub> | PLL operating current | In = 3 MHz, Out = 80 MHz | _   | 650 | _   | μA    |

|                 |                       | In = 3 MHz, Out = 67 MHz | _   | 400 | _   | μA    |

|                 |                       | In = 3 MHz, Out = 24 MHz | _   | 200 | -   | μΑ    |

### Table 11-85. PLL AC Specifications

| Parameter   | Description                                | Conditions          | Min | Тур | Max | Units |

|-------------|--------------------------------------------|---------------------|-----|-----|-----|-------|

| Fpllin      | PLL input frequency <sup>[92]</sup>        |                     | 1   | -   | 48  | MHz   |

|             | PLL intermediate frequency <sup>[93]</sup> | Output of prescaler | 1   | -   | 3   | MHz   |

| Fpllout     | PLL output frequency <sup>[92]</sup>       |                     | 24  | -   | 80  | MHz   |

|             | Lock time at startup                       |                     | _   | _   | 250 | μs    |

| Jperiod-rms | Jitter (rms) <sup>[91]</sup>               |                     | _   | _   | 250 | ps    |

### Notes

- 91. Based on device characterization (Not production tested).

- 92. This specification is guaranteed by testing the PLL across the specified range using the IMO as the source for the PLL.

- 93. PLL input divider, Q, must be set so that the input frequency is divided down to the intermediate frequency range. Value for Q ranges from 1 to 16.

Document Number: 001-84935 Rev. \*L Page 118 of 131

## 12. Ordering Information

In addition to the features listed in Table 12-1, every CY8C56LP device includes: up to 256K flash, 64K SRAM, 2K EEPROM, a precision on—chip voltage reference, precision oscillators, flash, ECC, DMA, a fixed function I<sup>2</sup>C, JTAG/SWD programming and debug, external memory interface, boost, and more. In addition to these features, the flexible UDBs and analog subsection support a wide range of peripherals. To assist you in selecting the ideal part, PSoC Creator makes a part recommendation after you choose the components required by your application. All CY8C56LP derivatives incorporate device and flash security in user-selectable security levels; see the TRM for details.

Table 12-1. CY8C56LP Family with ARM Cortex-M3 CPU

|                   | MCU Core        |            |           |             |                   | An                              | alo | g           |                                     |        |     |          |                      | Dig              | ital   |          |           | I/O[ | 96] |       |          |                         |

|-------------------|-----------------|------------|-----------|-------------|-------------------|---------------------------------|-----|-------------|-------------------------------------|--------|-----|----------|----------------------|------------------|--------|----------|-----------|------|-----|-------|----------|-------------------------|

| Part Number       | CPU Speed (MHz) | Flash (KB) | SRAM (KB) | EEPROM (KB) | LCD Segment Drive | ADCs                            | DAC | Comparators | SC/CT Analog Blocks <sup>[94]</sup> | Opamps | DFB | CapSense | UDBS <sup>[95]</sup> | 16-bit Timer/PWM | FS USB | CAN 2.0b | Total I/O | GPIO | SIO | USBIO | Package  | JTAG ID <sup>[97]</sup> |

| CY8C5668AXI-LP010 | 67              | 256        | 64        | 2           | ~                 | 2x12-bit SAR                    | 4   | 4           | 4                                   | 4      | ~   | ~        | 24                   | 4                | ~      | -        | 72        | 62   | 8   | 2     | 100-TQFP | 0x2E10A069              |

| CY8C5668AXI-LP013 | 67              | 256        | 64        | 2           | ~                 | 2x12-bit SAR                    | 4   | 4           | 4                                   | 4      | ~   | ~        | 24                   | 4                | ~      | ~        | 72        | 62   | 8   | 2     | 100-TQFP | 0x2E10D069              |

| CY8C5668LTI-LP014 | 67              | 256        | 64        | 2           | ~                 | 2x12-bit SAR                    | 4   | 4           | 4                                   | 4      | ~   | ~        | 24                   | 4                | ~      | -        | 48        | 38   | 8   | 2     | 68-QFN   | 0x2E10E069              |

| CY8C5667AXI-LP006 | 67              | 128        | 32        | 2           | ~                 | 2x12-bit SAR                    | 4   | 4           | 4                                   | 4      | ~   | ~        | 24                   | 4                | ~      | _        | 72        | 62   | 8   | 2     | 100-TQFP | 0x2E106069              |

| CY8C5667LTI-LP008 | 67              | 128        | 32        | 2           | ~                 | 2x12-bit SAR                    | 4   | 4           | 4                                   | 4      | ~   | ~        | 24                   | 4                | ~      | _        | 48        | 38   | 8   | 2     | 68-QFN   | 0x2E108069              |

| CY8C5667LTI-LP009 | 67              | 128        | 32        | 2           | ~                 | 2x12-bit SAR                    | 4   | 4           | 4                                   | 4      | ~   | ~        | 24                   | 4                | ~      | ~        | 48        | 38   | 8   | 2     | 68-QFN   | 0x2E109069              |

| CY8C5666AXI-LP001 | 67              | 64         | 16        | 2           | ~                 | 12-bit Del-Sig,<br>1x12-bit SAR | 4   | 4           | 4                                   | 4      | ~   | ~        | 20                   | 4                | -      | -        | 70        | 62   | 8   | 0     | 100-TQFP | 0x2E101069              |

| CY8C5666AXI-LP004 | 67              | 64         | 16        | 2           | ~                 | 12-bit Del-Sig,<br>1x12-bit SAR | 4   | 4           | 4                                   | 4      | ~   | ~        | 20                   | 4                | ~      | ı        | 72        | 62   | 8   | 2     | 100-TQFP | 0x2E104069              |

| CY8C5666AXQ-LP004 | 67              | 64         | 16        | 2           | ~                 | 12-bit Del-Sig,<br>1x12-bit SAR | 4   | 4           | 4                                   | 4      | ~   | ~        | 20                   | 4                | ~      | -        | 72        | 62   | 8   | 2     | 100-TQFP | 0x2E104069              |

| CY8C5666LTI-LP005 | 67              | 64         | 16        | 2           | ~                 | 12-bit Del-Sig,<br>1x12-bit SAR | 4   | 4           | 4                                   | 4      | ~   | ~        | 20                   | 4                | ~      | -        | 48        | 38   | 8   | 2     | 68-QFN   | 0x2E105069              |

| CY8C5667AXI-LP040 | 67              | 128        | 32        | 2           | ~                 | 12-bit Del-Sig,<br>1x12-bit SAR | 4   | 4           | 4                                   | 4      | ~   | ~        | 24                   | 4                | ~      | ı        | 72        | 62   | 8   | 2     | 100-TQFP | 0x2E128069              |

| CY8C5667AXQ-LP040 | 67              | 128        | 32        | 2           | ~                 | 12-bit Del-Sig,<br>1x12-bit SAR | 4   | 4           | 4                                   | 4      | ~   | ~        | 24                   | 4                | ~      | -        | 72        | 62   | 8   | 2     | 100-TQFP | 0x2E128069              |

| CY8C5668AXI-LP034 | 67              | 256        | 64        | 2           | ~                 | 12-bit Del-Sig,<br>1x12-bit SAR | 4   | 4           | 4                                   | 4      | ~   | ~        | 24                   | 4                | ~      | -        | 72        | 62   | 8   | 2     | 100-TQFP | 0x2E122069              |

| CY8C5667LTI-LP041 | 67              | 128        | 32        | 2           | ~                 | 12-bit Del-Sig,<br>1x12-bit SAR | 4   | 4           | 4                                   | 4      | ~   | ~        | 24                   | 4                | ~      | -        | 48        | 38   | 8   | 2     | 68-QFN   | 0x2E129069              |

| CY8C5688AXI-LP099 | 80              | 256        | 64        | 2           | 4                 | 2x12-bit SAR                    | 4   | 4           | 4                                   | 4      | ~   | ~        | 24                   | 4                | ~      | >        | 72        | 62   | 8   | 2     | 100-TQFP | 0x2E163069              |

| CY8C5688LTI-LP086 | 80              | 256        | 64        | 2           | 4                 | 2x12-bit SAR                    | 4   | 4           | 4                                   | 4      | ~   | ~        | 24                   | 4                | ~      | _        | 48        | 38   | 8   | 2     | 68-QFN   | 0x2E156069              |

| CY8C5688FNI-LP211 | 80              | 256        | 64        | 2           | ~                 | 2x12-bit SAR                    | 4   | 4           | 4                                   | 4      | ~   | ~        | 24                   | 4                | ~      | ~        | 72        | 62   | 8   | 2     | 99-WLCSP | 0x2E1D3069              |

### Notes

<sup>94.</sup> Analog blocks support a wide variety of functionality including TIA, PGA, and mixers. See Example Peripherals on page 39 for more information on how analog blocks can be used.

<sup>95.</sup> UDBs support a wide variety of functionality including SPI, LIN, UART, timer, counter, PWM, PRS, and others. Individual functions may use a fraction of a UDB or multiple UDBs. Multiple functions can share a single UDB. See Example Peripherals on page 39 for more information on how UDBs can be used.

<sup>96.</sup> The I/O Count includes all types of digital I/O: GPIO, SIO, and the two USB I/O. See I/O System and Routing on page 32 for details on the functionality of each of these types of I/O.

<sup>97.</sup> The JTAG ID has three major fields. The most significant nibble (left digit) is the version, followed by a 2 byte part number and a 3 nibble manufacturer ID.

# 13. Packaging

### Table 13-1. Package Characteristics

| Parameter      | Description                            | Conditions    | Min | Тур  | Max | Units   |

|----------------|----------------------------------------|---------------|-----|------|-----|---------|

| T <sub>A</sub> | Operating ambient temperature          |               | -40 | 25   | 105 | °C      |

| $T_J$          | Operating junction temperature         |               | -40 | _    | 120 | °C      |

| $T_{JA}$       | Package θ <sub>JA</sub> (68-pin QFN)   |               | _   | 15   | _   | °C/Watt |

| $T_JA$         | Package θ <sub>JA</sub> (100-pin TQFP) |               | _   | 34   | _   | °C/Watt |

| $T_JC$         | Package θ <sub>JC</sub> (68-pin QFN)   |               | _   | 13   | _   | °C/Watt |

| $T_JC$         | Package θ <sub>JC</sub> (100-pin TQFP) |               | _   | 10   | _   | °C/Watt |

| T <sub>A</sub> | Operating ambient temperature          | For CSP parts | -40 | 25   | 85  | °C      |

| T <sub>J</sub> | Operating junction temperature         | For CSP parts | -40 | _    | 100 | °C      |

| $T_{JA}$       | Package $\theta_{JA}$ (99-ball CSP)    |               |     | 16.5 |     | °C/Watt |

| $T_Jc$         | Package $\theta_{JC}$ (99-ball CSP)    |               | _   | 0.1  | _   | °C/Watt |

Table 13-2. Solder Reflow Peak Temperature

| Package      | Maximum Peak<br>Temperature | Maximum Time at<br>Peak Temperature |  |  |

|--------------|-----------------------------|-------------------------------------|--|--|

| 68-pin QFN   | 260 °C                      | 30 seconds                          |  |  |

| 100-pin TQFP | 260 °C                      | 30 seconds                          |  |  |

| 99-pin CSP   | 255 °C                      | 30 seconds                          |  |  |

Table 13-3. Package Moisture Sensitivity Level (MSL), IPC/JEDEC J-STD-2

| Package      | MSL   |

|--------------|-------|

| 68-pin QFN   | MSL 3 |

| 100-pin TQFP | MSL 3 |

| 99-pin CSP   | MSL 1 |

Document Number: 001-84935 Rev. \*L Page 121 of 131

Table 14-1. Acronyms Used in this Document (continued)

|                   | Acronyms Used in this Document (continued)                   |

|-------------------|--------------------------------------------------------------|

| Acronym           | Description                                                  |

| PHUB              | peripheral hub                                               |

| PHY               | physical layer                                               |

| PICU              | port interrupt control unit                                  |

| PLA               | programmable logic array                                     |

| PLD               | programmable logic device, see also PAL                      |

| PLL               | phase-locked loop                                            |

| PMDD              | package material declaration datasheet                       |

| POR               | power-on reset                                               |

| PRES              | precise low-voltage reset                                    |

| PRS               | pseudo random sequence                                       |

| PS                | port read data register                                      |

| PSoC <sup>®</sup> | Programmable System-on-Chip™                                 |

| PSRR              | power supply rejection ratio                                 |

| PWM               | pulse-width modulator                                        |

| RAM               | random-access memory                                         |

| RISC              | reduced-instruction-set computing                            |

| RMS               | root-mean-square                                             |

| RTC               | real-time clock                                              |

| RTL               | register transfer language                                   |

| RTR               | remote transmission request                                  |

| RX                | receive                                                      |