Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | ARM® Cortex®-M3                                                              |

| Core Size                  | 32-Bit Single-Core                                                           |

| Speed                      | 67MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                               |

| Peripherals                | CapSense, DMA, LCD, POR, PWM, WDT                                            |

| Number of I/O              | 38                                                                           |

| Program Memory Size        | 64KB (64K x 8)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 2K x 8                                                                       |

| RAM Size                   | 16K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 5.5V                                                                 |

| Data Converters            | A/D 2x12b; D/A 4x8b                                                          |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 68-VFQFN Exposed Pad                                                         |

| Supplier Device Package    | 68-QFN (8x8)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c5666lti-lp005 |

## More Information

Cypress provides a wealth of data at www.cypress.com to help you to select the right PSoC device for your design, and to help you to quickly and effectively integrate the device into your design. For a comprehensive list of resources, see the knowledge base article KBA86521, How to Design with PSoC 3, PSoC 4, and PSoC 5LP. Following is an abbreviated list for PSoC 5LP:

- Overview: PSoC Portfolio, PSoC Roadmap

- Product Selectors: PSoC 1, PSoC 3, PSoC 4, PSoC 5LP In addition, PSoC Creator includes a device selection tool.

- Application notes: Cypress offers a large number of PSoC application notes and code examples covering a broad range of topics, from basic to advanced level. Recommended application notes for getting started with PSoC 5LP are:

- □ AN77759: Getting Started With PSoC 5LP

- □ AN77835: PSoC 3 to PSoC 5LP Migration Guide

- □ AN61290: Hardware Design Considerations

- AN57821: Mixed Signal Circuit Board Layout

- AN58304: Pin Selection for Analog Designs

- □ AN81623: Digital Design Best Practices

- □ AN73854: Introduction To Bootloaders

- Development Kits:

- CY8CKIT-059 is a low-cost platform for prototyping, with a unique snap-away programmer and debugger on the USB connector.

- CY8CKIT-050 is designed for analog performance, for developing high-precision analog, low-power, and low-voltage applications.

- CY8CKIT-001 provides a common development platform for any one of the PSoC 1, PSoC 3, PSoC 4, or PSoC 5LP families of devices.

- The MiniProg3 device provides an interface for flash programming and debug.

- Technical Reference Manuals (TRM)

- Architecture TRM

- Registers TRM

- Programming Specification

## **PSoC Creator**

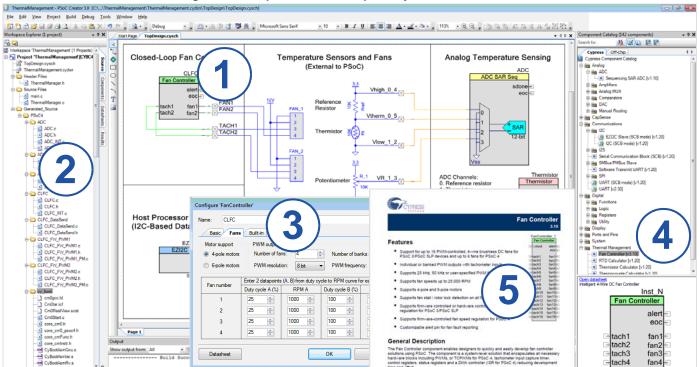

PSoC Creator is a free Windows-based Integrated Design Environment (IDE). It enables concurrent hardware and firmware design of PSoC 3, PSoC 4, and PSoC 5LP based systems. Create designs using classic, familiar schematic capture supported by over 100 pre-verified, production-ready PSoC Components; see the list of component datasheets. With PSoC Creator, you can:

- Drag and drop component icons to build your hardware system design in the main design workspace

- Codesign your application firmware with the PSoC hardware, using the PSoC Creator IDE C compiler

- 3. Configure components using the configuration tools

- 4. Explore the library of 100+ components

- 5. Review component datasheets

Figure 1. Multiple-Sensor Example Project in PSoC Creator

# **Contents**

| 1. Architectural Overview                                                                                                                                                                                                                                           | 4                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 2. Pinouts                                                                                                                                                                                                                                                          | 6                                |

| 3. Pin Descriptions                                                                                                                                                                                                                                                 | 11                               |

| 4. CPU                                                                                                                                                                                                                                                              | 12<br>14<br>15                   |

| 5. Memory                                                                                                                                                                                                                                                           |                                  |

| 5.1 Static RAM 5.2 Flash Program Memory 5.3 Flash Security 5.4 EEPROM 5.5 Nonvolatile Latches (NVLs) 5.6 External Memory Interface 5.7 Memory Map                                                                                                                   | 19<br>19<br>20<br>21             |

| 6. System Integration                                                                                                                                                                                                                                               |                                  |

| 6.1 Clocking System                                                                                                                                                                                                                                                 |                                  |

| 6.3 Reset                                                                                                                                                                                                                                                           |                                  |

| 6.4 I/O System and Routing                                                                                                                                                                                                                                          | 32                               |

| 7. Digital Subsystem  7.1 Example Peripherals  7.2 Universal Digital Block  7.3 UDB Array Description  7.4 DSI Routing Interface Description  7.5 CAN  7.6 USB  7.7 Timers, Counters, and PWMs  7.8 I <sup>2</sup> C  7.9 Digital Filter Block  8. Analog Subsystem | 39<br>40<br>44<br>46<br>48<br>48 |

| 8.1 Analog Routing                                                                                                                                                                                                                                                  |                                  |

| 8.2 Delta-sigma ADC                                                                                                                                                                                                                                                 | 54                               |

| 8.3 Successive Approximation ADCs                                                                                                                                                                                                                                   |                                  |

| 8.4 Comparators                                                                                                                                                                                                                                                     |                                  |

| 8.6 Programmable SC/CT Blocks                                                                                                                                                                                                                                       |                                  |

| 8.7 LCD Direct Drive                                                                                                                                                                                                                                                | 58                               |

| 8.8 CapSense                                                                                                                                                                                                                                                        |                                  |

| 8.9 Temp Sensor                                                                                                                                                                                                                                                     |                                  |

| 8.10 DAC<br>8.11 Up/Down Mixer                                                                                                                                                                                                                                      |                                  |

| 8.12 Sample and Hold                                                                                                                                                                                                                                                |                                  |

| 9. Programming, Debug Interfaces, Resources |     |

|---------------------------------------------|-----|

| 9.1 JTAG Interface                          |     |

| 9.2 SWD Interface                           |     |

| 9.3 Debug Features                          |     |

| 9.4 Trace Features                          |     |

| 9.5 SWV and TRACEPORT Interfaces            |     |

| 9.6 Programming Features                    |     |

| 9.7 Device Security                         |     |

| 9.8 CSP Package Bootloader                  |     |

| 10. Development Support                     |     |

| 10.1 Documentation                          |     |

| 10.2 Online                                 |     |

| 10.3 Tools                                  | 65  |

| 11. Electrical Specifications               | 6   |

| 11.1 Absolute Maximum Ratings               | 66  |

| 11.2 Device Level Specifications            | 67  |

| 11.3 Power Regulators                       | 7   |

| 11.4 Inputs and Outputs                     |     |

| 11.5 Analog Peripherals                     |     |

| 11.6 Digital Peripherals                    |     |

| 11.7 Memory                                 | 108 |

| 11.8 PSoC System Resources                  |     |

| 11.9 Clocking                               | 115 |

| 12. Ordering Information                    |     |

| 12.1 Part Numbering Conventions             | 120 |

| 13. Packaging                               | 12  |

| 14. Acronyms                                | 12  |

| 15. Reference Documents                     | 12  |

| 16. Document Conventions                    | 12  |

| 16.1 Units of Measure                       |     |

| Document History Page                       | 12  |

| Sales, Solutions, and Legal Information     |     |

| Worldwide Sales and Design Support          |     |

| Products                                    |     |

| PSoC® Solutions                             |     |

| Cypress Developer Community                 |     |

| Technical Support                           | 13  |

very low power internal low-speed oscillator (ILO) for the sleep and watchdog timers. A 32.768-kHz external watch crystal is also supported for use in RTC applications. The clocks, together with programmable clock dividers, provide the flexibility to integrate most timing requirements.

The CY8C56LP family supports a wide supply operating range from 1.71 to 5.5 V. This allows operation from regulated supplies such as  $1.8 \pm 5\%$ ,  $2.5 \text{ V} \pm 10\%$ ,  $3.3 \text{ V} \pm 10\%$ , or  $5.0 \text{ V} \pm 10\%$ , or directly from a wide range of battery types. In addition, it provides an integrated high efficiency synchronous boost converter that can power the device from supply voltages as low as 0.5 V. This enables the device to be powered directly from a single battery. In addition, you can use the boost converter to generate other voltages required by the device, such as a 3.3 V supply for LCD glass drive. The boost's output is available on the VBOOST pin, allowing other devices in the application to be powered from the PSoC.

PSoC supports a wide range of low power modes. These include a 300 nA hibernate mode with RAM retention and a 2  $\mu$ A sleep mode with RTC. In the second mode the optional 32.768-kHz watch crystal runs continuously and maintains an accurate RTC.

Power to all major functional blocks, including the programmable digital and analog peripherals, can be controlled independently by firmware. This allows low power background processing when some peripherals are not in use. This, in turn, provides a total device current of only 3.1 mA when the CPU is running at 6 MHz.

The details of the PSoC power modes are covered in the "Power System" section on page 26 of this datasheet.

PSoC uses JTAG (4 wire) or SWD (2 wire) interfaces for programming, debug, and test. Using these standard interfaces you can debug or program the PSoC with a variety of hardware solutions from Cypress or third party vendors. The Cortex-M3 debug and trace modules include Flash Patch and Breakpoint (FPB), Data Watchpoint and Trace (DWT), Embedded Trace Macrocell (ETM), and Instrumentation Trace Macrocell (ITM). These modules have many features to help solve difficult debug and trace problems. Details of the programming, test, and debugging interfaces are discussed in the "Programming, Debug Interfaces, Resources" section on page 61 of this datasheet.

## 2. Pinouts

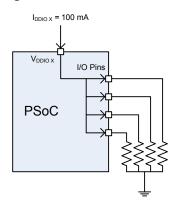

Each VDDIO pin powers a specific set of I/O pins. (The USBIOs are powered from VDDD.) Using the VDDIO pins, a single PSoC can support multiple voltage levels, reducing the need for off-chip level shifters. The black lines drawn on the pinout diagrams in Figure 2-3 and Figure 2-4, as well as Table 2-1, show the pins that are powered by each VDDIO.

Each VDDIO may source up to 100 mA total to its associated I/O pins, as shown in Figure 2-1.

Figure 2-1. VDDIO Current Limit

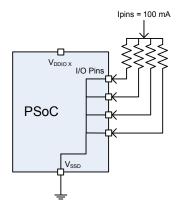

Conversely, for the 100-pin and 68-pin devices, the set of I/O pins associated with any VDDIO may sink up to 100 mA total, as shown in Figure 2-2.

Figure 2-2. I/O Pins Current Limit

#### Note

3. Pins are Do Not Use (DNU) on devices without USB. The pin must be left floating.

## 4.3 DMA and PHUB

The PHUB and the DMA controller are responsible for data transfer between the CPU and peripherals, and also data transfers between peripherals. The PHUB and DMA also control device configuration during boot. The PHUB consists of:

- A central hub that includes the DMA controller, arbiter, and router

- Multiple spokes that radiate outward from the hub to most peripherals

There are two PHUB masters: the CPU and the DMA controller. Both masters may initiate transactions on the bus. The DMA channels can handle peripheral communication without CPU intervention. The arbiter in the central hub determines which DMA channel is the highest priority if there are multiple requests.

#### 4.3.1 PHUB Features

- CPU and DMA controller are both bus masters to the PHUB

- Eight multi-layer AHB bus parallel access paths (spokes) for peripheral access

- Simultaneous CPU and DMA access to peripherals located on different spokes

- Simultaneous DMA source and destination burst transactions on different spokes

- Supports 8, 16, 24, and 32-bit addressing and data Table 4-3. PHUB Spokes and Peripherals

| PHUB Spokes | Peripherals                                                                                         |

|-------------|-----------------------------------------------------------------------------------------------------|

| 0           | SRAM                                                                                                |

| 1           | IOs, PICU, EMIF                                                                                     |

| 2           | PHUB local configuration, Power manager,<br>Clocks, IC, SWV, EEPROM, Flash<br>programming interface |

| 3           | Analog interface and trim, Decimator                                                                |

| 4           | USB, I <sup>2</sup> C, CAN, Timers, Counters, and PWMs                                              |

| 5           | DFB                                                                                                 |

| 6           | UDBs group 1                                                                                        |

| 7           | UDBs group 2                                                                                        |

#### 4.3.2 DMA Features

- 24 DMA channels

- Each channel has one or more Transaction Descriptors (TDs) to configure channel behavior. Up to 128 total TDs can be defined

- TDs can be dynamically updated

- Eight levels of priority per channel

- Any digitally routable signal, the CPU, or another DMA channel, can trigger a transaction

- Each channel can generate up to two interrupts per transfer

- Transactions can be stalled or canceled

- Supports transaction size of infinite or 1 to 64k bytes

- Large transactions may be broken into smaller bursts of 1 to 127 bytes

- TDs may be nested and/or chained for complex transactions

#### 4.3.3 Priority Levels

The CPU always has higher priority than the DMA controller when their accesses require the same bus resources. Due to the system architecture, the CPU can never starve the DMA. DMA channels of higher priority (lower priority number) may interrupt current DMA transfers. In the case of an interrupt, the current transfer is allowed to complete its current transaction. To ensure latency limits when multiple DMA accesses are requested simultaneously, a fairness algorithm guarantees an interleaved minimum percentage of bus bandwidth for priority levels 2 through 7. Priority levels 0 and 1 do not take part in the fairness algorithm and may use 100% of the bus bandwidth. If a tie occurs on two DMA requests of the same priority level, a simple round robin method is used to evenly share the allocated bandwidth. The round robin allocation can be disabled for each DMA channel, allowing it to always be at the head of the line. Priority levels 2 to 7 are guaranteed the minimum bus bandwidth shown in Table 4-4 after the CPU and DMA priority levels 0 and 1 have satisfied their requirements.

Table 4-4. Priority Levels

| Priority Level | % Bus Bandwidth |

|----------------|-----------------|

| 0              | 100.0           |

| 1              | 100.0           |

| 2              | 50.0            |

| 3              | 25.0            |

| 4              | 12.5            |

| 5              | 6.2             |

| 6              | 3.1             |

| 7              | 1.5             |

When the fairness algorithm is disabled, DMA access is granted based solely on the priority level; no bus bandwidth guarantees are made.

# 4.3.4 Transaction Modes Supported

The flexible configuration of each DMA channel and the ability to chain multiple channels allow the creation of both simple and complex use cases. General use cases include, but are not limited to:

## 4.3.4.1 Simple DMA

In a simple DMA case, a single TD transfers data between a source and sink (peripherals or memory location). The basic timing diagrams of DMA read and write cycles are shown in Figure 4-2. For more description on other transfer modes, refer to the Technical Reference Manual.

The central timewheel can be programmed to wake the system periodically and optionally issue an interrupt. This enables flexible, periodic wakeups from low power modes or coarse timing applications. Systems that require accurate timing should use Real Time Clock capability instead of the central timewheel.

The 100-kHz clock (CLK100K) can be used as a low power system clock to run the CPU. It can also generate time intervals using the fast timewheel.

The fast timewheel is a 5-bit counter, clocked by the 100-kHz clock. It features programmable settings and automatically resets when the terminal count is reached. An optional interrupt can be generated each time the terminal count is reached. This enables flexible, periodic interrupts of the CPU at a higher rate than is allowed using the central timewheel.

The 33 kHz clock (CLK33K) comes from a divide-by-3 operation on CLK100K. This output can be used as a reduced accuracy version of the 32.768 kHz ECO clock with no need for a crystal.

#### 6.1.2 External Oscillators

Figure 6-1 shows that there are two external oscillators. They can be routed directly or divided. The direct routes may not have a 50% duty cycle. Divided clocks have a 50% duty cycle.

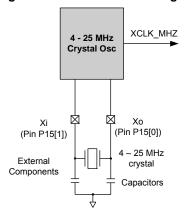

#### 6.1.2.1 MHz External Crystal Oscillator

The MHzECO provides high frequency, high precision clocking using an external crystal (see Figure 6-2). It supports a wide variety of crystal types, in the range of 4 to 25 MHz. When used in conjunction with the PLL, it can generate CPU and system clocks up to the device's maximum frequency (see Phase-Locked Loop on page 24). The GPIO pins connecting to the external crystal and capacitors are fixed. MHzECO accuracy depends on the crystal chosen.

Figure 6-2. MHzECO Block Diagram

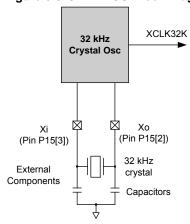

## 6.1.2.2 32.768 kHz ECO

The 32.768 kHz External Crystal Oscillator (32kHzECO) provides precision timing with minimal power consumption using an external 32.768 kHz watch crystal (see Figure 6-3). The 32kHzECO also connects directly to the sleep timer and provides the source for the Real Time Clock (RTC). The RTC uses a 1 second interrupt to implement the RTC functionality in firmware.

The oscillator works in two distinct power modes. This allows users to trade off power consumption with noise immunity from neighboring circuits. The GPIO pins connected to the external crystal and capacitors are fixed.

Figure 6-3. 32kHzECO Block Diagram

It is recommended that the external 32.768-kHz watch crystal have a load capacitance (CL) of 6 pF or 12.5 pF. Check the crystal manufacturer's datasheet. The two external capacitors, CL1 and CL2, are typically of the same value, and their total capacitance, CL1CL2 / (CL1 + CL2), including pin and trace capacitance, should equal the crystal CL value. For more information, refer to application note AN54439: PSoC 3 and PSoC 5 External Oscillators. See also pin capacitance specifications in the "GPIO" section on page 75.

#### 6.1.2.3 Digital System Interconnect

The DSI provides routing for clocks taken from external clock oscillators connected to I/O. The oscillators can also be generated within the device in the digital system and UDBs.

While the primary DSI clock input provides access to all clocking resources, up to eight other DSI clocks (internally or externally generated) may be routed directly to the eight digital clock dividers. This is only possible if there are multiple precision clock sources.

#### 6.1.3 Clock Distribution

All seven clock sources are inputs to the central clock distribution system. The distribution system is designed to create multiple high precision clocks. These clocks are customized for the design's requirements and eliminate the common problems found with limited resolution prescalers attached to peripherals. The clock distribution system generates several types of clock trees.

- The system clock is used to select and supply the fastest clock in the system for general system clock requirements and clock synchronization of the PSoC device.

- Bus Clock 16-bit divider uses the system clock to generate the system's bus clock used for data transfers and the CPU. The CPU clock is directly derived from the bus clock.

- Eight fully programmable 16-bit clock dividers generate digital system clocks for general use in the digital system, as configured by the design's requirements. Digital system clocks can generate custom clocks derived from any of the seven clock sources for any purpose. Examples include baud rate generators, accurate PWM periods, and timer clocks, and many others. If more than eight digital clock dividers are required, the UDBs and fixed function Timer/Counter/PWMs can also generate clocks.

**Digital Input Path** Naming Convention 'x' = Port Number PRT[x]CTL PRT[x]DBL\_SYNC\_IN 'y' = Pin Number PRT[x]PS Digital System Input PICU[x]INTTYPE[y] Input Buffer Disable PICU[x]INTSTAT Interrupt Pin Interrupt Signal Logic PICU[x]INTSTAT **Digital Output Path** PRT[x]SLW PRT[x]SYNC\_OUT Vddio Vddio PRT[x]DR In Digital System Output Vddio PRT[x]BYP Drive PRT[x]DM2 Slew PIN Logic PRT[x]DM1 Cntl PRT[x]DM0 **Bidirectional Control** OE PRT[x]BIE Analog Capsense Global Control CAPS[x]CFG1 Switches PRT[x]AG Analog Global PRT[x]AMUX Analog Mux LCD Display PRT[x]LCD\_COM\_SEG Logic & MUX PRT[x]LCD\_EN LCD Bias Bus

Figure 6-9. GPIO Block Diagram

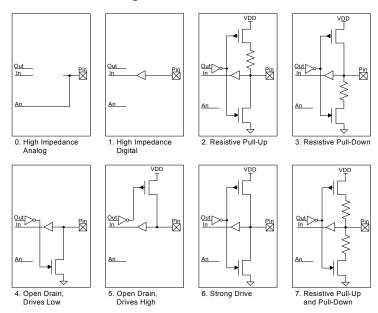

#### 6.4.1 Drive Modes

Each GPIO and SIO pin is individually configurable into one of the eight drive modes listed in Table 6-6. Three configuration bits are used for each pin (DM[2:0]) and set in the PRTxDM[2:0] registers. Figure 6-12 depicts a simplified pin view based on each of the eight drive modes. Table 6-6 shows the I/O pin's drive state based on the port data register value or digital array signal

if bypass mode is selected. Note that the actual I/O pin voltage is determined by a combination of the selected drive mode and the load at the pin. For example, if a GPIO pin is configured for resistive pull up mode and driven high while the pin is floating, the voltage measured at the pin is a high logic state. If the same GPIO pin is externally tied to ground then the voltage unmeasured at the pin is a low logic state.

Figure 6-12. Drive Mode

The 'Out' connection is driven from either the Digital System (when the Digital Output terminal is connected) or the Data Register (when HW connection is disabled).

The 'In' connection drives the Pin State register, and the Digital System if the Digital Input terminal is enabled and connected. The 'An' connection connects to the Analog System.

Table 6-6. Drive Modes

| Diagram | Drive Mode                                      | PRTxDM2 | PRTxDM1 | PRTxDM0 | PRTxDR = 1    | PRTxDR = 0   |

|---------|-------------------------------------------------|---------|---------|---------|---------------|--------------|

| 0       | High-impedance analog                           | 0       | 0       | 0       | High Z        | High Z       |

| 1       | High-impedance digital                          | 0       | 0       | 1       | High Z        | High Z       |

| 2       | Resistive pull-up <sup>[10]</sup>               | 0       | 1       | 0       | Res High (5K) | Strong Low   |

| 3       | Resistive pull-down <sup>[10]</sup>             | 0       | 1       | 1       | Strong High   | Res Low (5K) |

| 4       | Open drain, drives low                          | 1       | 0       | 0       | High Z        | Strong Low   |

| 5       | Open drain, drive high                          | 1       | 0       | 1       | Strong High   | High Z       |

| 6       | Strong drive                                    | 1       | 1       | 0       | Strong High   | Strong Low   |

| 7       | Resistive pull up and pull down <sup>[10]</sup> | 1       | 1       | 1       | Res High (5K) | Res Low (5K) |

#### Note

<sup>10.</sup> Resistive pull up and pull down are not available with SIO in regulated output mode.

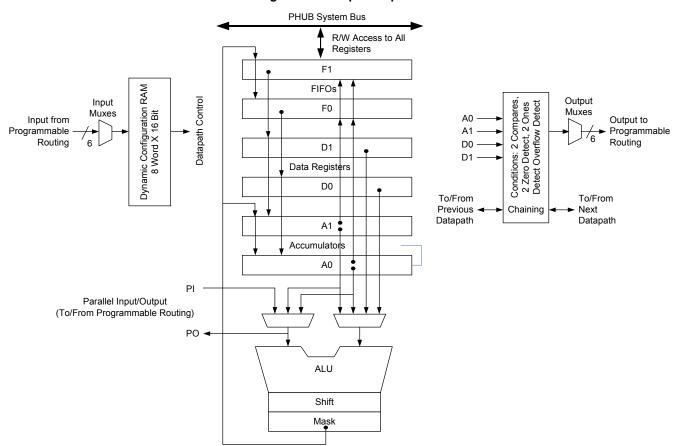

Figure 7-4. Datapath Top Level

## 7.2.2.1 Working Registers

The datapath contains six primary working registers, which are accessed by CPU firmware or DMA during normal operation.

Table 7-1. Working Datapath Registers

| Name      | Function       | Description                                                                                                                                                                                               |  |  |  |  |  |

|-----------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| A0 and A1 | Accumulators   | These are sources and sinks for the ALU and also sources for the compares.                                                                                                                                |  |  |  |  |  |

| D0 and D1 | Data Registers | These are sources for the ALU and sources for the compares.                                                                                                                                               |  |  |  |  |  |

| F0 and F1 | FIFOs          | These are the primary interface to the system bus. They can be a data source for the data registers and accumulators or they can capture data from the accumulators or ALU. Each FIFO is four bytes deep. |  |  |  |  |  |

## 7.2.2.2 Dynamic Configuration RAM

Dynamic configuration is the ability to change the datapath function and internal configuration on a cycle-by-cycle basis, under sequencer control. This is implemented using the 8-word x 16-bit configuration RAM, which stores eight unique 16-bit wide

configurations. The address input to this RAM controls the sequence, and can be routed from any block connected to the UDB routing matrix, most typically PLD logic, I/O pins, or from the outputs of this or other datapath blocks.

#### ΔΙΙ

The ALU performs eight general-purpose functions. They are:

- Increment

- Decrement

- Add

- Subtract

- Logical AND

- Logical OR

- Logical XOR

- Pass, used to pass a value through the ALU to the shift register, mask, or another UDB register

Independent of the ALU operation, these functions are available:

- Shift left

- Shift right

- Nibble swap

- Bitwise OR mask

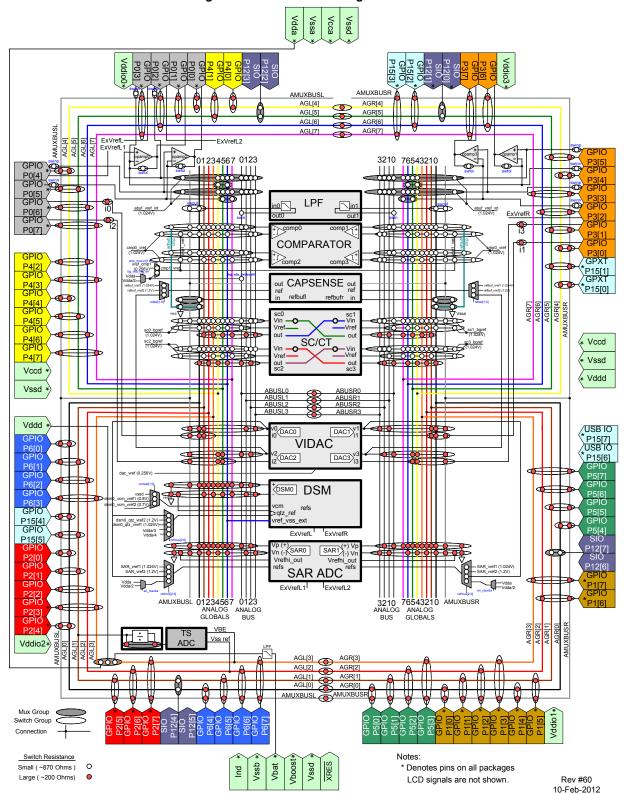

Figure 8-2. CY8C56LP Analog Interconnect

To preserve detail of this image, this image is best viewed with a PDF display program or printed on 11" × 17" paper.

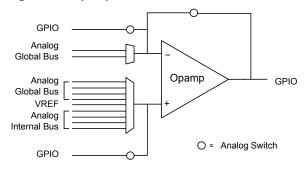

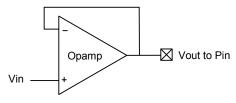

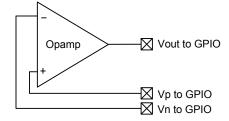

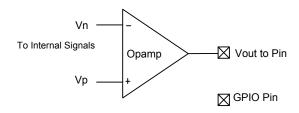

## 8.5 Opamps

The CY8C56LP family of devices contain four general purpose opamps.

Figure 8-7. Opamp

The opamp is uncommitted and can be configured as a gain stage or voltage follower on external or internal signals.

See Figure 8-8. In any configuration, the input and output signals can all be connected to the internal global signals and monitored with an ADC, or comparator. The configurations are implemented with switches between the signals and GPIO pins.

Figure 8-8. Opamp Configurations

a) Voltage Follower

b) External Uncommitted Opamp

c) Internal Uncommitted Opamp

The opamp has three speed modes, slow, medium, and fast. The slow mode consumes the least amount of quiescent power and the fast mode consumes the most power. The inputs are able to swing rail-to-rail. The output swing is capable of rail-to-rail operation at low current output, within 50 mV of the rails. When driving high current loads (about 25 mA) the output voltage may only get within 500 mV of the rails.

## 8.6 Programmable SC/CT Blocks

The CY8C56LP family of devices contains four switched capacitor/continuous time (SC/CT) blocks. Each switched capacitor/continuous time block is built around a single rail-to-rail high bandwidth opamp.

Switched capacitor is a circuit design technique that uses capacitors plus switches instead of resistors to create analog functions. These circuits work by moving charge between capacitors by opening and closing different switches. Nonoverlapping in phase clock signals control the switches, so that not all switches are ON simultaneously.

The PSoC Creator tool offers a user friendly interface, which allows you to easily program the SC/CT blocks. Switch control and clock phase control configuration is done by PSoC Creator so users only need to determine the application use parameters such as gain, amplifier polarity, V<sub>REF</sub> connection, and so on.

The same opamps and block interfaces are also connectable to an array of resistors which allows the construction of a variety of continuous time functions.

The opamp and resistor array is programmable to perform various analog functions including

- Naked Operational Amplifier Continuous Mode

- Unity-Gain Buffer Continuous Mode

- Programmable Gain Amplifier (PGA) Continuous Mode

- Transimpedance Amplifier (TIA) Continuous Mode

- Up/Down Mixer Continuous Mode

- Sample and Hold Mixer (NRZ S/H) Switched Cap Mode

- First Order Analog to Digital Modulator Switched Cap Mode

#### 8.6.1 Naked Opamp

The Naked Opamp presents both inputs and the output for connection to internal or external signals. The opamp has a unity gain bandwidth greater than 6.0 MHz and output drive current up to 650 µA. This is sufficient for buffering internal signals (such as DAC outputs) and driving external loads greater than 7.5 kohms.

## 8.6.2 Unity Gain

The Unity Gain buffer is a Naked Opamp with the output directly connected to the inverting input for a gain of 1.00. It has a -3 dB bandwidth greater than 6.0 MHz.

If the device is protected with a WOL setting, Cypress cannot perform failure analysis and, therefore, cannot accept RMAs from customers. The WOL can be read out via Serial Wire Debug (SWD) port to electrically identify protected parts. The user can write the key in WOL to lock out external access only if no flash protection is set. For more information on how to take full advantage of the security features in PSoC see the PSoC 5 TRM.

#### Disclaimer

Note the following details of the flash code protection features on Cypress devices.

Cypress products meet the specifications contained in their particular Cypress datasheets. Cypress believes that its family of products is one of the most secure families of its kind on the market today, regardless of how they are used. There may be methods, unknown to Cypress, that can breach the code protection features. Any of these methods, to our knowledge, would be dishonest and possibly illegal. Neither Cypress nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Cypress is willing to work with the customer who is concerned about the integrity of their code. Code protection is constantly evolving. We at Cypress are committed to continuously improving the code protection features of our products.

## 9.8 CSP Package Bootloader

A factory-installed bootloader program is included in all devices with CSP packages. The bootloader is compatible with PSoC Creator 3.0 bootloadable project files, and has the following features:

- I2C-based

- SCLK and SDAT available at P1[6] and P1[7], respectively

- External pull-up resistors required

- I2C slave, address 4, data rate = 100 kbps

- Single application

- Wait 2 seconds for bootload command

- Other bootloader options are as set by the PSoC Creator 3.0 Bootloader Component default

- Occupies the bottom 9 Kbytes of flash

For more information on this bootloader, see the following Cypress application notes:

- AN73854, PSoC 3 and PSoC 5 LP Introduction to Bootloaders

- AN60317, PSoC 3 and PSoC 5 LP I2C Bootloader

Note that a PSoC Creator bootloadable project must be associated with .hex and .elf files for a bootloader project that is configured for the target device. Bootloader .hex and .elf files can be found at www.cypress.com/go/PSoC5LPdatasheet.

The factory-installed bootloader can be overwritten using JTAG or SWD programming.

# 10. Development Support

The CY8C56LP family has a rich set of documentation, development tools, and online resources to assist you during your development process. Visit psoc.cypress.com/getting-started to find out more.

#### 10.1 Documentation

A suite of documentation, to ensure that you can find answers to your questions quickly, supports the CY8C56LP family. This section contains a list of some of the key documents.

**Software User Guide**: A step-by-step guide for using PSoC Creator. The software user guide shows you how the PSoC Creator build process works in detail, how to use source control with PSoC Creator, and much more.

**Component Datasheets**: The flexibility of PSoC allows the creation of new peripherals (components) long after the device has gone into production. Component datasheets provide all of the information needed to select and use a particular component, including a functional description, API documentation, example code, and AC/DC specifications.

**Application Notes**: PSoC application notes discuss a particular application of PSoC in depth; examples include brushless DC motor control and on-chip filtering. Application notes often include example projects in addition to the application note document.

**Technical Reference Manual**: PSoC Creator makes designing with PSoC as easy as dragging a peripheral onto a schematic, but, when low level details of the PSoC device are required, use the technical reference manual (TRM) as your guide.

**Note** Visit www.arm.com for detailed documentation about the Cortex-M3 CPU.

## 10.2 Online

In addition to print documentation, the Cypress PSoC forums connect you with fellow PSoC users and experts in PSoC from around the world, 24 hours a day, 7 days a week.

## 10.3 Tools

With industry standard cores, programming, and debugging interfaces, the CY8C56LP family is part of a development tool ecosystem. Visit us at <a href="https://www.cypress.com/go/psoccreator">www.cypress.com/go/psoccreator</a> for the latest information on the revolutionary, easy to use PSoC Creator IDE, supported third party compilers, programmers, debuggers, and development kits.

Document Number: 001-84935 Rev. \*L Page 65 of 131

# 11. Electrical Specifications

Specifications are valid for -40 °C  $\leq T_A \leq 105$  °C and  $T_J \leq 120$  °C, except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted. The unique flexibility of the PSoC UDBs and analog blocks enable many functions to be implemented in PSoC Creator components, see the component datasheets for full AC/DC specifications of individual functions. See the "Example Peripherals" section on page 39 for further explanation of PSoC Creator components.

## 11.1 Absolute Maximum Ratings

Table 11-1. Absolute Maximum Ratings DC Specifications<sup>[14]</sup>

| Parameter                         | Description                                         | Conditions                                                                   | Min                    | Тур | Max                     | Units |

|-----------------------------------|-----------------------------------------------------|------------------------------------------------------------------------------|------------------------|-----|-------------------------|-------|

| $V_{DDA}$                         | Analog supply voltage relative to V <sub>SSA</sub>  |                                                                              | -0.5                   | _   | 6                       | V     |

| $V_{DDD}$                         | Digital supply voltage relative to V <sub>SSD</sub> |                                                                              | -0.5                   | _   | 6                       | V     |

| $V_{DDIO}$                        | I/O supply voltage relative to V <sub>SSD</sub>     |                                                                              | -0.5                   | _   | 6                       | V     |

| $V_{CCA}$                         | Direct analog core voltage input                    |                                                                              | -0.5                   | _   | 1.95                    | V     |

| $V_{CCD}$                         | Direct digital core voltage input                   |                                                                              | -0.5                   | _   | 1.95                    | V     |

| $V_{SSA}$                         | Analog ground voltage                               |                                                                              | $V_{SSD} - 0.5$        | _   | V <sub>SSD</sub> + 0.5  | V     |

| V <sub>GPIO</sub> <sup>[15]</sup> | DC input voltage on GPIO                            | Includes signals sourced by V <sub>DDA</sub> and routed internal to the pin. | V <sub>SSD</sub> – 0.5 | _   | V <sub>DDIO</sub> + 0.5 | V     |

| $V_{SIO}$                         | DC input voltage on SIO                             | Output disabled                                                              | $V_{SSD} - 0.5$        | -   | 7                       | V     |

|                                   |                                                     | Output enabled                                                               | $V_{SSD} - 0.5$        | _   | 6                       | V     |

| $V_{IND}$                         | Voltage at boost converter input                    |                                                                              | 0.5                    | -   | 5.5                     | V     |

| $V_{BAT}$                         | Boost converter supply                              |                                                                              | $V_{SSD} - 0.5$        | _   | 5.5                     | V     |

| I <sub>VDDIO</sub>                | Current per V <sub>DDIO</sub> supply pin            |                                                                              | _                      | -   | 100                     | mA    |

| I <sub>GPIO</sub>                 | GPIO current                                        |                                                                              | -30                    | _   | 41                      | mA    |

| I <sub>SIO</sub>                  | SIO current                                         |                                                                              | -49                    | _   | 28                      | mA    |

| I <sub>USBIO</sub>                | USBIO current                                       |                                                                              | -56                    | _   | 59                      | mA    |

| LU                                | Latch up current <sup>[16]</sup>                    |                                                                              | -140                   | -   | 140                     | mA    |

| ESD <sub>HBM</sub>                | Electrostatic discharge voltage                     | Human Body Model                                                             | 2000                   | _   | _                       | V     |

| ESD <sub>CDM</sub>                | Electrostatic discharge voltage                     | Charge Device Model                                                          | 500                    | _   | _                       | V     |

<sup>14.</sup> Usage above the absolute maximum conditions listed in Table 11-1 may cause permanent damage to the device. Exposure to Absolute Maximum conditions for extended periods of time may affect device reliability. The Maximum Storage Temperature is 150 °C in compliance with JEDEC Standard JESD22-A103, High Temperature Storage Life. When used below Absolute Maximum conditions but above normal operating conditions, the device may not operate to specification.

<sup>15.</sup> The V<sub>DDIO</sub> supply voltage must be greater than the maximum voltage on the associated GPIO pins. Maximum voltage on GPIO pin ≤ V<sub>DDIO</sub> ≤ V<sub>DDA</sub>. 16. Meets or exceeds JEDEC Spec EIA/JESD78 IC Latch-up Test.

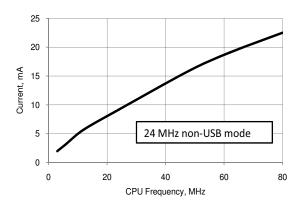

Figure 11-1. Active Mode Current vs  $F_{CPU}$ ,  $V_{DD}$  = 3.3 V, Temperature = 25 °C

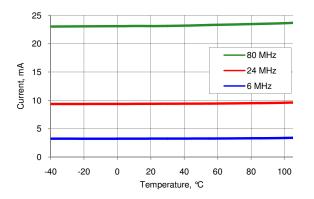

Figure 11-3. Active Mode Current vs Temperature and  $F_{CPU}$ ,  $V_{DD}$  = 3.3 V

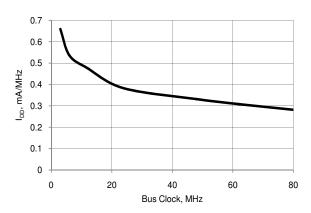

Figure 11-2. I<sub>DD</sub> vs Frequency at 25 °C

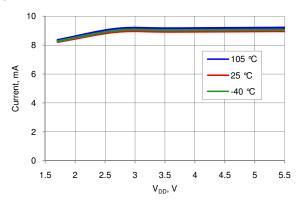

Figure 11-4. Active Mode Current vs  $\rm V_{DD}$  and Temperature,  $\rm F_{CPU}$  = 24 MHz

Table 11-3. AC Specifications

| Parameter                            | Description                                                                                                                   | Conditions                                                                                           | Min | Тур | Max   | Units |

|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-----|-----|-------|-------|

| F <sub>CPU</sub>                     | CPU frequency                                                                                                                 | 1.71 V ≤ V <sub>DDD</sub> ≤ 5.5 V                                                                    | DC  | -   | 80.01 | MHz   |

|                                      | Bus frequency                                                                                                                 | $1.71 \text{ V} \le \text{V}_{DDD} \le 5.5 \text{ V}$                                                | DC  | _   | 80.01 | MHz   |

| S <sub>VDD</sub> <sup>[28]</sup>     | V <sub>DD</sub> ramp rate                                                                                                     |                                                                                                      | _   | -   | 0.066 | V/µs  |

| T <sub>IO_INIT</sub> <sup>[28]</sup> | Time from $V_{DDD}/V_{DDA}/V_{CCD}/V_{CCA} \ge IPOR$ to I/O ports set to their reset states                                   |                                                                                                      | -   | -   | 10    | μs    |

| T <sub>STARTUP</sub> <sup>[28]</sup> | Time from V <sub>DDD</sub> /V <sub>DDA</sub> /V <sub>CCD</sub> /V <sub>CCA</sub> ≥ PRES to CPU executing code at reset vector | $V_{CCA}/V_{DDA}$ = regulated from $V_{DDA}/V_{DDD}$ , no PLL used, fast IMO boot mode (48 MHz typ.) | -   | -   | 33    | μs    |

|                                      |                                                                                                                               | $V_{CCA}/V_{CCD}$ = regulated from $V_{DDA}/V_{DDD}$ , no PLL used, slow IMO boot mode (12 MHz typ.) | -   | -   | 66    | μs    |

| OLLLI                                | Wakeup from sleep mode –<br>Application of non-LVD interrupt to<br>beginning of execution of next CPU<br>instruction          |                                                                                                      | -   | -   | 25    | μs    |

|                                      | Wakeup form hibernate mode – Application of external interrupt to beginning of execution of next CPU instruction              |                                                                                                      | _   | _   | 150   | μs    |

#### Note

28. Based on device characterization (not production tested).

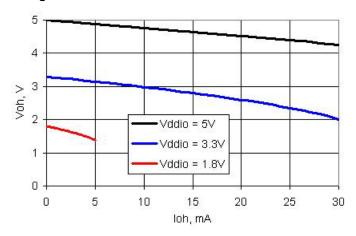

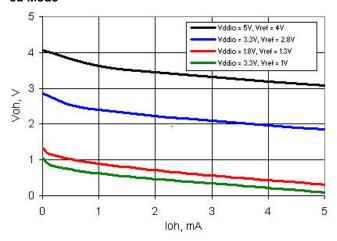

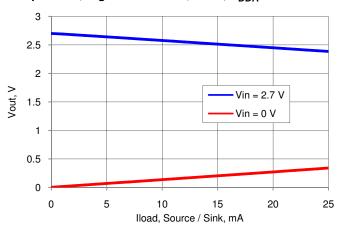

Figure 11-17. SIO Output High Voltage and Current, Unregulated Mode

Figure 11-19. SIO Output High Voltage and Current, Regulated Mode

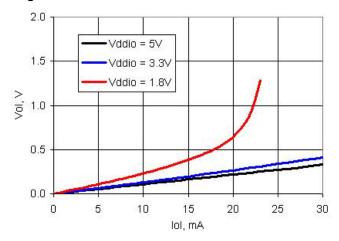

Figure 11-18. SIO Output Low Voltage and Current, Unregulated Mode

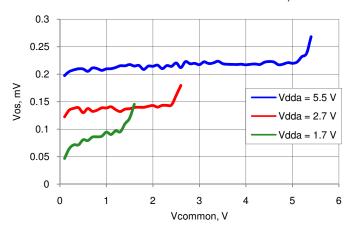

Figure 11-27. Opamp Vos vs Vcommon and  $V_{DDA,}$  25 °C

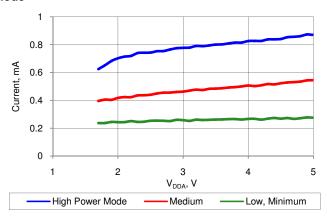

Figure 11-28. Opamp Output Voltage vs Load Current and Temperature, High Power Mode, 25  $^{\circ}$ C, V<sub>DDA</sub> = 2.7 V

Figure 11-29. Opamp Operating Current vs  $V_{\text{DDA}}$  and Power Mode

Table 11-19. Opamp AC Specifications<sup>[40]</sup>

| Parameter      | Description            | Conditions                                            | Min | Тур | Max | Units     |

|----------------|------------------------|-------------------------------------------------------|-----|-----|-----|-----------|

| GBW            | Gain-bandwidth product | Power mode = minimum, 15 pF load                      | 1   | _   | _   | MHz       |

|                |                        | Power mode = low, 15 pF load                          | 2   | _   | _   | MHz       |

|                |                        | Power mode = medium, 200 pF load                      | 1   | _   | -   | MHz       |

|                |                        | Power mode = high, 200 pF load                        | 3   | _   | _   | MHz       |

| SR             | Slew rate, 20% - 80%   | Power mode = minimum, 15 pF load                      | 1.1 | -   | _   | V/µs      |

|                |                        | Power mode = low, 15 pF load                          | 1.1 | -   | _   | V/µs      |

|                |                        | Power mode = medium, 200 pF load                      | 0.9 | _   | _   | V/µs      |

|                |                        | Power mode = high, 200 pF load                        | 3   | _   | _   | V/µs      |

| e <sub>n</sub> | Input noise density    | Power mode = high, V <sub>DDA</sub> = 5 V, at 100 kHz | -   | 45  | _   | nV/sqrtHz |

#### Note

<sup>40.</sup> Based on device characterization (Not production tested).

## 11.5.2 Delta-Sigma ADC

Unless otherwise specified, operating conditions are:

- Operation in continuous sample mode

- fclk = 6.144 MHz

- Reference = 1.024 V internal reference bypassed on P3.2 or P0.3

- Unless otherwise specified, all charts and graphs show typical values

Table 11-20. 12-bit Delta-sigma ADC DC Specifications

| Parameter          | Description                                                                                       | Conditions                                                    | Min              | Тур                    | Max                  | Units      |

|--------------------|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------|------------------|------------------------|----------------------|------------|

|                    | Resolution                                                                                        |                                                               | 8                | _                      | 12                   | bits       |

|                    | Number of channels, single ended                                                                  |                                                               | _                | _                      | No. of<br>GPIO       | -          |

|                    | Number of channels, differential                                                                  | Differential pair is formed using a pair of GPIOs.            | _                | _                      | No. of<br>GPIO/2     | -          |

|                    | Monotonic                                                                                         | Yes                                                           | _                | _                      | -                    | _          |

| Ge                 | Gain error                                                                                        | Buffered, buffer gain = 1,<br>Range = ±1.024 V, 25 °C         | -                | _                      | ±0.4                 | %          |

| Gd                 | Gain drift                                                                                        | Buffered, buffer gain = 1,<br>Range = ±1.024 V                | -                | _                      | 50                   | ppm/°<br>C |

| Vos                | Input offset voltage                                                                              | Buffered, 16-bit mode, full voltage range                     | -                | _                      | ±0.2                 | mV         |

| VOS                | Imput onset voltage                                                                               | Buffered, 16-bit mode,<br>V <sub>DDA</sub> = 1.8 V ±5%, 25 °C | -                | _                      | ±0.1                 | mV         |

| TCVos              | Temperature coefficient, input offset voltage                                                     | Buffer gain = 1, 12-bit,<br>Range = ±1.024 V                  | -                | _                      | 1                    | μV/°C      |

|                    | Input voltage range, single ended <sup>[41]</sup>                                                 |                                                               | $V_{SSA}$        | -                      | $V_{DDA}$            | V          |

|                    | Input voltage range, differential unbuffered <sup>[41]</sup>                                      |                                                               | V <sub>SSA</sub> | _                      | $V_{DDA}$            | V          |

|                    | Input voltage range, differential, buffered <sup>[41]</sup>                                       |                                                               | V <sub>SSA</sub> | _                      | V <sub>DDA</sub> – 1 | V          |

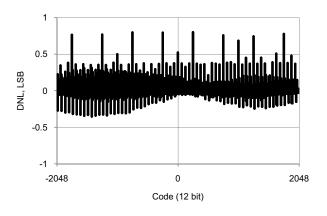

| INL12              | Integral non linearity <sup>[41]</sup>                                                            | Range = ±1.024 V, unbuffered                                  | _                | -                      | ±1                   | LSB        |

| DNL12              | Differential non linearity <sup>[41]</sup>                                                        | Range = ±1.024 V, unbuffered                                  | -                | -                      | ±1                   | LSB        |

| INL8               | Integral non linearity <sup>[41]</sup>                                                            | Range = ±1.024 V, unbuffered                                  | _                | -                      | ±1                   | LSB        |

| DNL8               | Differential non linearity <sup>[41]</sup>                                                        | Range = ±1.024 V, unbuffered                                  | _                | -                      | ±1                   | LSB        |

| Rin_Buff           | ADC input resistance                                                                              | Input buffer used                                             | 10               | -                      | -                    | MΩ         |

| Rin_ADC12          | ADC input resistance                                                                              | Input buffer bypassed, 12 bit, Range = ±1.024 V               | _                | 148 <sup>[42]</sup>    | _                    | kΩ         |

| Rin_ExtRef         | ADC external reference input resistance                                                           |                                                               | -                | 70 <sup>[42, 43]</sup> | -                    | kΩ         |

| Vextref            | ADC external reference input voltage, see also internal reference in Voltage Reference on page 88 | Pins P0[3], P3[2]                                             | 0.9              | _                      | 1.3                  | V          |

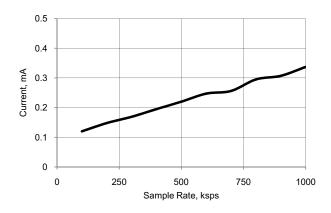

| <b>Current Cor</b> |                                                                                                   |                                                               |                  |                        |                      |            |

| I <sub>DD_12</sub> | Current consumption, 12 bit <sup>[41]</sup>                                                       | 192 ksps, unbuffered                                          | _                | _                      | 1.4                  | mA         |

| I <sub>BUFF</sub>  | Buffer current consumption <sup>[41]</sup>                                                        |                                                               | _                | _                      | 2.5                  | mA         |

Document Number: 001-84935 Rev. \*L Page 86 of 131

<sup>41.</sup> Based on device characterization (not production tested).

<sup>42.</sup> By using switched capacitors at the ADC input an effective input resistance is created. Holding the gain and number of bits constant, the resistance is proportional to

the inverse of the clock frequency. This value is calculated, not measured. For more information see the Technical Reference Manual.

Recommend an external reference device with an output impedance <100 Ω, for example, the LM185/285/385 family. A 1 μF capacitor is recommended. For more information, see AN61290 - PSoC® 3 and PSoC 5LP Hardware Design Considerations.</li>

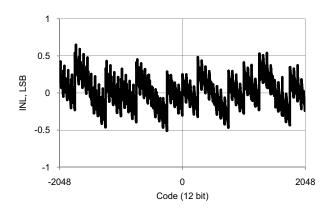

Figure 11-36. SAR ADC DNL vs Output Code, Bypassed Internal Reference Mode

Figure 11-38. SAR ADC  $I_{DD}$  vs sps,  $V_{DDA}$  = 5 V, Continuous Sample Mode, External Reference Mode

Figure 11-37. SAR ADC INL vs Output Code, Bypassed Internal Reference Mode

Table 11-39. PGA AC Specifications<sup>[62]</sup>

| Parameter      | Description         | Conditions                                                     | Min | Тур | Max | Units     |

|----------------|---------------------|----------------------------------------------------------------|-----|-----|-----|-----------|

| BW1            | -3 dB bandwidth     | Power mode = high,<br>gain = 1, input = 100 mV<br>peak-to-peak | 6.7 | 8   | -   | MHz       |

|                |                     | T <sub>A</sub> ≤ 105 °C                                        | 6   | 8   | _   | ]         |

| SR1            | Slew rate           | Power mode = high,<br>gain = 1, 20% to 80%                     | 3   | _   | -   | V/µs      |

| e <sub>n</sub> | Input noise density | Power mode = high,<br>V <sub>DDA</sub> = 5 V, at 100 kHz       | _   | 43  | _   | nV/sqrtHz |

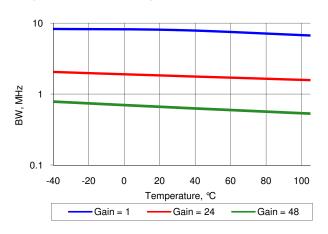

Figure 11-69. Bandwidth vs. Temperature, at Different Gain Settings, Power Mode = High

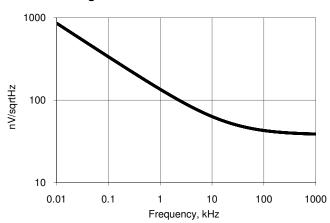

Figure 11-70. Noise vs. Frequency, Vdda = 5 V, Power Mode = High

11.5.12 Temperature Sensor

Table 11-40. Temperature Sensor Specifications

|   | Parameter | Description          | Conditions               | Min | Тур | Max | Units |

|---|-----------|----------------------|--------------------------|-----|-----|-----|-------|

| ĺ |           | Temp sensor accuracy | Range: -40 °C to +105 °C | -   | ±5  | _   | °C    |

11.5.13 LCD Direct Drive

Table 11-41. LCD Direct Drive DC Specifications<sup>[62]</sup>

| Parameter           | Description                                                                         | Conditions                                                                                                                                                                       | Min | Тур                    | Max  | Units |

|---------------------|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------------------|------|-------|

| I <sub>CC</sub>     | LCD Block (no glass)                                                                | Device sleep mode with wakeup at 400 Hz rate to refresh LCD, bus, clock = 3MHz, Vddio = Vdda = 3 V, 8 commons, 16 segments, 1/5 duty cycle, 40 Hz frame rate, no glass connected | -   | 81                     | -    | μА    |

| I <sub>CC SEG</sub> | Current per segment driver                                                          | Strong drive mode                                                                                                                                                                | _   | 260                    | _    | μA    |

| $V_{BIAS}$          | LCD bias range (V <sub>BIAS</sub> refers to the main output voltage(V0) of LCD DAC) | $V_{DDA} \ge 3 \text{ V and } V_{DDA} \ge V_{BIAS}$                                                                                                                              | 2   | _                      | 5    | V     |

|                     | LCD bias step size                                                                  | $V_{DDA} \ge 3 \text{ V and } V_{DDA} \ge V_{BIAS}$                                                                                                                              | _   | 9.1 × V <sub>DDA</sub> | _    | mV    |

|                     | LCD capacitance per segment/ common driver                                          | Drivers may be combined                                                                                                                                                          | _   | 500                    | 5000 | pF    |

|                     | Maximum segment DC offset                                                           | $V_{DDA} \ge 3V$ and $V_{DDA} \ge V_{BIAS}$                                                                                                                                      | _   | _                      | 20   | mV    |

| I <sub>OUT</sub>    | Output drive current per segment driver)                                            | V <sub>DDIO</sub> = 5.5 V, strong drive mode                                                                                                                                     | 355 | _                      | 710  | μA    |

#### Note

<sup>62.</sup> Based on device characterization (Not production tested).

# 11.8.3 Interrupt Controller

# Table 11-71. Interrupt Controller AC Specifications

| Parameter | Description                                                                                           | Conditions | Min | Тур | Max | Units   |

|-----------|-------------------------------------------------------------------------------------------------------|------------|-----|-----|-----|---------|

|           | Delay from interrupt signal input to ISR code execution from main line code <sup>[80]</sup>           |            | _   | _   | 12  | Tcy CPU |

|           | Delay from interrupt signal input to ISR code execution from ISR code (tail-chaining) <sup>[80]</sup> |            | _   | _   | 6   | Tcy CPU |

## 11.8.4 JTAG Interface

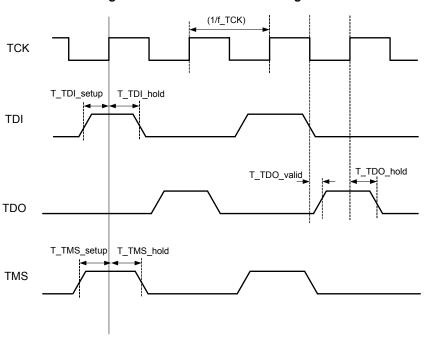

Figure 11-74. JTAG Interface Timing

Table 11-72. JTAG Interface AC Specifications [81]

| Parameter   | Description                  | Conditions                                           | Min        | Тур | Max                | Units |

|-------------|------------------------------|------------------------------------------------------|------------|-----|--------------------|-------|

| f_TCK       | TCK frequency                | $3.3 \text{ V} \leq \text{V}_{DDD} \leq 5 \text{ V}$ | -          | _   | 12 <sup>[82]</sup> | MHz   |

|             |                              | 1.71 V ≤ V <sub>DDD</sub> < 3.3 V                    | _          | -   | 7 <sup>[82]</sup>  | MHz   |

| T_TDI_setup | TDI setup before TCK high    |                                                      | (T/10) - 5 |     | _                  | ns    |

| T_TMS_setup | TMS setup before TCK high    |                                                      | T/4        | ı   | _                  |       |

| T_TDI_hold  | TDI, TMS hold after TCK high | T = 1/f_TCK max                                      | T/4        | ı   | _                  |       |

| T_TDO_valid | TCK low to TDO valid         | T = 1/f_TCK max                                      | -          | ı   | 2T/5               |       |

| T_TDO_hold  | TDO hold after TCK high      | T = 1/f_TCK max                                      | T/4        | ı   | _                  |       |

| T_nTRST     | Minimum nTRST pulse width    | f_TCK = 2 MHz                                        | 8          | _   | _                  | ns    |

## Notes

80. ARM Cortex-M3 NVIC spec. Visit www.arm.com for detailed documentation about the Cortex-M3 CPU.

<sup>81.</sup> Based on device characterization (Not production tested).

<sup>82.</sup> f\_TCK must also be no more than 1/3 CPU clock frequency.

Table 11-76. IMO AC Specifications

| Parameter                        | Description                                                      | Conditions                                                                                                                     | Min        | Тур | Max  | Units |  |  |

|----------------------------------|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|------------|-----|------|-------|--|--|

|                                  | IMO frequency stability (with factory trim)                      |                                                                                                                                |            |     |      |       |  |  |

|                                  | 74.7 MHz                                                         |                                                                                                                                | <b>-</b> 7 | -   | 7    | %     |  |  |

|                                  | 62.6 MHz                                                         |                                                                                                                                | <b>-7</b>  | _   | 7    | %     |  |  |

|                                  | 48 MHz                                                           |                                                                                                                                | -5         | -   | 5    | %     |  |  |

|                                  | 24 MHz – Non USB mode                                            |                                                                                                                                | -4         | -   | 4    | %     |  |  |

|                                  | 24 MHz – USB mode                                                | With oscillator locking to USB bus                                                                                             | -0.25      | _   | 0.25 | %     |  |  |

| F <sub>IMO</sub> <sup>[87]</sup> | 12 MHz                                                           |                                                                                                                                | -3         | _   | 3    | %     |  |  |

|                                  | 6 MHz                                                            |                                                                                                                                | -2         | -   | 2    | %     |  |  |

|                                  | 3 MHz                                                            | 0 °C to 70 °C                                                                                                                  | -1         | -   | 1    | %     |  |  |

|                                  |                                                                  | –40 °C to 105 °C                                                                                                               | -1.5       | _   | 1.5  | %     |  |  |

|                                  | 3 MHz frequency stability after typical PCB assembly post-reflow | Typical (non-optimized) board layout and 250 °C solder reflow. Device may be calibrated after assembly to improve performance. | -          | ±2% | _    | %     |  |  |

| Tstart_imo                       | Startup time <sup>[88]</sup>                                     | From enable (during normal system operation)                                                                                   | -          | _   | 13   | μs    |  |  |

|                                  | Jitter (peak to peak)[88]                                        |                                                                                                                                |            | I.  | l .  | 1     |  |  |

| Јр–р                             | F = 24 MHz                                                       |                                                                                                                                | _          | 0.9 | _    | ns    |  |  |

|                                  | F = 3 MHz                                                        |                                                                                                                                | _          | 1.6 | -    | ns    |  |  |

|                                  | Jitter (long term) <sup>[88]</sup>                               |                                                                                                                                |            |     | i.   |       |  |  |

| Jperiod                          | F = 24 MHz                                                       |                                                                                                                                | -          | 0.9 | _    | ns    |  |  |

|                                  | F = 3 MHz                                                        |                                                                                                                                | _          | 12  | -    | ns    |  |  |

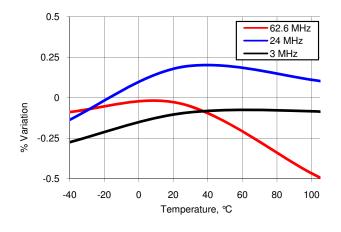

Figure 11-77. IMO Frequency Variation vs. Temperature

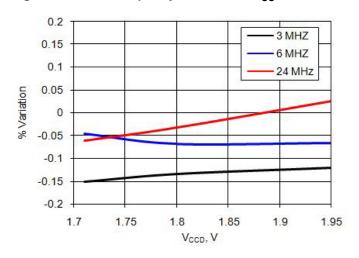

Figure 11-78. IMO Frequency Variation vs.  $V_{\text{CC}}$

### Notes

87. F<sub>IMO</sub> is measured after packaging, and thus accounts for substrate and die attach stresses. 88. Based on device characterization (Not production tested).