#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                              |

| Core Size                  | 32-Bit Single-Core                                                           |

| Speed                      | 80MHz                                                                        |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                       |

| Peripherals                | CapSense, DMA, LCD, POR, PWM, WDT                                            |

| Number of I/O              | 62                                                                           |

| Program Memory Size        | 256KB (256K x 8)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 2K x 8                                                                       |

| RAM Size                   | 64K × 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 5.5V                                                                 |

| Data Converters            | A/D 2x12b; D/A 4x8b                                                          |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 100-LQFP                                                                     |

| Supplier Device Package    | 100-TQFP (14x14)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c5688axi-lp099 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 4.3 DMA and PHUB

The PHUB and the DMA controller are responsible for data transfer between the CPU and peripherals, and also data transfers between peripherals. The PHUB and DMA also control device configuration during boot. The PHUB consists of:

- A central hub that includes the DMA controller, arbiter, and router

- Multiple spokes that radiate outward from the hub to most peripherals

There are two PHUB masters: the CPU and the DMA controller. Both masters may initiate transactions on the bus. The DMA channels can handle peripheral communication without CPU intervention. The arbiter in the central hub determines which DMA channel is the highest priority if there are multiple requests.

#### 4.3.1 PHUB Features

- CPU and DMA controller are both bus masters to the PHUB

- Eight multi-layer AHB bus parallel access paths (spokes) for peripheral access

- Simultaneous CPU and DMA access to peripherals located on different spokes

- Simultaneous DMA source and destination burst transactions on different spokes

Supports 8, 16, 24, and 32-bit addressing and data Table 4-3. PHUB Spokes and Peripherals

| PHUB Spokes | Peripherals                                                                                         |

|-------------|-----------------------------------------------------------------------------------------------------|

| 0           | SRAM                                                                                                |

| 1           | IOs, PICU, EMIF                                                                                     |

| 2           | PHUB local configuration, Power manager,<br>Clocks, IC, SWV, EEPROM, Flash<br>programming interface |

| 3           | Analog interface and trim, Decimator                                                                |

| 4           | USB, I <sup>2</sup> C, CAN, Timers, Counters, and PWMs                                              |

| 5           | DFB                                                                                                 |

| 6           | UDBs group 1                                                                                        |

| 7           | UDBs group 2                                                                                        |

#### 4.3.2 DMA Features

- 24 DMA channels

- Each channel has one or more Transaction Descriptors (TDs) to configure channel behavior. Up to 128 total TDs can be defined

- TDs can be dynamically updated

- Eight levels of priority per channel

- Any digitally routable signal, the CPU, or another DMA channel, can trigger a transaction

- Each channel can generate up to two interrupts per transfer

- Transactions can be stalled or canceled

- Supports transaction size of infinite or 1 to 64k bytes

- Large transactions may be broken into smaller bursts of 1 to 127 bytes

- TDs may be nested and/or chained for complex transactions

#### 4.3.3 Priority Levels

The CPU always has higher priority than the DMA controller when their accesses require the same bus resources. Due to the system architecture, the CPU can never starve the DMA. DMA channels of higher priority (lower priority number) may interrupt current DMA transfers. In the case of an interrupt, the current transfer is allowed to complete its current transaction. To ensure latency limits when multiple DMA accesses are requested simultaneously, a fairness algorithm guarantees an interleaved minimum percentage of bus bandwidth for priority levels 2 through 7. Priority levels 0 and 1 do not take part in the fairness algorithm and may use 100% of the bus bandwidth. If a tie occurs on two DMA requests of the same priority level, a simple round robin method is used to evenly share the allocated bandwidth. The round robin allocation can be disabled for each DMA channel, allowing it to always be at the head of the line. Priority levels 2 to 7 are guaranteed the minimum bus bandwidth shown in Table 4-4 after the CPU and DMA priority levels 0 and 1 have satisfied their requirements.

#### Table 4-4. Priority Levels

| Priority Level | % Bus Bandwidth |

|----------------|-----------------|

| 0              | 100.0           |

| 1              | 100.0           |

| 2              | 50.0            |

| 3              | 25.0            |

| 4              | 12.5            |

| 5              | 6.2             |

| 6              | 3.1             |

| 7              | 1.5             |

When the fairness algorithm is disabled, DMA access is granted based solely on the priority level; no bus bandwidth guarantees are made.

#### 4.3.4 Transaction Modes Supported

The flexible configuration of each DMA channel and the ability to chain multiple channels allow the creation of both simple and complex use cases. General use cases include, but are not limited to:

#### 4.3.4.1 Simple DMA

In a simple DMA case, a single TD transfers data between a source and sink (peripherals or memory location). The basic timing diagrams of DMA read and write cycles are shown in Figure 4-2. For more description on other transfer modes, refer to the Technical Reference Manual.

#### Table 4-6. Interrupt Vector Table

| Interrupt # | Cortex-M3 Exception # | Fixed Function           | DMA               | UDB          |

|-------------|-----------------------|--------------------------|-------------------|--------------|

| 0           | 16                    | Low voltage detect (LVD) | phub_termout0[0]  | udb_intr[0]  |

| 1           | 17                    | Cache/ECC                | phub_termout0[1]  | udb_intr[1]  |

| 2           | 18                    | Reserved                 | phub_termout0[2]  | udb_intr[2]  |

| 3           | 19                    | Sleep (Pwr Mgr)          | phub_termout0[3]  | udb_intr[3]  |

| 4           | 20                    | PICU[0]                  | phub_termout0[4]  | udb_intr[4]  |

| 5           | 21                    | PICU[1]                  | phub_termout0[5]  | udb_intr[5]  |

| 6           | 22                    | PICU[2]                  | phub_termout0[6]  | udb_intr[6]  |

| 7           | 23                    | PICU[3]                  | phub_termout0[7]  | udb_intr[7]  |

| 8           | 24                    | PICU[4]                  | phub_termout0[8]  | udb_intr[8]  |

| 9           | 25                    | PICU[5]                  | phub_termout0[9]  | udb_intr[9]  |

| 10          | 26                    | PICU[6]                  | phub_termout0[10] | udb_intr[10] |

| 11          | 27                    | PICU[12]                 | phub_termout0[11] | udb_intr[11] |

| 12          | 28                    | PICU[15]                 | phub_termout0[12] | udb_intr[12] |

| 13          | 29                    | Comparators Combined     | phub_termout0[13] | udb_intr[13] |

| 14          | 30                    | Switched Caps Combined   | phub_termout0[14] | udb_intr[14] |

| 15          | 31                    | l <sup>2</sup> C         | phub_termout0[15] | udb_intr[15] |

| 16          | 32                    | CAN                      | phub_termout1[0]  | udb_intr[16] |

| 17          | 33                    | Timer/Counter0           | phub_termout1[1]  | udb_intr[17] |

| 18          | 34                    | Timer/Counter1           | phub_termout1[2]  | udb_intr[18] |

| 19          | 35                    | Timer/Counter2           | phub_termout1[3]  | udb_intr[19] |

| 20          | 36                    | Timer/Counter3           | phub_termout1[4]  | udb_intr[20] |

| 21          | 37                    | USB SOF Int              | phub_termout1[5]  | udb_intr[21] |

| 22          | 38                    | USB Arb Int              | phub_termout1[6]  | udb_intr[22] |

| 23          | 39                    | USB Bus Int              | phub_termout1[7]  | udb_intr[23] |

| 24          | 40                    | USB Endpoint[0]          | phub_termout1[8]  | udb_intr[24] |

| 25          | 41                    | USB Endpoint Data        | phub_termout1[9]  | udb_intr[25] |

| 26          | 42                    | Reserved                 | phub_termout1[10] | udb_intr[26] |

| 27          | 43                    | LCD                      | phub_termout1[11] | udb_intr[27] |

| 28          | 44                    | DFB Int                  | phub_termout1[12] | udb_intr[28] |

| 29          | 45                    | Decimator Int            | phub_termout1[13] | udb_intr[29] |

| 30          | 46                    | phub_err_int             | phub_termout1[14] | udb_intr[30] |

| 31          | 47                    | eeprom_fault_int         | phub_termout1[15] | udb_intr[31] |

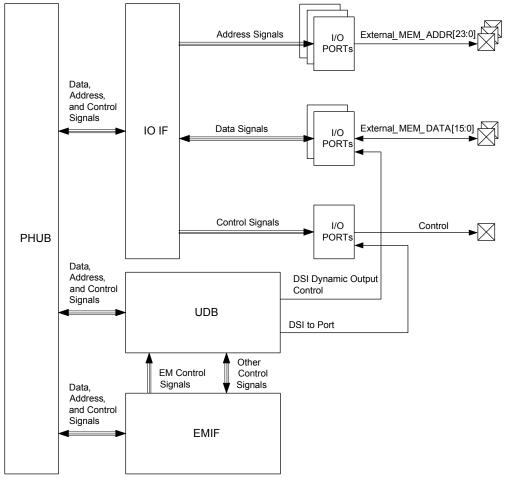

#### 5.6 External Memory Interface

CY8C56LP provides an External Memory Interface (EMIF) for connecting to external memory devices. The connection allows read and write accesses to external memories. The EMIF operates in conjunction with UDBs, I/O ports, and other hardware to generate external memory address and control signals. At 33 MHz, each memory access cycle takes four bus clock cycles. Figure 5-1 is the EMIF block diagram. The EMIF supports synchronous and asynchronous memories. The CY8C56LP only supports one type of external memory device at a time. External memory is located in the Cortex-M3 external RAM space; it can use up to 24 address bits. See Table 5-4 on page 22Memory Map on page 22. The memory can be 8 or 16 bits wide.

Cortex-M3 instructions can be fetched from external memory if it is 16-bit. Other limitations apply; for details, see application note AN89610, PSoC<sup>®</sup> 4 and PSoC 5LP ARM Cortex Code Optimization. There is no provision for code security in external memory. If code must be kept secure, then it should be placed in internal flash. See Flash Security on page 19 and Device Security on page 64.

Figure 5-1. EMIF Block Diagram

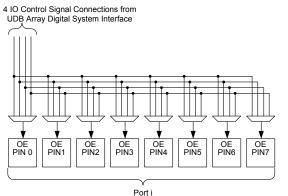

#### Figure 7-13. I/O Pin Output Enable Connectivity

YPRESS

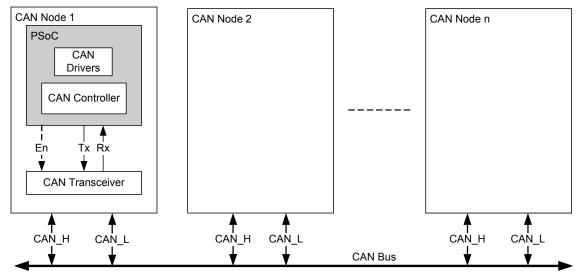

#### 7.5 CAN

The CAN peripheral is a fully functional Controller Area Network (CAN) supporting communication baud rates up to 1 Mbps. The CAN controller implements the CAN2.0A and CAN2.0B specifications as defined in the Bosch specification and conforms to the ISO-11898-1 standard. The CAN protocol was originally designed for automotive applications with a focus on a high level of fault detection. This ensures high communication reliability at a low cost. Because of its success in automotive applications, CAN is used as a standard communication protocol for motion oriented machine control networks (CANOpen) and factory automation applications (DeviceNet). The CAN controller features allow the efficient implementation of higher level without affecting the performance of the protocols microcontroller CPU. Full configuration support is provided in PSoC Creator.

#### Figure 7-14. CAN Bus System Implementation

#### 7.5.1 CAN Features

- CAN2.0A/B protocol implementation ISO 11898 compliant

Standard and extended frames with up to 8 bytes of data per frame

- Message filter capabilities

- Remote Transmission Request (RTR) support

- Programmable bit rate up to 1 Mbps

- Listen Only mode

- SW readable error counter and indicator

- Sleep mode: Wake the device from sleep with activity on the Rx pin

- Supports two or three wire interface to external transceiver (Tx, Rx, and Enable). The three-wire interface is compatible with the Philips PHY; the PHY is not included on-chip. The three wires can be routed to any I/O

Enhanced interrupt controller

- CAN receive and transmit buffers status

- CAN controller error status including BusOff

#### Receive path

- In 16 receive buffers each with its own message filter

- Enhanced hardware message filter implementation that covers the ID, IDE and RTR

- DeviceNet addressing support

- Multiple receive buffers linkable to build a larger receive message array

- Automatic transmission request (RTR) response handler

- Lost received message notification

- Transmit path

- Eight transmit buffers

- Programmable transmit priority

- Round robin

- Fixed priority

- Message transmissions abort capability

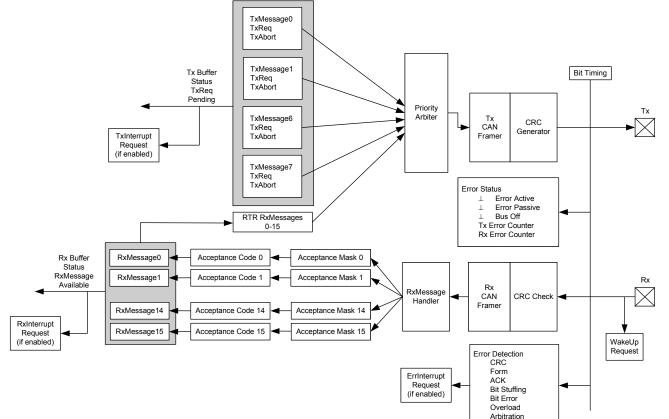

#### 7.5.2 Software Tools Support

CAN Controller configuration integrated into PSoC Creator:

- CAN Configuration walkthrough with bit timing analyzer

- Receive filter setup

Figure 7-15. CAN Controller Block Diagram

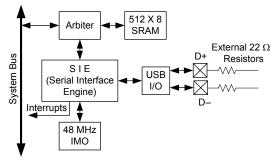

#### 7.6 USB

PSoC includes a dedicated FS (12 Mbps) USB 2.0 transceiver supporting all four USB transfer types: control, interrupt, bulk, and isochronous. PSoC Creator provides full configuration support. USB interfaces to hosts through two dedicated USBIO pins, which are detailed in the "I/O System and Routing" section on page 32.

USB includes the following features:

- Eight unidirectional data endpoints

- One bidirectional control endpoint 0 (EP0)

- Shared 512-byte buffer for the eight data endpoints

- Dedicated 8-byte buffer for EP0

- Three memory modes

- Manual Memory Management with No DMA Access

- Manual Memory Management with Manual DMA Access

- Automatic Memory Management with Automatic DMA Access

- Internal 3.3 V regulator for transceiver

- Internal 48 MHz oscillator that auto locks to USB bus clock, requiring no external crystal for USB (USB equipped parts only)

- Interrupts on bus and each endpoint event, with device wakeup

- USB Reset, Suspend, and Resume operations

- Bus powered and self powered modes

#### Figure 7-16. USB

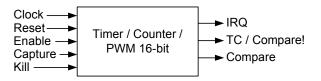

## 7.7 Timers, Counters, and PWMs

The Timer/Counter/PWM peripheral is a 16-bit dedicated peripheral providing three of the most common embedded peripheral features. As almost all embedded systems use some combination of timers, counters, and PWMs. Four of them have been included on this PSoC device family. Additional and more advanced functionality timers, counters, and PWMs can also be instantiated in Universal Digital Blocks (UDBs) as required. PSoC Creator allows you to choose the timer, counter, and PWM features that they require. The tool set utilizes the most optimal resources available.

The Timer/Counter/PWM peripheral can select from multiple clock sources, with input and output signals connected through the DSI routing. DSI routing allows input and output connections to any device pin and any internal digital signal accessible through the DSI. Each of the four instances has a compare output, terminal count output (optional complementary compare output), and programmable interrupt request line. The Timer/Counter/PWMs are configurable as free running, one shot, or Enable input controlled. The peripheral has timer reset and capture inputs, and a kill input for control of the comparator outputs. The peripheral supports full 16-bit capture.

Timer/Counter/PWM features include:

- 16-bit Timer/Counter/PWM (down count only)

- Selectable clock source

- PWM comparator (configurable for LT, LTE, EQ, GTE, GT)

- Period reload on start, reset, and terminal count

- Interrupt on terminal count, compare true, or capture

- Dynamic counter reads

- Timer capture mode

- Count while enable signal is asserted mode

- Free run mode

- One Shot mode (stop at end of period)

- Complementary PWM outputs with deadband

- PWM output kill

#### Figure 7-17. Timer/Counter/PWM

## 7.8 I<sup>2</sup>C

PSoC includes a single fixed-function  $I^2C$  peripheral. Additional  $I^2C$  interfaces can be instantiated using Universal Digital Blocks (UDBs) in PSoC Creator, as required.

The I<sup>2</sup>C peripheral provides a synchronous two-wire interface designed to interface the PSoC device with a two-wire I<sup>2</sup>C serial communication bus. It is compatible<sup>[13]</sup> with I<sup>2</sup>C Standard-mode, Fast-mode, and Fast-mode Plus devices as defined in the NXP I<sup>2</sup>C-bus specification and user manual (UM10204). The I<sup>2</sup>C bus I/O may be implemented with GPIO or SIO in open-drain modes.

To eliminate the need for excessive CPU intervention and overhead,  $I^2C$  specific support is provided for status detection and generation of framing bits.  $I^2C$  operates as a slave, a master, or multimaster (Slave and Master)<sup>[13]</sup>. In slave mode, the unit always listens for a start condition to begin sending or receiving data. Master mode supplies the ability to generate the Start and Stop conditions and initiate transactions. Multimaster mode provides clock synchronization and arbitration to allow multiple masters on the same bus. If Master mode is enabled and Slave mode is not enabled, the block does not generate interrupts on externally generated Start conditions.  $I^2C$  interfaces through the DSI routing and allows direct connections to any GPIO or SIO pins.

I<sup>2</sup>C provides hardware address detect of a 7-bit address without CPU intervention. Additionally the device can wake from low power modes on a 7-bit hardware address match. If wakeup functionality is required, I<sup>2</sup>C pin connections are limited to one of two specific pairs of SIO pins. See descriptions of SCL and SDA pins in Pin Descriptions on page 11.

I<sup>2</sup>C features include:

- Slave and master, transmitter, and receiver operation

- Byte processing for low CPU overhead

- Interrupt or polling CPU interface

- Support for bus speeds up to 1 Mbps

- 7 or 10-bit addressing (10-bit addressing requires firmware support)

- SMBus operation (through firmware support SMBus supported in hardware in UDBs)

- 7-bit hardware address compare

- Wake from low power modes on address match

- Glitch filtering (active and alternate-active modes only)

Data transfers follow the format shown in Figure 7-18. After the START condition (S), a slave address is sent. This address is 7 bits long followed by an eighth bit which is a data direction bit (R/W) - a 'zero' indicates a transmission (WRITE), a 'one' indicates a request for data (READ). A data transfer is always terminated by a STOP condition (P) generated by the master.

#### Notes

- 12. The I<sup>2</sup>C peripheral is non-compliant with the NXP I<sup>2</sup>C specification in the following areas: analog glitch filter, I/O V<sub>OL</sub>/I<sub>OL</sub>, I/O hysteresis. The I<sup>2</sup>C Block has a digital glitch filter (not available in sleep mode). The Fast-mode minimum fall-time specification can be met by setting the I/Os to slow speed mode. See the I/O Electrical Specifications in "Inputs and Outputs" section on page 75 for details.

- 13. Fixed-block I<sup>2</sup>C does not support undefined bus conditions, nor does it support Repeated Start in Slave mode. These conditions should be avoided, or the UDB-based I<sup>2</sup>C component should be used instead.

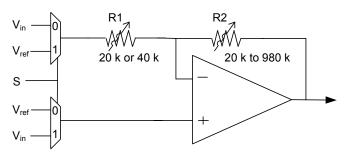

#### 8.6.3 PGA

The PGA amplifies an external or internal signal. The PGA can be configured to operate in inverting mode or noninverting mode. The PGA function may be configured for both positive and negative gains as high as 50 and 49 respectively. The gain is adjusted by changing the values of R1 and R2 as illustrated in Figure 8-9. The schematic in Figure 8-9 shows the configuration and possible resistor settings for the PGA. The gain is switched from inverting and non inverting by changing the shared select value of the both the input muxes. The bandwidth for each gain case is listed in Table 8-3.

#### Table 8-3. Bandwidth

| Gain | Bandwidth |

|------|-----------|

| 1    | 6.0 MHz   |

| 24   | 340 kHz   |

| 48   | 220 kHz   |

| 50   | 215 kHz   |

#### Figure 8-9. PGA Resistor Settings

The PGA is used in applications where the input signal may not be large enough to achieve the desired resolution in the ADC, or dynamic range of another SC/CT block such as a mixer. The gain is adjustable at runtime, including changing the gain of the PGA prior to each ADC sample.

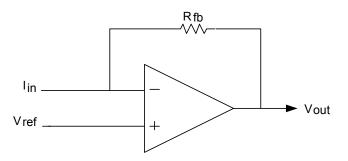

#### 8.6.4 TIA

The Transimpedance Amplifier (TIA) converts an internal or external current to an output voltage. The TIA uses an internal feedback resistor in a continuous time configuration to convert input current to output voltage. For an input current I<sub>in</sub>, the output voltage is V<sub>REF</sub> - I<sub>in</sub> x R<sub>fb</sub>, where V<sub>REF</sub> is the value placed on the non inverting input. The feedback resistor Rfb is programmable between 20 K $\Omega$  and 1 M $\Omega$  through a configuration register. Table 8-4 shows the possible values of Rfb and associated configuration settings.

| Table 8-4. | Feedback | Resistor | Settings |

|------------|----------|----------|----------|

|------------|----------|----------|----------|

| Configuration Word | Nominal R <sub>fb</sub> (KΩ) |

|--------------------|------------------------------|

| 000b               | 20                           |

| 001b               | 30                           |

| 010b               | 40                           |

| 011b               | 60                           |

| 100b               | 120                          |

#### Table 8-4. Feedback Resistor Settings

| 101b | 250  |

|------|------|

| 110b | 500  |

| 111b | 1000 |

#### Figure 8-10. Continuous Time TIA Schematic

The TIA configuration is used for applications where an external sensor's output is current as a function of some type of stimulus such as temperature, light, magnetic flux etc. In a common application, the voltage DAC output can be connected to the  $V_{REF}$  TIA input to allow calibration of the external sensor bias current by adjusting the voltage DAC output voltage.

#### 8.7 LCD Direct Drive

The PSoC Liquid Crystal Display (LCD) driver system is a highly configurable peripheral designed to allow PSoC to directly drive a broad range of LCD glass. All voltages are generated on chip, eliminating the need for external components. With a high multiplex ratio of up to 1/16, the CY8C56LP family LCD driver system can drive a maximum of 736 segments. The PSoC LCD driver module was also designed with the conservative power budget of portable devices in mind, enabling different LCD drive modes and power down modes to conserve power.

PSoC Creator provides an LCD segment drive component. The component wizard provides easy and flexible configuration of LCD resources. You can specify pins for segments and commons along with other options. The software configures the device to meet the required specifications. This is possible because of the programmability inherent to PSoC devices.

Key features of the PSoC LCD segment system are:

- LCD panel direct driving

- Type A (standard) and Type B (low power) waveform support

- Wide operating voltage range support (2 V to 5 V) for LCD panels

- Static, 1/2, 1/3, 1/4, 1/5 bias voltage levels

- Internal bias voltage generation through internal resistor ladder

- Up to 62 total common and segment outputs

- Up to 1/16 multiplex for a maximum of 16 backplane/common outputs

- Up to 62 front plane/segment outputs for direct drive

- Drives up to 736 total segments (16 backplane x 46 front plane)

- Up to 64 levels of software controlled contrast

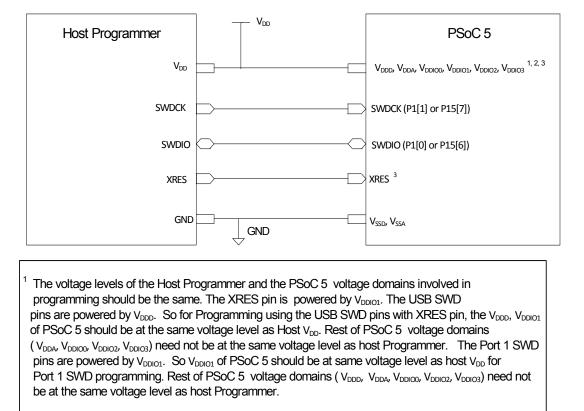

#### 9.2 SWD Interface

The SWD interface is the preferred alternative to the JTAG interface. It requires only two pins instead of the four or five needed by JTAG. SWD provides all of the programming and debugging features of JTAG at the same speed. SWD does not provide access to scan chains or device chaining. The SWD clock frequency can be up to 1/3 of the CPU clock frequency.

SWD uses two pins, either two of the JTAG pins (TMS and TCK) or the USBIO D+ and D- pins. The USBIO pins are useful for in system programming of USB solutions that would otherwise require a separate programming connector. One pin is used for the data clock and the other is used for data input and output.

SWD can be enabled on only one of the pin pairs at a time. This only happens if, within 8 µs (key window) after reset, that pin pair

(JTAG or USB) receives a predetermined acquire sequence of 1s and 0s. If the NVL latches are set for SWD (see Section 5.5), this sequence need not be applied to the JTAG pin pair. The acquire sequence must always be applied to the USB pin pair.

SWD is used for debugging or for programming the flash memory.

The SWD interface can be enabled from the JTAG interface or disabled, allowing its pins to be used as GPIO. Unlike JTAG, the SWD interface can always be reacquired on any device during the key window. It can then be used to reenable the JTAG interface, if desired. When using SWD or JTAG pins as standard GPIO, make sure that the GPIO functionality and PCB circuits do not interfere with SWD or JTAG use.

Figure 9-2. SWD Interface Connections between PSoC 5LP and Programmer

<sup>2</sup> Vdda must be greater than or equal to all other power supplies (Vddd, Vddio's) in PSoC 5.

For Power cycle mode Programming, XRES pin is not required. But the Host programmer must have the capability to toggle power (Vddd, Vdda, All Vddio's) to PSoC 5. This may typically require external interface circuitry to toggle power which will depend on the programming setup. The power supplies can be brought up in any sequence, however, once stable, VDDA must be greater than or equal to all other supplies.

#### 11.4 Inputs and Outputs

Specifications are valid for –40 °C  $\leq$  T<sub>A</sub>  $\leq$  105 °C and T<sub>J</sub>  $\leq$  120 °C, except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted. Unless otherwise specified, all charts and graphs show typical values.

When the power supplies ramp up, there are low-impedance connections between each GPIO pin and its  $V_{DDIO}$  supply. This causes the pin voltages to track  $V_{DDIO}$  until both  $V_{DDIO}$  and  $V_{DDA}$  reach the IPOR voltage, which can be as high as 1.45 V. At that point the low-impedance connections no longer exist, and the pins change to their normal NVL settings.

Also, if  $V_{DDA}$  is less than  $V_{DDIO}$ , a low-impedance path may exist between a GPIO and  $V_{DDA}$ , causing the GPIO to track  $V_{DDA}$  until  $V_{DDA}$  becomes greater than or equal to  $V_{DDIO}$ .

#### 11.4.1 GPIO

#### Table 11-8. GPIO DC Specifications

| Parameter       | Description                                                   | Conditions                                               | Min                           | Тур | Max                   | Units |

|-----------------|---------------------------------------------------------------|----------------------------------------------------------|-------------------------------|-----|-----------------------|-------|

| V <sub>IH</sub> | Input voltage high threshold                                  | CMOS Input, PRT[x]CTL = 0                                | $0.7 \times V_{DDIO}$         | _   | -                     | V     |

| V <sub>IL</sub> | Input voltage low threshold                                   | CMOS Input, PRT[x]CTL = 0                                | _                             | -   | $0.3 \times V_{DDIO}$ | V     |

| V <sub>IH</sub> | Input voltage high threshold                                  | LVTTL Input, PRT[x]CTL = 1,V <sub>DDIO</sub> < 2.7 V     | $0.7 	ext{ x V}_{	ext{DDIO}}$ | I   | -                     | V     |

| V <sub>IH</sub> | Input voltage high threshold                                  | LVTTL Input, PRT[x]CTL = 1, $V_{DDIO} \ge 2.7 \text{ V}$ | 2.0                           | I   | -                     | V     |

| V <sub>IL</sub> | Input voltage low threshold                                   | LVTTL Input, PRT[x]CTL = 1,V <sub>DDIO</sub> < 2.7 V     | _                             | I   | $0.3 \times V_{DDIO}$ | V     |

| V <sub>IL</sub> | Input voltage low threshold                                   | LVTTL Input, PRT[x]CTL = 1, $V_{DDIO} \ge 2.7 V$         | _                             | I   | 0.8                   | V     |

| V <sub>OH</sub> | Output voltage high                                           | I <sub>OH</sub> = 4 mA at 3.3 V <sub>DDIO</sub>          | V <sub>DDIO</sub> – 0.6       | I   | -                     | V     |

|                 |                                                               | I <sub>OH</sub> = 1 mA at 1.8 V <sub>DDIO</sub>          | $V_{DDIO} - 0.5$              | 1   | -                     | V     |

| V <sub>OL</sub> | Output voltage low                                            | I <sub>OL</sub> = 8 mA at 3.3 V <sub>DDIO</sub>          | -                             | 1   | 0.6                   | V     |

|                 |                                                               | I <sub>OL</sub> = 3 mA at 3.3 V <sub>DDIO</sub>          | -                             | I   | 0.4                   | V     |

|                 |                                                               | I <sub>OL</sub> = 4 mA at 1.8 V <sub>DDIO</sub>          | -                             | I   | 0.6                   | V     |

| Rpullup         | Pull up resistor                                              |                                                          | 3.5                           | 5.6 | 8.5                   | kΩ    |

| Rpulldown       | Pull down resistor                                            |                                                          | 3.5                           | 5.6 | 8.5                   | kΩ    |

| I <sub>IL</sub> | Input leakage current<br>(absolute value) <sup>[34]</sup>     | 25 °C, V <sub>DDIO</sub> = 3.0 V                         | -                             | Ι   | 2                     | nA    |

| C <sub>IN</sub> | Input capacitance <sup>[34]</sup>                             | P0.0, P0.1, P0.2, P3.6, P3.7                             | _                             | 17  | 20                    | pF    |

|                 |                                                               | P0.3, P0.4, P3.0, P3.1, P3.2                             | _                             | 10  | 15                    | pF    |

|                 |                                                               | P0.6, P0.7, P15.0, P15.6, P15.7 <sup>[35]</sup>          | _                             | 7   | 12                    | pF    |

|                 |                                                               | All other GPIOs                                          | _                             | 5   | 9                     | pF    |

| V <sub>H</sub>  | Input voltage hysteresis<br>(Schmitt–Trigger) <sup>[34]</sup> |                                                          | -                             | 40  | -                     | mV    |

| Idiode          | Current through protection diode to $V_{DDIO}$ and $V_{SSIO}$ |                                                          | -                             | Ι   | 100                   | μA    |

| Rglobal         | Resistance pin to analog<br>global bus                        | 25 °C, V <sub>DDIO</sub> = 3.0 V                         | -                             | 320 | -                     | Ω     |

| Rmux            | Resistance pin to analog mux bus                              | 25 °C, V <sub>DDIO</sub> = 3.0 V                         | -                             | 220 | -                     | Ω     |

Notes

34. Based on device characterization (Not production tested).

35. For information on designing with PSoC oscillators, refer to the application note, AN54439 - PSoC® 3 and PSoC 5 External Oscillator.

#### Table 11-21. Delta-sigma ADC AC Specifications

| Parameter     | Description                                                       | Conditions                                   | Min | Тур | Max    | Units   |

|---------------|-------------------------------------------------------------------|----------------------------------------------|-----|-----|--------|---------|

|               | Startup time                                                      |                                              | _   | -   | 4      | Samples |

| THD           | Total harmonic distortion <sup>[44]</sup>                         | Buffer gain = 1, 12-bit,<br>Range = ±1.024 V | _   | -   | 0.0032 | %       |

| 12-Bit Resolu | ition Mode                                                        |                                              |     |     |        |         |

| SR12          | Sample rate, continuous, high power <sup>[44]</sup>               | Range = ±1.024 V, unbuffered                 | 4   | -   | 192    | ksps    |

| BW12          | Input bandwidth at max sample rate <sup>[44]</sup>                | Range = ±1.024 V, unbuffered                 | -   | 44  | -      | kHz     |

| SINAD12int    | Signal to noise ratio, 12-bit, internal reference <sup>[44]</sup> | Range = ±1.024 V, unbuffered                 | 66  | -   | -      | dB      |

| 8-Bit Resolut | ion Mode                                                          | · · · ·                                      |     |     |        |         |

| SR8           | Sample rate, continuous, high power <sup>[44]</sup>               | Range = ±1.024 V, unbuffered                 | 8   | -   | 384    | ksps    |

| BW8           | Input bandwidth at max sample rate <sup>[44]</sup>                | Range = ±1.024 V, unbuffered                 | -   | 88  | _      | kHz     |

| SINAD8int     | Signal to noise ratio, 8-bit, internal reference <sup>[44]</sup>  | Range = ±1.024 V, unbuffered                 | 43  | —   | -      | dB      |

#### Table 11-22. Delta-sigma ADC Sample Rates, Range = ±1.024 V

| Resolution, | Conti | Continuous |      | Sample |

|-------------|-------|------------|------|--------|

| Bits        | Min   | Max        | Min  | Max    |

| 8           | 8000  | 384000     | 1911 | 91701  |

| 9           | 6400  | 307200     | 1543 | 74024  |

| 10          | 5566  | 267130     | 1348 | 64673  |

| 11          | 4741  | 227555     | 1154 | 55351  |

| 12          | 4000  | 192000     | 978  | 46900  |

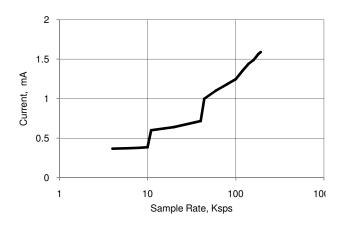

# Figure 11-33. Delta-sigma ADC IDD vs sps, Range = $\pm$ 1.024 V, Continuous Sample Mode, Input Buffer Bypassed

Note 44. Based on device characterization (Not production tested).

**YPRESS**

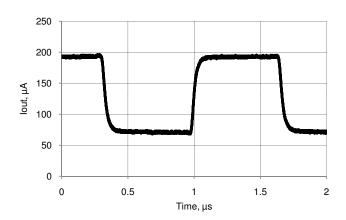

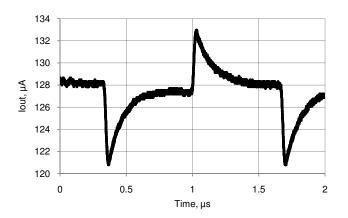

Figure 11-53. IDAC Glitch Response, Codes 0x7F - 0x80, 255  $\mu A$  Mode, Source Mode, Fast Mode,  $V_{DDA}$  = 5 V

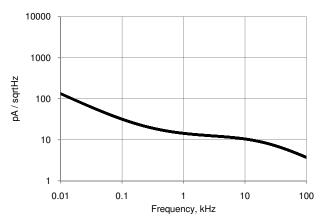

Figure 11-55. IDAC Current Noise, 255  $\mu$ A Mode, Source Mode, Fast Mode, V<sub>DDA</sub> = 5 V

## 11.5.8 Voltage Digital to Analog Converter (VDAC)

See the VDAC component datasheet in PSoC Creator for full electrical specifications and APIs.

Unless otherwise specified, all charts and graphs show typical values.

### Table 11-32. VDAC DC Specifications

| Parameter        | Description                               | Conditions                        | Min | Тур  | Max  | Units     |

|------------------|-------------------------------------------|-----------------------------------|-----|------|------|-----------|

|                  | Resolution                                |                                   | -   | 8    | I    | bits      |

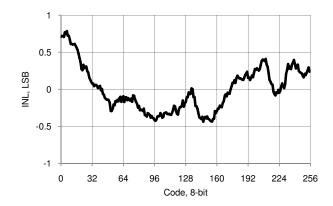

| INL1             | Integral nonlinearity                     | 1 V scale                         | -   | ±2.1 | ±2.5 | LSB       |

| INL4             | Integral nonlinearity <sup>[57]</sup>     | 4 V scale                         | -   | ±2.1 | ±2.5 | LSB       |

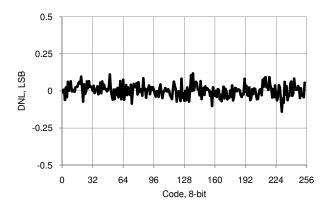

| DNL1             | Differential nonlinearity                 | 1 V scale                         | -   | ±0.3 | ±1   | LSB       |

| DNL4             | Differential nonlinearity <sup>[57]</sup> | 4 V scale                         | -   | ±0.3 | ±1   | LSB       |

| Rout             | Output resistance                         | 1 V scale                         | -   | 4    | 1    | kΩ        |

|                  |                                           | 4 V scale                         | -   | 16   | Ι    | kΩ        |

| V <sub>OUT</sub> | Output voltage range, code = 255          | 1 V scale                         | -   | 1.02 | Ι    | V         |

|                  |                                           | 4 V scale, V <sub>DDA</sub> = 5 V | -   | 4.08 | 1    | V         |

|                  | Monotonicity                              |                                   | -   | _    | Yes  | -         |

| V <sub>OS</sub>  | Zero scale error                          |                                   | -   | 0    | ±0.9 | LSB       |

| Eg               | Gain error                                | 1 V scale                         | -   | -    | ±2.5 | %         |

|                  |                                           | 4 V scale                         | -   | _    | ±2.5 | %         |

| TC_Eg            | Temperature coefficient, gain error       | 1 V scale                         | -   | _    | 0.03 | %FSR/°C   |

|                  |                                           | 4 V scale                         | -   | -    | 0.03 | %FSR / °C |

| I <sub>DD</sub>  | Operating current <sup>[57]</sup>         | Slow mode                         | -   | -    | 100  | μA        |

|                  |                                           | Fast mode                         | -   | -    | 500  | μA        |

## Figure 11-56. VDAC INL vs Input Code, 1 V Mode

#### Figure 11-57. VDAC DNL vs Input Code, 1 V Mode

Note 57. Based on device characterization (Not production tested).

## Table 11-42. LCD Direct Drive AC Specifications<sup>[63]</sup>

| Parameter        | Description    | Conditions | Min | Тур | Max | Units |

|------------------|----------------|------------|-----|-----|-----|-------|

| f <sub>LCD</sub> | LCD frame rate |            | 10  | 50  | 150 | Hz    |

#### **11.6 Digital Peripherals**

Specifications are valid for -40  $^{\circ}C \le T_A \le 105 ^{\circ}C$  and  $T_J \le 120 ^{\circ}C$ , except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted.

#### 11.6.1 Timer

The following specifications apply to the Timer/Counter/PWM peripheral in timer mode. Timers can also be implemented in UDBs; for more information, see the Timer component datasheet in PSoC Creator.

#### Table 11-43. Timer DC Specifications<sup>[63]</sup>

| Parameter | Description               | Conditions                                       | Min | Тур | Max | Units |

|-----------|---------------------------|--------------------------------------------------|-----|-----|-----|-------|

|           | Block current consumption | 16-bit timer, at listed input clock<br>frequency | -   | -   | -   | μA    |

|           | 3 MHz                     |                                                  | -   | 15  | -   | μA    |

|           | 12 MHz                    |                                                  | _   | 60  | -   | μA    |

|           | 48 MHz                    |                                                  | _   | 260 | _   | μA    |

|           | 80 MHz                    |                                                  | -   | 360 | -   | μA    |

Table 11-44. Timer AC Specifications<sup>[63]</sup>

| Parameter | Description                                    | Conditions | Min | Тур | Max   | Units |

|-----------|------------------------------------------------|------------|-----|-----|-------|-------|

|           | Operating frequency                            |            | DC  | -   | 80.01 | MHz   |

|           | Capture pulse width (Internal) <sup>[64]</sup> |            | 15  | _   | _     | ns    |

|           | Capture pulse width (external)                 |            | 30  | -   | _     | ns    |

|           | Timer resolution <sup>[64]</sup>               |            | 15  | -   | _     | ns    |

|           | Enable pulse width <sup>[64]</sup>             |            | 15  | _   | _     | ns    |

|           | Enable pulse width (external)                  |            | 30  | -   | _     | ns    |

|           | Reset pulse width <sup>[64]</sup>              |            | 15  | -   | -     | ns    |

|           | Reset pulse width (external)                   |            | 30  | -   | -     | ns    |

#### 11.6.2 Counter

The following specifications apply to the Timer/Counter/PWM peripheral, in counter mode. Counters can also be implemented in UDBs; for more information, see the Counter component datasheet in PSoC Creator.

## Table 11-45. Counter DC Specifications<sup>[63]</sup>

| Parameter | Description               | Conditions                                      | Min | Тур | Max | Units |

|-----------|---------------------------|-------------------------------------------------|-----|-----|-----|-------|

|           | Block current consumption | 16-bit counter, at listed input clock frequency | -   | -   | -   | μA    |

|           | 3 MHz                     |                                                 | -   | 15  | -   | μA    |

|           | 12 MHz                    |                                                 | -   | 60  | -   | μA    |

|           | 48 MHz                    |                                                 | -   | 260 | -   | μA    |

|           | 80 MHz                    |                                                 | _   | 360 | _   | μA    |

Notes

<sup>63.</sup> Based on device characterization (Not production tested).

64. For correct operation, the minimum Timer/Counter/PWM input pulse width is the period of bus clock.

#### 11.6.8 Universal Digital Blocks (UDBs)

PSoC Creator provides a library of pre-built and tested standard digital peripherals (UART, SPI, LIN, PRS, CRC, timer, counter, PWM, AND, OR, and so on) that are mapped to the UDB array. See the component datasheets in PSoC Creator for full AC/DC specifications, APIs, and example code.

#### Table 11-56. UDB AC Specifications<sup>[70]</sup>

| Parameter              | Description                                                   | Conditions                                       | Min | Тур | Max   | Units |

|------------------------|---------------------------------------------------------------|--------------------------------------------------|-----|-----|-------|-------|

| Datapath Per           | formance                                                      |                                                  | •   | •   |       |       |

| F <sub>MAX_TIMER</sub> | Maximum frequency of 16-bit timer in a UDB pair               |                                                  | -   | -   | 67.01 | MHz   |

| F <sub>MAX_ADDER</sub> | Maximum frequency of 16-bit adder in a UDB pair               |                                                  | -   | -   | 67.01 | MHz   |

| F <sub>MAX_CRC</sub>   | Maximum frequency of 16-bit<br>CRC/PRS in a UDB pair          |                                                  | -   | -   | 67.01 | MHz   |

| PLD Perform            | ance                                                          |                                                  |     |     |       |       |

| F <sub>MAX_PLD</sub>   | Maximum frequency of a two-pass<br>PLD function in a UDB pair |                                                  | -   | -   | 67.01 | MHz   |

| Clock to Outp          | but Performance                                               |                                                  |     |     |       |       |

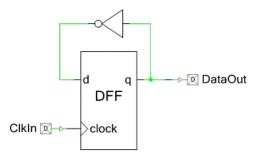

| t <sub>CLK_OUT</sub>   | Propagation delay for clock in to data out, see Figure 11-71. | 25 °C, $V_{DDD} \ge 2.7 V$                       | -   | 20  | 25    | ns    |

| t <sub>CLK_OUT</sub>   | Propagation delay for clock in to data out, see Figure 11-71. | Worst-case placement, routing, and pin selection | -   | -   | 55    | ns    |

#### Figure 11-71. Clock to Output Performance

## 11.7 Memory

Specifications are valid for –40 °C  $\leq$  T<sub>A</sub>  $\leq$  105 °C and T<sub>J</sub>  $\leq$  120 °C, except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted.

11.7.1 Flash

#### Table 11-57. Flash DC Specifications

| Parameter | Description               | Conditions           | Min  | Тур | Max | Units |

|-----------|---------------------------|----------------------|------|-----|-----|-------|

|           | Erase and program voltage | V <sub>DDD</sub> pin | 1.71 | _   | 5.5 | V     |

#### Table 11-58. Flash AC Specifications

| Parameter          | Description                                                                | Conditions                                                                                                                          | Min | Тур | Max | Units   |

|--------------------|----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|---------|

| T <sub>WRITE</sub> | Row write time (erase + program)                                           |                                                                                                                                     | -   | 15  | 20  | ms      |

| T <sub>ERASE</sub> | Row erase time                                                             |                                                                                                                                     | -   | 10  | 13  | ms      |

|                    | Row program time                                                           |                                                                                                                                     | -   | 5   | 7   | ms      |

| T <sub>BULK</sub>  | Bulk erase time (256 KB)                                                   |                                                                                                                                     | -   | _   | 140 | ms      |

|                    | Sector erase time (16 KB)                                                  |                                                                                                                                     | -   | _   | 15  | ms      |

| T <sub>PROG</sub>  | Total device programming time                                              | No overhead <sup>[71]</sup>                                                                                                         | -   | 5   | 7.5 | seconds |

|                    | Flash data retention time, retention period measured from last erase cycle | Average ambient temp. T <sub>A</sub> ≤55 °C,<br>100 K erase/program cycles                                                          | 20  | -   | -   | years   |

|                    |                                                                            | Average ambient temp. $T_A \le 85 \degree C$ , 10 K erase/program cycles                                                            | 10  | _   | _   |         |

|                    |                                                                            | Ambient temp. $T_A \le 105 \text{ °C}$ ,<br>10 K erase/program cycles,<br>$\le$ one year at $T_A \ge 75 \text{ °C}$ <sup>[72]</sup> | 10  | _   | _   |         |

#### 11.7.2 EEPROM

#### Table 11-59. EEPROM DC Specifications

| Parameter | Description               | Conditions | Min  | Тур | Max | Units |

|-----------|---------------------------|------------|------|-----|-----|-------|

|           | Erase and program voltage |            | 1.71 | -   | 5.5 | V     |

#### Table 11-60. EEPROM AC Specifications

| Parameter          | Description                                                                 | Conditions                                                                                                                 | Min | Тур | Max | Units |

|--------------------|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| T <sub>WRITE</sub> | Single row erase/write cycle time                                           |                                                                                                                            | -   | 10  | 20  | ms    |

|                    | EEPROM data retention time, retention period measured from last erase cycle | Average ambient temp, $T_A \le 25 \text{ °C}$ , 1M erase/program cycles                                                    | 20  | -   | -   | years |

|                    |                                                                             | Average ambient temp, T <sub>A</sub> ≤ 55 °C,<br>100 K erase/program cycles                                                | 20  | -   | _   |       |

|                    |                                                                             | Average ambient temp. T <sub>A</sub> ≤85 °C,<br>10 K erase/program cycles                                                  | 10  | -   | -   |       |

|                    |                                                                             | Ambient temp. T <sub>A</sub> ≤ 105 °C,<br>10K erase/program cycles,<br>≤ one year at T <sub>A</sub> ≥75 °C <sup>[72]</sup> | 10  | -   | -   |       |

Notes

<sup>71.</sup> See PSoC 5 Device Programming Specifications for a description of a low-overhead method of programming PSoC 5 flash.

72. Cypress provides a retention calculator to calculate the retention lifetime based on customers' individual temperature profiles for operation over the -40 °C to +105 °C ambient temperature range. Contact customercare@cypress.com.

## 11.9 Clocking

Specifications are valid for –40 °C  $\leq$  T<sub>A</sub>  $\leq$  105 °C and T<sub>J</sub>  $\leq$  120 °C, except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted. Unless otherwise specified, all charts and graphs show typical values.

11.9.1 Internal Main Oscillator

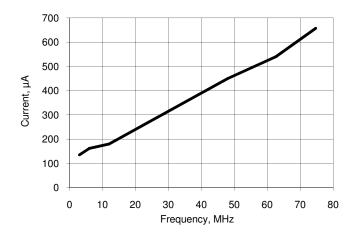

Table 11-75. IMO DC Specifications<sup>[86]</sup>

| Parameter | Description           | Conditions                         | Min | Тур | Max | Units |  |  |  |

|-----------|-----------------------|------------------------------------|-----|-----|-----|-------|--|--|--|

|           | Supply current        |                                    |     |     |     |       |  |  |  |

|           | 74.7 MHz              |                                    | _   | _   | 730 | μA    |  |  |  |

|           | 62.6 MHz              |                                    | -   | _   | 600 | μA    |  |  |  |

|           | 48 MHz                |                                    | -   | _   | 500 | μA    |  |  |  |

| lcc_imo   | 24 MHz – USB mode     | With oscillator locking to USB bus | -   | _   | 500 | μA    |  |  |  |

|           | 24 MHz – non USB mode |                                    | _   | _   | 300 | μA    |  |  |  |

|           | 12 MHz                |                                    | -   | _   | 200 | μA    |  |  |  |

|           | 6 MHz                 |                                    | -   | -   | 180 | μA    |  |  |  |

|           | 3 MHz                 |                                    | -   | -   | 150 | μA    |  |  |  |

#### Figure 11-76. IMO Current vs. Frequency

#### Table 11-76. IMO AC Specifications

| Parameter                        | Description                                                      | Conditions                                                                                                                              | Min   | Тур | Max  | Units |  |  |

|----------------------------------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-------|-----|------|-------|--|--|

|                                  | IMO frequency stability (with factory trim)                      |                                                                                                                                         |       |     |      |       |  |  |

|                                  | 74.7 MHz                                                         |                                                                                                                                         | -7    | -   | 7    | %     |  |  |

|                                  | 62.6 MHz                                                         |                                                                                                                                         | -7    | -   | 7    | %     |  |  |

|                                  | 48 MHz                                                           |                                                                                                                                         | -5    | _   | 5    | %     |  |  |

|                                  | 24 MHz – Non USB mode                                            |                                                                                                                                         | -4    | -   | 4    | %     |  |  |

|                                  | 24 MHz – USB mode                                                | With oscillator locking to USB bus                                                                                                      | -0.25 | -   | 0.25 | %     |  |  |

| F <sub>IMO</sub> <sup>[87]</sup> | 12 MHz                                                           |                                                                                                                                         | -3    | _   | 3    | %     |  |  |

| -                                | 6 MHz                                                            |                                                                                                                                         | -2    | -   | 2    | %     |  |  |

|                                  | 3 MHz                                                            | 0 °C to 70 °C                                                                                                                           | -1    | -   | 1    | %     |  |  |

|                                  |                                                                  | –40 °C to 105 °C                                                                                                                        | -1.5  | -   | 1.5  | %     |  |  |

|                                  | 3 MHz frequency stability after typical PCB assembly post-reflow | Typical (non-optimized) board<br>layout and 250 °C solder reflow.<br>Device may be calibrated after<br>assembly to improve performance. | _     | ±2% | _    | %     |  |  |

| Tstart_imo                       | Startup time <sup>[88]</sup>                                     | From enable (during normal system operation)                                                                                            | _     | -   | 13   | μs    |  |  |

|                                  | Jitter (peak to peak) <sup>[88]</sup>                            |                                                                                                                                         |       |     |      |       |  |  |

| Јр–р                             | F = 24 MHz                                                       |                                                                                                                                         | -     | 0.9 | -    | ns    |  |  |

|                                  | F = 3 MHz                                                        |                                                                                                                                         | _     | 1.6 | -    | ns    |  |  |

|                                  | Jitter (long term) <sup>[88]</sup>                               |                                                                                                                                         |       |     |      |       |  |  |

| Jperiod                          | F = 24 MHz                                                       |                                                                                                                                         | -     | 0.9 | -    | ns    |  |  |

|                                  | F = 3 MHz                                                        |                                                                                                                                         | _     | 12  | -    | ns    |  |  |

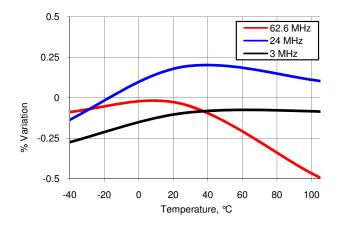

#### Figure 11-77. IMO Frequency Variation vs. Temperature

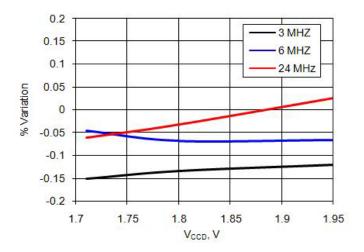

## Figure 11-78. IMO Frequency Variation vs. $V_{CC}$

Notes

87. FIMO is measured after packaging, and thus accounts for substrate and die attach stresses.

88. Based on device characterization (Not production tested).

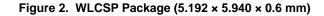

NOTES:

1. REFERENCE JEDEC Publication 95: Design Guide 4.18

2. ALL DIMENSIONS ARE IN MILLIMETERS

001-88034 \*B

## 14. Acronyms

#### Table 14-1. Acronyms Used in this Document

| Acronym          | Description                                                                                             |

|------------------|---------------------------------------------------------------------------------------------------------|

| abus             | analog local bus                                                                                        |

| ADC              | analog-to-digital converter                                                                             |

| AG               | analog global                                                                                           |

| АНВ              | AMBA (advanced microcontroller bus archi-<br>tecture) high-performance bus, an ARM data<br>transfer bus |

| ALU              | arithmetic logic unit                                                                                   |

| AMUXBUS          | analog multiplexer bus                                                                                  |

| API              | application programming interface                                                                       |

| APSR             | application program status register                                                                     |

| ARM <sup>®</sup> | advanced RISC machine, a CPU architecture                                                               |

| ATM              | automatic thump mode                                                                                    |

| BW               | bandwidth                                                                                               |

| CAN              | Controller Area Network, a communications protocol                                                      |

| CMRR             | common-mode rejection ratio                                                                             |

| CPU              | central processing unit                                                                                 |

| CRC              | cyclic redundancy check, an error-checking protocol                                                     |

| DAC              | digital-to-analog converter, see also IDAC, VDAC                                                        |

| DFB              | digital filter block                                                                                    |

| DIO              | digital input/output, GPIO with only digital capabilities, no analog. See GPIO.                         |

| DMA              | direct memory access, see also TD                                                                       |

| DNL              | differential nonlinearity, see also INL                                                                 |

| DNU              | do not use                                                                                              |

| DR               | port write data registers                                                                               |

| DSI              | digital system interconnect                                                                             |

| DWT              | data watchpoint and trace                                                                               |

| ECC              | error correcting code                                                                                   |

| ECO              | external crystal oscillator                                                                             |

| EEPROM           | electrically erasable programmable read-only memory                                                     |

| EMI              | electromagnetic interference                                                                            |

| EMIF             | external memory interface                                                                               |

| EOC              | end of conversion                                                                                       |

| EOF              | end of frame                                                                                            |

| EPSR             | execution program status register                                                                       |

| ESD              | electrostatic discharge                                                                                 |

| ETM              | embedded trace macrocell                                                                                |

## Table 14-1. Acronyms Used in this Document (continued)

| Acronym                  | Description                                            |  |  |  |

|--------------------------|--------------------------------------------------------|--|--|--|

| FIR                      | finite impulse response, see also IIR                  |  |  |  |

| FPB                      | flash patch and breakpoint                             |  |  |  |

| FS                       | full-speed                                             |  |  |  |

| GPIO                     | general-purpose input/output, applies to a PSoC pin    |  |  |  |

| HVI                      | high-voltage interrupt, see also LVI, LVD              |  |  |  |

| IC                       | integrated circuit                                     |  |  |  |

| IDAC                     | current DAC, see also DAC, VDAC                        |  |  |  |

| IDE                      | integrated development environment                     |  |  |  |

| I <sup>2</sup> C, or IIC | Inter-Integrated Circuit, a communications protocol    |  |  |  |

| lir                      | infinite impulse response, see also FIR                |  |  |  |

| ILO                      | internal low-speed oscillator, see also IMO            |  |  |  |

| IMO                      | internal main oscillator, see also ILO                 |  |  |  |

| INL                      | integral nonlinearity, see also DNL                    |  |  |  |

| I/O                      | input/output, see also GPIO, DIO, SIO, USBIO           |  |  |  |

| IPOR                     | initial power-on reset                                 |  |  |  |

| IPSR                     | interrupt program status register                      |  |  |  |

| IRQ                      | interrupt request                                      |  |  |  |

| ITM                      | instrumentation trace macrocell                        |  |  |  |

| LCD                      | liquid crystal display                                 |  |  |  |

| LIN                      | Local Interconnect Network, a communications protocol. |  |  |  |

| LR                       | link register                                          |  |  |  |

| LUT                      | lookup table                                           |  |  |  |

| LVD                      | low-voltage detect, see also LVI                       |  |  |  |

| LVI                      | low-voltage interrupt, see also HVI                    |  |  |  |

| LVTTL                    | low-voltage transistor-transistor logic                |  |  |  |

| MAC                      | multiply-accumulate                                    |  |  |  |

| MCU                      | microcontroller unit                                   |  |  |  |

| MISO                     | master-in slave-out                                    |  |  |  |

| NC                       | no connect                                             |  |  |  |

| NMI                      | nonmaskable interrupt                                  |  |  |  |

| NRZ                      | non-return-to-zero                                     |  |  |  |

| NVIC                     | nested vectored interrupt controller                   |  |  |  |

| NVL                      | nonvolatile latch, see also WOL                        |  |  |  |

| opamp                    | operational amplifier                                  |  |  |  |

| PAL                      | programmable array logic, see also PLD                 |  |  |  |

| PC                       | program counter                                        |  |  |  |

| РСВ                      | printed circuit board                                  |  |  |  |

| PGA                      | programmable gain amplifier                            |  |  |  |

# **Document History Page**

| Revision | ECN     | Orig. of<br>Change | Submission<br>Date | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------|---------|--------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| **       | 3825653 | MKEA               | 12/07/2012         | Datasheet for new CY8C56LP family.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| *A       | 3897878 | MKEA               | 02/07/2013         | Removed Preliminary status.<br>Updated characterization footnotes in Electrical Specifications.<br>Changed number of opamps in Ordering Information<br>Updated conditions for SAR ADC INL and DNL specifications in Table 11-24<br>Updated Table 11-78 (ILO AC Specifications).<br>Changed "UDB Configuration" to "UDB Working Registers" in Table 5-5.<br>Removed references to CAN.<br>Updated VIDAC INL spec.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| *B       | 3902085 | MKEA               | 02/12/2013         | Changed Hibernate wakeup time from 125 µs to 200 µs in Table 6-3 and Table 11-3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| *C       | 3917994 | MKEA               | 01/08/2013         | Added Controller Area Network (CAN) content.<br>Added CY8C5667AXI-LP040, CY8C5668AXI-LP034, and<br>CY8C5667LTI-LP041 parts in Ordering Information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| *D       | 4114902 | MKEA               | 09/30/2013         | Added information about 1 KB cache in Features.<br>Added warning on reset devices in the EEPROM section.<br>Added DBGEN field in Table 5-3.<br>Deleted statement about repeat start from the I <sup>2</sup> C section.<br>Removed T <sub>STG</sub> spec from Table 11-1 and added a note clarifying the maximum<br>storage temperature range.<br>Updated chip Idd, regulator, opamp, delta-sigma ADC, SAR ADC, IDAC, and<br>VDAC graphs.<br>Added min and max values for the Regulator Output Capacitor parameter.<br>Updated C <sub>IN</sub> specs in GPIO DC Specifications and SIO DC Specifications.<br>Updated rise and fall time specs in Fast Strong mode in Table 11-9, and deleted<br>related graphs.<br>Added I <sub>IB</sub> parameter in Opamp DC Specifications<br>Updated Vos spec conditions and changed TCVos max value from 0.55 to 1 in<br>Table 11-20.<br>Updated Voltage Reference Specifications and IMO AC Specifications.<br>Updated T <sub>IMO</sub> spec (3 MHz).<br>Updated 100-TQFP package diagram.<br>Added Appendix for CSP package (preliminary). |