Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                      |

| Core Processor             | ARM® Cortex®-M3                                                               |

| Core Size                  | 32-Bit Single-Core                                                            |

| Speed                      | 80MHz                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                        |

| Peripherals                | CapSense, DMA, LCD, POR, PWM, WDT                                             |

| Number of I/O              | 62                                                                            |

| Program Memory Size        | 256KB (256K x 8)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 2K x 8                                                                        |

| RAM Size                   | 64K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 5.5V                                                                  |

| Data Converters            | A/D 2x12b; D/A 4x8b                                                           |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 99-UFBGA, WLCSP                                                               |

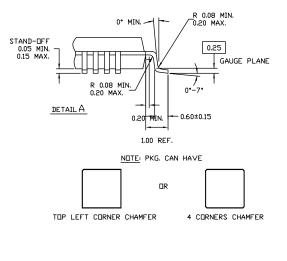

| Supplier Device Package    | 99-WLCSP (5.19x5.94)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c5688fni-lp211t |

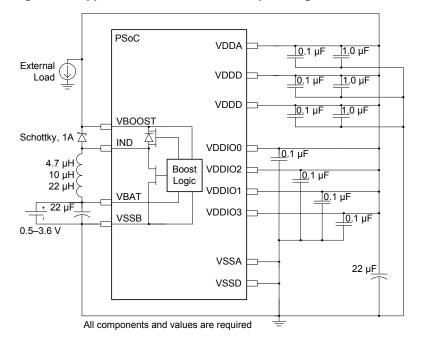

Figure 6-6. Application of Boost Converter powering PSoC device

The boost converter may also generate a supply that is not used directly by the PSoC device. An example of this use case is boosting a 1.8 V supply to 4.0 V to drive a white LED. If the boost converter is not supplying the PSoC devices  $V_{DDA},\ V_{DDD},$  and  $V_{DDIO}$  it must comply with the same design rules as supplying

the PSoC device, but with a change to the bulk capacitor requirements. A parallel arrangement 22  $\mu F$ , 1.0  $\mu F$ , and 0.1  $\mu F$  capacitors are all required on the Vout supply and must be placed within 1 cm of the VBOOST pin to ensure regulator stability.

Figure 6-7. Application of Boost Converter not powering PSoC device

The switching frequency is set to 400 kHz using an oscillator integrated into the boost converter. The boost converter can be operated in two different modes: active and standby. Active

mode is the normal mode of operation where the boost regulator actively generates a regulated output voltage. In standby mode, most boost functions are disabled, thus reducing power

**Note** IPOR disables the watchdog function. The program must enable the watchdog function at an appropriate point in the code by setting a register bit. When this bit is set, it cannot be cleared again except by an IPOR power on reset event.

# 6.4 I/O System and Routing

PSoC I/Os are extremely flexible. Every GPIO has analog and digital I/O capability. All I/Os have a large number of drive modes, which are set at POR. PSoC also provides up to four individual I/O voltage domains through the VDDIO pins.

There are two types of I/O pins on every device; those with USB provide a third type. Both General Purpose I/O (GPIO) and Special I/O (SIO) provide similar digital functionality. The primary differences are their analog capability and drive strength. Devices that include USB also provide two USBIO pins that support specific USB functionality as well as limited GPIO capability.

All I/O pins are available for use as digital inputs and outputs for both the CPU and digital peripherals. In addition, all I/O pins can generate an interrupt. The flexible and advanced capabilities of the PSoC I/O, combined with any signal to any pin routability, greatly simplify circuit design and board layout. All GPIO pins can be used for analog input, CapSense<sup>[9]</sup>, and LCD segment drive, while SIO pins are used for voltages in excess of VDDA and for programmable output voltages.

- Features supported by both GPIO and SIO:

- □ User programmable port reset state

- □ Separate I/O supplies and voltages for up to four groups of I/O

- □ Digital peripherals use DSI to connect the pins

- □ Input or output or both for CPU and DMA

- Eight drive modes

- Every pin can be an interrupt source configured as rising edge, falling edge or both edges. If required, level sensitive interrupts are supported through the DSI

- Dedicated port interrupt vector for each port

- Slew rate controlled digital output drive mode

- Access port control and configuration registers on either port basis or pin basis

- Separate port read (PS) and write (DR) data registers to avoid read modify write errors

- Special functionality on a pin by pin basis

- Additional features only provided on the GPIO pins:

- □ LCD segment drive on LCD equipped devices

- □ CapSense<sup>[9]</sup>

- Analog input and output capability

- □ Continuous 100 µA clamp current capability

- Standard drive strength down to 1.71 V

- Additional features only provided on SIO pins:

- □ Higher drive strength than GPIO

- Hot swap capability (5 V tolerance at any operating VDD)

- Programmable and regulated high input and output drive levels down to 1.2 V

- No analog input, CapSense, or LCD capability

- Overvoltage tolerance up to 5.5 V

- □ SIO can act as a general purpose analog comparator

- USBIO features:

- □ Full speed USB 2.0 compliant I/O

- □ Highest drive strength for general purpose use

- □ Input, output, or both for CPU and DMA

- Input, output, or both for digital peripherals

- □ Digital output (CMOS) drive mode

- □ Each pin can be an interrupt source configured as rising edge, falling edge, or both edges

## Note

9. GPIOs with opamp outputs are not recommended for use with CapSense.

The USBIO pins (P15[7] and P15[6]), when enabled for I/O mode, have limited drive mode control. The drive mode is set using the PRT15.DM0[7, 6] register. A resistive pull option is also available at the USBIO pins, which can be enabled using the PRT15.DM1[7, 6] register. When enabled for USB mode, the drive mode control has no impact on the configuration of the USB pins. Unlike the GPIO and SIO configurations, the port wide configuration registers do not configure the USB drive mode bits. Table 6-7 shows the drive mode configuration for the USBIO pins.

Table 6-7. USBIO Drive Modes (P15[7] and P15[6])

| PRT15.DM1[7,6]<br>Pull up enable | PRT15.DM0[7,6]<br>Drive Mode enable | PRT15.DR[7,6] = 1 | PRT15.DR[7,6] = 0 | Description                   |

|----------------------------------|-------------------------------------|-------------------|-------------------|-------------------------------|

| 0                                | 0                                   | High Z            | Strong Low        | Open Drain, Strong Low        |

| 0                                | 1                                   | Strong High       | Strong Low        | Strong Outputs                |

| 1                                | 0                                   | Res High (5k)     | Strong Low        | Resistive Pull Up, Strong Low |

| 1                                | 1                                   | Strong High       | Strong Low        | Strong Outputs                |

# ■ High impedance analog

The default reset state with both the output driver and digital input buffer turned off. This prevents any current from flowing in the I/O's digital input buffer due to a floating voltage. This state is recommended for pins that are floating or that support an analog voltage. High impedance analog pins do not provide digital input functionality.

To achieve the lowest chip current in sleep modes, all I/Os must either be configured to the high impedance analog mode, or have their pins driven to a power supply rail by the PSoC device or by external circuitry.

## ■ High impedance digital

The input buffer is enabled for digital signal input. This is the standard high impedance (HiZ) state recommended for digital inputs.

## ■ Resistive pull up or resistive pull down

Resistive pull up or pull down, respectively, provides a series resistance in one of the data states and strong drive in the other. Pins can be used for digital input and output in these modes. Interfacing to mechanical switches is a common application for these modes. Resistive pull up and pull down are not available with SIO in regulated output mode.

Open drain, drives high and open drain, drives low Open drain modes provide high impedance in one of the data states and strong drive in the other. Pins can be used for digital input and output in these modes. A common application for these modes is driving the I<sup>2</sup>C bus signal lines.

## Strong drive

Provides a strong CMOS output drive in either high or low state. This is the standard output mode for pins. Strong Drive mode pins must not be used as inputs under normal circumstances. This mode is often used to drive digital output signals or external FETs.

## ■ Resistive pull up and pull down

Similar to the resistive pull up and resistive pull down modes except the pin is always in series with a resistor. The high data state is pull up while the low data state is pull down. This mode is most often used when other signals that may cause shorts can drive the bus. Resistive pull up and pull down are not available with SIO in regulated output mode.

## 6.4.2 Pin Registers

Registers to configure and interact with pins come in two forms that may be used interchangeably.

All I/O registers are available in the standard port form, where each bit of the register corresponds to one of the port pins. This register form is efficient for quickly reconfiguring multiple port pins at the same time.

I/O registers are also available in pin form, which combines the eight most commonly used port register bits into a single register for each pin. This enables very fast configuration changes to individual pins with a single register write.

## 6.4.3 Bidirectional Mode

High speed bidirectional capability allows pins to provide both the high impedance digital drive mode for input signals and a second user selected drive mode such as strong drive (set using PRTxDM[2:0] registers) for output signals on the same pin, based on the state of an auxiliary control bus signal. The bidirectional capability is useful for processor busses and communications interfaces such as the SPI Slave MISO pin that requires dynamic hardware control of the output buffer.

The auxiliary control bus routes up to 16 UDB or digital peripheral generated output enable signals to one or more pins.

## 6.4.4 Slew Rate Limited Mode

GPIO and SIO pins have fast and slow output slew rate options for strong and open drain drive modes, not resistive drive modes. Because it results in reduced EMI, the slow edge rate option is recommended for signals that are not speed critical, generally less than 1 MHz. The fast slew rate is for signals between 1 MHz and 33 MHz. The slew rate is individually configurable for each pin, and is set by the PRTxSLW registers.

# 6.4.5 Pin Interrupts

All GPIO and SIO pins are able to generate interrupts to the system. All eight pins in each port interface to their own Port Interrupt Control Unit (PICU) and associated interrupt vector. Each pin of the port is independently configurable to detect rising edge, falling edge, both edge interrupts, or to not generate an interrupt.

Depending on the configured mode for each pin, each time an interrupt event occurs on a pin, its corresponding status bit of the interrupt status register is set to "1" and an interrupt request is sent to the interrupt controller. Each PICU has its own interrupt

Document Number: 001-84935 Rev. \*L Page 36 of 131

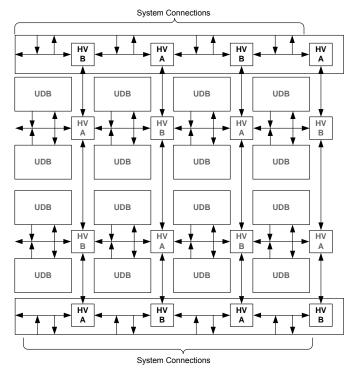

# 7.3 UDB Array Description

Figure 7-7 shows an example of a 16 UDB array. In addition to the array core, there are a DSI routing interfaces at the top and bottom of the array. Other interfaces that are not explicitly shown include the system interfaces for bus and clock distribution. The UDB array includes multiple horizontal and vertical routing channels each comprised of 96 wires. The wire connections to UDBs, at horizontal/vertical intersection and at the DSI interface are highly permutable providing efficient automatic routing in PSoC Creator. Additionally the routing allows wire by wire segmentation along the vertical and horizontal routing to further increase routing flexibility and capability.

Figure 7-7. Digital System Interface Structure

# 7.3.1 UDB Array Programmable Resources

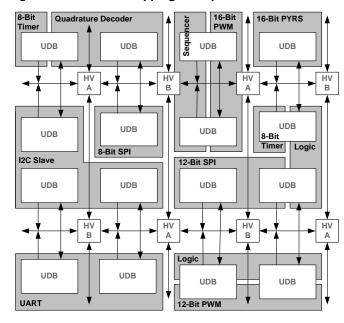

Figure 7-8 shows an example of how functions are mapped into a bank of 16 UDBs. The primary programmable resources of the UDB are two PLDs, one datapath and one status/control register. These resources are allocated independently, because they have independently selectable clocks, and therefore unused blocks are allocated to other unrelated functions.

An example of this is the 8-bit Timer in the upper left corner of the array. This function only requires one datapath in the UDB, and therefore the PLD resources may be allocated to another function. A function such as a Quadrature Decoder may require more PLD logic than one UDB can supply and in this case can

utilize the unused PLD blocks in the 8-bit Timer UDB. Programmable resources in the UDB array are generally homogeneous so functions can be mapped to arbitrary boundaries in the array.

Figure 7-8. Function Mapping Example in a Bank of UDBs

# 7.4 DSI Routing Interface Description

The DSI routing interface is a continuation of the horizontal and vertical routing channels at the top and bottom of the UDB array core. It provides general purpose programmable routing between device peripherals, including UDBs, I/Os, analog peripherals, interrupts, DMA and fixed function peripherals.

Figure 7-9 illustrates the concept of the digital system interconnect, which connects the UDB array routing matrix with other device peripherals. Any digital core or fixed function peripheral that needs programmable routing is connected to this interface.

Signals in this category include:

- Interrupt requests from all digital peripherals in the system.

- DMA requests from all digital peripherals in the system.

- Digital peripheral data signals that need flexible routing to I/Os.

- Digital peripheral data signals that need connections to UDBs.

- Connections to the interrupt and DMA controllers.

- Connection to I/O pins.

- Connection to analog system digital signals.

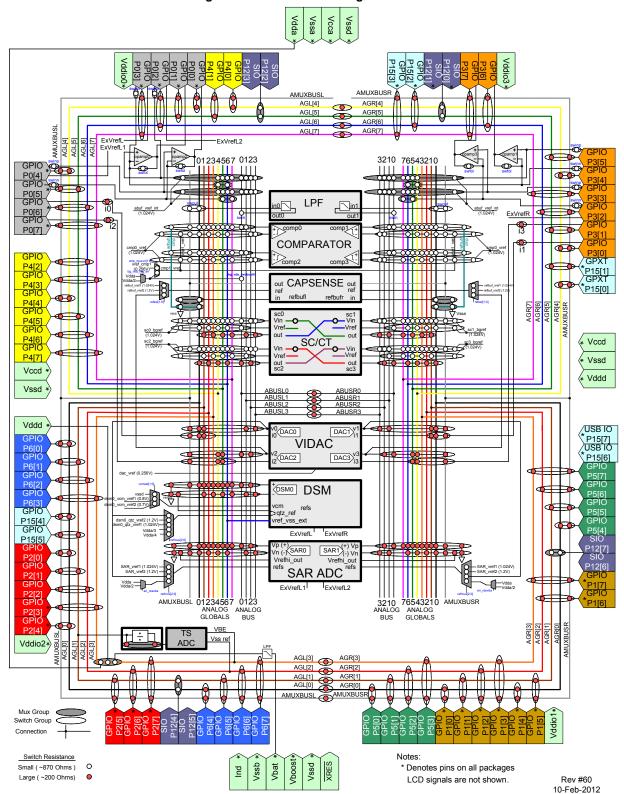

Figure 8-2. CY8C56LP Analog Interconnect

To preserve detail of this image, this image is best viewed with a PDF display program or printed on 11" × 17" paper.

## 8.2.3 Start of Conversion Input

The SoC signal is used to start an ADC conversion. A digital clock or UDB output can be used to drive this input. It can be used when the sampling period must be longer than the ADC conversion time or when the ADC must be synchronized to other hardware. This signal is optional and does not need to be connected if ADC is running in a continuous mode.

## 8.2.4 End of Conversion Output

The EoC signal goes high at the end of each ADC conversion. This signal may be used to trigger either an interrupt or DMA request.

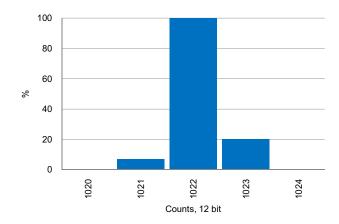

# 8.3 Successive Approximation ADCs

The CY8C56LP family of devices has one or two Successive Approximation (SAR) ADCs, depending on device selected. These ADCs are 12-bit at up to 1 Msps, with single-ended or differential inputs, making them useful for a wide variety of sampling and control applications.

## 8.3.1 Functional Description

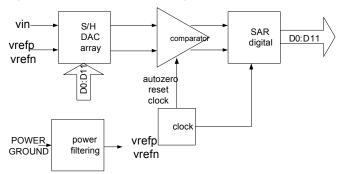

In a SAR ADC an analog input signal is sampled and compared with the output of a DAC. A binary search algorithm is applied to the DAC and used to determine the output bits in succession from MSB to LSB. A block diagram of one SAR ADC is shown in Figure 8-5.

Figure 8-5. SAR ADC Block Diagram

The input is connected to the analog globals and muxes. The frequency of the clock is 18 times the sample rate; the clock rate ranges from 1 to 18 MHz.

## 8.3.2 Conversion Signals

Writing a start bit or assertion of a Start of Frame (SOF) signal is used to start a conversion. SOF can be used in applications where the sampling period is longer than the conversion time, or when the ADC needs to be synchronized to other hardware. This signal is optional and does not need to be connected if the SAR ADC is running in a continuous mode. A digital clock or UDB output can be used to drive this input. When the SAR is first powered up or awakened from any of the sleeping modes, there is a power up wait time of 10 µs before it is ready to start the first conversion.

When the conversion is complete, a status bit is set and the output signal End of Frame (EOF) asserts and remains asserted until the value is read by either the DMA controller or the CPU. The EOF signal may be used to trigger an interrupt or a DMA request.

# 8.3.3 Operational Modes

A ONE\_SHOT control bit is used to set the SAR ADC conversion mode to either continuous or one conversion per SOF signal. DMA transfer of continuous samples, without CPU intervention, is supported.

## 8.4 Comparators

The CY8C56LP family of devices contains four comparators. Comparators have these features:

- Input offset factory trimmed to less than 5 mV

- Rail-to-rail common mode input range (V<sub>SSA</sub> to V<sub>DDA</sub>)

- Speed and power can be traded off by using one of three modes: fast, slow, or ultra low power

- Comparator outputs can be routed to look up tables to perform simple logic functions and then can also be routed to digital blocks

- The positive input of the comparators may be optionally passed through a low pass filter. Two filters are provided

- Comparator inputs can be connections to GPIO, DAC outputs and SC block outputs

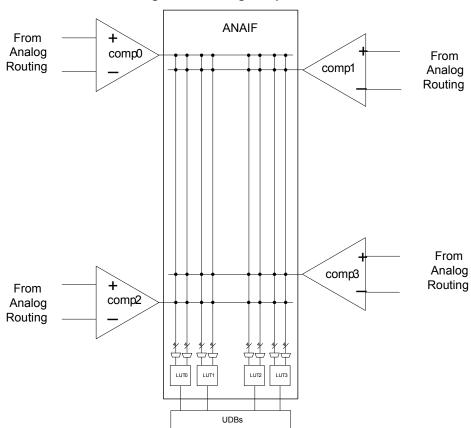

# 8.4.1 Input and Output Interface

The positive and negative inputs to the comparators come from the analog global buses, the analog mux line, the analog local bus and precision reference through multiplexers. The output from each comparator could be routed to any of the two input LUTs. The output of that LUT is routed to the UDB Digital System Interface.

Figure 8-6. Analog Comparator

# 8.4.2 LUT

The CY8C56LP family of devices contains four LUTs. The LUT is a two input, one output lookup table that is driven by any one or two of the comparators in the chip. The output of any LUT is routed to the digital system interface of the UDB array. From the digital system interface of the UDB array, these signals can be connected to UDBs, DMA controller, I/O, or the interrupt controller.

The LUT control word written to a register sets the logic function on the output. The available LUT functions and the associated control word is shown in Table 8-2.

Table 8-2. LUT Function vs. Program Word and Inputs

| Control Word | Output (A and B are LUT inputs) |

|--------------|---------------------------------|

| 0000b        | FALSE ('0')                     |

| 0001b        | A AND B                         |

| 0010b        | A AND (NOT B)                   |

| 0011b        | Α                               |

| 0100b        | (NOT <b>A</b> ) AND <b>B</b>    |

| 0101b        | В                               |

| 0110b        | A XOR B                         |

| 0111b        | A OR B                          |

| 1000b        | A NOR B                         |

| 1001b        | A XNOR B                        |

| 1010b        | NOT <b>B</b>                    |

| 1011b        | A OR (NOT B)                    |

| 1100b        | NOT A                           |

| 1101b        | (NOT A) OR B                    |

| 1110b        | A NAND B                        |

| 1111b        | TRUE ('1')                      |

Document Number: 001-84935 Rev. \*L Page 56 of 131

# 9.1 JTAG Interface

The IEEE 1149.1 compliant JTAG interface exists on four or five pins (the nTRST pin is optional). The JTAG clock frequency can be up to 12 MHz, or 1/3 of the CPU clock frequency for 8 and 16-bit transfers, or 1/5 of the CPU clock frequency for 32-bit

transfers, whichever is least. By default, the JTAG pins are enabled on new devices but the JTAG interface can be disabled, allowing these pins to be used as General Purpose I/O (GPIO) instead. The JTAG interface is used for programming the flash memory, debugging, I/O scan chains, and JTAG device chaining.

$V_{\text{DD}}$ Host Programmer PSoC 5  $V_{\text{DDD}}\text{, }V_{\text{DDA}}\text{, }V_{\text{DDIO0}}\text{, }V_{\text{DDIO1}}\text{, }V_{\text{DDIO2}}\text{, }V_{\text{DDIO3}}\text{ }^{1\text{, }2\text{, }3\text{, }4}$  $V_{DD}$ **TCK** TCK (P1[1] TMS (P1[0]) 5 TMS TDO TDI (P1[4]) TDI TDO (P1[3]) nTRST (P1[5]) 6 nTRST 6 **XRFS** XRES 4 GND VSSD, VSSA **GND**

Figure 9-1. JTAG Interface Connections between PSoC 5LP and Programmer

<sup>&</sup>lt;sup>1</sup> The voltage levels of Host Programmer and the PSoC 5 voltage domains involved in Programming should be same. The Port 1 JTAG pins and XRES pin are powered by V<sub>DDIO1</sub>. So, V<sub>DDIO1</sub> of PSoC 5 should be at same voltage level as host V<sub>DD</sub>. Rest of PSoC 5 voltage domains (V<sub>DDD</sub>, V<sub>DDA</sub>, V<sub>DDIO2</sub>, V<sub>DDIO2</sub>, V<sub>DDIO3</sub>) need not be at the same voltage level as host Programmer.

<sup>&</sup>lt;sup>2</sup> Vdda must be greater than or equal to all other power supplies (Vddd, Vddio's) in PSoC 5.

<sup>&</sup>lt;sup>3</sup> For Power cycle mode Programming, XRES pin is not required. But the Host programmer must have the capability to toggle power (Vddd, Vdda, All Vddio's) to PSoC 5. This may typically require external interface circuitry to toggle power which will depend on the programming setup. The power supplies can be brought up in any sequence, however, once stable, VDDA must be greater than or equal to all other supplies.

<sup>&</sup>lt;sup>4</sup> For JTAG Programming, Device reset can also be done without connecting to the XRES pin or Power cycle mode by using the TMS,TCK,TDI, TDO pins of PSoC 5, and writing to a specific register. But this requires that the DPS setting in NVL is not equal to "Debug Ports Disabled".

<sup>&</sup>lt;sup>5</sup> By default, PSoC 5 is configured for 4-wire JTAG mode unless user changes the DPS setting. So the TMS pin is unidirectional. But if the DPS setting is changed to non-JTAG mode, the TMS pin in JTAG is bi-directional as the SWD Protocol has to be used for acquiring the PSoC 5 device initially. After switching from SWD to JTAG mode, the TMS pin will be uni-directional. In such a case, unidirectional buffer should not be used on TMS line.

<sup>&</sup>lt;sup>6</sup> nTRST JTAG pin (P1[5]) cannot be used to reset the JTAG TAP controlller during first time programming of PSoC 5 as the default setting is 4-wire JTAG (nTRST disabled). Use the TMS, TCK pins to do a reset of JTAG TAP controller.

# Table 11-2. DC Specifications (continued)

| Parameter                            | Description                                                                                          | Conditions                                            |          | Min | Тур  | Max | Units |

|--------------------------------------|------------------------------------------------------------------------------------------------------|-------------------------------------------------------|----------|-----|------|-----|-------|

| I <sub>DD</sub> <sup>[26]</sup>      | Hibernate Mode                                                                                       |                                                       |          |     |      |     |       |

|                                      |                                                                                                      | $V_{DD} = V_{DDIO} = T = 4.5-5.5 V$                   | = -40 °C | 1   | 0.2  | 2   | μA    |

|                                      |                                                                                                      | 4.5–5.5 V T =                                         | = 25 °C  | -   | 0.24 | 2   |       |

|                                      |                                                                                                      | T =                                                   | = 85 °C  | -   | 2.6  | 15  |       |

|                                      |                                                                                                      | T =                                                   | = 105 °C | -   | 2.6  | 15  |       |

|                                      | Hibernate mode current All regulators and oscillators off.                                           | $V_{DD} = V_{DDIO} = T = 2.7-3.6 V$                   | = -40 °C | -   | 0.11 | 2   |       |

|                                      | SRAM retention                                                                                       | 2.7–3.6 V T =                                         | = 25 °C  | -   | 0.3  | 2   |       |

|                                      | GPIO interrupts are active                                                                           | T =                                                   | = 85 °C  | 1   | 2    | 15  |       |

|                                      | Boost = OFF<br>SIO pins in single ended input, unregulated output mode                               | T =                                                   | = 105 °C | -   | 2    | 15  |       |

|                                      |                                                                                                      | V <sub>DD</sub> = V <sub>DDIO</sub> = T = 1.71–1.95 V | = -40 °C | -   | 0.9  | 2   |       |

|                                      |                                                                                                      | 1.71–1.95 V T =                                       | = 25 °C  | 1   | 0.11 | 2   |       |

|                                      |                                                                                                      | T =                                                   | = 85 °C  | -   | 1.8  | 15  |       |

|                                      |                                                                                                      | T =                                                   | = 105 °C | -   | 1.8  | 15  |       |

| I <sub>DDAR</sub> <sup>[27]</sup>    | Analog current consumption while device is reset                                                     | $V_{DDA} \le 3.6 \text{ V}$                           |          | -   | 0.3  | 0.6 | mA    |

|                                      |                                                                                                      | V <sub>DDA</sub> > 3.6 V                              |          | -   | 1.4  | 3.3 | mA    |

| I <sub>DDDR</sub> <sup>[27]</sup>    | Digital current consumption while device is reset                                                    | $V_{DDD} \le 3.6 \text{ V}$                           |          | -   | 1.1  | 3.1 | mA    |

|                                      |                                                                                                      | V <sub>DDD</sub> > 3.6 V                              |          | -   | 0.7  | 3.1 | mA    |

| I <sub>DD_PROG</sub> <sup>[25]</sup> | Current consumption while device programming. Sum of digital, analog, and IOs: IDDD + IDDA + IDDIOX. |                                                       |          | -   | 15   | 21  | mA    |

Document Number: 001-84935 Rev. \*L Page 69 of 131

Notes

26. The current consumption of additional peripherals that are implemented only in programmed logic blocks can be found in their respective datasheets, available in PSoC Creator, the integrated design environment. To estimate total current, find CPU current at frequency of interest and add peripheral currents for your particular system from the device datasheet and component datasheets.

<sup>27.</sup> Based on device characterization (Not production tested).

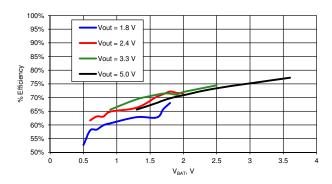

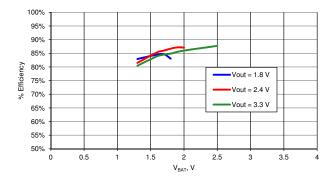

Figure 11-11. Efficiency vs  $V_{BAT}$ ,  $L_{BOOST}$  = 4.7  $\mu H^{[33]}$

Figure 11-13. Efficiency vs  $V_{BAT}$ ,  $L_{BOOST}$  = 22  $\mu H^{[33]}$

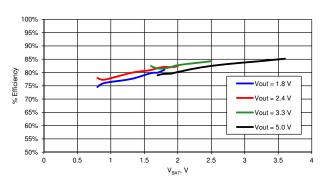

Figure 11-12. Efficiency vs  $V_{BAT}$ ,  $L_{BOOST}$  = 10  $\mu H^{[33]}$

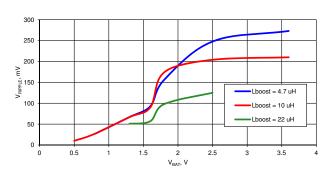

Figure 11-14.  $V_{RIPPLE}$  vs  $V_{BAT}$  [33]

## Note

<sup>33.</sup> Typical example. Actual values may vary depending on external component selection, PCB layout, and other design parameters.

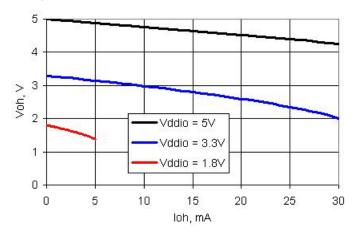

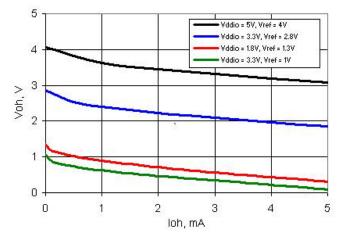

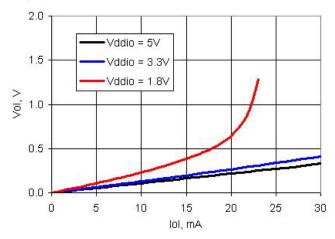

Figure 11-17. SIO Output High Voltage and Current, Unregulated Mode

Figure 11-19. SIO Output High Voltage and Current, Regulated Mode

Figure 11-18. SIO Output Low Voltage and Current, Unregulated Mode

Table 11-12. SIO Comparator Specifications [40]

| Parameter | Description                    | Conditions                | Min | Тур | Max | Units |

|-----------|--------------------------------|---------------------------|-----|-----|-----|-------|

| Vos       | Offset voltage                 | V <sub>DDIO</sub> = 2 V   | -   | _   | 68  | mV    |

|           |                                | V <sub>DDIO</sub> = 2.7 V | _   | _   | 72  |       |

|           |                                | V <sub>DDIO</sub> = 5.5 V | _   | _   | 82  |       |

| TCVos     | Offset voltage drift with temp |                           | _   | _   | 250 | μV/°C |

| CMRR      | Common mode rejection ratio    | V <sub>DDIO</sub> = 2 V   | 30  | _   | _   | dB    |

|           |                                | V <sub>DDIO</sub> = 2.7 V | 35  | _   | _   |       |

|           |                                | V <sub>DDIO</sub> = 5.5 V | 40  | _   | _   |       |

| Tresp     | Response time                  |                           | _   | _   | 30  | ns    |

# 11.4.3 USBIO

For operation in GPIO mode, the standard range for  $V_{DDD}$  applies, see Device Level Specifications on page 67.

Table 11-13. USBIO DC Specifications

| Parameter       | Description                                    | Conditions                                                      | Min            | Тур | Max            | Units |

|-----------------|------------------------------------------------|-----------------------------------------------------------------|----------------|-----|----------------|-------|

| Rusbi           | USB D+ pull-up resistance <sup>[40]</sup>      | With idle bus                                                   | 0.900          | _   | 1.575          | kΩ    |

| Rusba           | USB D+ pull-up resistance <sup>[40]</sup>      | While receiving traffic                                         | 1.425          | _   | 3.090          | kΩ    |

| Vohusb          | Static output high <sup>[40]</sup>             | 15 k $\Omega$ ±5% to V <sub>SS</sub> , internal pull-up enabled | 2.8            | _   | 3.6            | V     |

| Volusb          | Static output low <sup>[40]</sup>              | 15 k $\Omega$ ±5% to V <sub>SS</sub> , internal pull-up enabled | -              | _   | 0.3            | V     |

| Vihgpio         | Input voltage high, GPIO mode <sup>[40]</sup>  | V <sub>DDD</sub> = 1.8 V                                        | 1.5            | _   | _              | V     |

|                 |                                                | V <sub>DDD</sub> = 3.3 V                                        | 2              | _   | -              | V     |

|                 |                                                | V <sub>DDD</sub> = 5.0 V                                        | 2              | _   | _              | V     |

| Vilgpio         | Input voltage low, GPIO mode <sup>[40]</sup>   | V <sub>DDD</sub> = 1.8 V                                        | -              | _   | 0.8            | V     |

|                 |                                                | V <sub>DDD</sub> = 3.3 V                                        | -              | _   | 0.8            | V     |

|                 |                                                | V <sub>DDD</sub> = 5.0 V                                        | -              | _   | 0.8            | V     |

| Vohgpio         | Output voltage high, GPIO mode <sup>[40]</sup> | I <sub>OH</sub> = 4 mA, V <sub>DDD</sub> = 1.8 V                | 1.6            | _   | -              | V     |

|                 |                                                | I <sub>OH</sub> = 4 mA, V <sub>DDD</sub> = 3.3 V                | 3.1            | _   | _              | V     |

|                 |                                                | I <sub>OH</sub> = 4 mA, V <sub>DDD</sub> = 5.0 V                | 4.2            | _   | _              | V     |

| Volgpio         | Output voltage low, GPIO mode <sup>[40]</sup>  | I <sub>OL</sub> = 4 mA, V <sub>DDD</sub> = 1.8 V                | _              | _   | 0.3            | V     |

|                 |                                                | I <sub>OL</sub> = 4 mA, V <sub>DDD</sub> = 3.3 V                | _              | _   | 0.3            | V     |

|                 |                                                | I <sub>OL</sub> = 4 mA, V <sub>DDD</sub> = 5.0 V                | _              | _   | 0.3            | V     |

| $V_{DI}$        | Differential input sensitivity                 | (D+)-(D-)                                                       | _              | _   | 0.2            | V     |

| Vcm             | Differential input common mode range           |                                                                 | 8.0            | _   | 2.5            | V     |

| Vse             | Single ended receiver threshold                |                                                                 | 0.8            | _   | 2              | V     |

| Rps2            | PS/2 pull-up resistance <sup>[40]</sup>        | In PS/2 mode, with PS/2 pull-up enabled                         | 3              | _   | 7              | kΩ    |

| Rext            | External USB series resistor [40]              | In series with each USB pin                                     | 21.78<br>(–1%) | 22  | 22.22<br>(+1%) | Ω     |

| Zo              | USB driver output impedance <sup>[40]</sup>    | Including Rext                                                  | 28             | _   | 44             | Ω     |

| C <sub>IN</sub> | USB transceiver input capacitance              |                                                                 | _              | _   | 20             | pF    |

| I <sub>IL</sub> | Input leakage current (absolute value)[40]     | 25 °C, V <sub>DDD</sub> = 3.0 V                                 | _              | _   | 2              | nA    |

## Note

<sup>40.</sup> Based on device characterization (Not production tested).

# 11.5.2 Delta-Sigma ADC

Unless otherwise specified, operating conditions are:

- Operation in continuous sample mode

- fclk = 6.144 MHz

- Reference = 1.024 V internal reference bypassed on P3.2 or P0.3

- Unless otherwise specified, all charts and graphs show typical values

Table 11-20. 12-bit Delta-sigma ADC DC Specifications

| Parameter          | arameter Description Conditions                                                                   |                                                               | Min              | Тур                    | Max                  | Units      |

|--------------------|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------|------------------|------------------------|----------------------|------------|

|                    | Resolution                                                                                        |                                                               | 8                | _                      | 12                   | bits       |

|                    | Number of channels, single ended                                                                  |                                                               | _                | _                      | No. of<br>GPIO       | _          |

|                    | Number of channels, differential                                                                  | Differential pair is formed using a pair of GPIOs.            | _                | _                      | No. of<br>GPIO/2     | -          |

|                    | Monotonic                                                                                         | Yes                                                           | _                | _                      | -                    | _          |

| Ge                 | Gain error                                                                                        | Buffered, buffer gain = 1,<br>Range = ±1.024 V, 25 °C         | -                | _                      | ±0.4                 | %          |

| Gd                 | Gain drift                                                                                        | Buffered, buffer gain = 1,<br>Range = ±1.024 V                | -                | _                      | 50                   | ppm/°<br>C |

| Vos                | Input offset voltage                                                                              | Buffered, 16-bit mode, full voltage range                     | -                | _                      | ±0.2                 | mV         |

| VOS                | Imput onset voltage                                                                               | Buffered, 16-bit mode,<br>V <sub>DDA</sub> = 1.8 V ±5%, 25 °C | -                | _                      | ±0.1                 | mV         |

| TCVos              | Temperature coefficient, input offset voltage                                                     | Buffer gain = 1, 12-bit,<br>Range = ±1.024 V                  | -                | _                      | 1                    | μV/°C      |

|                    | Input voltage range, single ended <sup>[41]</sup>                                                 |                                                               | $V_{SSA}$        | -                      | $V_{DDA}$            | V          |

|                    | Input voltage range, differential unbuffered <sup>[41]</sup>                                      |                                                               | V <sub>SSA</sub> | _                      | $V_{DDA}$            | V          |

|                    | Input voltage range, differential, buffered <sup>[41]</sup>                                       |                                                               | V <sub>SSA</sub> | _                      | V <sub>DDA</sub> – 1 | V          |

| INL12              | Integral non linearity <sup>[41]</sup>                                                            | Range = ±1.024 V, unbuffered                                  | _                | -                      | ±1                   | LSB        |

| DNL12              | Differential non linearity <sup>[41]</sup>                                                        | Range = ±1.024 V, unbuffered                                  | -                | -                      | ±1                   | LSB        |

| INL8               | Integral non linearity <sup>[41]</sup>                                                            | Range = ±1.024 V, unbuffered                                  | _                | -                      | ±1                   | LSB        |

| DNL8               | Differential non linearity <sup>[41]</sup>                                                        | Range = ±1.024 V, unbuffered                                  | _                | -                      | ±1                   | LSB        |

| Rin_Buff           | ADC input resistance                                                                              | Input buffer used                                             | 10               | -                      | -                    | MΩ         |

| Rin_ADC12          | ADC input resistance                                                                              | Input buffer bypassed, 12 bit, Range = ±1.024 V               | _                | 148 <sup>[42]</sup>    | _                    | kΩ         |

| Rin_ExtRef         | ADC external reference input resistance                                                           |                                                               | -                | 70 <sup>[42, 43]</sup> | -                    | kΩ         |

| Vextref            | ADC external reference input voltage, see also internal reference in Voltage Reference on page 88 | Pins P0[3], P3[2]                                             | 0.9              | _                      | 1.3                  | V          |

| <b>Current Cor</b> |                                                                                                   |                                                               |                  |                        |                      |            |

| I <sub>DD_12</sub> | Current consumption, 12 bit <sup>[41]</sup>                                                       | 192 ksps, unbuffered                                          | _                | _                      | 1.4                  | mA         |

| I <sub>BUFF</sub>  | Buffer current consumption <sup>[41]</sup>                                                        |                                                               | _                | _                      | 2.5                  | mA         |

Document Number: 001-84935 Rev. \*L Page 86 of 131

<sup>41.</sup> Based on device characterization (not production tested).

<sup>42.</sup> By using switched capacitors at the ADC input an effective input resistance is created. Holding the gain and number of bits constant, the resistance is proportional to

the inverse of the clock frequency. This value is calculated, not measured. For more information see the Technical Reference Manual.

Recommend an external reference device with an output impedance <100 Ω, for example, the LM185/285/385 family. A 1 μF capacitor is recommended. For more information, see AN61290 - PSoC® 3 and PSoC 5LP Hardware Design Considerations.</li>

Table 11-21. Delta-sigma ADC AC Specifications

| Parameter     | Description                                                       | Conditions                                   | Min | Тур | Max    | Units   |

|---------------|-------------------------------------------------------------------|----------------------------------------------|-----|-----|--------|---------|

|               | Startup time                                                      |                                              | -   | _   | 4      | Samples |

| THD           | Total harmonic distortion <sup>[44]</sup>                         | Buffer gain = 1, 12-bit,<br>Range = ±1.024 V | -   | _   | 0.0032 | %       |

| 12-Bit Resolu | ition Mode                                                        |                                              |     |     |        | •       |

| SR12          | Sample rate, continuous, high power <sup>[44]</sup>               | Range = ±1.024 V, unbuffered                 | 4   | _   | 192    | ksps    |

| BW12          | Input bandwidth at max sample rate <sup>[44]</sup>                | Range = ±1.024 V, unbuffered                 | _   | 44  | _      | kHz     |

| SINAD12int    | Signal to noise ratio, 12-bit, internal reference <sup>[44]</sup> | Range = ±1.024 V, unbuffered                 | 66  | _   | _      | dB      |

| 8-Bit Resolut | ion Mode                                                          |                                              |     |     |        | •       |

| SR8           | Sample rate, continuous, high power <sup>[44]</sup>               | Range = ±1.024 V, unbuffered                 | 8   | _   | 384    | ksps    |

| BW8           | Input bandwidth at max sample rate <sup>[44]</sup>                | Range = ±1.024 V, unbuffered                 | _   | 88  | _      | kHz     |

| SINAD8int     | Signal to noise ratio, 8-bit, internal reference <sup>[44]</sup>  | Range = ±1.024 V, unbuffered                 | 43  | _   | _      | dB      |

Table 11-22. Delta-sigma ADC Sample Rates, Range = ±1.024 V

| Resolution, | Conti | nuous  | Multi-S | Sample |

|-------------|-------|--------|---------|--------|

| Bits        | Min   | Max    | Min     | Max    |

| 8           | 8000  | 384000 | 1911    | 91701  |

| 9           | 6400  | 307200 | 1543    | 74024  |

| 10          | 5566  | 267130 | 1348    | 64673  |

| 11          | 4741  | 227555 | 1154    | 55351  |

| 12          | 4000  | 192000 | 978     | 46900  |

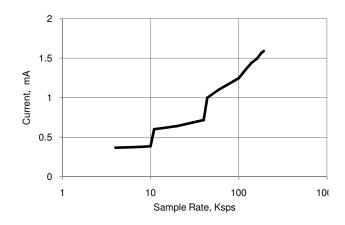

Figure 11-33. Delta-sigma ADC IDD vs sps, Range =  $\pm 1.024$  V, Continuous Sample Mode, Input Buffer Bypassed

## Note

44. Based on device characterization (Not production tested).

Table 11-25. SAR ADC AC Specifications<sup>[49]</sup>

| Parameter | Description                                                    | Conditions | Min | Тур | Max  | Units |

|-----------|----------------------------------------------------------------|------------|-----|-----|------|-------|

| A_SAMP_1  | Sample rate with external reference bypass cap                 |            | _   | _   | 1    | Msps  |

| A_SAMP_2  | Sample rate with no bypass cap.<br>Reference = V <sub>DD</sub> |            | _   | _   | 500  | Ksps  |

| A_SAMP_3  | Sample rate with no bypass cap. Internal reference             |            | _   | _   | 100  | Ksps  |

|           | Startup time                                                   |            | _   | _   | 10   | μs    |

| SINAD     | Signal-to-noise ratio                                          |            | 68  | _   | _    | dB    |

| THD       | Total harmonic distortion                                      |            | _   | _   | 0.02 | %     |

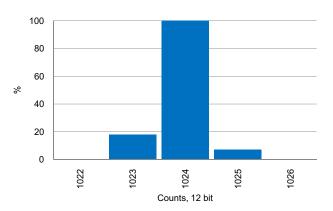

Figure 11-39. SAR ADC Noise Histogram, 100 ksps, Internal Reference No Bypass

Figure 11-40. SAR ADC Noise Histogram, 1 msps, Internal Reference Bypassed

Figure 11-41. SAR ADC Noise Histogram, 1 msps, External Reference

## Note

<sup>49.</sup> Based on device characterization (Not production tested).

Table 11-30. IDAC DC Specifications (continued)

| Parameter       | Description                          | Conditions                                                                                       | Min | Тур  | Max | Units |

|-----------------|--------------------------------------|--------------------------------------------------------------------------------------------------|-----|------|-----|-------|

| DNL             | Differential nonlinearity            | Sink mode, range = 255 $\mu$ A,<br>Rload = 2.4 $k\Omega$ , Cload = 15 pF                         | -   | ±0.3 | ±1  | LSB   |

|                 |                                      | Source mode, range = 255 $\mu$ A,<br>Rload = 2.4 $k\Omega$ , Cload = 15 pF                       | -   | ±0.3 | ±1  | LSB   |

|                 |                                      | Source mode, range = 31.875 $\mu$ A,<br>Rload = 20 k $\Omega$ , Cload = 15 pF <sup>[55]</sup>    | -   | ±0.2 | ±1  | LSB   |

|                 |                                      | Sink mode, range = 31.875 $\mu$ A,<br>Rload = 20 k $\Omega$ , Cload = 15 pF <sup>[55]</sup>      | -   | ±0.2 | ±1  | LSB   |

|                 |                                      | Source mode, range = 2.0 4 mA,<br>Rload = 600 $\Omega$ , Cload = 15 pF <sup>[55]</sup>           | -   | ±0.2 | ±1  | LSB   |

|                 |                                      | Sink mode, range = 2.0 4 mA,<br>Rload = 600 $\Omega$ , Cload = 15 pF <sup>[55]</sup>             | _   | ±0.2 | ±1  | LSB   |

| Vcompliance     | Dropout voltage, source or sink mode | Voltage headroom at max current, Rload to $V_{DDA}$ or Rload to $V_{SSA}$ , Vdiff from $V_{DDA}$ | 1   | _    | _   | V     |

| I <sub>DD</sub> | Operating current, code = 0          | Slow mode, source mode, range = 31.875 µA                                                        | -   | 44   | 100 | μA    |

|                 |                                      | Slow mode, source mode, range = 255 µA,                                                          | -   | 33   | 100 | μA    |

|                 |                                      | Slow mode, source mode, range = 2.04 mA                                                          | -   | 33   | 100 | μA    |

|                 |                                      | Slow mode, sink mode, range = 31.875 µA                                                          | _   | 36   | 100 | μA    |

|                 |                                      | Slow mode, sink mode, range = 255 μA                                                             | -   | 33   | 100 | μA    |

|                 |                                      | Slow mode, sink mode, range = 2.04 mA                                                            | -   | 33   | 100 | μA    |

|                 |                                      | Fast mode, source mode, range = 31.875 µA                                                        | _   | 310  | 500 | μA    |

|                 |                                      | Fast mode, source mode, range = 255 μA                                                           | _   | 305  | 500 | μA    |

|                 |                                      | Fast mode, source mode, range = 2.04 mA                                                          | _   | 305  | 500 | μA    |

|                 |                                      | Fast mode, sink mode, range = 31.875 µA                                                          | -   | 310  | 500 | μΑ    |

|                 |                                      | Fast mode, sink mode, range = 255 μA                                                             | _   | 300  | 500 | μA    |

|                 |                                      | Fast mode, sink mode, range = 2.04 mA                                                            | _   | 300  | 500 | μA    |

Note 55. Based on device characterization (Not production tested).

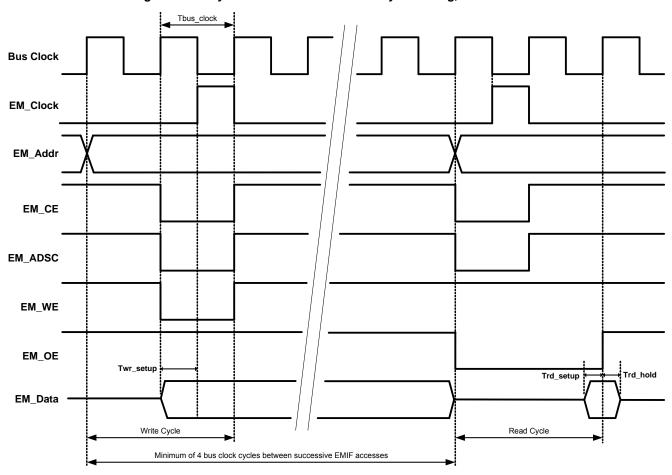

Figure 11-73. Synchronous Write and Read Cycle Timing, No Wait States

Table 11-66. Synchronous Write and Read Timing Specifications<sup>[75]</sup>

| Parameter  | Description                                                 | Conditions | Min             | Тур | Max | Units |

|------------|-------------------------------------------------------------|------------|-----------------|-----|-----|-------|

| Fbus_clock | Bus clock frequency <sup>[76]</sup>                         |            | -               | _   | 33  | MHz   |

| Tbus_clock | Bus clock period <sup>[77]</sup>                            |            | 30.3            | _   | _   | ns    |

| Twr_Setup  | Time from EM_data valid to rising edge of EM_Clock          |            | Tbus_clock - 10 | _   | _   | ns    |

| Trd_setup  | Time that EM_data must be valid before rising edge of EM_OE |            | 5               | _   | _   | ns    |

| Trd_hold   | Time that EM_data must be valid after rising edge of EM_OE  |            | 5               | _   | _   | ns    |

## Notes

<sup>75.</sup> Based on device characterization (Not production tested).

76. EMIF signal timings are limited by GPIO frequency limitations. See "GPIO" section on page 75.

77. EMIF output signals are generally synchronized to bus clock, so EMIF signal timings are dependent on bus clock frequency.

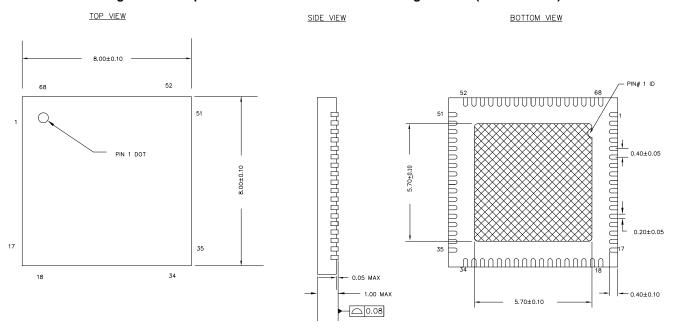

Figure 13-1. 68-pin QFN 8 × 8 with 0.4 mm Pitch Package Outline (Sawn Version)

## NOTES:

- 1. MATCH AREA IS SOLDERABLE EXPOSED METAL.

- 2. REFERENCE JEDEC#: MO-220

- 3. PACKAGE WEIGHT: 17  $\pm$  2mg

- 4. ALL DIMENSIONS ARE IN MILLIMETERS

001-09618 \*E

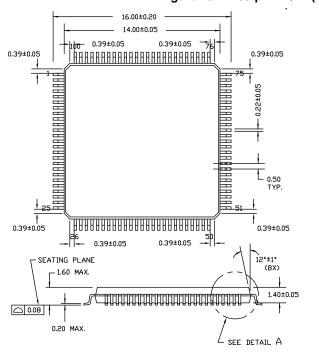

# Figure 13-2. 100-pin TQFP (14 x 14 x 1.4 mm) Package Outline

## NUTE:

- 1. JEDEC STD REF MS-026

- 2. BODY LENGTH DIMENSION DOES NOT INCLUDE MOLD PROTRUSION/END FLASH

MOLD PROTRUSION/END FLASH SHALL NOT EXCEED 0.0098 in (0.25 mm) PER SIDE

BODY LENGTH DIMENSIONS ARE MAX PLASTIC BODY SIZE INCLUDING MOLD MISMATCH

- 3. DIMENSIONS IN MILLIMETERS

51-85048 \*J

# **Document History Page** (continued)

| Description Title: PSoC <sup>®</sup> 5LP: CY8C56LP Family Datasheet Programmable System-on-Chip (PSoC <sup>®</sup> ) Document Number: 001-84935 |         |                         |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision                                                                                                                                        | ECN     | Orig. of<br>Change      | Submission<br>Date | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| *H (cont.)                                                                                                                                      | 4698847 | AVER /<br>MKEA /<br>GJV | 03/24/2015         | Updated Electrical Specifications: Updated Memory: Updated Flash: Updated Table 11-58: Updated details in "Conditions" column corresponding to "Flash data retention time" parameter. Added Note 72 and referred the same note in last condition corresponding to "Flash data retention time" parameter. Updated EEPROM: Updated Table 11-60: Updated details in "Conditions" column corresponding to "EEPROM data retention time" parameter. Added Note 72 and referred the same note in last condition corresponding to "EEPROM data retention time" parameter. Updated Nonvolatile Latches (NVL): Updated Nonvolatile Latches (NVL): Updated Table 11-62: Updated details in "Conditions" column corresponding to "NVL data retention time" parameter. Added Note 73 and referred the same note in last condition corresponding to "NVL data retention time" parameter. Updated Clocking: Updated Clocking: Updated Internal Main Oscillator: Updated Table 11-76: Replaced 85 °C with 105 °C. Updated Figure 11-78. Updated Ordering Information: |

|                                                                                                                                                 |         |                         |                    | Updated Part Numbering Conventions: Added "Q: Extended" as sub bullet under "g: Temperature Range".  Updated Packaging: Updated Table 13-1: Changed maximum value of T <sub>A</sub> parameter from 85 °C to 105 °C. Changed maximum value of T <sub>J</sub> parameter from 100 °C to 120 °C.  Updated: Updated: Updated: Spec 001-88034 – Changed revision from ** to *A.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| *                                                                                                                                               | 4839323 | MKEA                    | 07/15/2015         | Added reference to code examples in More Information. Updated typ value of $T_{WRITE}$ from 2 to 10 in EEPROM AC specs table. Changed "Device supply for USB operation" to "Device supply $(V_{DDD})$ for USB operation" in USB DC Specifications. Clarified power supply sequencing and margin for $V_{DDA}$ and $V_{DDD}$ . Updated Serial Wire Debug Interface with limitations of debugging on Port 15. Updated Delta-sigma ADC DC Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

Document Number: 001-84935 Rev. \*L Page 129 of 131

# Sales, Solutions, and Legal Information

# Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

# **Products**

ARM® Cortex® Microcontrollers cypress.com/arm Automotive cypress.com/automotive Clocks & Buffers cypress.com/clocks Interface cypress.com/interface Internet of Things cypress.com/iot Memory cypress.com/memory Microcontrollers cypress.com/mcu **PSoC** cypress.com/psoc

Power Management ICs cypress.com/pmic

Touch Sensing cypress.com/touch

USB Controllers cypress.com/usb

Wireless Connectivity cypress.com/wireless

# PSoC® Solutions

PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP | PSoC 6

# **Cypress Developer Community**

Forums | WICED IOT Forums | Projects | Video | Blogs | Training | Components

# **Technical Support**

cypress.com/support

© Cypress Semiconductor Corporation, 2012-2017. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress hereby grants you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software (a) for Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware product units, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware products. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. To the extent permitted by applicable law, Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, life-support devices or systems, other medical devices or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or system could cause personal injury, death, or property damage ("Unintended Uses"). A critical component is any component of a device or system whose failure to perform can be reasonably expected to cause the failure of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and you shall and hereby do release Cypress from any claim, damage, or other liability arising from or related to all Unintended Uses of Cypress products. You shall indemnify and hold Cypress harmless from and against all claims, costs, damages, and other liabilities, including claims for personal injury or death, arising from or related to any Unintended Uses of Cypress products.

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, WICED, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.

Document Number: 001-84935 Rev. \*L Revised April 20, 2017 Page 131 of 131