Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                               |

|----------------------------|--------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                   |

| Speed                      | 150MHz                                                                               |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, SD, SPI, UART/USART, USB, USB OTG |

| Peripherals                | DMA, I <sup>2</sup> S, LVD, POR, PWM, WDT                                            |

| Number of I/O              | 128                                                                                  |

| Program Memory Size        | 1MB (1M x 8)                                                                         |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | -                                                                                    |

| RAM Size                   | 128K x 8                                                                             |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                                         |

| Data Converters            | A/D 77x16b; D/A 2x12b                                                                |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                   |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 256-LBGA                                                                             |

| Supplier Device Package    | 256-MAPPBGA (17x17)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mk61fn1m0vmj15               |

|                            |                                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Communication interfaces

- Ethernet controller with MII and RMII interface to external PHY and hardware IEEE 1588 capability

- USB high-/full-/low-speed On-the-Go controller with ULPI interface

- USB full-/low-speed On-the-Go controller with on-chip transceiver

- USB Device Charger detect (USBDCD)

- Two Controller Area Network (CAN) modules

- Three SPI modules

- Two I2C modules

- Six UART modules

- Secure Digital Host Controller (SDHC)

- Two I2S modules

# 1 Ordering parts

# 1.1 Determining valid orderable parts

Valid orderable part numbers are provided on the web. To determine the orderable part numbers for this device, go to freescale.com and perform a part number search for the following device numbers: PK61 and MK61

# 2 Part identification

# 2.1 Description

Part numbers for the chip have fields that identify the specific part. You can use the values of these fields to determine the specific part you have received.

# 2.2 Format

Part numbers for this device have the following format:

Q K## A M FFF T PP CC N

# 2.3 Fields

This table lists the possible values for each field in the part number (not all combinations are valid):

| Field | Description               | Values                                                                                     |

|-------|---------------------------|--------------------------------------------------------------------------------------------|

| Q     | Qualification status      | <ul> <li>M = Fully qualified, general market flow</li> <li>P = Prequalification</li> </ul> |

| K##   | Kinetis family            | • K61                                                                                      |

| A     | Key attribute             | • F = Cortex-M4 w/ DSP and FPU                                                             |

| М     | Flash memory type         | <ul> <li>N = Program flash only</li> <li>X = Program flash and FlexMemory</li> </ul>       |

| FFF   | Program flash memory size | <ul> <li>512 = 512 KB</li> <li>1M0 = 1 MB</li> </ul>                                       |

Table continues on the next page ....

Jeneral

Symbol Description Unit Notes Min. Тур. Max. Output high current total for DDR pins I<sub>OHT\_DDR</sub> 100 mΑ DDR1 56 mΑ DDR2 39 mΑ LPDDR1 Output high voltage — high drive strength  $V_{BAT} - 0.5$ V V<sub>OH\_Tamper</sub> • 2.7 V  $\leq$  V<sub>BAT</sub>  $\leq$  3.6 V, I<sub>OH</sub> = -10mA  $V_{BAT} - 0.5$ V • 1.71 V  $\leq$  V<sub>BAT</sub>  $\leq$  2.7 V, I<sub>OH</sub> = -3mA Output high voltage - low drive strength  $V_{BAT} - 0.5$ ۷ \_  $V_{BAT} - 0.5$ V • 2.7 V  $\leq$  V<sub>BAT</sub>  $\leq$  3.6 V, I<sub>OH</sub> = -2mA • 1.71 V  $\leq$  V<sub>BAT</sub>  $\leq$  2.7 V, I<sub>OH</sub> = -0.6mA Output high current total for Tamper pins 100 \_\_\_\_ \_\_\_\_ mΑ I<sub>OH\_Tamper</sub>  $V_{OL}$ Output low voltage - high drive strength • 2.7 V  $\leq$  V<sub>DD</sub>  $\leq$  3.6 V, I<sub>OL</sub> = 10 mA 0.5 V •  $1.71 \text{ V} \le \text{V}_{DD} \le 2.7 \text{ V}, \text{ I}_{OL} = 5 \text{ mA}$ 0.5 V Output low voltage - low drive strength • 2.7 V  $\leq$  V<sub>DD</sub>  $\leq$  3.6 V, I<sub>OL</sub> = 2 mA 0.5 V • 1.71 V  $\leq$  V<sub>DD</sub>  $\leq$  2.7 V, I<sub>OL</sub> = 1 mA 0.5 ٧ IOLT Output low current total for all ports 100 mΑ Output low current total for fast digital ports 100 \_\_\_\_ mΑ I<sub>OLT io60</sub> Output low voltage for DDR pins V<sub>OL\_DDR</sub> 0.37 V DDR1 (I<sub>OL</sub> = 16.2 mA) 0.28 ۷ DDR2 half strength (I<sub>OL</sub> = 5.36 mA) 0.28 ٧ DDR2 full strength (I<sub>OL</sub> = 13.4 mA) 0.1 x ٧ • LPDDR1 half strength (I<sub>OL</sub> = 0.1 mA) V<sub>DD DDR</sub> V LPDDR1 full strength (I<sub>OL</sub> = 0.1 mA) 0.1 x V<sub>DD\_DDR</sub> Output low current total for DDR pins IOLT\_DDR 100 mΑ DDR1 56 mΑ DDR2 39 mΑ LPDDR1 V<sub>OL\_Tamper</sub> Output low voltage — high drive strength 0.5 ۷ • 2.7 V  $\leq$  V<sub>BAT</sub>  $\leq$  3.6 V, I<sub>OL</sub> = 10mA V 0.5 1.71 V ≤ V<sub>BAT</sub> ≤ 2.7 V, I<sub>OL</sub> = 3mA Output low voltage - low drive strength V 0.5 • 2.7 V  $\leq$  V<sub>BAT</sub>  $\leq$  3.6 V, I<sub>OL</sub> = 2mA 0.5 V • 1.71 V  $\leq$  V<sub>BAT</sub>  $\leq$  2.7 V, I<sub>OL</sub> = 0.6mA

Table 4. Voltage and current operating behaviors (continued)

Table continues on the next page ...

General

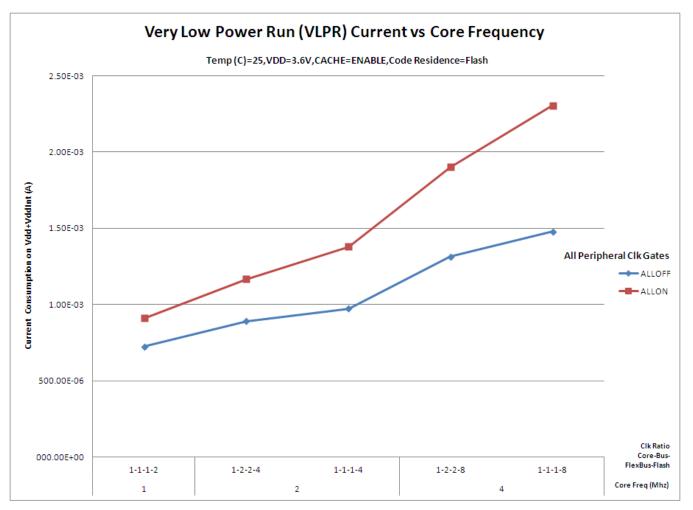

Figure 4. VLPR mode supply current vs. core frequency

## 5.2.6 EMC radiated emissions operating behaviors Table 7. EMC radiated emissions operating behaviors for 256MAPBGA

| Symbol           | Description                        | Frequency<br>band (MHz) | Тур. | Unit | Notes   |

|------------------|------------------------------------|-------------------------|------|------|---------|

| V <sub>RE1</sub> | Radiated emissions voltage, band 1 | 0.15–50                 | 21   | dBµV | 1, 2, 3 |

| V <sub>RE2</sub> | Radiated emissions voltage, band 2 | 50–150                  | 24   | dBµV |         |

| V <sub>RE3</sub> | Radiated emissions voltage, band 3 | 150–500                 | 29   | dBµV |         |

| V <sub>RE4</sub> | Radiated emissions voltage, band 4 | 500–1000                | 28   | dBµV |         |

- Determined according to IEC Standard 61967-1, Integrated Circuits Measurement of Electromagnetic Emissions, 150 kHz to 1 GHz Part 1: General Conditions and Definitions and IEC Standard 61967-2, Integrated Circuits - Measurement of Electromagnetic Emissions, 150 kHz to 1 GHz Part 2: Measurement of Radiated Emissions – TEM Cell and Wideband TEM Cell Method. Measurements were made while the microcontroller was running basic application code. The reported emission level is the value of the maximum measured emission, rounded up to the next whole number, from among the measured orientations in each frequency range.

- 2.  $V_{DD}$  = 3.3 V,  $T_A$  = 25 °C,  $f_{OSC}$  = 12 MHz (crystal),  $f_{SYS}$  = 72 MHz,  $f_{BUS}$  = 72 MHz

- 3. Determined according to IEC Standard JESD78, IC Latch-Up Test

# 5.2.7 Designing with radiated emissions in mind

To find application notes that provide guidance on designing your system to minimize interference from radiated emissions:

- 1. Go to www.freescale.com.

- 2. Perform a keyword search for "EMC design."

## 5.2.8 Capacitance attributes

Table 8. Capacitance attributes

| Symbol                 | Description                          | Min. | Max. | Unit |

|------------------------|--------------------------------------|------|------|------|

| C <sub>IN_A</sub>      | Input capacitance: analog pins       | —    | 7    | pF   |

| C <sub>IN_D</sub>      | Input capacitance: digital pins      |      | 7    | pF   |

| C <sub>IN_D_io60</sub> | Input capacitance: fast digital pins |      | 9    | pF   |

# 5.3 Switching specifications

# 5.3.1 Device clock specifications

#### Table 9. Device clock specifications

| Symbol                 | Description                                            | Min. | Max. | Unit | Notes |

|------------------------|--------------------------------------------------------|------|------|------|-------|

|                        | Normal run mod                                         | e    |      | •    |       |

| f <sub>SYS</sub>       | System and core clock                                  | _    | 150  | MHz  |       |

| fsys_usbfs             | System and core clock when Full Speed USB in operation | 20   | -    | MHz  |       |

| f <sub>SYS_USBHS</sub> | System and core clock when High Speed USB in operation | 60   | _    | MHz  |       |

| f <sub>ENET</sub>      | System and core clock when ethernet in operation       |      |      | MHz  |       |

|                        | • 10 Mbps                                              | 5    | _    |      |       |

|                        | • 100 Mbps                                             | 50   | _    |      |       |

| f <sub>BUS</sub>       | Bus clock                                              | _    | 75   | MHz  |       |

| FB_CLK                 | FlexBus clock                                          | —    | 50   | MHz  |       |

| f <sub>FLASH</sub>     | Flash clock                                            | _    | 25   | MHz  |       |

| f <sub>DDR</sub>       | DDR clock                                              | _    | 150  | MHz  |       |

| f <sub>LPTMR</sub>     | LPTMR clock                                            | _    | 25   | MHz  |       |

|                        | VLPR mode <sup>1</sup>                                 |      |      |      |       |

Table continues on the next page ...

rempheral operating requirements and behaviors

## 6.3.1 MCG specifications Table 15. MCG specifications

| Symbol                  | Description                                                                       |                                                                  | Min.                           | Тур.  | Max.    | Unit              | Notes |

|-------------------------|-----------------------------------------------------------------------------------|------------------------------------------------------------------|--------------------------------|-------|---------|-------------------|-------|

| f <sub>ints_ft</sub>    | Internal reference<br>factory trimmed at                                          | —                                                                | 32.768                         | _     | kHz     |                   |       |

| $f_{ints_t}$            | Internal reference<br>trimmed                                                     | frequency (slow clock) — user                                    | 31.25                          | _     | 39.0625 | kHz               |       |

| ∆ <sub>fdco_res_t</sub> |                                                                                   | ned average DCO output<br>voltage and temperature —<br>d SCFTRIM | _                              | ± 0.3 | ± 0.6   | %f <sub>dco</sub> | 1     |

| ∆f <sub>dco_res_t</sub> |                                                                                   | ned average DCO output<br>voltage and temperature —<br>y         |                                | ± 0.2 | ± 0.5   | %f <sub>dco</sub> | 1     |

| $\Delta f_{dco_t}$      |                                                                                   | rimmed average DCO output<br>ed voltage and temperature          | _                              | ± 4.5 |         | %f <sub>dco</sub> | 1     |

| f <sub>intf_ft</sub>    |                                                                                   | frequency (fast clock) —<br>nominal VDD and 25°C                 | —                              | 4     | —       | MHz               |       |

| f <sub>intf_t</sub>     | Internal reference frequency (fast clock) — user trimmed at nominal VDD and 25 °C |                                                                  | 3                              | _     | 5       | MHz               |       |

| f <sub>loc_low</sub>    | Loss of external clock minimum frequency —<br>RANGE = 00                          |                                                                  | (3/5) x<br>f <sub>ints_t</sub> |       | —       | kHz               |       |

| f <sub>loc_high</sub>   | Loss of external cle<br>RANGE = 01, 10, 0                                         | (16/5) x<br>f <sub>ints_t</sub>                                  |                                |       | kHz     |                   |       |

|                         |                                                                                   | FI                                                               | L                              |       |         |                   |       |

| f <sub>fll_ref</sub>    | FLL reference freq                                                                | uency range                                                      | 31.25                          | _     | 39.0625 | kHz               |       |

| f <sub>dco</sub>        | DCO output<br>frequency range                                                     | Low range (DRS=00)<br>640 × f <sub>fll_ref</sub>                 | 20                             | 20.97 | 25      | MHz               | 2, 3  |

|                         |                                                                                   | Mid range (DRS=01)<br>1280 × f <sub>fll_ref</sub>                | 40                             | 41.94 | 50      | MHz               |       |

|                         |                                                                                   | Mid-high range (DRS=10)<br>1920 × f <sub>fll_ref</sub>           | 60                             | 62.91 | 75      | MHz               |       |

|                         |                                                                                   | High range (DRS=11)<br>2560 × f <sub>fll_ref</sub>               | 80                             | 83.89 | 100     | MHz               |       |

| co_t_DMX32              | DCO output<br>frequency                                                           | Low range (DRS=00)<br>732 × f <sub>fll_ref</sub>                 | —                              | 23.99 | -       | MHz               | 4, 5  |

|                         |                                                                                   | Mid range (DRS=01)<br>1464 × f <sub>fll_ref</sub>                | —                              | 47.97 | -       | MHz               | •     |

|                         |                                                                                   | <br>Mid-high range (DRS=10)<br>2197 × f <sub>fll_ref</sub>       | —                              | 71.99 | -       | MHz               | -     |

|                         |                                                                                   | High range (DRS=11)<br>2929 × f <sub>fll_ref</sub>               | _                              | 95.98 | -       | MHz               | -     |

|                         |                                                                                   |                                                                  |                                |       |         |                   |       |

Table continues on the next page...

#### rempheral operating requirements and behaviors

| Symbol                   | Description                                            | Min. | Тур. | Max. | Unit | Notes |

|--------------------------|--------------------------------------------------------|------|------|------|------|-------|

| t <sub>swapx01</sub>     | control code 0x01                                      | _    | 200  | —    | μs   |       |

| t <sub>swapx02</sub>     | control code 0x02                                      | —    | 70   | 150  | μs   |       |

| t <sub>swapx04</sub>     | control code 0x04                                      | —    | 70   | 150  | μs   |       |

| t <sub>swapx08</sub>     | control code 0x08                                      | —    | —    | 30   | μs   |       |

|                          | Program Partition for EEPROM execution time            |      |      |      |      |       |

| t <sub>pgmpart64k</sub>  | 64 KB EEPROM backup                                    | —    | 235  | _    | ms   |       |

| t <sub>pgmpart256k</sub> | • 256 KB EEPROM backup                                 | —    | 240  | _    | ms   |       |

|                          | Set FlexRAM Function execution time:                   |      |      |      |      |       |

| t <sub>setramff</sub>    | Control Code 0xFF                                      | —    | 205  | —    | μs   |       |

| t <sub>setram64k</sub>   | 64 KB EEPROM backup                                    | —    | 1.6  | 2.5  | ms   |       |

| t <sub>setram128k</sub>  | 128 KB EEPROM backup                                   | —    | 2.7  | 3.8  | ms   |       |

| t <sub>setram256k</sub>  | • 256 KB EEPROM backup                                 | —    | 4.8  | 6.2  | ms   |       |

| t <sub>eewr8bers</sub>   | Byte-write to erased FlexRAM location execution time   | _    | 140  | 225  | μs   | 3     |

|                          | Byte-write to FlexRAM execution time:                  |      |      |      |      |       |

| t <sub>eewr8b64k</sub>   | 64 KB EEPROM backup                                    | —    | 400  | 1700 | μs   |       |

| t <sub>eewr8b128k</sub>  | 128 KB EEPROM backup                                   | —    | 450  | 1800 | μs   |       |

| t <sub>eewr8b256k</sub>  | • 256 KB EEPROM backup                                 | —    | 525  | 2000 | μs   |       |

| t <sub>eewr16bers</sub>  | 16-bit write to erased FlexRAM location execution time | _    | 140  | 225  | μs   |       |

|                          | 16-bit write to FlexRAM execution time:                |      |      |      |      |       |

| t <sub>eewr16b64k</sub>  | 64 KB EEPROM backup                                    | —    | 400  | 1700 | μs   |       |

| t <sub>eewr16b128k</sub> | 128 KB EEPROM backup                                   | —    | 450  | 1800 | μs   |       |

| t <sub>eewr16b256k</sub> | • 256 KB EEPROM backup                                 | —    | 525  | 2000 | μs   |       |

| t <sub>eewr32bers</sub>  | 32-bit write to erased FlexRAM location execution time |      | 180  | 275  | μs   |       |

|                          | 32-bit write to FlexRAM execution time:                |      |      |      |      |       |

| t <sub>eewr32b64k</sub>  | • 64 KB EEPROM backup                                  | _    | 475  | 1850 | μs   |       |

| t <sub>eewr32b128k</sub> | • 128 KB EEPROM backup                                 | _    | 525  | 2000 | μs   |       |

| t <sub>eewr32b256k</sub> | • 256 KB EEPROM backup                                 | —    | 600  | 2200 | μs   |       |

#### Table 21. Flash command timing specifications (continued)

1. Assumes 25MHz or greater flash clock frequency.

2. Maximum times for erase parameters based on expectations at cycling end-of-life.

3. For byte-writes to an erased FlexRAM location, the aligned word containing the byte must be erased.

| Symbol              | Description                                                               | Min.                                 | Max.                             | Unit               | Notes |

|---------------------|---------------------------------------------------------------------------|--------------------------------------|----------------------------------|--------------------|-------|

|                     | • DDR2                                                                    | 6.6                                  | 20                               | ns                 |       |

|                     | • LPDDR                                                                   |                                      |                                  |                    |       |

| V <sub>OX-AC</sub>  | DDRCK AC differential cross point voltage                                 | 0.5 x V <sub>DD DDR</sub>            | 0.5 x V <sub>DD DDR</sub>        | V                  |       |

|                     | • DDR1                                                                    | - 0.2 V                              | + 0.2 V                          | V                  |       |

|                     | • DDR2                                                                    | $0.5 \times V_{DD_DDR}$              |                                  | V                  |       |

|                     | LPDDR                                                                     | – 0.125 V                            | + 0.125 V                        | -                  |       |

|                     |                                                                           | 0.4 x V <sub>DD_DDR</sub>            | 0.4 x V <sub>DD_DDR</sub>        |                    |       |

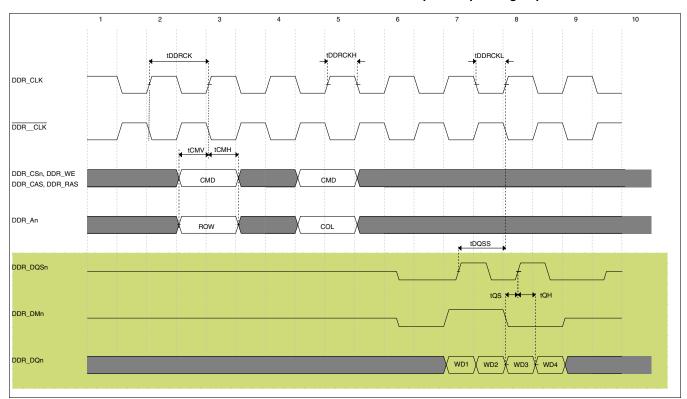

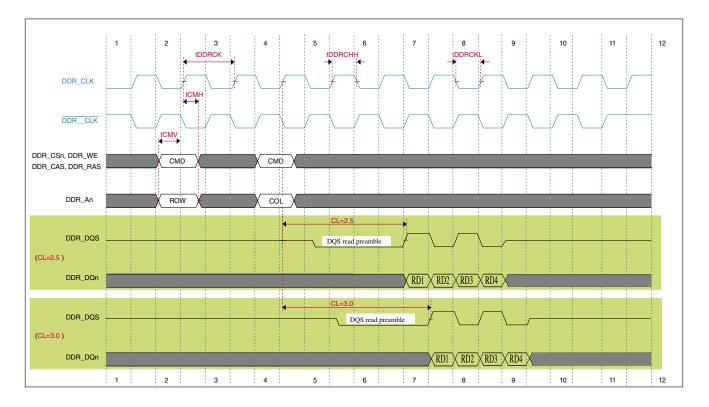

| t <sub>DDRCKH</sub> | Pulse width high                                                          | 0.45                                 | 0.55                             | t <sub>DDRCK</sub> | 3     |

| t <sub>DDRCKL</sub> | Pulse width low                                                           | 0.45                                 | 0.55                             | t <sub>DDRCK</sub> | 3     |

| t <sub>CMV</sub>    | Address, DDR_CKE, DDR_CAS, DDR_RAS,<br>DDR_WE, DDR_CSn — output setup     | 0.5 x t <sub>DDRCK</sub> –<br>1      | —                                | ns                 | 4     |

| t <sub>CMH</sub>    | Address, DDR_CKE, DDR_CAS, DDR_RAS, DDR_WE, DDR_CSn — output hold         | 0.5 x t <sub>DDRCK</sub> –<br>1      | —                                | ns                 |       |

| t <sub>DQSS</sub>   | DQS rising edge to CK rising edge                                         | -0.2 x t <sub>DDRCK</sub>            | 0.2 x t <sub>DDRCK</sub>         | ns                 |       |

| t <sub>QS</sub>     | Data and data mask output setup (DQ→DQS) relative to DQS (DDR write mode) | 0.25 x t <sub>DDRCK</sub> –<br>1     | —                                | ns                 | 5, 6  |

| t <sub>QH</sub>     | Data and data mask output hold (DQS→DQ) relative to DQS (DDR write mode)  | 0.25 x t <sub>DDRCK</sub> –<br>1     | —                                | ns                 | 7     |

| t <sub>DQSQ</sub>   | DQS-DQ skew for DQS and associated DQ signals                             | – (0.25 х<br>t <sub>DDRCK</sub> – 1) | 0.25 x t <sub>DDRCK</sub> –<br>1 | ns                 | 8     |

#### Table 26. DDR controller — AC timing specifications (continued)

- 1. This is minimum frequency of operation according to JEDEC DDR2 specification.

- 2. DDR data rate =  $2 \times DDR$  clock frequency

- 3. Pulse width high plus pulse width low cannot exceed min and max clock period.

- Command output setup should be 1/2 the memory bus clock (t<sub>DDRCK</sub>) plus some minor adjustments for process, temperature, and voltage variations.

- This specification relates to the required input setup time of DDR memories. The microprocessor's output setup should be larger than the input setup of the DDR memories. If it is not larger, then the input setup on the memory is in violation. DDR\_DQ[15:8] is relative to DDR\_DQS[1]; DDR\_DQ[7:0] is relative to DDR\_DQS[0].

- 6. The first data beat is valid before the first rising edge of DQS and after the DQS write preamble. The remaining data beats are valid for each subsequent DQS edge.

- 7. This specification relates to the required hold time of DDR memories. DDR\_DQ[15:8] is relative to DDR\_DQS[1]; DDR\_DQ[7:0] is relative to DDR\_DQS[0]

- Data input skew is derived from each DQS clock edge. It begins with a DQS transition and ends when the last data line becomes valid. This input skew must include DDR memory output skew and system level board skew (due to routing or other factors).

Peripheral operating requirements and behaviors

Figure 18. DDR write timing

### Figure 19. DDR read timing

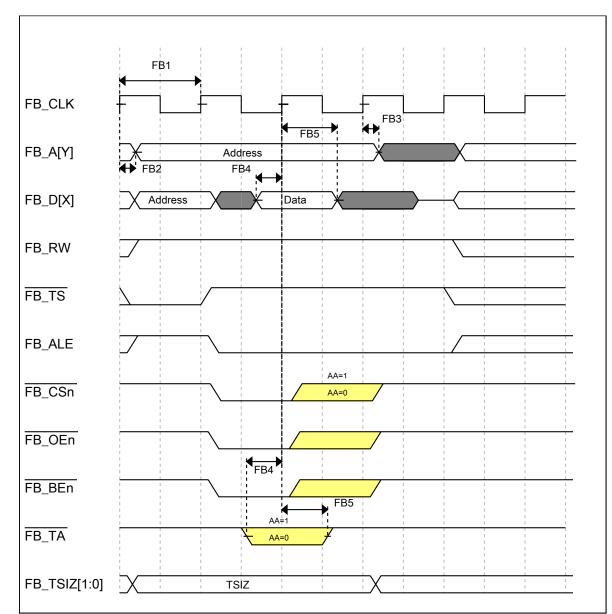

Table 28. Flexbus full voltage range switching specifications (continued)

| Num | Description                | Min. | Max. | Unit | Notes |

|-----|----------------------------|------|------|------|-------|

| FB4 | Data and FB_TA input setup | 13.7 | —    | ns   | 2     |

| FB5 | Data and FB_TA input hold  | 0.5  | —    | ns   | 2     |

1. Specification is valid for all FB\_AD[31:0], FB\_BE/BWEn, FB\_CSn, FB\_OE, FB\_R/W, FB\_TBST, FB\_TSIZ[1:0], FB\_ALE, and FB\_TS.

2. Specification is valid for all FB\_AD[31:0] and  $\overline{\text{FB}_{-}\text{TA}}.$

Figure 21. FlexBus read timing diagram

#### rempheral operating requirements and behaviors

| Symbol              | Description         | Conditions <sup>1</sup>                         | Min.                   | Typ. <sup>2</sup> | Max. | Unit  | Notes                                                                  |

|---------------------|---------------------|-------------------------------------------------|------------------------|-------------------|------|-------|------------------------------------------------------------------------|

|                     |                     | • Avg = 32                                      |                        |                   |      |       |                                                                        |

| EIL                 | Input leakage error |                                                 | $I_{ln} \times R_{AS}$ |                   |      | mV    | I <sub>In</sub> = leakage<br>current                                   |

|                     |                     |                                                 |                        |                   |      |       | (refer to the<br>MCU's voltage<br>and current<br>operating<br>ratings) |

|                     | Temp sensor slope   | Across the full temperature range of the device | 1.55                   | 1.62              | 1.69 | mV/°C | 8                                                                      |

| V <sub>TEMP25</sub> | Temp sensor voltage | 25 °C                                           | 706                    | 716               | 726  | mV    | 8                                                                      |

### Table 30. 16-bit ADC characteristics ( $V_{REFH} = V_{DDA}$ , $V_{REFL} = V_{SSA}$ ) (continued)

1. All accuracy numbers assume the ADC is calibrated with  $V_{\mathsf{REFH}}$  =  $V_{\mathsf{DDA}}$

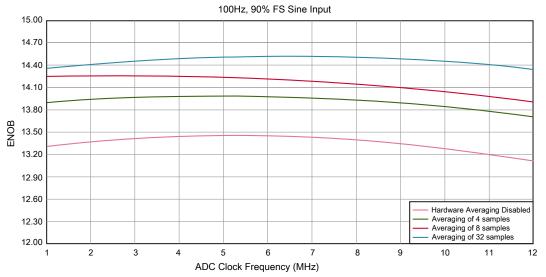

Typical values assume V<sub>DDA</sub> = 3.0 V, Temp = 25 °C, f<sub>ADCK</sub> = 2.0 MHz unless otherwise stated. Typical values are for reference only and are not tested in production.

The ADC supply current depends on the ADC conversion clock speed, conversion rate and ADC\_CFG1[ADLPC] (low power). For lowest power operation, ADC\_CFG1[ADLPC] must be set, the ADC\_CFG2[ADHSC] bit must be clear with 1 MHz ADC conversion clock speed.

4. 1 LSB =  $(V_{REFH} - V_{REFL})/2^N$

5. ADC conversion clock < 16 MHz, Max hardware averaging (AVGE = %1, AVGS = %11)

- 6. Input data is 100 Hz sine wave. ADC conversion clock < 12 MHz.

- 7. Input data is 1 kHz sine wave. ADC conversion clock < 12 MHz.

- 8. ADC conversion clock < 3 MHz

Typical ADC 16-bit Differential ENOB vs ADC Clock

Figure 24. Typical ENOB vs. ADC\_CLK for 16-bit differential mode

| Symbol               | Description                                   | Conditions                                                                                                                  | Min.     | Typ. <sup>1</sup>                                          | Max.                 | Unit             | Notes                                                                  |

|----------------------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|----------|------------------------------------------------------------|----------------------|------------------|------------------------------------------------------------------------|

|                      |                                               |                                                                                                                             |          |                                                            |                      |                  | f <sub>VDDA</sub> = 50Hz,<br>60Hz                                      |

| CMRR                 | Common mode rejection ratio                   | • Gain=1<br>• Gain=64                                                                                                       | -        | -84<br>-85                                                 | _                    | dB<br>dB         | V <sub>CM</sub> =<br>500mVpp,<br>f <sub>VCM</sub> = 50Hz,<br>100Hz     |

| V <sub>OFS</sub>     | Input offset<br>voltage                       | <ul> <li>Chopping disabled<br/>(ADC_PGA[PGACHPb]<br/>=1)</li> <li>Chopping enabled<br/>(ADC_PGA[PGACHPb]<br/>=0)</li> </ul> | _        | 2.4<br>0.2                                                 | _                    | mV<br>mV         | Output offset =<br>V <sub>OFS</sub> *(Gain+1)                          |

| T <sub>GSW</sub>     | Gain switching<br>settling time               |                                                                                                                             | -        | _                                                          | 10                   | μs               | 5                                                                      |

| dG/dT                | Gain drift over full temperature range        | • Gain=1<br>• Gain=64                                                                                                       | -        | 6<br>31                                                    | 10<br>42             | ppm/°C<br>ppm/°C |                                                                        |

| $dG/dV_{DDA}$        | Gain drift over supply voltage                | • Gain=1<br>• Gain=64                                                                                                       | -        | 0.07<br>0.14                                               | 0.21<br>0.31         | %/V<br>%/V       | V <sub>DDA</sub> from 1.71<br>to 3.6V                                  |

| E <sub>IL</sub>      | Input leakage<br>error                        | All modes                                                                                                                   |          | $I_{ln} \times R_{AS}$                                     |                      | mV               | I <sub>In</sub> = leakage<br>current                                   |

|                      |                                               |                                                                                                                             |          |                                                            |                      |                  | (refer to the<br>MCU's voltage<br>and current<br>operating<br>ratings) |

| V <sub>PP,DIFF</sub> | Maximum<br>differential input<br>signal swing |                                                                                                                             |          | √ <sub>x</sub> ,V <sub>DDA</sub> −V <sub>x</sub> )<br>Gain |                      | V                | 6                                                                      |

|                      |                                               |                                                                                                                             | -        | $K = V_{\text{REFPG}}$                                     | <sub>A</sub> × 0.583 |                  |                                                                        |

| SNR                  | Signal-to-noise<br>ratio                      | • Gain=1<br>• Gain=64                                                                                                       | 80<br>52 | 90<br>66                                                   | _                    | dB<br>dB         | 16-bit<br>differential<br>mode,<br>Average=32                          |

| THD                  | Total harmonic                                | Gain=1                                                                                                                      | 85       | 100                                                        | _                    | dB               | 16-bit                                                                 |

|                      | distortion                                    | • Gain=64                                                                                                                   | 49       | 95                                                         | _                    | dB               | differential<br>mode,<br>Average=32,<br>f <sub>in</sub> =100Hz         |

| SFDR                 | Spurious free                                 | Gain=1                                                                                                                      | 85       | 105                                                        | _                    | dB               | 16-bit                                                                 |

|                      | dynamic range                                 | • Gain=64                                                                                                                   | 53       | 88                                                         |                      | dB               | differential<br>mode,<br>Average=32,<br>f <sub>in</sub> =100Hz         |

| ENOB                 | Effective number                              | Gain=1, Average=4                                                                                                           | 11.6     | 13.4                                                       | —                    | bits             | 16-bit                                                                 |

|                      | of bits                                       | <ul> <li>Gain=1, Average=8</li> </ul>                                                                                       | 8.0      | 13.6                                                       | _                    | bits             | differential<br>mode,f <sub>in</sub> =100Hz                            |

|                      |                                               | Gain=64, Average=4                                                                                                          | 7.2      | 9.6                                                        | _                    | bits             |                                                                        |

|                      |                                               | Gain=64, Average=8                                                                                                          | 6.3      | 9.6                                                        |                      | bits             |                                                                        |

|                      |                                               |                                                                                                                             | 12.8     | 14.5                                                       | —                    | bits             |                                                                        |

### Table 32. 16-bit ADC with PGA characteristics (continued)

Table continues on the next page...

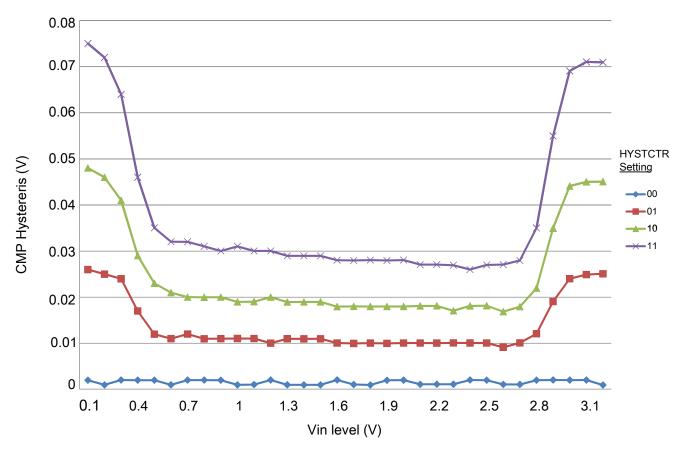

Table 33. Comparator and 6-bit DAC electrical specifications (continued)

| Symbol | Description                          | Min. | Тур. | Max. | Unit             |

|--------|--------------------------------------|------|------|------|------------------|

| INL    | 6-bit DAC integral non-linearity     | -0.5 | —    | 0.5  | LSB <sup>3</sup> |

| DNL    | 6-bit DAC differential non-linearity | -0.3 |      | 0.3  | LSB              |

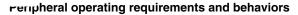

1. Typical hysteresis is measured with input voltage range limited to 0.6 to V<sub>DD</sub>-0.6 V.

Comparator initialization delay is defined as the time between software writes to change control inputs (Writes to CMP\_DACCR[DACEN], CMP\_DACCR[VRSEL], CMP\_DACCR[VOSEL], CMP\_MUXCR[PSEL], and CMP\_MUXCR[MSEL]) and the comparator output settling to a stable level.

Figure 26. Typical hysteresis vs. Vin level (VDD = 3.3 V, PMODE = 0)

Figure 27. Typical hysteresis vs. Vin level (VDD = 3.3 V, PMODE = 1)

## 6.6.3 12-bit DAC electrical characteristics

#### 6.6.3.1 12-bit DAC operating requirements Table 34. 12-bit DAC operating requirements

| Symbol            | Desciption              | Min.          | Max. | Unit | Notes |

|-------------------|-------------------------|---------------|------|------|-------|

| V <sub>DDA</sub>  | Supply voltage          | 1.71          | 3.6  | V    |       |

| V <sub>DACR</sub> | Reference voltage       | 1.13          | 3.6  | V    | 1     |

| CL                | Output load capacitance | —             | 100  | pF   | 2     |

| ١L                | Output load current     | urrent — 1 mA |      |      |       |

1. The DAC reference can be selected to be  $V_{\text{DDA}}$  or  $V_{\text{REFH}}$

2. A small load capacitance (47 pF) can improve the bandwidth performance of the DAC.

|     |                  | •                                               |               |           |      |

|-----|------------------|-------------------------------------------------|---------------|-----------|------|

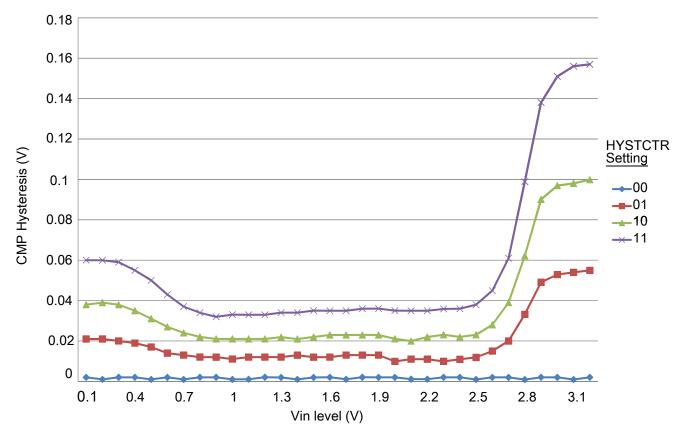

| Num | Symbol           | Description                                     | Min.          | Max.      | Unit |

|     |                  | Operating voltage                               | 1.71          | 3.6       | V    |

|     |                  | Card input clock                                |               |           |      |

| SD1 | fpp              | Clock frequency (low speed)                     | 0             | 400       | kHz  |

|     | fpp              | Clock frequency (SD\SDIO full speed\high speed) | 0             | 25\50     | MHz  |

|     | fpp              | Clock frequency (MMC full speed\high speed)     | 0             | 20\50     | MHz  |

|     | f <sub>OD</sub>  | Clock frequency (identification mode)           | 0             | 400       | kHz  |

| SD2 | t <sub>WL</sub>  | Clock low time                                  | 7             | _         | ns   |

| SD3 | t <sub>WH</sub>  | Clock high time                                 | 7             | —         | ns   |

| SD4 | t <sub>TLH</sub> | Clock rise time                                 | _             | 3         | ns   |

| SD5 | t <sub>THL</sub> | Clock fall time                                 | _             | 3         | ns   |

|     |                  | SDHC output / card inputs SDHC_CMD, SDHC_DAT    | (reference to | SDHC_CLK) |      |

| SD6 | t <sub>OD</sub>  | SDHC output delay (output valid)                | -5            | 6.5       | ns   |

|     |                  | SDHC input / card inputs SDHC_CMD, SDHC_DAT (   | reference to  | SDHC_CLK) |      |

| SD7 | t <sub>ISU</sub> | SDHC input setup time                           | 5             | —         | ns   |

| SD8 | t <sub>IH</sub>  | SDHC input hold time                            | 1.3           | —         | ns   |

|     |                  |                                                 |               | -         |      |

# Table 51. SDHC switching specifications over the full operating voltage range

Figure 38. SDHC timing

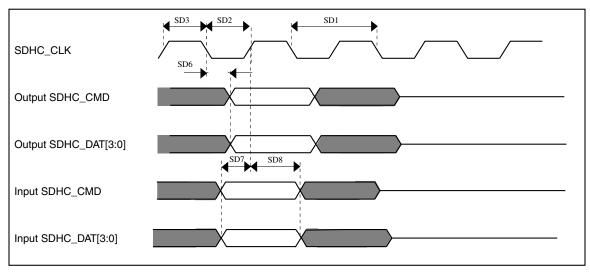

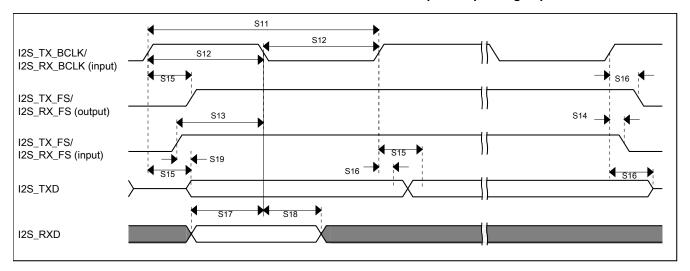

# 6.8.12 I2S/SAI switching specifications

This section provides the AC timing for the I2S/SAI module in master mode (clocks are driven) and slave mode (clocks are input). All timing is given for noninverted serial clock polarity (TCR2[BCP] is 0, RCR2[BCP] is 0) and a noninverted frame sync (TCR4[FSP]

Peripheral operating requirements and behaviors

Figure 40. I2S/SAI timing — slave modes

# 6.8.12.2 Normal Run, Wait and Stop mode performance over the full operating voltage range

This section provides the operating performance over the full operating voltage for the device in Normal Run, Wait and Stop modes.

Table 54.

I2S/SAI master mode timing in Normal Run, Wait and Stop modes (full voltage range)

| Num. | Characteristic                                                    | Min. | Max. | Unit        |

|------|-------------------------------------------------------------------|------|------|-------------|

|      | Operating voltage                                                 | 1.71 | 3.6  | V           |

| S1   | I2S_MCLK cycle time                                               | 40   | —    | ns          |

| S2   | I2S_MCLK pulse width high/low                                     | 45%  | 55%  | MCLK period |

| S3   | I2S_TX_BCLK/I2S_RX_BCLK cycle time (output)                       | 80   | —    | ns          |

| S4   | I2S_TX_BCLK/I2S_RX_BCLK pulse width high/low                      | 45%  | 55%  | BCLK period |

| S5   | I2S_TX_BCLK/I2S_RX_BCLK to I2S_TX_FS/<br>I2S_RX_FS output valid   | -    | 15   | ns          |

| S6   | I2S_TX_BCLK/I2S_RX_BCLK to I2S_TX_FS/<br>I2S_RX_FS output invalid | -1.0 | -    | ns          |

| S7   | I2S_TX_BCLK to I2S_TXD valid                                      | _    | 15   | ns          |

| S8   | I2S_TX_BCLK to I2S_TXD invalid                                    | 0    | —    | ns          |

| S9   | I2S_RXD/I2S_RX_FS input setup before<br>I2S_RX_BCLK               | 20.5 | —    | ns          |

| S10  | I2S_RXD/I2S_RX_FS input hold after I2S_RX_BCLK                    | 0    | —    | ns          |

Peripheral operating requirements and behaviors

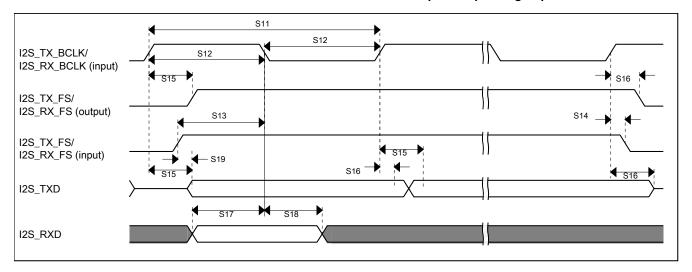

Figure 42. I2S/SAI timing — slave modes

# 6.8.12.3 VLPR, VLPW, and VLPS mode performance over the full operating voltage range

This section provides the operating performance over the full operating voltage for the device in VLPR, VLPW, and VLPS modes.

Table 56.

I2S/SAI master mode timing in VLPR, VLPW, and VLPS modes (full voltage range)

| Num. | Characteristic                                                    | Min. | Max. | Unit        |  |  |

|------|-------------------------------------------------------------------|------|------|-------------|--|--|

|      | Operating voltage                                                 | 1.71 | 3.6  | V           |  |  |

| S1   | I2S_MCLK cycle time                                               | 62.5 | —    | ns          |  |  |

| S2   | I2S_MCLK pulse width high/low                                     | 45%  | 55%  | MCLK period |  |  |

| S3   | I2S_TX_BCLK/I2S_RX_BCLK cycle time (output)                       | 250  | —    | ns          |  |  |

| S4   | I2S_TX_BCLK/I2S_RX_BCLK pulse width high/low                      | 45%  | 55%  | BCLK period |  |  |

| S5   | I2S_TX_BCLK/I2S_RX_BCLK to I2S_TX_FS/<br>I2S_RX_FS output valid   | -    | 45   | ns          |  |  |

| S6   | I2S_TX_BCLK/I2S_RX_BCLK to I2S_TX_FS/<br>I2S_RX_FS output invalid | 0    | -    | ns          |  |  |

| S7   | I2S_TX_BCLK to I2S_TXD valid                                      | -    | 45   | ns          |  |  |

| S8   | I2S_TX_BCLK to I2S_TXD invalid                                    | -1.6 | —    | ns          |  |  |

| S9   | I2S_RXD/I2S_RX_FS input setup before<br>I2S_RX_BCLK               | 45   | —    | ns          |  |  |

| S10  | I2S_RXD/I2S_RX_FS input hold after I2S_RX_BCLK                    | 0    | —    | ns          |  |  |

Peripheral operating requirements and behaviors

# 6.9 Human-machine interfaces (HMI)

# 6.9.1 TSI electrical specifications

Table 58. TSI electrical specifications

| Symbol               | Description                                                                      | Min.  | Тур.   | Max.  | Unit     | Notes            |

|----------------------|----------------------------------------------------------------------------------|-------|--------|-------|----------|------------------|

| V <sub>DDTSI</sub>   | Operating voltage                                                                | 1.71  |        | 3.6   | V        |                  |

| C <sub>ELE</sub>     | Target electrode capacitance range                                               | 1     | 20     | 500   | pF       | 1                |

| f <sub>REFmax</sub>  | Reference oscillator frequency                                                   | _     | 8      | 15    | MHz      | <sup>2</sup> , 3 |

| f <sub>ELEmax</sub>  | Electrode oscillator frequency                                                   | _     | 1      | 1.8   | MHz      | <sup>2</sup> , 4 |

| C <sub>REF</sub>     | Internal reference capacitor                                                     |       | 1      | _     | pF       |                  |

| V <sub>DELTA</sub>   | Oscillator delta voltage                                                         | _     | 600    | _     | mV       | <sup>2</sup> , 5 |

| I <sub>REF</sub>     | Reference oscillator current source base current<br>• 2 μA setting (REFCHRG = 0) | _     | 2      | 3     | μA       | 2, 6             |

|                      | <ul> <li>32 µA setting (REFCHRG = 15)</li> </ul>                                 | —     | 36     | 50    |          |                  |

| I <sub>ELE</sub>     | Electrode oscillator current source base current<br>• 2 µA setting (EXTCHRG = 0) | _     | 2      | 3     | μA       | 2, 7             |

|                      | <ul> <li>32 µA setting (EXTCHRG = 15)</li> </ul>                                 | —     | 36     | 50    |          |                  |

| Pres5                | Electrode capacitance measurement precision                                      | _     | 8.3333 | 38400 | fF/count | 8                |

| Pres20               | Electrode capacitance measurement precision                                      |       | 8.3333 | 38400 | fF/count | 9                |

| Pres100              | Electrode capacitance measurement precision                                      | _     | 8.3333 | 38400 | fF/count | 10               |

| MaxSens              | Maximum sensitivity                                                              | 0.008 | 1.46   | _     | fF/count | 11               |

| Res                  | Resolution                                                                       |       |        | 16    | bits     |                  |

| T <sub>Con20</sub>   | Response time @ 20 pF                                                            | 8     | 15     | 25    | μs       | 12               |

| I <sub>TSI_RUN</sub> | V Current added in run mode - 55 -                                               |       |        | μA    |          |                  |

| I <sub>TSI_LP</sub>  | Low power mode current adder                                                     |       | 1.3    | 2.5   | μA       | 13               |

#### onnensions

- 1. The TSI module is functional with capacitance values outside this range. However, optimal performance is not guaranteed.

- 2. Fixed external capacitance of 20 pF.

- 3. REFCHRG = 2, EXTCHRG=0.

- 4. REFCHRG = 0, EXTCHRG = 10.

- 5.  $V_{DD} = 3.0 V.$

- 6. The programmable current source value is generated by multiplying the SCANC[REFCHRG] value and the base current.

- 7. The programmable current source value is generated by multiplying the SCANC[EXTCHRG] value and the base current.

- 8. Measured with a 5 pF electrode, reference oscillator frequency of 10 MHz, PS = 128, NSCN = 8; lext = 16.

- 9. Measured with a 20 pF electrode, reference oscillator frequency of 10 MHz, PS = 128, NSCN = 2; lext = 16.

- 10. Measured with a 20 pF electrode, reference oscillator frequency of 10 MHz, PS = 16, NSCN = 3; lext = 16.

- 11. Sensitivity defines the minimum capacitance change when a single count from the TSI module changes. Sensitivity depends on the configuration used. The documented values are provided as examples calculated for a specific configuration of operating conditions using the following equation: (C<sub>ref</sub> \* I<sub>ext</sub>)/( I<sub>ref</sub> \* PS \* NSCN)

The typical value is calculated with the following configuration:

I<sub>ext</sub> = 6 μA (EXTCHRG = 2), PS = 128, NSCN = 2, I<sub>ref</sub> = 16 μA (REFCHRG = 7), C<sub>ref</sub> = 1.0 pF

The minimum value is calculated with the following configuration:

I<sub>ext</sub> = 2 μA (EXTCHRG = 0), PS = 128, NSCN = 32, I<sub>ref</sub> = 32 μA (REFCHRG = 15), C<sub>ref</sub> = 0.5 pF

The highest possible sensitivity is the minimum value because it represents the smallest possible capacitance that can be measured by a single count.

- 12. Time to do one complete measurement of the electrode. Sensitivity resolution of 0.0133 pF, PS = 0, NSCN = 0, 1 electrode, EXTCHRG = 7.

- 13. REFCHRG=0, EXTCHRG=4, PS=7, NSCN=0F, LPSCNITV=F, LPO is selected (1 kHz), and fixed external capacitance of 20 pF. Data is captured with an average of 7 periods window.

# 7 Dimensions

## 7.1 Obtaining package dimensions

Package dimensions are provided in package drawings.

To find a package drawing, go to freescale.com and perform a keyword search for the drawing's document number:

| If you want the drawing for this package | Then use this document number |  |  |  |

|------------------------------------------|-------------------------------|--|--|--|

| 256-pin MAPBGA                           | 98ASA00346D                   |  |  |  |

# 8 Pinout

## 8.1 Pins with active pull control after reset

The following pins are actively pulled up or down after reset:

| Rev. No. | Date    | Substantial Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3        | 3/2012  | Initial public release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 4        | 10/2012 | Replaced TBDs throughout.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 5        | 10/2013 | Changes for 4N96B mask set:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|          |         | <ul> <li>Min VDD operating requirement specification updated to support operation down to<br/>1.71V.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|          |         | New specifications:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|          |         | <ul> <li>Updated Vdd_ddr min specification.</li> <li>Added Vodpu specification.</li> <li>Removed loz, loz_ddr, and loz_tamper Hi-Z leakage specifications. They have been replaced by new lina, lind, and Zind specifications.</li> </ul>                                                                                                                                                                                                                                                                                                                               |

|          |         | <ul> <li>Fpll_ref_acc specification has been added.</li> <li>I<sup>2</sup>C module was previously covered by the general switching specifications. To provide more detail on I<sup>2</sup>C operation a dedicated Inter-Integrated Circuit Interface (I<sup>2</sup>C) timing section has been added.</li> </ul>                                                                                                                                                                                                                                                         |

|          |         | Modified specifications:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|          |         | <ul> <li>Vref_ddr max spec has been updated.</li> <li>Tpor spec has been split into two specifications based on VDD slew rate.</li> <li>Trd1allx and Trd1alln max have been updated.</li> <li>16-bit ADC Temp sensor slope and Temp sensor voltage (Vtemp25) have been modified. The typical values that were listed previously have been updated, and min and max specifications have been added.</li> </ul>                                                                                                                                                           |

|          |         | Corrections:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|          |         | <ul> <li>Some versions of the datasheets listed incorrect clock mode information in the<br/>"Diagram: Typical IDD_RUN operating behavior section." These errors have been<br/>corrected.</li> <li>Fintf_ft specification was previously shown as a max value. It has been corrected to be<br/>shown as a typical value as originally intended.</li> <li>Corrected DDR write and read timing diagrams to show the correct location of the Tcmv<br/>specification.</li> <li>SDHC peripheral 50MHz high speed mode options were left out of the last datasheet.</li> </ul> |

|          |         | These have been added to the SDHC specifications section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 6        | 09/2015 | <ul> <li>Updated Power Sequencing section</li> <li>Added footnote to ambient temperature specification of Thermal Operating requirements</li> <li>Updated the data and DQS waveforms in DDR read timing diagram</li> <li>Removed "USB HS/LS/FS on-the-go controller with on-chip high speed transceiver" from features section</li> <li>Updated Terminology and guidelines section</li> <li>Updated the footnotes and the values of Power consumption operating behaviors table</li> <li>Added Notes in USB electrical specification section</li> </ul>                 |

## Table 60. Revision History