Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                             |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 25MHz                                                           |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT              |

| Number of I/O              | 32                                                              |

| Program Memory Size        | 16KB (16K × 8)                                                  |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 1.25K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.8V ~ 3.6V                                                     |

| Data Converters            | A/D 8x10b                                                       |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 64-TQFP                                                         |

| Supplier Device Package    | 64-TQFP (10x10)                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f018-gqr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|     | Figure 6.3. CPT0CN: Comparator 0 Control Register      | 39   |

|-----|--------------------------------------------------------|------|

|     | Figure 6.4. CPT1CN: Comparator 1 Control Register      | 40   |

|     | Table 6.1. Comparator Electrical Characteristics       | 41   |

| 7.  | VOLTAGE REFERENCE                                      | . 42 |

|     | Figure 7.1. Voltage Reference Functional Block Diagram |      |

|     | Figure 7.2. REFOCN: Reference Control Register         |      |

|     | Table 7.1. Reference Electrical Characteristics        |      |

| 8.  | CIP-51 CPU                                             |      |

| 0.  | Figure 8.1. CIP-51 Block Diagram.                      |      |

|     | 8.1. INSTRUCTION SET                                   |      |

|     | Table 8.1. CIP-51 Instruction Set Summary              |      |

|     | 8.2. MEMORY ORGANIZATION                               |      |

|     | Figure 8.2. Memory Map                                 |      |

|     | 8.3. SPECIAL FUNCTION REGISTERS.                       |      |

|     | Table 8.2. Special Function Register Memory Map        |      |

|     | Table 8.3. Special Function Registers                  |      |

|     | Figure 8.3. SP: Stack Pointer                          |      |

|     | Figure 8.4. DPL: Data Pointer Low Byte                 |      |

|     | Figure 8.5. DPH: Data Pointer High Byte                |      |

|     | Figure 8.6. PSW: Program Status Word                   |      |

|     | Figure 8.7. ACC: Accumulator                           |      |

|     | Figure 8.8. B: B Register                              |      |

|     | 8.4. INTERRUPT HANDLER                                 |      |

|     | Table 8.4. Interrupt Summary                           |      |

|     | Figure 8.9. IE: Interrupt Enable                       | 61   |

|     | Figure 8.10. IP: Interrupt Priority                    |      |

|     | Figure 8.11. EIE1: Extended Interrupt Enable 1         | 63   |

|     | Figure 8.12. EIE2: Extended Interrupt Enable 2         | 64   |

|     | Figure 8.13. EIP1: Extended Interrupt Priority 1       | 65   |

|     | Figure 8.14. EIP2: Extended Interrupt Priority 2       |      |

|     | 8.5. Power Management Modes                            | 67   |

|     | Figure 8.15. PCON: Power Control Register              | 68   |

| 9.  | FLASH MEMORY                                           | . 69 |

|     | 9.1. Programming The Flash Memory                      | 69   |

|     | Table 9.1. FLASH Memory Electrical Characteristics     | 69   |

|     | 9.2. Non-volatile Data Storage                         |      |

|     | 9.3. Security Options                                  |      |

|     | Figure 9.1. PSCTL: Program Store RW Control            |      |

|     | Figure 9.2. Flash Program Memory Security Bytes        |      |

|     | Figure 9.3. FLACL: Flash Access Limit                  |      |

|     | Figure 9.4. FLSCL: Flash Memory Timing Prescaler       |      |

| 10. | EXTERNAL RAM                                           | . 74 |

|     | Figure 10.1. EMI0CN: External Memory Interface Control | 74   |

| 11. | RESET SOURCES                                          |      |

|     | Figure 11.1. Reset Sources Diagram                     | 75   |

|     | 11.1. Power-on Reset                                   | 76   |

|     | 11.2. Software Forced Reset                            |      |

|     | Figure 11.2. VDD Monitor Timing Diagram                |      |

|     | 11.3. Power-fail Reset                                 |      |

|     | 11.4. External Reset                                   |      |

|     | 11.5. Missing Clock Detector Reset                     |      |

|     | 11.6. Comparator 0 Reset                               |      |

|     | 11.7. External CNVSTR Pin Reset                        |      |

|     | 11.8. Watchdog Timer Reset                             | 77   |

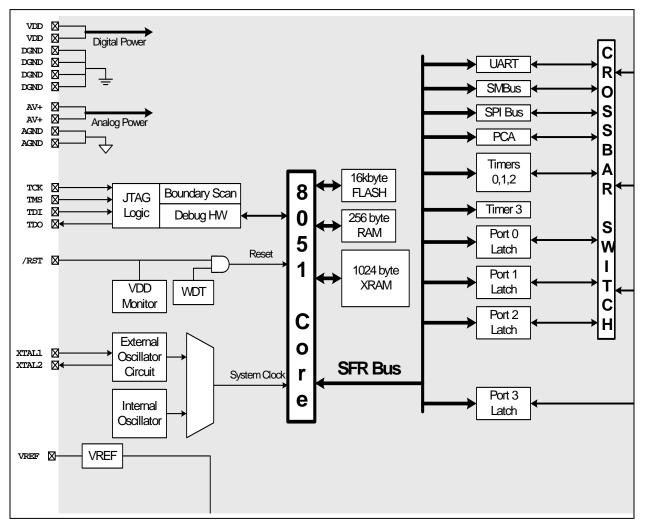

Figure 1.2. C8051F019 Block Diagram

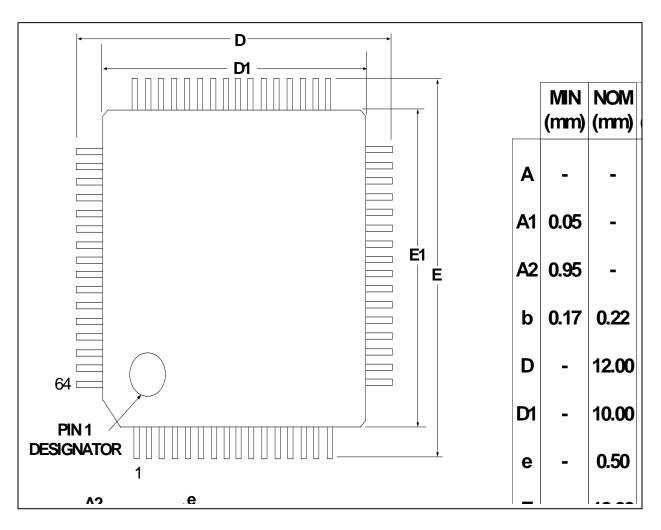

Figure 4.2. TQFP-64 Package Drawing

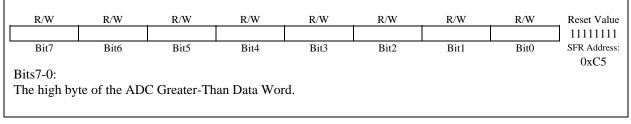

### 5.3. ADC Programmable Window Detector

The ADC programmable window detector is very useful in many applications. It continuously compares the ADC output to user-programmed limits and notifies the system when an out-of-band condition is detected. This is especially effective in an interrupt-driven system, saving code space and CPU bandwidth while delivering faster system response times. The window detector interrupt flag (ADWINT in ADCOCN) can also be used in polled mode. The high and low bytes of the reference words are loaded into the ADC Greater-Than and ADC Less-Than registers (ADC0GTH, ADC0GTL, ADC0LTH, and ADC0LTL). Figure 5.14 and Figure 5.15 show example comparisons for reference. Notice that the window detector flag can be asserted when the measured data is inside or outside the user-programmed limits, depending on the programming of the ADC0GTX and ADC0LTX registers.

#### Figure 5.10. ADC0GTH: ADC Greater-Than Data High Byte Register

#### Figure 5.11. ADC0GTL: ADC Greater-Than Data Low Byte Register

| R/W         | R/W                           | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | Reset Value                      |

|-------------|-------------------------------|------|------|------|------|------|------|----------------------------------|

| Bit7        | Bit6                          | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | 11111111<br>SFR Address:<br>0xC4 |

| Definition: | te of the ADC<br>er-Than Data |      |      |      |      |      |      |                                  |

| Figure 5.12. ADC0LTH: ADC Less-Than Data High Byte Register |

|-------------------------------------------------------------|

|-------------------------------------------------------------|

| R/W                             | R/W                   | R/W                 | R/W                | R/W  | R/W  | R/W  | R/W  | Reset Value<br>00000000 |

|---------------------------------|-----------------------|---------------------|--------------------|------|------|------|------|-------------------------|

| Bit7<br>Bits7-0:<br>The high by | Bit6<br>wte of the AD | Bit5<br>C Less-Than | Bit4<br>Data Word. | Bit3 | Bit2 | Bit1 | Bit0 | SFR Address:<br>0xC7    |

#### Figure 5.13. ADC0LTL: ADC Less-Than Data Low Byte Register

|              | •              |              |             |            |      | • •  |      |              |

|--------------|----------------|--------------|-------------|------------|------|------|------|--------------|

| R/W          | R/W            | R/W          | R/W         | R/W        | R/W  | R/W  | R/W  | Reset Value  |

|              |                |              |             |            |      |      |      | 00000000     |

| Bit7         | Bit6           | Bit5         | Bit4        | Bit3       | Bit2 | Bit1 | Bit0 | SFR Address: |

|              |                |              |             |            |      |      |      | 0xC6         |

|              |                |              |             |            |      |      |      |              |

| Bits7-0:     |                |              |             |            |      |      |      |              |

| These bits a | are the low by | te of the AD | C Less-Than | Data Word. |      |      |      |              |

| Definition:  |                |              |             |            |      |      |      |              |

| ADC Less-    | Than Data Wo   | ord = ADC0   | LTH:ADC0I   | TL         |      |      |      |              |

|              |                |              |             |            |      |      |      |              |

|              |                |              |             |            |      |      |      |              |

| Figure 8.7.   | <b>ACC: Accumulator</b> |

|---------------|-------------------------|

| I Igui C 0.7. | noon neculiation        |

| R/W   | R/W         | R/W   | R/W             | R/W           | R/W   | R/W   | R/W               | Reset Value  |

|-------|-------------|-------|-----------------|---------------|-------|-------|-------------------|--------------|

| ACC.7 | ACC.6       | ACC.5 | ACC.4           | ACC.3         | ACC.2 | ACC.1 | ACC.0             | 00000000     |

| Bit7  | Bit6        | Bit5  | Bit4            | Bit3          | Bit2  | Bit1  | Bit0              | SFR Address: |

|       |             |       |                 |               |       |       | (bit addressable) | 0xE0         |

|       | ACC: Accumu |       | lator for arith | nmetic operat | ions. |       |                   |              |

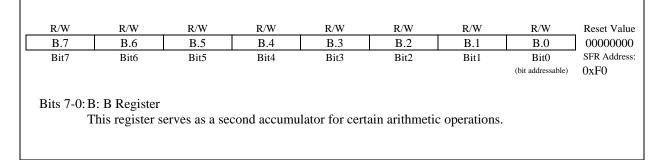

Figure 8.8. B: B Register

### Figure 8.10. IP: Interrupt Priority

| R/W     | R/W                               | R/W            | R/W            | R/W        | R/W        | R/W  | R/W               | Reset Value |

|---------|-----------------------------------|----------------|----------------|------------|------------|------|-------------------|-------------|

| -       | -                                 | PT2            | PS             | PT1        | PX1        | PT0  | PX0               | 0000000     |

| Bit7    | Bit6                              | Bit5           | Bit4           | Bit3       | Bit2       | Bit1 | Bit0              | SFR Address |

|         |                                   |                |                |            |            |      | (bit addressable) | 0xB8        |

| Bits7-6 | : UNUSED. Re                      | ad = 11b, W    | rite = don't o | care.      |            |      |                   |             |

|         |                                   |                |                |            |            |      |                   |             |

| Bit5:   | PT2 Timer 2 I<br>This bit sets th |                |                | intomunto  |            |      |                   |             |

|         | 0: Timer 2 int                    |                |                |            |            |      |                   |             |

|         | 1: Timer 2 int                    |                |                |            |            |      |                   |             |

|         |                                   | r              | 81             | ) · · · ·  |            |      |                   |             |

| Bit4:   | PS: Serial Port                   |                |                |            |            |      |                   |             |

|         | This bit sets th<br>0: UART inte  |                |                |            | nterrupts. |      |                   |             |

|         | 1: UART inte                      |                |                |            |            |      |                   |             |

|         | 1. Orner inte                     | inapis set to  | ingii priority |            |            |      |                   |             |

| Bit3:   | PT1: Timer 1                      |                |                |            |            |      |                   |             |

|         | This bit sets th                  |                |                |            |            |      |                   |             |

|         | 0: Timer 1 int<br>1: Timer 1 int  |                |                |            |            |      |                   |             |

|         | 1: Timer I int                    | errupts set to | nign priorit   | y level.   |            |      |                   |             |

| Bit2:   | PX1: External                     |                |                |            |            |      |                   |             |

|         | This bit sets th                  |                |                |            | nterrupts. |      |                   |             |

|         | 0: External In                    |                |                |            |            |      |                   |             |

|         | 1: External In                    | terrupt 1 set  | to high prior  | ity level. |            |      |                   |             |

| Bit1:   | PT0: Timer 0                      | Interrupt Prie | ority Control  |            |            |      |                   |             |

|         | This bit sets th                  |                |                |            |            |      |                   |             |

|         | 0: Timer 0 int                    | 1              | 1 .            |            |            |      |                   |             |

|         | 1: Timer 0 int                    | errupt set to  | high priority  | level.     |            |      |                   |             |

| Bit0:   | PX0: External                     | Interrupt 0 I  | Priority Cont  | rol.       |            |      |                   |             |

|         | This bit sets th                  |                |                |            | nterrupts. |      |                   |             |

|         | 0: External In                    | -              | -              | •          |            |      |                   |             |

|         | 1: External In                    | terrupt 0 set  | to high prior  | ity level. |            |      |                   |             |

|         |                                   |                |                |            |            |      |                   |             |

|         |                                   |                |                |            |            |      |                   |             |

|         |                                   |                |                |            |            |      |                   |             |

#### 8.5. Power Management Modes

The CIP-51 core has two software programmable power management modes: Idle and Stop. Idle mode halts the CPU while leaving the external peripherals and internal clocks active. In Stop mode, the CPU is halted, all interrupts and timers (except the Missing Clock Detector) are inactive, and the system clock is stopped. Since clocks are running in Idle mode, power consumption is dependent upon the system clock frequency and the number of peripherals left in active mode before entering Idle. Stop mode consumes the least power. Figure 8.15 describes the Power Control Register (PCON) used to control the CIP-51's power management modes.

Although the CIP-51 has Idle and Stop modes built in (as with any standard 8051 architecture), power management of the entire MCU is better accomplished by enabling/disabling individual peripherals as needed. Each analog peripheral can be disabled when not in use and put into low power mode. Digital peripherals, such as timers or serial buses, draw little power whenever they are not in use. Turning off the oscillator saves even more power, but requires a reset to restart the MCU.

#### 8.5.1. Idle Mode

Setting the Idle Mode Select bit (PCON.0) causes the CIP-51 to halt the CPU and enter Idle mode as soon as the instruction that sets the bit completes. All internal registers and memory maintain their original data. All analog and digital peripherals can remain active during Idle mode.

Idle mode is terminated when an enabled interrupt or /RST is asserted. The assertion of an enabled interrupt will cause the Idle Mode Selection bit (PCON.0) to be cleared and the CPU will resume operation. The pending interrupt will be serviced and the next instruction to be executed after the return from interrupt (RETI) will be the instruction immediately following the one that set the Idle Mode Select bit. If Idle mode is terminated by an internal or external reset, the CIP-51 performs a normal reset sequence and begins program execution at address 0x0000.

Note: If the instruction following the write of the IDLE bit is a single-byte instruction and an interrupt occurs during the execution phase of the instruction that sets the IDLE bit, the CPU may not wake from Idle mode when a future interrupt occurs. Any instructions that set the IDLE bit should be followed by an instruction that has 2 or more opcode bytes, for example:

| // in 'C':<br>PCON  = 0x01;<br>PCON = PCON;        | <pre>// set IDLE bit // followed by a 3-cycle dummy instruction</pre> |

|----------------------------------------------------|-----------------------------------------------------------------------|

| ; in assembly:<br>ORL PCON, #01h<br>MOV PCON, PCON | ; set IDLE bit<br>; followed by a 3-cycle dummy instruction           |

If enabled, the WDT will eventually cause an internal watchdog reset and thereby terminate the Idle mode. This feature protects the system from an unintended permanent shutdown in the event of an inadvertent write to the PCON register. If this behavior is not desired, the WDT may be disabled by software prior to entering the Idle mode if the WDT was initially configured to allow this operation. This provides the opportunity for additional power savings, allowing the system to remain in the Idle mode indefinitely, waiting for an external stimulus to wake up the system. Refer to Section 11.8 Watchdog Timer for more information on the use and configuration of the WDT.

#### 8.5.2. Stop Mode

Setting the Stop Mode Select bit (PCON.1) causes the CIP-51 to enter Stop mode as soon as the instruction that sets the bit completes. In Stop mode, the CPU and oscillators are stopped, effectively shutting down all digital peripherals. Each analog peripheral must be shut down individually prior to entering Stop Mode. Stop mode can only be terminated by an internal or external reset. On reset, the CIP-51 performs the normal reset sequence and begins program execution at address 0x0000.

| R/W    | R/W            | R/W            | R/W           | R/W  | R/W   | R/W  | R/W    | Reset Value  |

|--------|----------------|----------------|---------------|------|-------|------|--------|--------------|

| SYSCKE | T2EXE          | T2E            | INT1E         | T1E  | INT0E | T0E  | CP10EN | 00000000     |

| Bit7   | Bit6           | Bit5           | Bit4          | Bit3 | Bit2  | Bit1 | Bit0   | SFR Address: |

|        |                |                |               |      |       |      |        | 0xE2         |

|        |                |                |               |      |       |      |        |              |

| Bit7:  | SYSCKE: SY     | SCLK Outpu     | it Enable Bit |      |       |      |        |              |

|        | 0: SYSCLK u    | ınavailable a  | t Port pin.   |      |       |      |        |              |

|        | 1: SYSCLK of   | output routed  | to Port Pin.  |      |       |      |        |              |

| Bit6:  | T2EXE: T2EX    | K Enable Bit   |               |      |       |      |        |              |

|        | 0: T2EX unav   | vailable at Po | ort pin.      |      |       |      |        |              |

|        | 1: T2EX rout   | ed to Port Pi  | n.            |      |       |      |        |              |

| Bit5:  | T2E: T2 Enab   | le Bit         |               |      |       |      |        |              |

|        | 0: T2 unavaila | able at Port p | oin.          |      |       |      |        |              |

|        | 1: T2 routed t | o Port Pin.    |               |      |       |      |        |              |

| Bit4:  | INT1E: /INT1   |                |               |      |       |      |        |              |

|        | 0: /INT1 unav  |                | -             |      |       |      |        |              |

|        | 1: /INT1 rout  |                | n.            |      |       |      |        |              |

| Bit3:  | T1E: T1 Enab   |                |               |      |       |      |        |              |

|        | 0: T1 unavail  | -              | oin.          |      |       |      |        |              |

|        | 1: T1 routed t |                |               |      |       |      |        |              |

| Bit2:  | INTOE: /INTO   |                |               |      |       |      |        |              |

|        | 0: /INTO unav  |                | 1             |      |       |      |        |              |

|        | 1: /INT0 rout  |                | n.            |      |       |      |        |              |

| Bit1:  | T0E: T0 Enab   |                |               |      |       |      |        |              |

|        | 0: T0 unavail  | -              | oin.          |      |       |      |        |              |

|        | 1: T0 routed t |                |               |      |       |      |        |              |

| Bit0:  | CP1OEN: Con    |                |               | Bit  |       |      |        |              |

|        | 0: CP1 unava   |                | pin.          |      |       |      |        |              |

|        | 1: CP1 routed  | to Port Pin.   |               |      |       |      |        |              |

|        |                |                |               |      |       |      |        |              |

|        |                |                |               |      |       |      |        |              |

### Figure 13.4. XBR1: Port I/O CrossBar Register 1

#### 14.6.1. Control Register

The SMBus Control register SMB0CN is used to configure and control the SMBus interface. All of the bits in the register can be read or written by software. Two of the control bits are also affected by the SMBus hardware. The Serial Interrupt flag (SI, SMB0CN.3) is set to logic 1 by the hardware when a valid serial interrupt condition occurs. It can only be cleared by software. The Stop flag (STO, SMB0CN.4) is cleared to logic 0 by hardware when a STOP condition is present on the bus.

Setting the ENSMB flag to logic 1 enables the SMBus interface. Clearing the ENSMB flag to logic 0 disables the SMBus interface and removes it from the bus. Momentarily clearing the ENSMB flag and then resetting it to logic 1 will reset a SMBus communication. However, ENSMB should not be used to temporarily remove a device from the bus since the bus state information will be lost. Instead, the Assert Acknowledge (AA) flag should be used to temporarily remove the device from the bus (see description of AA flag below).

Setting the Start flag (STA, SMB0CN.5) to logic 1 will put the SMBus in a master mode. If the bus is free, the SMBus hardware will generate a START condition. If the bus is not free, the SMBus hardware waits for a STOP condition to free the bus and then generates a START condition after a 5 $\mu$ s delay per the SMB0CR value. (In accordance with the SMBus protocol, the SMBus interface also considers the bus free if the bus is idle for 50 $\mu$ s and no STOP condition was recognized.) If STA is set to logic 1 while the SMBus is in master mode and one or more bytes have been transferred, a repeated START condition will be generated. To ensure proper operation, the STO flag should be explicitly cleared before setting STA to a logic 1.

When the Stop flag (STO, SMB0CN.4) is set to logic 1 while the SMBus interface is in master mode, the hardware generates a STOP condition on the SMBus. In a slave mode, the STO flag may be used to recover from an error condition. In this case, a STOP condition is not generated on the SMBus, but the SMBus hardware behaves as if a STOP condition has been received and enters the "not addressed" slave receiver mode. The SMBus hardware automatically clears the STO flag to logic 0 when a STOP condition is detected on the bus.

The Serial Interrupt flag (SI, SMB0CN.3) is set to logic 1 by hardware when the SMBus interface enters one of 27 possible states. If interrupts are enabled for the SMBus interface, an interrupt request is generated when the SI flag is set. The SI flag must be cleared by software. While SI is set to logic 1, the clock-low period of the serial clock will be stretched and the serial transfer is suspended.

The Assert Acknowledge flag (AA, SMB0CN.2) is used to set the level of the SDA line during the acknowledge clock cycle on the SCL line. Setting the AA flag to logic 1 will cause an ACKNOWLEDGE (low level on SDA) to be sent during the acknowledge cycle if the device has been addressed. Setting the AA flag to logic 0 will cause a NOT ACKNOWLEDGE (high level on SDA) to be sent during acknowledge cycle. After the transmission of a byte in slave mode, the slave can be temporarily removed from the bus by clearing the AA flag. The slave's own address and general call address will be ignored. To resume operation on the bus, the AA flag must be reset to logic 1 to allow the slave's address to be recognized.

Setting the SMBus Free Timer Enable bit (FTE, SMB0CN.1) to logic 1 enables the SMBus Free Timeout feature. If SCL and SDA remain high for the SMBus Free Timeout given in the SMBus Clock Rate Register (Figure 14.5), the bus will be considered free and a Start will be generated if pending. The bus free period should be greater than 50µs.

Setting the SMBus timeout enable bit (TOE, SMB0CN.0) to logic 1 enables Timer 3 to count up when the SCL line is low and Timer 3 is enabled. If Timer 3 overflows, a Timer 3 interrupt will be generated, which will alert the CPU that a SMBus SCL low timeout has occurred.

### 14.6.2. Clock Rate Register

| R/W  | R/W                                                                                                                   | R/W                                                                                                       | R/W                                                                                                            | R/W                                                                                                 | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R/W                                                                        | R/W                                                       | Reset Valu<br>00000000 |

|------|-----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|-----------------------------------------------------------|------------------------|

| Bit7 | Bit6                                                                                                                  | Bit5                                                                                                      | Bit4                                                                                                           | Bit3                                                                                                | Bit2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Bit1                                                                       | Bit0                                                      | SFR Addres<br>0xCF     |

|      | SMB0CR.[7:0<br>The SMB0CR<br>mode. The 8<br>The timer cour<br>The SMB0CR<br>unsigned 8-bit<br>Hz:<br>The resulting \$ | Clock Rate :<br>-bit word sto<br>nts up, and w<br>setting shou<br>value in regi<br>SMB0CR<br>SCL signal h | register cont<br>red in the S<br>hen it rolls c<br>ld be bounde<br>ister SMB0C<br>< ((288 - 0.8<br>igh and low | rols the frequ<br>MB0CR Reg<br>over to 0x00,<br>ed by the follo<br>R, and <i>SYSC</i><br>35 * SYSCL | (ister preload<br>the SCL loginary constraints) (in the SCL loginary constra | Is a dedicated<br>ic state toggle<br>on, where <i>SN</i><br>stem clock fre | d 8-bit timer<br>es.<br><i>MBOCR</i> is the<br>equency in | r                      |

|      | Using the sam<br>the following                                                                                        | ne value of S<br>equation:                                                                                | MB0CR fro                                                                                                      | OCR) / SYSCA<br>m above, the<br>6 – SMBOCR                                                          | e Bus Free T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -                                                                          | od is given i                                             | n                      |

#### Figure 14.5. SMB0CR: SMBus Clock Rate Register

### **15.1.** Signal Descriptions

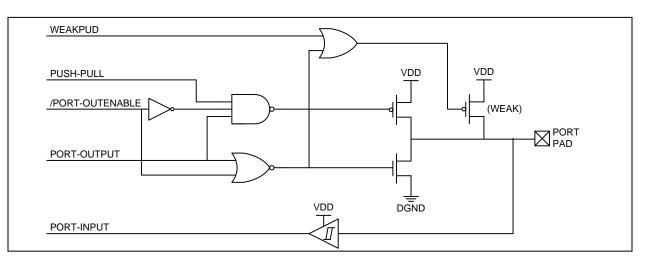

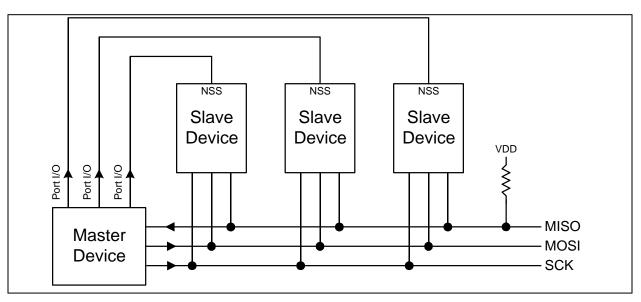

The four signals used by the SPI (MOSI, MISO, SCK, NSS) are described below.

#### 15.1.1. Master Out, Slave In

The master-out, slave-in (MOSI) signal is an output from a master device and an input to slave devices. It is used to serially transfer data from the master to the slave. Data is transferred most-significant bit first.

#### 15.1.2. Master In, Slave Out

The master-in, slave-out (MISO) signal is an output from a slave device and an input to the master device. It is used to serially transfer data from the slave to the master. Data is transferred most-significant bit first. A SPI slave places the MISO pin in a high-impedance state when the slave is not selected.

#### 15.1.3. Serial Clock

The serial clock (SCK) signal is an output from the master device and an input to slave devices. It is used to synchronize the transfer of data between the master and slave on the MOSI and MISO lines.

#### 15.1.4. Slave Select

The slave select (NSS) signal is an input used to select the SPI module when in slave mode by a master, or to disable the SPI module when in master mode. When in slave mode, it is pulled low to initiate a data transfer and remains low for the duration of the transfer.

#### 15.4. SPI Special Function Registers

The SPI is accessed and controlled through four special function registers in the system controller: SPIOCN Control Register, SPIODAT Data Register, SPIOCFG Configuration Register, and SPIOCKR Clock Rate Register. The four special function registers related to the operation of the SPI Bus are described in the following section.

| Figure 15.5.  | SPI0CEG:   | SPI | Configuration | Register |

|---------------|------------|-----|---------------|----------|

| 11gui c 15.5. | DI IUCI G. |     | Comiguiation  | Register |

| R/W      | R/W                                                                                           |                                                                                                    | R                                                                                  | R                                                                        | R                                       | R/W                               | R/W      | R/W     | Reset Valu         |

|----------|-----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|--------------------------------------------------------------------------|-----------------------------------------|-----------------------------------|----------|---------|--------------------|

| CKPHA    | CKPO                                                                                          | L B                                                                                                | BC2                                                                                | BC1                                                                      | BC0                                     | SPIFRS2                           | SPIFRS1  | SPIFRS0 | 00000111           |

| Bit7     | Bit6                                                                                          | E                                                                                                  | Bit5                                                                               | Bit4                                                                     | Bit3                                    | Bit2                              | Bit1     | Bit0    | SFR Addres<br>0x9A |

| Bit7:    | CKPHA: S                                                                                      | SPI Clock                                                                                          | Phase.                                                                             |                                                                          |                                         |                                   |          |         |                    |

|          | This bit co                                                                                   | ontrols the                                                                                        | e SPI cloc                                                                         | k phase.                                                                 |                                         |                                   |          |         |                    |

|          | 0: Data san                                                                                   | mpled on                                                                                           | first edge                                                                         | of SCK pe                                                                | eriod.                                  |                                   |          |         |                    |

|          | 1: Data sai                                                                                   | mpled on                                                                                           | second e                                                                           | lge of SCK                                                               | period.                                 |                                   |          |         |                    |

| Bit6:    | CKPOL: S                                                                                      | SPI Clock                                                                                          | Polarity.                                                                          |                                                                          |                                         |                                   |          |         |                    |

|          | This bit co                                                                                   | ontrols the                                                                                        | e SPI cloc                                                                         | k polarity.                                                              |                                         |                                   |          |         |                    |

|          | 0: SCK lin                                                                                    | ne low in i                                                                                        | idle state.                                                                        |                                                                          |                                         |                                   |          |         |                    |

|          | 1: SCK lin                                                                                    | he high in                                                                                         | idle state                                                                         |                                                                          |                                         |                                   |          |         |                    |

| Bits5-3: | BC2-BC0:                                                                                      | : SPI Bit (                                                                                        | Count.                                                                             |                                                                          |                                         |                                   |          |         |                    |

|          | Indicates w                                                                                   | which of t                                                                                         | the up to 8                                                                        | 8 bits of the                                                            | e SPI word h                            | nave been tran                    | smitted. |         |                    |

|          |                                                                                               | BC2-BC                                                                                             | 0                                                                                  | Bit Tra                                                                  | nsmitted                                |                                   |          |         |                    |

|          | 0                                                                                             | 0                                                                                                  | 0                                                                                  | Bit 0                                                                    | (LSB)                                   |                                   |          |         |                    |

|          | 0                                                                                             | 0                                                                                                  | 1                                                                                  | Bit 1                                                                    |                                         |                                   |          |         |                    |

|          | 0                                                                                             | 1                                                                                                  | 0                                                                                  | Bit 2                                                                    |                                         |                                   |          |         |                    |

|          | 0                                                                                             | 4                                                                                                  | 1                                                                                  | D'- 0                                                                    |                                         |                                   |          |         |                    |

|          | 0                                                                                             | 1                                                                                                  | 1                                                                                  | Bit 3                                                                    |                                         |                                   |          |         |                    |

|          | 0                                                                                             | 0                                                                                                  | 0                                                                                  | Bit 3<br>Bit 4                                                           |                                         |                                   |          |         |                    |

|          | -                                                                                             |                                                                                                    | -                                                                                  |                                                                          |                                         |                                   |          |         |                    |

|          | 1                                                                                             | 0                                                                                                  | 0                                                                                  | Bit 4                                                                    |                                         |                                   |          |         |                    |

|          | 1<br>1<br>1<br>1                                                                              | 0<br>0<br>1<br>1                                                                                   | 0<br>1<br>0<br>1                                                                   | Bit 4<br>Bit 5<br>Bit 6<br>Bit 7                                         |                                         |                                   |          |         |                    |

| Bits2-0: | 1111SPIFRS2-These three                                                                       | 0<br>0<br>1<br>SPIFRS0<br>ee bits dete<br>ata transfe                                              | 0<br>1<br>0<br>1<br>: SPI Fran<br>ermine th<br>er in mast                          | Bit 4<br>Bit 5<br>Bit 6<br>Bit 7<br>ne Size.<br>e number o<br>er mode. T | (MSB)<br>If bits to shi<br>They are ign | ft in/out of the<br>ored in slave |          | gister  |                    |

| Bits2-0: | 1       1       1       1       SPIFRS2       These thre       during a data                  | 0<br>0<br>1<br>SPIFRS0:<br>se bits dete<br>ata transfe<br>SPIFRS                                   | 0<br>1<br>0<br>: SPI Frar<br>ermine th<br>er in mast                               | Bit 4Bit 5Bit 6Bit 7ne Size.e number oer mode. TBits Shi                 | (MSB)<br>If bits to shi<br>They are ign |                                   |          | gister  |                    |

| Bits2-0: | 1         1         1         1         SPIFRS2-:         These three during a data         0 | 0<br>0<br>1<br>SPIFRS0:<br>ee bits dete<br>ata transfe<br>SPIFRS<br>0                              | 0<br>1<br>0<br>: SPI Frar<br>ermine th<br>er in mast                               | Bit 4Bit 5Bit 6Bit 7ne Size.e number oer mode. TBits Shi1                | (MSB)<br>If bits to shi<br>They are ign |                                   |          | gister  |                    |

| Bits2-0: | 11111SPIFRS2-3These three during a data data data data data data data d                       | 0<br>0<br>1<br>SPIFRS0:<br>we bits detern<br>ata transfe<br>SPIFRS<br>0<br>0<br>0                  | 0<br>1<br>0<br>1<br>: SPI Frar<br>ermine th<br>er in mast<br>0<br>1                | Bit 4Bit 5Bit 6Bit 7ne Size.e number oer mode. TBits Shi12               | (MSB)<br>If bits to shi<br>They are ign |                                   |          | gister  |                    |

| Bits2-0: | 1         1         1         1         SPIFRS2-:         These three during a data         0 | 0<br>0<br>1<br>SPIFRS0:<br>ee bits dete<br>ata transfe<br>SPIFRS<br>0                              | 0<br>1<br>0<br>: SPI Frar<br>ermine th<br>er in mast                               | Bit 4Bit 5Bit 6Bit 7ne Size.e number oer mode. TBits Shi1                | (MSB)<br>If bits to shi<br>They are ign |                                   |          | gister  |                    |

| Bits2-0: | 111111SPIFRS2-3These threeduring a data000000                                                 | 0<br>0<br>1<br>SPIFRS0:<br>ee bits dete<br>ata transfe<br>SPIFRS<br>0<br>0<br>1                    | 0<br>1<br>0<br>1<br>: SPI Fran<br>ermine th<br>er in mast<br>0<br>1<br>0           | Bit 4Bit 5Bit 6Bit 7ne Size.e number oer mode. TBits Shi123              | (MSB)<br>If bits to shi<br>They are ign |                                   |          | gister  |                    |

| Bits2-0: | 111111SPIFRS2-3These threeduring a data000000                                                 | 0<br>0<br>1<br>SPIFRS0<br>ee bits dete<br>ata transfe<br>SPIFRS<br>0<br>0<br>0<br>1<br>1           | 0101: SPI Franceermine the<br>er in mast01010                                      | Bit 4Bit 5Bit 6Bit 7ne Size.e number oer mode. TBits Shi1234             | (MSB)<br>If bits to shi<br>They are ign |                                   |          | gister  |                    |

| Bits2-0: | 111111SPIFRS2-3These threeduring a data000000                                                 | 0<br>0<br>1<br>1<br>SPIFRS0<br>ee bits dete<br>ata transfe<br>SPIFRS<br>0<br>0<br>0<br>1<br>1<br>0 | 0<br>1<br>0<br>1<br>: SPI Frar<br>ermine th<br>er in mast<br>0<br>1<br>0<br>1<br>0 | Bit 4Bit 5Bit 6Bit 7ne Size.e number oer mode. 7Bits Shi12345            | (MSB)<br>If bits to shi<br>They are ign |                                   |          | gister  |                    |

The Timer 2 overflow rate, when in *Baud Rate Generator Mode* and using an internal clock source, is determined solely by the Timer 2 16-bit reload value (RCAP2H:RCAP2L). The Timer 2 clock source is fixed at SYSCLK/2. The Timer 2 overflow rate can be calculated as follows:

#### $T2\_OVERFLOWRATE = (SYSCLK/2) / (65536 - [RCAP2H:RCAP2L]).$

Timer 2 can be selected as the baud rate generator for RX and/or TX by setting RCLK (T2CON.5) and/or TCLK (T2CON.4), respectively. When either RCLK or TCLK is set to logic 1, Timer 2 interrupts are automatically disabled and the timer is forced into *Baud Rate Generator Mode* with SYSCLK/2 as its clock source. If a different timebase is required, setting the C/T2 bit (T2CON.1) to logic 1 will allow Timer 2 to be clocked from the external input pin T2. See the Timers section for complete timer configuration details.

Figure 16.5. UART Modes 1, 2, and 3 Interconnect Diagram

| -                          |               |                     |                       |  |  |  |  |

|----------------------------|---------------|---------------------|-----------------------|--|--|--|--|

| Oscillator Frequency (MHz) | Divide Factor | Timer 1 Load Value* | Resulting Baud Rate** |  |  |  |  |

| 24.0                       | 208           | 0xF3                | 115200 (115384)       |  |  |  |  |

| 23.592                     | 205           | 0xF3                | 115200 (113423)       |  |  |  |  |

| 22.1184                    | 192           | 0xF4                | 115200                |  |  |  |  |

| 18.432                     | 160           | 0xF6                | 115200                |  |  |  |  |

| 16.5888                    | 144           | 0xF7                | 115200                |  |  |  |  |

| 14.7456                    | 128           | 0xF8                | 115200                |  |  |  |  |

| 12.9024                    | 112           | 0xF9                | 115200                |  |  |  |  |

| 11.0592                    | 96            | 0xFA                | 115200                |  |  |  |  |

| 9.216                      | 80            | 0xFB                | 115200                |  |  |  |  |

| 7.3728                     | 64            | 0xFC                | 115200                |  |  |  |  |

| 5.5296                     | 48            | 0xFD                | 115200                |  |  |  |  |

| 3.6864                     | 32            | 0xFE                | 115200                |  |  |  |  |

| 1.8432                     | 16            | 0xFF                | 115200                |  |  |  |  |

| 24.576                     | 320           | 0xEC                | 76800                 |  |  |  |  |

| 25.0                       | 434           | 0xE5                | 57600 (57870)         |  |  |  |  |

| 25.0                       | 868           | 0xCA                | 28800                 |  |  |  |  |

| 24.576                     | 848           | 0xCB                | 28800 (28921)         |  |  |  |  |

| 24.0                       | 833           | 0xCC                | 28800 (28846)         |  |  |  |  |

| 23.592                     | 819           | 0xCD                | 28800 (28911)         |  |  |  |  |

| 22.1184                    | 768           | 0xD0                | 28800                 |  |  |  |  |

| 18.432                     | 640           | 0xD8                | 28800                 |  |  |  |  |

| 16.5888                    | 576           | 0xDC                | 28800                 |  |  |  |  |

| 14.7456                    | 512           | 0xE0                | 28800                 |  |  |  |  |

| 12.9024                    | 448           | 0xE4                | 28800                 |  |  |  |  |

| 11.0592                    | 384           | 0xE8                | 28800                 |  |  |  |  |

| 9.216                      | 320           | 0xEC                | 28800                 |  |  |  |  |

| 7.3728                     | 256           | 0xF0                | 28800                 |  |  |  |  |

| 5.5296                     | 192           | 0xF4                | 28800                 |  |  |  |  |

| 3.6864                     | 128           | 0xF8                | 28800                 |  |  |  |  |

| 1.8432                     | 64            | 0xFC                | 28800                 |  |  |  |  |

Table 16.2. Oscillator Frequencies for Standard Baud Rates

\* Assumes SMOD=1 and T1M=1.

\*\* Numbers in parenthesis show the actual baud rate.

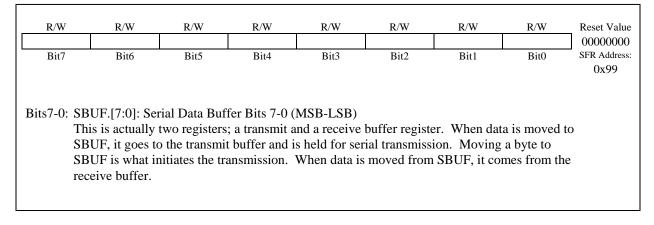

| Figure 16.8 | <b>SBUF:</b> Serial | (UART) Data | <b>Buffer Register</b> |

|-------------|---------------------|-------------|------------------------|

|-------------|---------------------|-------------|------------------------|

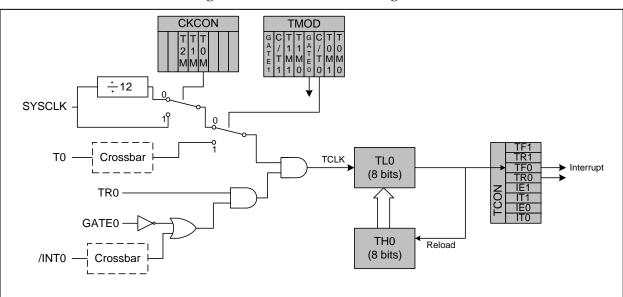

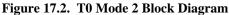

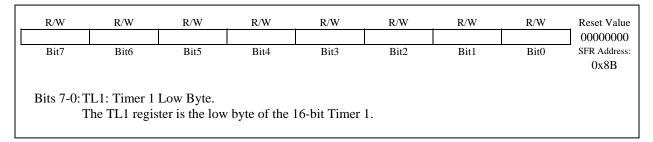

#### 17.1.3. Mode 2: 8-bit Counter/Timer with Auto-Reload

Mode 2 configures Timer 0 and Timer 1 to operate as 8-bit counter/timers with automatic reload of the start value. The TL0 holds the count and TH0 holds the reload value. When the count in TL0 overflows from all ones to 0x00, the timer overflow flag TF0 (TCON.5) is set and the counter in TL0 is reloaded from TH0. If enabled, an interrupt will occur when the TF0 flag is set. The reload value in TH0 is not changed. TL0 must be initialized to the desired value before enabling the timer for the first count to be correct. When in Mode 2, Timer 1 operates identically to Timer 0. Both counter/timers are enabled and configured in Mode 2 in the same manner as Mode 0.

#### Figure 17.7. TL0: Timer 0 Low Byte

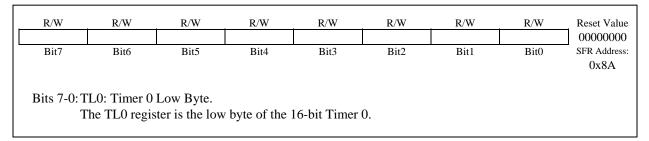

Figure 17.8. TL1: Timer 1 Low Byte

#### Figure 17.9. TH0: Timer 0 High Byte

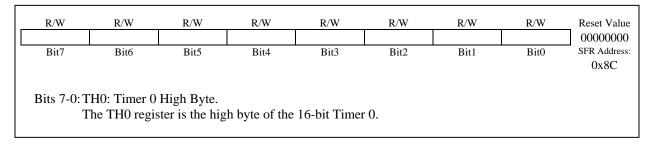

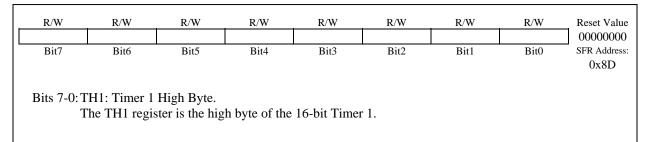

Figure 17.10. TH1: Timer 1 High Byte

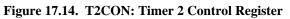

| R/W   | R/W                                                                                                                       | R/W                                                                     | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | R/W                                               | R/W                                             | R/W                           | R/W                       | Reset Valu      |

|-------|---------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-------------------------------------------------|-------------------------------|---------------------------|-----------------|

| TF2   | EXF2                                                                                                                      | RCLK                                                                    | TCLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | EXEN2                                             | TR2                                             | C/T2                          | CP/RL2                    | 0000000         |

| Bit7  | Bit6                                                                                                                      | Bit5                                                                    | Bit4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Bit3                                              | Bit2                                            | Bit1                          | Bit0<br>(bit addressable) | SFR Addres 0xC8 |

| Bit7: | TF2: Timer 2<br>Set by hardwa<br>the Timer 2 in<br>interrupt servi<br>cleared by sof                                      | re when Tim<br>terrupt is ena<br>ce routine. T                          | er 2 overflo<br>bled, setting<br>This bit is no                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | g this bit cause<br>t automaticall                | es the CPU to<br>y cleared by                   | o vector to th<br>hardware ar | ne Timer 2<br>nd must be  |                 |

| Bit6: | EXF2: Timer<br>Set by hardwa<br>the T2EX input<br>this bit causes<br>automatically                                        | tre when eith<br>ut pin and EX<br>the CPU to                            | er a capture<br>XEN2 is logi<br>vector to the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | c 1. When th<br>Timer 2 Inter                     | e Timer 2 int<br>rupt service                   | terrupt is ena<br>routine. Th | abled, setting            |                 |