# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                             |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 25MHz                                                           |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT              |

| Number of I/O              | 16                                                              |

| Program Memory Size        | 16KB (16K x 8)                                                  |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                |                                                                 |

| RAM Size                   | 1.25K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.8V ~ 3.6V                                                     |

| Data Converters            | A/D 8x10b                                                       |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 48-TQFP                                                         |

| Supplier Device Package    | 48-TQFP (7x7)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f019-gqr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 1. SYSTEM OVERVIEW

The C8051F018/9 are fully integrated mixed-signal System on a Chip MCUs with a true 10-bit multi-channel ADC. See the Product Selection Guide in Table 1.1 for a quick reference of each MCUs' feature set. Each has two voltage comparators, a voltage reference, and an 8051-compatible microcontroller core with 16kbytes of FLASH memory and 1.25kbytes of RAM. There are also I2C/SMBus, UART, and SPI serial interfaces implemented in hardware (not "bit-banged" in user software) as well as a Programmable Counter/Timer Array (PCA) with five capture/compare modules. There are also 4 general-purpose 16-bit timers and 4 byte-wide general-purpose digital Port I/O.

With an on-board VDD monitor, WDT, and clock oscillator, the MCUs are truly stand-alone System-on-a-Chip solutions. Each MCU effectively configures and manages the analog and digital peripherals. The FLASH memory can be reprogrammed even in-circuit, providing non-volatile data storage, and also allowing field upgrades of the 8051 firmware. Each MCU can also individually shut down any or all of the peripherals to conserve power.

On-board JTAG debug support allows non-intrusive (uses no on-chip resources), full speed, in-circuit debug using the production MCU installed in the final application. This debug system supports inspection and modification of memory and registers, setting breakpoints, watchpoints, single stepping, and run and halt commands. All analog and digital peripherals are fully functional when using JTAG debug.

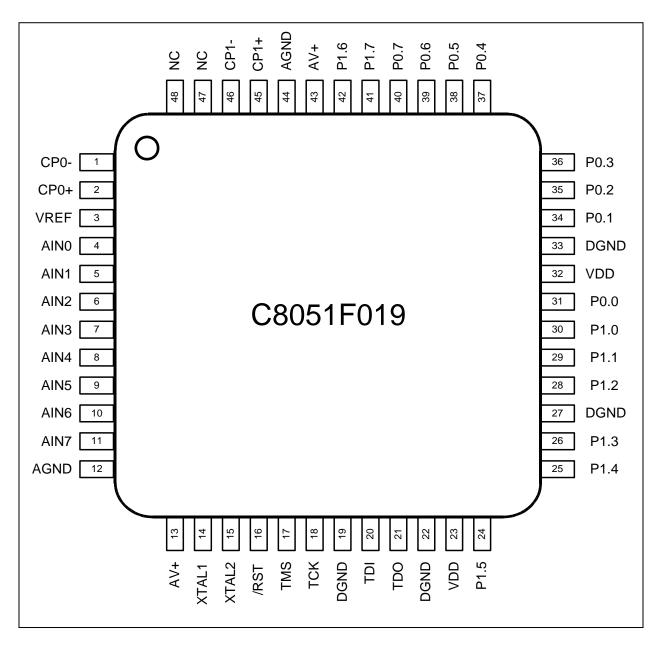

Each MCU is specified for 2.8V-to-3.6V operation over the industrial temperature range (-45C to +85C). The Port I/Os, /RST, and JTAG pins are tolerant for input signals up to 5V. The C8051F018 is available in the 64-pin TQFP (see block diagram in Figure 1.1). The C8051F019 is available in the 48-pin TQFP (see block diagram in Figure 1.2).

|           | MIPS (Peak) | FLASH Memory | RAM  | SMBus/12C    | IdS          | UART         | Timers (16-bit) | Programmable Counter Array | Digital Port I/O's | ADC Resolution (bits) | ADC Max Speed (ksps) | ADC Inputs | Voltage Reference | Temperature Sensor | Voltage Comparators | Package |

|-----------|-------------|--------------|------|--------------|--------------|--------------|-----------------|----------------------------|--------------------|-----------------------|----------------------|------------|-------------------|--------------------|---------------------|---------|

| C8051F018 | 25          | 16k          | 1280 | $\checkmark$ | $\checkmark$ | $\checkmark$ | 4               | $\checkmark$               | 32                 | 10                    | 100                  | 8          | $\checkmark$      | $\checkmark$       | 2                   | 64TQFP  |

| C8051F019 | 25          | 16k          | 1280 | $\checkmark$ | $\checkmark$ | $\checkmark$ | 4               | $\checkmark$               | 16                 | 10                    | 100                  | 8          | $\checkmark$      | $\checkmark$       | 2                   | 48TQFP  |

Table 1.1. Product Selection Guide

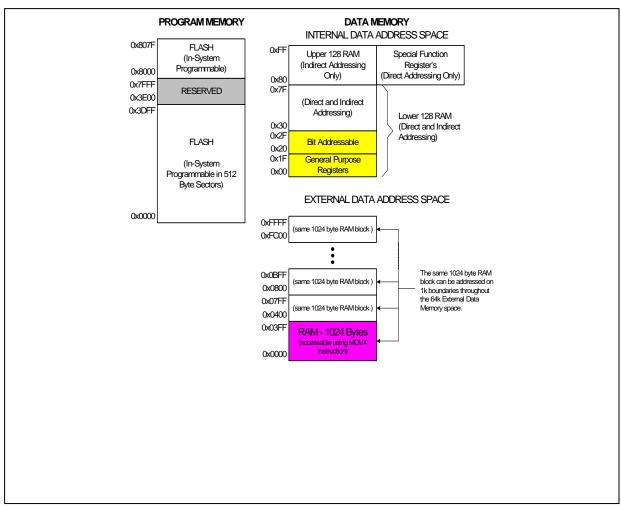

### 1.2. On-Board Memory

The CIP-51 has a standard 8051 program and data address configuration. It includes 256 bytes of data RAM, with the upper 128 bytes dual-mapped. Indirect addressing accesses the upper 128 bytes of general purpose RAM, and direct addressing accesses the 128 byte SFR address space. The lower 128 bytes of RAM are accessible via direct and indirect addressing. The first 32 bytes are addressable as four banks of general-purpose registers, and the next 16 bytes can be byte addressable or bit addressable.

The CIP-51 additionally has a 1024 byte RAM block in the external data memory address space. This 1024 byte block can be addressed over the entire 64k external data memory address range (see Figure 1.5).

The MCU's program memory consists of 16k + 128 bytes of FLASH. This memory may be reprogrammed insystem in 512 byte sectors, and requires no special off-chip programming voltage. The 512 bytes from addresses 0x3E00 to 0x3FFF are reserved for factory use. The additional 128 byte block is located at address 0x8000. See Figure 1.5 for the MCU system memory map.

Figure 1.5. On-Board Memory Map

Figure 4.3. TQFP-48 Pinout Diagram

| R/W      | R/W            | R/W            | R/W            | R/W            | R/W           | R/W            | R/W        | Reset Value  |

|----------|----------------|----------------|----------------|----------------|---------------|----------------|------------|--------------|

| -        | -              | -              | -              | AIN67IC        | AIN45IC       | AIN23IC        | AIN01IC    | 00000000     |

| Bit7     | Bit6           | Bit5           | Bit4           | Bit3           | Bit2          | Bit1           | Bit0       | SFR Address: |

|          |                |                |                |                |               |                |            | 0xBA         |

| Bits7-4: | UNUSED. Read   | d = 0000b; W   | rite = don't   | care           |               |                |            |              |

| Bit3:    | AIN67IC: AIN6  | ,              |                |                |               |                |            |              |

|          | 0: AIN6 and AI | N7 are indep   | endent singl   | ed-ended inp   | uts           |                |            |              |

|          | 1: AIN6, AIN7  | are (respectiv | vely) +, - dif | ferential inpu | ıt pair       |                |            |              |

| Bit2:    | AIN45IC: AIN4  | , AIN5 Input   | Pair Config    | uration Bit    |               |                |            |              |

|          | 0: AIN4 and AI | N5 are indep   | endent singl   | ed-ended inp   | uts           |                |            |              |

|          | 1: AIN4, AIN5  | are (respectiv | vely) +, - dif | ferential inpu | ıt pair       |                |            |              |

| Bit1:    | AIN23IC: AIN2  | , AIN3 Input   | Pair Config    | uration Bit    |               |                |            |              |

|          | 0: AIN2 and AI | 1              | 0              | 1              |               |                |            |              |

|          | 1: AIN2, AIN3  | · •            | •              | -              | ıt pair       |                |            |              |

| Bit0:    | AIN01IC: AIN0  | · •            | Ų              |                |               |                |            |              |

|          | 0: AIN0 and AI | -              | U              | -              |               |                |            |              |

|          | 1: AIN0, AIN1  | are (respectiv | vely) +, - dif | ferential inpu | ıt pair       |                |            |              |

|          |                |                | _              |                |               |                |            |              |

| NOTE:    | The ADC Data V | Word is in 2's | s complemen    | t format for o | channels cont | figured as dif | ferential. |              |

|          |                |                |                |                |               |                |            |              |

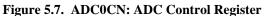

### Figure 5.4. AMX0CF: AMUX Configuration Register

| R/W      | R/W                           | R/W           | R/W           | R/W             | Control Regi<br>R/W | R/W            | R/W               | Reset Value  |

|----------|-------------------------------|---------------|---------------|-----------------|---------------------|----------------|-------------------|--------------|

| ADCE     | 1                             | ADCINT        | ADBUSY        | ADSTM1          | ADSTM0              | ADWINT         | ADLJST            | 00000000     |

| Bit7     | Bit6                          | Bit5          | Bit4          | Bit3            | Bit2                | Bit1           | Bit0              | SFR Address: |

|          |                               |               |               |                 |                     |                | (bit addressable) | 0xE8         |

| Bit7:    | ADCEN: ADC                    | Enable Bit    |               |                 |                     |                |                   |              |

| DII/.    | 0: ADC Disabl                 |               | n low nower   | shutdown        |                     |                |                   |              |

|          | 1: ADC Enable                 |               |               |                 | onversions          |                |                   |              |

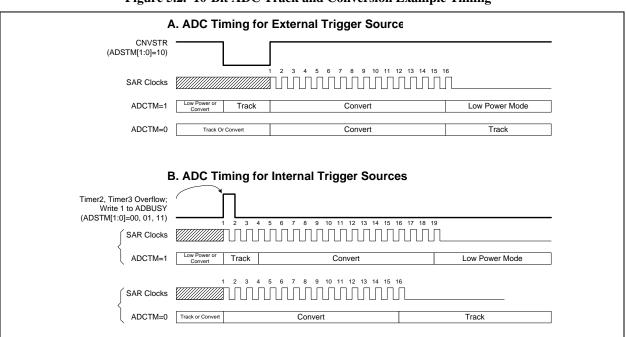

| Bit6:    | ADCTM: ADC                    |               |               | dy for data e   | Silversions.        |                |                   |              |

| Dito.    | 0: When the A                 |               |               | always done     | unless a con        | version is in  | process           |              |

|          | 1: Tracking De                |               |               | urwuys done     | uniess a con        |                | process           |              |

|          | ADST                          | -             | 51111 0 0115  |                 |                     |                |                   |              |

|          |                               |               | with the writ | te of 1 to AD   | BUSY and la         | asts for 3 SA  | R clocks          |              |

|          |                               |               |               |                 |                     | for 3 SAR clo  |                   |              |

|          |                               | DC tracks on  |               |                 |                     |                |                   |              |

|          |                               |               |               |                 |                     | for 3 SAR clo  | ocks              |              |

| Bit5:    | ADCINT: ADC                   |               |               |                 |                     |                |                   |              |

|          | (Must be cleare               |               |               |                 |                     |                |                   |              |

|          | 0: ADC has no                 | t completed a | data conver   | sion since the  | e last time thi     | is flag was cl | eared             |              |

|          | 1: ADC has co                 | mpleted a dat | a conversion  | L               |                     |                |                   |              |

| Bit4:    | ADBUSY: AD                    | C Busy Bit    |               |                 |                     |                |                   |              |

|          | Read                          |               |               |                 |                     |                |                   |              |

|          | 0: ADC Conve                  |               |               |                 |                     | since a reset. | The falling       |              |

|          |                               | BUSY genera   |               | upt when ena    | bled.               |                |                   |              |

|          | 1: ADC Busy of                | converting da | ta            |                 |                     |                |                   |              |

|          | Write                         |               |               |                 |                     |                |                   |              |

|          | 0: No effect                  |               |               |                 |                     |                |                   |              |

|          | 1: Starts ADC                 |               |               |                 |                     |                |                   |              |

| Bits3-2: | ADSTM1-0: A                   |               |               |                 |                     |                |                   |              |

|          | 00: ADC conve                 |               |               |                 |                     |                |                   |              |

|          | 01: ADC conve                 |               |               |                 |                     |                |                   |              |

|          | 10: ADC conve                 |               |               |                 |                     |                |                   |              |

| Bit1:    | 11: ADC conve                 |               |               |                 | her 2               |                |                   |              |

| BILL     | ADWINT: AD<br>(Must be cleare |               |               | rupt Flag       |                     |                |                   |              |

|          | 0: ADC Windo                  |               |               | h has not occ   | urrad               |                |                   |              |

|          | 1: ADC Windo                  |               |               |                 | uncu                |                |                   |              |

| Bit0:    | ADLJST: ADC                   |               |               |                 |                     |                |                   |              |

| DITO.    | 0: Data in ADC                |               |               | right instified | l                   |                |                   |              |

|          | 1: Data in ADC                |               |               |                 | •                   |                |                   |              |

|          |                               |               |               | Justified       |                     |                |                   |              |

|          |                               |               |               |                 |                     |                |                   |              |

|          |                               |               |               |                 |                     |                |                   |              |

| R/W     | R              | R/W            | R/W           | R/W                  | R/W             | R/W            | R/W     | Reset Value  |  |  |

|---------|----------------|----------------|---------------|----------------------|-----------------|----------------|---------|--------------|--|--|

| CP1EN   | CP1OUT         | CP1RIF         | CP1FIF        | CP1HYP1              | CP1HYP0         | CP1HYN1        | CP1HYN0 | 00000000     |  |  |

| Bit7    | Bit6           | Bit5           | Bit4          | Bit3                 | Bit2            | Bit1           | Bit0    | SFR Address: |  |  |

|         |                | 0x9F           |               |                      |                 |                |         |              |  |  |

| Bit7:   | CP1EN: Com     | parator 1 Ena  | ble Bit       |                      |                 |                |         |              |  |  |

|         | 0: Comparato   | r 1 Disabled.  |               |                      |                 |                |         |              |  |  |

|         | 1: Comparato   | r 1 Enabled.   |               |                      |                 |                |         |              |  |  |

| Bit6:   | CP1OUT: Con    | mparator 1 O   | utput State F | Flag                 |                 |                |         |              |  |  |

|         | 0: Voltage on  | CP1 + < CP1    | -             |                      |                 |                |         |              |  |  |

|         | 1: Voltage on  | CP1 + > CP1    | -             |                      |                 |                |         |              |  |  |

| Bit5:   | CP1RIF: Com    |                |               | terrupt Flag         |                 |                |         |              |  |  |

|         | 0: No Compa    | rator 1 Rising | g-Edge Inter  | rupt has occu        | rred since thi  | s flag was cl  | eared   |              |  |  |

|         | 1: Comparato   | r 1 Rising-Ed  | lge Interrupt | has occurred         | since this fla  | ag was cleare  | d       |              |  |  |

| Bit4:   | CP1FIF: Com    | parator 1 Fal  | ling-Edge In  | terrupt Flag         |                 |                |         |              |  |  |

|         | 0: No Compa    | rator 1 Fallin | g-Edge Inter  | rupt has occu        | irred since th  | is flag was cl | leared  |              |  |  |

|         | 1: Comparato   | r 1 Falling-E  | dge Interrup  | t has occurre        | d since this fl | ag was clear   | ed      |              |  |  |

| Bit3-2: | CP1HYP1-0:     | Comparator     | Positive Hy   | ysteresis Con        | trol Bits       |                |         |              |  |  |

|         | 00: Positive H | Iysteresis Di  | sabled        |                      |                 |                |         |              |  |  |

|         | 01: Positive H | Iysteresis = 2 | lmV           |                      |                 |                |         |              |  |  |

|         | 10: Positive H | Iysteresis = 4 | mV            |                      |                 |                |         |              |  |  |

|         | 11: Positive H | Iysteresis = 1 | 0mV           |                      |                 |                |         |              |  |  |

| Bit1-0: | CP1HYN1-0:     | Comparator     | 1 Negative H  | <b>Hysteresis</b> Co | ntrol Bits      |                |         |              |  |  |

|         | 00: Negative   | Hysteresis D   | isabled       |                      |                 |                |         |              |  |  |

|         | 01: Negative   | Hysteresis =   | 2mV           |                      |                 |                |         |              |  |  |

|         | 10: Negative   | Hysteresis =   | 4mV           |                      |                 |                |         |              |  |  |

|         | 11: Negative   | Hysteresis =   | 10mV          |                      |                 |                |         |              |  |  |

|         | -              |                |               |                      |                 |                |         |              |  |  |

### Figure 6.4. CPT1CN: Comparator 1 Control Register

| R/W   | R/W                                                                   | R/W                              | R/W                        | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | R/W                          | R/W            | R/W  | Reset Value         |

|-------|-----------------------------------------------------------------------|----------------------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|----------------|------|---------------------|

| PXVLD | -                                                                     | PX7                              | PX6                        | PX5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | PX4                          | PADC0          | PT3  | 00000000            |

| Bit7  | Bit6                                                                  | Bit5                             | Bit4                       | Bit3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Bit2                         | Bit1           | Bit0 | SFR Address<br>0xF7 |

| Bit7: | PXVLD: Exte<br>This bit sets th<br>0: XTLVLD i<br>1: XTLVLD i         | ne priority of                   | the XTLVL                  | D interrupt.<br>ty level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | nterrupt Pric                | ority Control. |      |                     |

| Bit6: | Reserved: Mu                                                          | st write 0. R                    | eads 0.                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                              |                |      |                     |

| Bit5: | PX7: External<br>This bit sets th<br>0: External In<br>1: External In | ne priority of terrupt 7 set     | the External to low priori | Interrupt 7.<br>ty level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                              |                |      |                     |

| Bit4: | PX6: External<br>This bit sets th<br>0: External In<br>1: External In | ne priority of terrupt 6 set     | the External to low priori | Interrupt 6.<br>ty level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                              |                |      |                     |

| Bit3: | PX5: External<br>This bit sets th<br>0: External In<br>1: External In | ne priority of terrupt 5 set     | the External to low priori | Interrupt 5.<br>ty level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                              |                |      |                     |

| Bit2: | PX4: External<br>This bit sets th<br>0: External In<br>1: External In | ne priority of terrupt 4 set     | the External to low priori | Interrupt 4.<br>ty level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                              |                |      |                     |

| Bit1: | PADC0: ADC<br>This bit sets th<br>0: ADC0 End<br>1: ADC0 End          | e priority of<br>of Conversi     | the ADC0 E<br>on interrupt | and of Conversions of Conversions of Conversions of the conversion | sion Interru<br>ority level. | pt.            |      |                     |

| Bit0: | PT3: Timer 3<br>This bit sets th<br>0: Timer 3 int<br>1: Timer 3 int  | ne priority of<br>terrupt set to | the Timer 3 low priority   | interrupts.<br>level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                              |                |      |                     |

|       |                                                                       |                                  |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                              |                |      |                     |

### Figure 8.14. EIP2: Extended Interrupt Priority 2

### **10. EXTERNAL RAM**

The C8051F018/9 includes 1024 bytes of RAM mapped into the external data memory space. All of these address locations may be accessed using the external move instruction (MOVX) and the data pointer (DPTR), or using MOVX indirect addressing mode. If the MOVX instruction is used with an 8-bit address operand (such as @R1), then the high byte of the 16-bit address is provided by the External Memory Interface Control Register (EMI0CN as shown in Figure 10.1). Note: the MOVX instruction is also used for writes to the Flash memory. See Section 9 for details. The MOVX instruction accesses XRAM by default (i.e. PSTCL.0 = 0).

For any of the addressing modes the upper 5-bits of the 16-bit external data memory address word are "don't cares". As a result, the 1024-byte RAM is mapped modulo style over the entire 64k external data memory address range. For example, the XRAM byte at address 0x0000 is also at address 0x0400, 0x0800, 0x0C00, 0x1000, etc. This is a useful feature when doing a linear memory fill, as the address pointer doesn't have to be reset when reaching the RAM block boundary.

| R          | R                                                                                                                                                                   | R                                                                                            | R                                            | R                               | R/W                            | R/W           | R/W       | Reset Value  |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|----------------------------------------------|---------------------------------|--------------------------------|---------------|-----------|--------------|

| -          | -                                                                                                                                                                   | -                                                                                            | -                                            | -                               | -                              | PGSEL1        | PGSEL0    | 00000000     |

| Bit7       | Bit6                                                                                                                                                                | Bit5                                                                                         | Bit4                                         | Bit3                            | Bit2                           | Bit1          | Bit0      | SFR Address: |

|            |                                                                                                                                                                     |                                                                                              |                                              |                                 |                                |               |           | 0xAF         |

| Bits 1-0:H | Not Used – rea<br>PGSEL[1:0]: 2<br>The XRAM Pa<br>address when<br>RAM. The up<br>over the entire<br>00: xxxxxx001<br>01: xxxxxx011<br>00: xxxxx101<br>11: xxxxxx111 | XRAM Page<br>age Select Bi<br>using an 8-bi<br>pper 6-bits ard<br>64k externa<br>5<br>5<br>5 | ts provide th<br>t MOVX con<br>e "don't care | nmand, effec<br>s", so the 1k a | tively selecti<br>address bloc | ing a 256-byt | e page of |              |

### Figure 10.1. EMIOCN: External Memory Interface Control

### **12. OSCILLATOR**

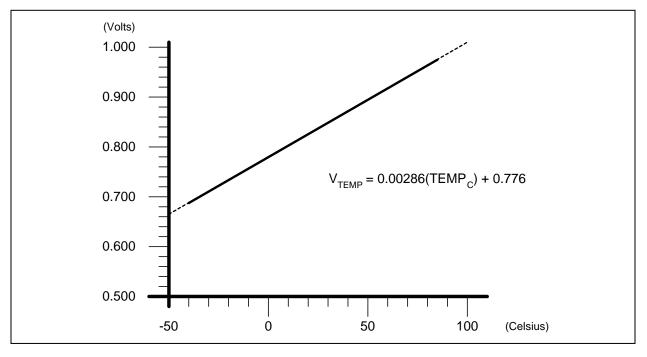

Each MCU includes an internal oscillator and an external oscillator drive circuit, either of which can generate the system clock. The MCUs boot from the internal oscillator after any reset. The internal oscillator starts up instantly. It can be enabled/disabled and its frequency can be changed using the Internal Oscillator Control Register (OSCICN) as shown in Figure 12.2. The internal oscillator's electrical specifications are given in Table 12.1.

Both oscillators are disabled when the /RST pin is held low. The MCUs can run from the internal oscillator or external oscillator, and switch between the two at will using the CLKSL bit in the OSCICN Register. The external oscillator requires an external resonator, parallel-mode crystal, capacitor, or RC network connected to the XTAL1/XTAL2 pins (see Figure 12.1). The oscillator circuit must be configured for one of these sources in the OSCXCN register. An external CMOS clock can also provide the system clock via overdriving the XTAL1 pin. The XTAL1 and XTAL2 pins are 3.6V (not 5V) tolerant. The external oscillator can be left enabled and running even when the MCU has switched to using the internal oscillator.

Figure 12.1. Oscillator Diagram

### **15. SERIAL PERIPHERAL INTERFACE BUS**

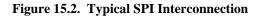

The Serial Peripheral Interface (SPI) provides access to a four-wire, full-duplex, serial bus. SPI supports the connection of multiple slave devices to a master device on the same bus. A separate slave-select signal (NSS) is used to select a slave device and enable a data transfer between the master and the selected slave. Multiple masters on the same bus are also supported. Collision detection is provided when two or more masters attempt a data transfer at the same time. The SPI can operate as either a master or a slave. When the SPI is configured as a master, the maximum data transfer rate (bits/sec) is one-half the system clock frequency.

When the SPI is configured as a slave, the maximum data transfer rate (bits/sec) for full-duplex operation is 1/10 the system clock frequency, provided that the master issues SCK, NSS, and the serial input data synchronously with the system clock. If the master issues SCK, NSS, and the serial input data asynchronously, the maximum data transfer rate (bits/sec) must be less that 1/10 the system clock frequency. In the special case where the master only wants to transmit data to the slave and does not need to receive data from the slave (i.e. half-duplex operation), the SPI slave can receive data at a maximum data transfer rate (bits/sec) of <sup>1</sup>/<sub>4</sub> the system clock frequency. This is provided that the master issues SCK, NSS, and the serial input data synchronously with the system clock.

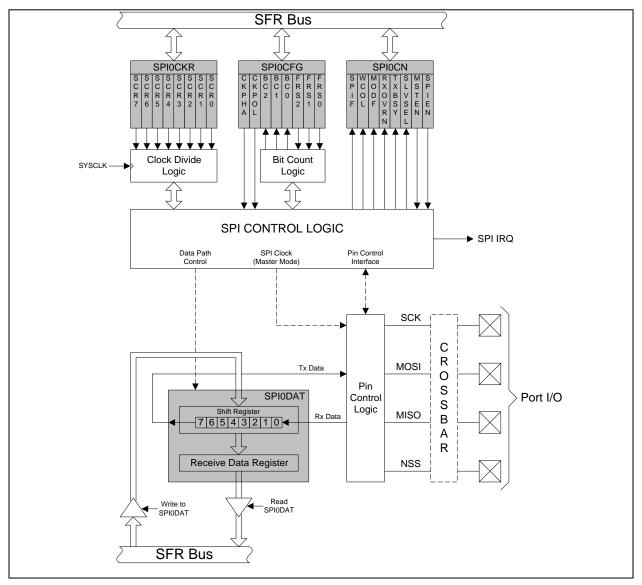

Figure 15.1. SPI Block Diagram

### **15.1.** Signal Descriptions

The four signals used by the SPI (MOSI, MISO, SCK, NSS) are described below.

### 15.1.1. Master Out, Slave In

The master-out, slave-in (MOSI) signal is an output from a master device and an input to slave devices. It is used to serially transfer data from the master to the slave. Data is transferred most-significant bit first.

### 15.1.2. Master In, Slave Out

The master-in, slave-out (MISO) signal is an output from a slave device and an input to the master device. It is used to serially transfer data from the slave to the master. Data is transferred most-significant bit first. A SPI slave places the MISO pin in a high-impedance state when the slave is not selected.

### 15.1.3. Serial Clock

The serial clock (SCK) signal is an output from the master device and an input to slave devices. It is used to synchronize the transfer of data between the master and slave on the MOSI and MISO lines.

#### 15.1.4. Slave Select

The slave select (NSS) signal is an input used to select the SPI module when in slave mode by a master, or to disable the SPI module when in master mode. When in slave mode, it is pulled low to initiate a data transfer and remains low for the duration of the transfer.

### 15.2. Operation

Only a SPI master device can initiate a data transfer. The SPI is placed in master mode by setting the Master Enable flag (MSTEN, SPIOCN.1). Writing a byte of data to the SPI data register (SPIODAT) when in Master Mode starts a data transfer. The SPI master immediately shifts out the data serially on the MOSI line while providing the serial clock on SCK. The SPIF (SPIOCN.7) flag is set to logic 1 at the end of the transfer. If interrupts are enabled, an interrupt request is generated when the SPIF flag is set. The SPI master can be configured to shift in/out from one to eight bits in a transfer operation in order to accommodate slave devices with different word lengths. The SPIFRS bits in the SPI Configuration Register (SPIOCFG.[2:0]) are used to select the number of bits to shift in/out in a transfer operation.

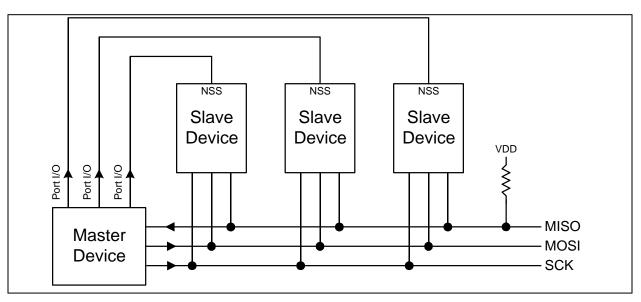

While the SPI master transfers data to a slave on the MOSI line, the addressed SPI slave device simultaneously transfers the contents of its shift register to the SPI master on the MISO line in a full-duplex operation. The data byte received from the slave replaces the data in the master's data register. Therefore, the SPIF flag serves as both a transmit-complete and receive-data-ready flag. The data transfer in both directions is synchronized with the serial clock generated by the master. Figure 15.3 illustrates the full-duplex operation of an SPI master and an addressed slave.

Figure 15.3. Full Duplex Operation

The SPI data register is double buffered on reads, but not on a write. If a write to SPI0DAT is attempted during a data transfer, the WCOL flag (SPI0CN.6) will be set to logic 1 and the write is ignored. The current data transfer will continue uninterrupted. A read of the SPI data register by the system controller actually reads the receive buffer. If the receive buffer still holds unread data from a previous transfer when the last bit of the current transfer is shifted into the SPI shift register, a receive overrun occurs and the RXOVRN flag (SPI0CN.4) is set to logic 1. The new data is not transferred to the receive buffer, allowing the previously received data byte to be read. The data byte causing the overrun is lost.

When the SPI is enabled and not configured as a master, it will operate as an SPI slave. Another SPI device acting as a master will initiate a transfer by driving the NSS signal low. The master then shifts data out of the shift register on the MOSI pin using the its serial clock. The SPIF flag is set to logic 1 at the end of a data transfer (when the NSS signal goes high). The slave can load its shift register for the next data transfer by writing to the SPI data register. The slave must make the write to the data register at least one SPI serial clock cycle before the master starts the next transmission. Otherwise, the byte of data already in the slave's shift register will be transferred.

Multiple masters may reside on the same bus. A Mode Fault flag (MODF, SPI0CN.5) is set to logic 1 when the SPI is configured as a master (MSTEN = 1) and its slave select signal NSS is pulled low. When the Mode Fault flag is set, the MSTEN and SPIEN bits of the SPI control register are cleared by hardware, thereby placing the SPI module

### 15.4. SPI Special Function Registers

The SPI is accessed and controlled through four special function registers in the system controller: SPIOCN Control Register, SPIODAT Data Register, SPIOCFG Configuration Register, and SPIOCKR Clock Rate Register. The four special function registers related to the operation of the SPI Bus are described in the following section.

| Figure 15.5.  | SPI0CEG:   | SPI | Configuration | Register |

|---------------|------------|-----|---------------|----------|

| 11gui c 15.5. | DI IUCI G. |     | Comiguiation  | Register |

| R/W      | R/W                                                                                     |                                                                                              | R                                                                                     | R                                                                        | R                             | R/W                               | R/W      | R/W     | Reset Valu         |

|----------|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|--------------------------------------------------------------------------|-------------------------------|-----------------------------------|----------|---------|--------------------|

| CKPHA    | СКРО                                                                                    | L B                                                                                          | BC2                                                                                   | BC1                                                                      | BC0                           | SPIFRS2                           | SPIFRS1  | SPIFRS0 | 00000111           |

| Bit7     | Bit6                                                                                    | E                                                                                            | Bit5                                                                                  | Bit4                                                                     | Bit3                          | Bit2                              | Bit1     | Bit0    | SFR Addres<br>0x9A |

| Bit7:    | CKPHA: S                                                                                | SPI Clock                                                                                    | Phase.                                                                                |                                                                          |                               |                                   |          |         |                    |

|          | This bit co                                                                             | ontrols the                                                                                  | e SPI cloc                                                                            | k phase.                                                                 |                               |                                   |          |         |                    |

|          | 0: Data sat                                                                             | mpled on                                                                                     | first edge                                                                            | of SCK pe                                                                | eriod.                        |                                   |          |         |                    |

|          | 1: Data sa                                                                              | mpled on                                                                                     | second e                                                                              | lge of SCK                                                               | period.                       |                                   |          |         |                    |

| Bit6:    | CKPOL: S                                                                                | SPI Clock                                                                                    | Polarity.                                                                             |                                                                          |                               |                                   |          |         |                    |

|          | This bit co                                                                             | ontrols the                                                                                  | e SPI cloc                                                                            | k polarity.                                                              |                               |                                   |          |         |                    |

|          | 0: SCK lin                                                                              | ne low in i                                                                                  | idle state.                                                                           |                                                                          |                               |                                   |          |         |                    |

|          | 1: SCK lin                                                                              | ne high in                                                                                   | idle state                                                                            |                                                                          |                               |                                   |          |         |                    |

| Bits5-3: | BC2-BC0                                                                                 | : SPI Bit (                                                                                  | Count.                                                                                |                                                                          |                               |                                   |          |         |                    |

|          | Indicates v                                                                             | which of t                                                                                   | the up to 8                                                                           | 8 bits of the                                                            | SPI word h                    | nave been tran                    | smitted. |         |                    |

|          | -                                                                                       | BC2-BC                                                                                       | )                                                                                     | Bit Tra                                                                  | nsmitted                      |                                   |          |         |                    |

|          | 0                                                                                       | 0                                                                                            | 0                                                                                     | Bit 0                                                                    | (LSB)                         |                                   |          |         |                    |

|          | 0                                                                                       | 0                                                                                            | 1                                                                                     | Bit 1                                                                    |                               |                                   |          |         |                    |

|          | 0                                                                                       | 1                                                                                            | 0                                                                                     | Bit 2                                                                    |                               |                                   |          |         |                    |

|          | 0                                                                                       |                                                                                              | 4                                                                                     | D: 0                                                                     |                               |                                   |          |         |                    |

|          | 0                                                                                       | 1                                                                                            | 1                                                                                     | Bit 3                                                                    |                               |                                   |          |         |                    |

|          | 0                                                                                       | 1<br>0                                                                                       | 0                                                                                     | Bit 3<br>Bit 4                                                           |                               |                                   |          |         |                    |

|          |                                                                                         |                                                                                              |                                                                                       |                                                                          |                               |                                   |          |         |                    |

|          | 1                                                                                       | 0                                                                                            | 0                                                                                     | Bit 4                                                                    |                               |                                   |          |         |                    |

|          | 1<br>1<br>1<br>1                                                                        | 0<br>0<br>1<br>1                                                                             | 0<br>1<br>0<br>1                                                                      | Bit 4<br>Bit 5<br>Bit 6<br>Bit 7                                         | (MSB)                         |                                   |          |         |                    |

| Bits2-0: | 1<br>1<br>1<br>SPIFRS2-<br>These three                                                  | 0<br>0<br>1<br>SPIFRS0<br>ee bits det<br>ata transfe                                         | 0<br>1<br>0<br>1<br>: SPI Fran<br>ermine th<br>er in mast                             | Bit 4<br>Bit 5<br>Bit 6<br>Bit 7<br>ne Size.<br>e number o<br>er mode. T | f bits to shi<br>They are ign | ft in/out of the<br>ored in slave |          | gister  |                    |

| Bits2-0: | 1         1         1         1         SPIFRS2-         These three         during a d | 0<br>0<br>1<br>SPIFRS0<br>se bits det<br>ata transfe<br>SPIFRS                               | 0<br>1<br>0<br>1<br>: SPI Frar<br>ermine th<br>er in mast                             | Bit 4Bit 5Bit 6Bit 7ne Size.e number oer mode. TBits Shi                 | f bits to shi<br>They are ign |                                   |          | gister  |                    |

| Bits2-0: | 11111SPIFRS2-<br>These three<br>during a d0                                             | 0<br>0<br>1<br>SPIFRS0<br>ee bits det<br>ata transfe<br>SPIFRS<br>0                          | 0<br>1<br>0<br>1<br>: SPI Frar<br>ermine th<br>er in mast                             | Bit 4Bit 5Bit 6Bit 7ne Size.e number oer mode. TBits Shi1                | f bits to shi<br>They are ign |                                   |          | gister  |                    |

| Bits2-0: | 11111SPIFRS2-<br>These three<br>during a d0000                                          | 0<br>0<br>1<br>SPIFRS0<br>ee bits det<br>ata transfe<br>SPIFRS<br>0<br>0                     | 0<br>1<br>0<br>1<br>: SPI Frar<br>ermine th<br>er in mast<br>0<br>1                   | Bit 4Bit 5Bit 6Bit 7ne Size.e number oer mode. TBits Shi12               | f bits to shi<br>They are ign |                                   |          | gister  |                    |

| Bits2-0: | 11111SPIFRS2-<br>These three<br>during a d0                                             | 0<br>0<br>1<br>SPIFRS0<br>ee bits det<br>ata transfe<br>SPIFRS<br>0                          | 0<br>1<br>0<br>1<br>: SPI Frar<br>ermine th<br>er in mast                             | Bit 4Bit 5Bit 6Bit 7ne Size.e number oer mode. TBits Shi1                | f bits to shi<br>They are ign |                                   |          | gister  |                    |

| Bits2-0: | 111111SPIFRS2-<br>These three during a d0000000                                         | 0<br>0<br>1<br>SPIFRS0<br>ee bits det<br>ata transfo<br><b>SPIFRS</b><br>0<br>0<br>1         | 0<br>1<br>0<br>1<br>: SPI Fran<br>ermine th<br>er in mast<br>0<br>1<br>0              | Bit 4Bit 5Bit 6Bit 7ne Size.e number oer mode. TBits Shi123              | f bits to shi<br>They are ign |                                   |          | gister  |                    |

| Bits2-0: | 111111SPIFRS2-<br>These three during a d0000000                                         | 0<br>0<br>1<br>SPIFRS0<br>ee bits det<br>ata transfe<br>SPIFRS<br>0<br>0<br>0<br>1<br>1      | 0<br>1<br>0<br>1<br>SPI Frar<br>ermine th<br>er in mast<br>0<br>1<br>0<br>1<br>0<br>1 | Bit 4Bit 5Bit 6Bit 7ne Size.e number oer mode. TBits Shi1234             | f bits to shi<br>They are ign |                                   |          | gister  |                    |

| Bits2-0: | 111111SPIFRS2-<br>These three during a d0000000                                         | 0<br>0<br>1<br>SPIFRS0<br>ee bits det<br>ata transfe<br>SPIFRS<br>0<br>0<br>0<br>1<br>1<br>0 | 0<br>1<br>0<br>1<br>: SPI Frar<br>ermine th<br>er in mast<br>0<br>1<br>0<br>1<br>0    | Bit 4Bit 5Bit 6Bit 7ne Size.e number oer mode. 7Bits Shi12345            | f bits to shi<br>They are ign |                                   |          | gister  |                    |

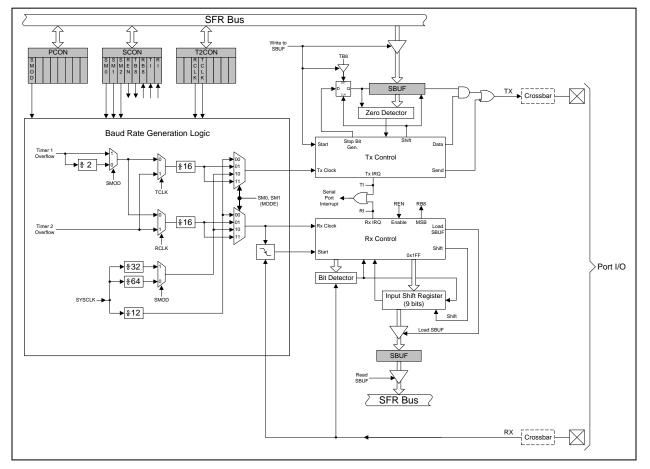

### **16. UART**

The UART is a serial port capable of asynchronous transmission. The UART can function in full duplex mode. In all modes, receive data is buffered in a holding register. This allows the UART to start reception of a second incoming data byte before software has finished reading the previous data byte.

The UART has an associated Serial Control Register (SCON) and a Serial Data Buffer (SBUF) in the SFRs. The single SBUF location provides access to both transmit and receive registers. Reads access the Receive register and writes access the Transmit register automatically.

The UART is capable of generating interrupts if enabled. The UART has two sources of interrupts: a Transmit Interrupt flag, TI (SCON.1) set when transmission of a data byte is complete, and a Receive Interrupt flag, RI (SCON.0) set when reception of a data byte is complete. The UART interrupt flags are not cleared by hardware when the CPU vectors to the interrupt service routine. They must be cleared manually by software. This allows software to determine the cause of the UART interrupt (transmit complete or receive complete).

Figure 16.1. UART Block Diagram

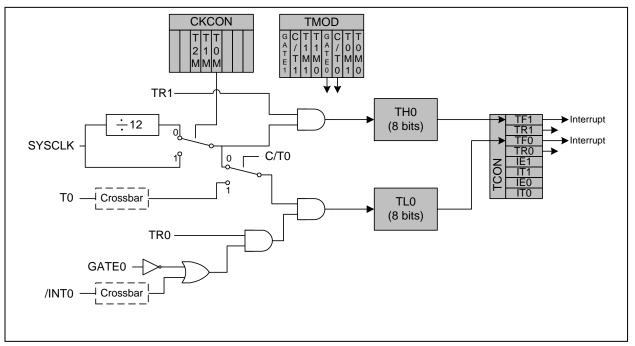

### 17.1.4. Mode 3: Two 8-bit Counter/Timers (Timer 0 Only)

Timer 0 and Timer 1 behave differently in Mode 3. Timer 0 is configured as two separate 8-bit counter/timers held in TL0 and TH0. The counter/timer in TL0 is controlled using the Timer 0 control/status bits in TCON and TMOD: TR0, C/T0, GATE0 and TF0. It can use either the system clock or an external input signal as its timebase. The TH0 register is restricted to a timer function sourced by the system clock. TH0 is enabled using the Timer 1 run control bit TR1. TH0 sets the Timer 1 overflow flag TF1 on overflow and thus controls the Timer 1 interrupt.

Timer 1 is inactive in Mode 3, so with Timer 0 in Mode 3, Timer 1 can be turned off and on by switching it into and out of its Mode 3. When Timer 0 is in Mode 3, Timer 1 can be operated in Modes 0, 1 or 2, but cannot be clocked by external signals nor set the TF1 flag and generate an interrupt. However, the Timer 1 overflow can be used for baud rate generation. Refer to Section 16 (UART) for information on configuring Timer 1 for baud rate generation.

| GATE1<br>Bit7 |                                                                                    | N                                                                                | /W                                       | R/W                                                      | R/W                            | R/W                            | R/W                 | R/W                     | Reset Valu          |