Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                             |

|----------------------------|-------------------------------------------------------------|

| Product Status             | Obsolete                                                    |

| Core Processor             | 8051                                                        |

| Core Size                  | 8-Bit                                                       |

| Speed                      | 25MHz                                                       |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART            |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT          |

| Number of I/O              | 16                                                          |

| Program Memory Size        | 16KB (16K x 8)                                              |

| Program Memory Type        | FLASH                                                       |

| EEPROM Size                | -                                                           |

| RAM Size                   | 1.25K x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.8V ~ 3.6V                                                 |

| Data Converters            | A/D 8x10b                                                   |

| Oscillator Type            | Internal                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                           |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 48-TQFP                                                     |

| Supplier Device Package    | 48-TQFP (7x7)                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f019 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.1. $CIP-51^{TM} CPU$

## 1.1.1. Fully 8051 Compatible

The C8051F018/9 utilizes Silcon Labs' proprietary CIP-51 microcontroller core. The CIP-51 is fully compatible with the MCS-51<sup>TM</sup> instruction set. Standard 803x/805x assemblers and compilers can be used to develop software. The core has all the peripherals included with a standard 8052, including four 16-bit counter/timers, a full-duplex UART, 256 bytes of internal RAM space, 128 byte Special Function Register (SFR) address space, and four byte-wide I/O Ports.

#### 1.1.2. Improved Throughput

The CIP-51 employs a pipelined architecture that greatly increases its instruction throughput over the standard 8051 architecture. In a standard 8051, all instructions except for MUL and DIV take 12 or 24 system clock cycles to execute with a maximum system clock of 12-to-24MHz. By contrast, the CIP-51 core executes 70% of its instructions in one or two system clock cycles, with only four instructions taking more than four system clock cycles.

The CIP-51 has a total of 109 instructions. The number of instructions versus the system clock cycles to execute them is as follows:

| Instructions      | 26 | 50 | 5   | 14 | 7   | 3 | 1   | 2 | 1 |

|-------------------|----|----|-----|----|-----|---|-----|---|---|

| Clocks to Execute | 1  | 2  | 2/3 | 3  | 3/4 | 4 | 4/5 | 5 | 8 |

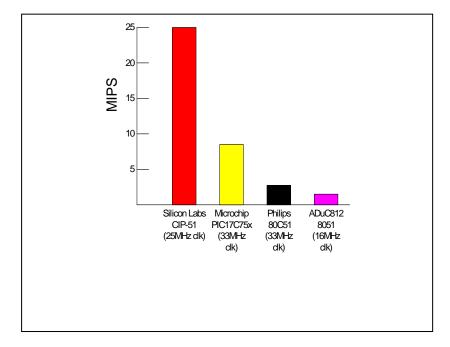

With the CIP-51's maximum system clock at 25MHz, it has a peak throughput of 25MIPS. Figure 1.3 shows a comparison of peak throughputs of various 8-bit microcontroller cores with their maximum system clocks.

Figure 1.3. Comparison of Peak MCU Execution Speeds

## 1.4. Programmable Digital I/O and Crossbar

The standard 8051 Ports (0, 1, 2, and 3) are available on the MCUs. All four ports are pinned out on the F018. Ports 0 and 1 are pinned out on the F019. The Ports not pinned out are still available for software use as general purpose registers. The Port I/O behave like the standard 8051 with a few enhancements.

Each Port I/O pin can be configured as either a push-pull or open-drain output. Also, the "weak pull-ups" which are normally fixed on an 8051 can be globally disabled, providing additional power saving capabilities for low power applications.

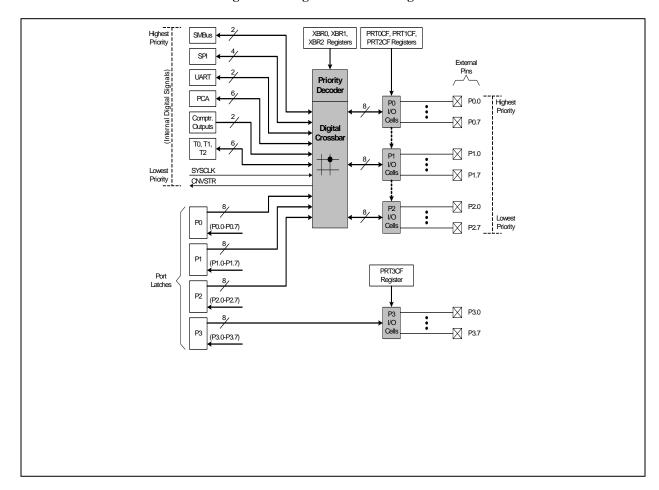

Perhaps the most unique enhancement is the Digital Crossbar. This is essentially a large digital switching network that allows mapping of internal digital system resources to Port I/O pins on P0, P1, and P2. (See Figure 1.7.) Unlike microcontrollers with standard multiplexed digital I/O, all combinations of functions are supported.

The on-board counter/timers, serial buses, HW interrupts, ADC Start of Conversion input, comparator outputs, and other digital signals in the controller can be configured to appear on the Port I/O pins specified in the Crossbar Control registers. This allows the user to select the exact mix of general purpose Port I/O and digital resources needed for his particular application.

Figure 1.7. Digital Crossbar Diagram

## 2. ABSOLUTE MAXIMUM RATINGS\*

| Ambient temperature under bias                                    | 55 to 125°C               |

|-------------------------------------------------------------------|---------------------------|

| Storage Temperature                                               | 65 to 150°C               |

| Voltage on any Pin (except VDD and Port I/O) with respect to DGND | $-0.3V$ to $(VDD + 0.3V)$ |

| Voltage on any Port I/O Pin or /RST with respect to DGND          | 0.3V to 5.8V              |

| Voltage on VDD with respect to DGND                               | 0.3V to 4.2V              |

| Maximum Total current through VDD, AV+, DGND and AGND             | 800mA                     |

| Maximum output current sunk by any Port pin                       | 100mA                     |

| Maximum output current sunk by any other I/O pin                  | 25mA                      |

| Maximum output current sourced by any Port pin                    | 100mA                     |

| Maximum output current sourced by any other I/O pin               | 25mA                      |

<sup>\*</sup>Note: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the devices at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

## 3. GLOBAL DC ELECTRICAL CHARACTERISTICS

-40°C to +85°C unless otherwise specified.

| PARAMETER                   | CONDITIONS                         | MIN | TYP  | MAX | UNITS |

|-----------------------------|------------------------------------|-----|------|-----|-------|

| Analog Supply Voltage       | (Note 1)                           | 2.8 | 3.0  | 3.6 | V     |

| Analog Supply Current       | Internal REF, ADC, Comparators all |     | 1    | 2   | mA    |

|                             | active                             |     |      |     |       |

| Analog Supply Current with  | Internal REF, ADC, Comparators all |     | 5    | 20  | μΑ    |

| analog sub-systems inactive | disabled, oscillator disabled      |     |      |     |       |

| Analog-to-Digital Supply    |                                    |     |      | 0.5 | V     |

| Delta (   VDD – AV+   )     |                                    |     |      |     |       |

| Digital Supply Voltage      |                                    | 2.8 | 3.0  | 3.6 | V     |

| Digital Supply Current with | VDD = 2.8V, $Clock=25MHz$          |     | 12.5 |     | mA    |

| CPU active                  | VDD = 2.8V, $Clock=1MHz$           |     | 0.5  |     | mA    |

|                             | VDD = 2.8V, $Clock=32kHz$          |     | 10   |     | μΑ    |

| Digital Supply Current      | Oscillator not running             |     | 5    |     | μΑ    |

| (shutdown)                  |                                    |     |      |     | -     |

| Digital Supply RAM Data     |                                    |     | 1.5  |     | V     |

| Retention Voltage           |                                    |     |      |     |       |

| Specified Operating         |                                    | -40 |      | +85 | °C    |

| Temperature Range           |                                    |     |      |     |       |

| SYSCLK (System Clock        | (Note 2)                           | 0   |      | 25  | MHz   |

| Frequency)                  |                                    |     |      |     |       |

| Tsysl (SYSCLK Low Time)     |                                    | 18  |      |     | ns    |

| Tsysh (SYSCLK High Time)    |                                    | 18  |      |     | ns    |

Note 1: Analog Supply AV+ must be greater than 1V for VDD monitor to operate.

Note 2: SYSCLK must be at least 32 kHz to enable debugging.

| <b>N</b> T | Ty   | ре   | Descripti | on                                                                          |

|------------|------|------|-----------|-----------------------------------------------------------------------------|

| Name       | F018 | F019 |           |                                                                             |

| P0.0       | 39   | 31   | D I/O     | Port0 Bit0. (See the Port I/O Sub-System section for complete description). |

| P0.1       | 42   | 34   | D I/O     | Port0 Bit1. (See the Port I/O Sub-System section for complete description). |

| P0.2       | 47   | 35   | D I/O     | Port0 Bit2. (See the Port I/O Sub-System section for complete description). |

| P0.3       | 48   | 36   | D I/O     | Port0 Bit3. (See the Port I/O Sub-System section for complete description). |

| P0.4       | 49   | 37   | D I/O     | Port0 Bit4. (See the Port I/O Sub-System section for complete description). |

| P0.5       | 50   | 38   | D I/O     | Port0 Bit5. (See the Port I/O Sub-System section for complete description). |

| P0.6       | 55   | 39   | D I/O     | Port0 Bit6. (See the Port I/O Sub-System section for complete description). |

| P0.7       | 56   | 40   | D I/O     | Port0 Bit7. (See the Port I/O Sub-System section for complete description). |

| P1.0       | 38   | 30   | D I/O     | Port1 Bit0. (See the Port I/O Sub-System section for complete description). |

| P1.1       | 37   | 29   | D I/O     | Port1 Bit1. (See the Port I/O Sub-System section for complete description). |

| P1.2       | 36   | 28   | D I/O     | Port1 Bit2. (See the Port I/O Sub-System section for complete description). |

| P1.3       | 35   | 26   | D I/O     | Port1 Bit3. (See the Port I/O Sub-System section for complete description). |

| P1.4       | 34   | 25   | D I/O     | Port1 Bit4. (See the Port I/O Sub-System section for complete description). |

| P1.5       | 32   | 24   | D I/O     | Port1 Bit5. (See the Port I/O Sub-System section for complete description). |

| P1.6       | 60   | 42   | D I/O     | Port1 Bit6. (See the Port I/O Sub-System section for complete description). |

| P1.7       | 59   | 41   | D I/O     | Port1 Bit7. (See the Port I/O Sub-System section for complete description). |

| P2.0       | 33   |      | D I/O     | Port2 Bit0. (See the Port I/O Sub-System section for complete description). |

| P2.1       | 27   |      | D I/O     | Port2 Bit1. (See the Port I/O Sub-System section for complete description). |

| P2.2       | 54   |      | D I/O     | Port2 Bit2. (See the Port I/O Sub-System section for complete description). |

| P2.3       | 53   |      | D I/O     | Port2 Bit3. (See the Port I/O Sub-System section for complete description). |

| P2.4       | 52   |      | D I/O     | Port2 Bit4. (See the Port I/O Sub-System section for complete description). |

| P2.5       | 51   |      | D I/O     | Port2 Bit5. (See the Port I/O Sub-System section for complete description). |

| P2.6       | 44   |      | D I/O     | Port2 Bit6. (See the Port I/O Sub-System section for complete description). |

| P2.7       | 43   |      | D I/O     | Port2 Bit7. (See the Port I/O Sub-System section for complete description). |

| P3.0       | 26   |      | D I/O     | Port3 Bit0. (See the Port I/O Sub-System section for complete description). |

| P3.1       | 25   |      | D I/O     | Port3 Bit1. (See the Port I/O Sub-System section for complete description). |

| P3.2       | 24   |      | D I/O     | Port3 Bit2. (See the Port I/O Sub-System section for complete description). |

| P3.3       | 23   |      | D I/O     | Port3 Bit3. (See the Port I/O Sub-System section for complete description). |

| P3.4       | 58   |      | D I/O     | Port3 Bit4. (See the Port I/O Sub-System section for complete description). |

| P3.5       | 57   |      | D I/O     | Port3 Bit5. (See the Port I/O Sub-System section for complete description). |

| P3.6       | 46   |      | D I/O     | Port3 Bit6. (See the Port I/O Sub-System section for complete description). |

| P3.7       | 45   |      | D I/O     | Port3 Bit7. (See the Port I/O Sub-System section for complete description). |

Figure 5.4. AMX0CF: AMUX Configuration Register

| ı |      |      |      |      |         |         |         |         |              |

|---|------|------|------|------|---------|---------|---------|---------|--------------|

|   | R/W  | R/W  | R/W  | R/W  | R/W     | R/W     | R/W     | R/W     | Reset Value  |

|   | -    | -    | -    | ı    | AIN67IC | AIN45IC | AIN23IC | AIN01IC | 00000000     |

|   | Bit7 | Bit6 | Bit5 | Bit4 | Bit3    | Bit2    | Bit1    | Bit0    | SFR Address: |

|   |      |      |      |      |         |         |         |         | 0xBA         |

Bits7-4: UNUSED. Read = 0000b; Write = don't care

Bit3: AIN67IC: AIN6, AIN7 Input Pair Configuration Bit

0: AIN6 and AIN7 are independent singled-ended inputs

1: AIN6, AIN7 are (respectively) +, - differential input pair

Bit2: AIN45IC: AIN4, AIN5 Input Pair Configuration Bit

0: AIN4 and AIN5 are independent singled-ended inputs

1: AIN4, AIN5 are (respectively) +, - differential input pair

Bit1: AIN23IC: AIN2, AIN3 Input Pair Configuration Bit

0: AIN2 and AIN3 are independent singled-ended inputs

1: AIN2, AIN3 are (respectively) +, - differential input pair

Bit0: AIN01IC: AIN0, AIN1 Input Pair Configuration Bit

0: AIN0 and AIN1 are independent singled-ended inputs

1: AINO, AIN1 are (respectively) +, - differential input pair

NOTE: The ADC Data Word is in 2's complement format for channels configured as differential.

## C8051F018 C8051F019

#### 8.4. INTERRUPT HANDLER

The CIP-51 includes an extended interrupt system supporting a total of 22 interrupt sources with two priority levels. The allocation of interrupt sources between on-chip peripherals and external inputs pins varies according to the specific version of the device. Each interrupt source has one or more associated interrupt-pending flag(s) located in an SFR. When a peripheral or external source meets a valid interrupt condition, the associated interrupt-pending flag is set to logic 1.

If interrupts are enabled for the source, an interrupt request is generated when the interrupt-pending flag is set. As soon as execution of the current instruction is complete, the CPU generates an LCALL to a predetermined address to begin execution of an interrupt service routine (ISR). Each ISR must end with an RETI instruction, which returns program execution to the next instruction that would have been executed if the interrupt request had not occurred. If interrupts are not enabled, the interrupt-pending flag is ignored by the hardware and program execution continues as normal. (The interrupt-pending flag is set to logic 1 regardless of the interrupt's enable/disable state.)

Each interrupt source can be individually enabled or disabled through the use of an associated interrupt enable bit in an SFR (IE-EIE2). However, interrupts must first be globally enabled by setting the EA bit (IE.7) to logic 1 before the individual interrupt enables are recognized. Setting the EA bit to logic 0 disables all interrupt sources regardless of the individual interrupt-enable settings.

Some interrupt-pending flags are automatically cleared by the hardware when the CPU vectors to the ISR. However, most are not cleared by the hardware and must be cleared by software before returning from the ISR. If an interrupt-pending flag remains set after the CPU completes the return-from-interrupt (RETI) instruction, a new interrupt request will be generated immediately and the CPU will re-enter the ISR after the completion of the next instruction.

#### **8.4.1.** MCU Interrupt Sources and Vectors

The MCUs allocate 12 interrupt sources to on-chip peripherals. Up to 10 additional external interrupt sources are available depending on the I/O pin configuration of the device. Software can simulate an interrupt by setting any interrupt-pending flag to logic 1. If interrupts are enabled for the flag, an interrupt request will be generated and the CPU will vector to the ISR address associated with the interrupt-pending flag. MCU interrupt sources, associated vector addresses, priority order and control bits are summarized in Table 8.4. Refer to the datasheet section associated with a particular on-chip peripheral for information regarding valid interrupt conditions for the peripheral and the behavior of its interrupt-pending flag(s).

#### 8.4.2. External Interrupts

Two of the external interrupt sources (/INT0 and /INT1) are configurable as active-low level-sensitive or active-low edge-sensitive inputs depending on the setting of IT0 (TCON.0) and IT1 (TCON.2). IE0 (TCON.1) and IE1 (TCON.3) serve as the interrupt-pending flag for the /INT0 and /INT1 external interrupts, respectively. If an /INT0 or /INT1 external interrupt is configured as edge-sensitive, the corresponding interrupt-pending flag is automatically cleared by the hardware when the CPU vectors to the ISR. When configured as level sensitive, the interrupt-pending flag follows the state of the external interrupt's input pin. The external interrupt source must hold the input active until the interrupt request is recognized. It must then deactivate the interrupt request before execution of the ISR completes or another interrupt request will be generated.

The remaining four external interrupts (External Interrupts 4-7) are active-low, edge-sensitive inputs. The interrupt-pending flags for these interrupts are in the Port 1 Interrupt Flag Register shown in Figure 13.10.

## 10. EXTERNAL RAM

The C8051F018/9 includes 1024 bytes of RAM mapped into the external data memory space. All of these address locations may be accessed using the external move instruction (MOVX) and the data pointer (DPTR), or using MOVX indirect addressing mode. If the MOVX instruction is used with an 8-bit address operand (such as @R1), then the high byte of the 16-bit address is provided by the External Memory Interface Control Register (EMI0CN as shown in Figure 10.1). Note: the MOVX instruction is also used for writes to the Flash memory. See Section 9 for details. The MOVX instruction accesses XRAM by default (i.e. PSTCL.0 = 0).

For any of the addressing modes the upper 5-bits of the 16-bit external data memory address word are "don't cares". As a result, the 1024-byte RAM is mapped modulo style over the entire 64k external data memory address range. For example, the XRAM byte at address 0x0000 is also at address 0x0400, 0x0800, 0x0C00, 0x1000, etc. This is a useful feature when doing a linear memory fill, as the address pointer doesn't have to be reset when reaching the RAM block boundary.

Figure 10.1. EMI0CN: External Memory Interface Control

| R    | R    | R    | R    | R    | R/W  | R/W    | R/W    | Reset Value  |

|------|------|------|------|------|------|--------|--------|--------------|

| -    | -    | -    | -    | -    | -    | PGSEL1 | PGSEL0 | 00000000     |

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1   | Bit0   | SFR Address: |

|      |      |      |      |      |      |        |        | OxAF         |

Bits 7-2: Not Used – reads 000000b

Bits 1-0: PGSEL[1:0]: XRAM Page Select Bits

The XRAM Page Select Bits provide the high byte of the 16-bit external data memory address when using an 8-bit MOVX command, effectively selecting a 256-byte page of RAM. The upper 6-bits are "don't cares", so the 1k address blocks are repeated modulo over the entire 64k external data memory address space.

00: xxxxxx00b 01: xxxxxx01b 10: xxxxxx10b 11: xxxxxx11b

## C8051F018 C8051F019

## 13. PORT INPUT/OUTPUT

The MCUs have a wide array of digital resources, which are available through four digital I/O ports, P0, P1, P2 and P3. Each of the pins on Ports 0, 1, and 2 can be defined as either its corresponding port I/O or one of the internal digital resources assigned as shown in Figure 13.1. The designer has complete control over which functions are assigned, limited only by the number of physical I/O pins available on the selected package (the C8051F018 has all four ports pinned out, and the C8051F019 has P0 and P1). This resource assignment flexibility is achieved through the use of a Priority CrossBar Decoder. (Note that the state of a Port I/O pin can always be read in the corresponding Port latch regardless of the Crossbar settings).

The CrossBar assigns the selected internal digital resources to the I/O pins based on the Priority Decode Table 13.1. The registers XBR0, XBR1, and XBR2, defined in Figure 13.3, Figure 13.4, and Figure 13.5 are used to select an internal digital function or let an I/O pin default to being a Port I/O. The crossbar functions identically for each MCU, with the caveat that P2 is not pinned out on the C8051F019. Digital resources assigned to port pins that are not pinned out cannot be accessed.

All Port I/Os are 5V tolerant (Refer to Figure 13.2 for the port cell circuit.) The Port I/O cells are configured as either push-pull or open-drain in the Port Configuration Registers (PRT0CF, PRT1CF, PRT2CF, PRT3CF). Complete Electrical Specifications for Port I/O are given in Table 13.2.

## 13.1. Priority Cross Bar Decoder

One of the design goals of this MCU family was to make the entire palette of digital resources available to the designer even on reduced pin count packages. The Priority CrossBar Decoder provides an elegant solution to the problem of connecting the internal digital resources to the physical I/O pins.

The Priority CrossBar Decode (Table 13.1) assigns a priority to each I/O function, starting at the top with the SMBus. As the table illustrates, when selected, its two signals will be assigned to Pin 0 and 1 of I/O Port 0. The decoder always fills I/O bits from LSB to MSB starting with Port 0, then Port 1, finishing if necessary with Port 2. If you choose not to use a resource, the next function down on the table will fill the priority slot. In this way it is possible to choose only the functions required by the design, making full use of the available I/O pins. Also, any extra Port I/O are grouped together for more convenient use in application code.

Registers XBR0, XBR1 and XBR2 are used to assign the digital I/O resources to the physical I/O Port pins. It is important to understand that when the SMBus, SPI Bus, or UART is selected, the crossbar assigns all pins associated with the selected bus. It would be impossible for instance to assign the RX pin from the UART function without also assigning the TX function. Standard Port I/Os appear contiguously after the prioritized functions have been assigned. For example, if you choose functions that take the first 14 Port I/O (P0.[7:0], P1.[5:0]), you would have 18 Port I/O left unused by the crossbar (P1.[7:6], P2 and P3).

#### 13.2. Port I/O Initialization

Port I/O initialization is straightforward. Registers XBR0, XBR1 and XBR2 must be loaded with the appropriate values to select the digital I/O functions required by the design. Setting the XBARE bit in XBR2 to 1 enables the CrossBar. Until the Crossbar is enabled, the external pins remain as standard Ports in input mode regardless of the XBRn Register settings. For given XBRn Register settings, one can determine the I/O pin-out using the Priority Decode Table; as an alternative, the Code Configuration Wizard function of the IDE software will determine the Port I/O pin-assignments based on the XBRn Register settings.

The output driver characteristics of the I/O pins are defined using the Port Configuration Registers PRT0CF, PRT1CF, PRT2CF and PRT3CF (see Figure 13.7, Figure 13.9, Figure 13.12, and Figure 13.14). Each Port Output driver can be configured as either Open Drain or Push-Pull. This is required even for the digital resources selected in the XBRn registers and is not automatic. The only exception to this is the SMBus (SDA, SCL) and UART Receive (RX, when in mode 0) pins which are Open-drain regardless of the PRTnCF settings. When the WEAKPUD bit in XBR2 is 0, a weak pullup is enabled for all Port I/O configured as open-drain. WEAKPUD does

## 13.3. General Purpose Port I/O

Each MCU has four byte-wide, bi-directional parallel ports that can be used general purpose I/O. Each port is accessed through a corresponding special function register (SFR) that is both byte addressable and bit addressable. When writing to a port, the value written to the SFR is latched to maintain the output data value at each pin. When reading, the logic levels of the port's input pins are returned regardless of the XBRn settings (i.e. even when the pin is assigned to another signal by the Crossbar, the Port Register can always still read its corresponding Port I/O pin). The exception to this is the execution of the *read-modify-write* instructions. The *read-modify-write* instructions when operating on a port SFR are the following: ANL, ORL, XRL, JBC, CPL, INC, DEC, DJNZ and MOV, CLR or SET, when the destination is an individual bit in a port SFR. For these instructions, the value of the port register (not the pin) is read, modified, and written back to the SFR.

## 13.4. Configuring Ports Which are not Pinned Out

P2 and P3 are not pinned out on the C8051F019. These port registers are still available for software use in the C8051F019. Whether used or not in software, it is recommended not to let these port drivers go to high impedance state. This is prevented after reset by having the weak pull-ups enabled as described in the XBR2 register. It is recommended that each output driver for ports not pinned out should be configured as push-pull using the corresponding PRTnCF register. This will inhibit a high impedance state even if the weak pull-up is disabled.

Figure 13.6. P0: Port0 Register

| Г |      |      |      |      |      |      |      |                   |              |

|---|------|------|------|------|------|------|------|-------------------|--------------|

|   | R/W               | Reset Value  |

|   | P0.7 | P0.6 | P0.5 | P0.4 | P0.3 | P0.2 | P0.1 | P0.0              | 11111111     |

|   | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0              | SFR Address: |

|   |      |      |      |      |      |      |      | (bit addressable) | 0x80         |

Bits7-0: P0.[7:0]

(Write – Output appears on I/O pins per XBR0, XBR1, and XBR2 Registers)

0: Logic Low Output.

1: Logic High Output (high-impedance if corresponding PRT0CF.n bit = 0)

(Read – Regardless of XBR0, XBR1, and XBR2 Register settings).

0: P0.n pin is logic low.

1: P0.n pin is logic high.

Figure 13.7. PRT0CF: Port0 Configuration Register

| R/W  | Reset Value  |

|------|------|------|------|------|------|------|------|--------------|

|      |      |      |      |      |      |      |      | 00000000     |

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | SFR Address: |

|      |      |      |      |      |      |      |      | 0xA4         |

Bits7-0: PRT0CF.[7:0]: Output Configuration Bits for P0.7-P0.0 (respectively)

0: Corresponding P0.n Output mode is Open-Drain.

1: Corresponding P0.n Output mode is Push-Pull.

(Note: When SDA, SCL, and RX appear on any of the P0 I/O, each are open-drain

regardless of the value of PRT0CF).

#### 14.6.1. Control Register

The SMBus Control register SMB0CN is used to configure and control the SMBus interface. All of the bits in the register can be read or written by software. Two of the control bits are also affected by the SMBus hardware. The Serial Interrupt flag (SI, SMB0CN.3) is set to logic 1 by the hardware when a valid serial interrupt condition occurs. It can only be cleared by software. The Stop flag (STO, SMB0CN.4) is cleared to logic 0 by hardware when a STOP condition is present on the bus.

Setting the ENSMB flag to logic 1 enables the SMBus interface. Clearing the ENSMB flag to logic 0 disables the SMBus interface and removes it from the bus. Momentarily clearing the ENSMB flag and then resetting it to logic 1 will reset a SMBus communication. However, ENSMB should not be used to temporarily remove a device from the bus since the bus state information will be lost. Instead, the Assert Acknowledge (AA) flag should be used to temporarily remove the device from the bus (see description of AA flag below).

Setting the Start flag (STA, SMB0CN.5) to logic 1 will put the SMBus in a master mode. If the bus is free, the SMBus hardware will generate a START condition. If the bus is not free, the SMBus hardware waits for a STOP condition to free the bus and then generates a START condition after a 5µs delay per the SMB0CR value. (In accordance with the SMBus protocol, the SMBus interface also considers the bus free if the bus is idle for 50µs and no STOP condition was recognized.) If STA is set to logic 1 while the SMBus is in master mode and one or more bytes have been transferred, a repeated START condition will be generated. To ensure proper operation, the STO flag should be explicitly cleared before setting STA to a logic 1.

When the Stop flag (STO, SMB0CN.4) is set to logic 1 while the SMBus interface is in master mode, the hardware generates a STOP condition on the SMBus. In a slave mode, the STO flag may be used to recover from an error condition. In this case, a STOP condition is not generated on the SMBus, but the SMBus hardware behaves as if a STOP condition has been received and enters the "not addressed" slave receiver mode. The SMBus hardware automatically clears the STO flag to logic 0 when a STOP condition is detected on the bus.

The Serial Interrupt flag (SI, SMB0CN.3) is set to logic 1 by hardware when the SMBus interface enters one of 27 possible states. If interrupts are enabled for the SMBus interface, an interrupt request is generated when the SI flag is set. The SI flag must be cleared by software. While SI is set to logic 1, the clock-low period of the serial clock will be stretched and the serial transfer is suspended.

The Assert Acknowledge flag (AA, SMB0CN.2) is used to set the level of the SDA line during the acknowledge clock cycle on the SCL line. Setting the AA flag to logic 1 will cause an ACKNOWLEDGE (low level on SDA) to be sent during the acknowledge cycle if the device has been addressed. Setting the AA flag to logic 0 will cause a NOT ACKNOWLEDGE (high level on SDA) to be sent during acknowledge cycle. After the transmission of a byte in slave mode, the slave can be temporarily removed from the bus by clearing the AA flag. The slave's own address and general call address will be ignored. To resume operation on the bus, the AA flag must be reset to logic 1 to allow the slave's address to be recognized.

Setting the SMBus Free Timer Enable bit (FTE, SMB0CN.1) to logic 1 enables the SMBus Free Timeout feature. If SCL and SDA remain high for the SMBus Free Timeout given in the SMBus Clock Rate Register (Figure 14.5), the bus will be considered free and a Start will be generated if pending. The bus free period should be greater than 50µs.

Setting the SMBus timeout enable bit (TOE, SMB0CN.0) to logic 1 enables Timer 3 to count up when the SCL line is low and Timer 3 is enabled. If Timer 3 overflows, a Timer 3 interrupt will be generated, which will alert the CPU that a SMBus SCL low timeout has occurred.

## 14.6.3. Data Register

The SMBus Data register SMB0DAT holds a byte of serial data to be transmitted or one that has just been received. Data remains stable in the register as long as SI is set to logic 1. Software can safely read or write to the data register when the SI flag is set. Software should not attempt to access the SMB0DAT register when the SMBus is enabled and the SI flag is cleared to logic 0 since the hardware may be in the process of shifting a byte of data in or out of the register.

Data in SMB0DAT is always shifted out MSB first. After a byte has been received, the first bit of received data is located at the MSB of SMB0DAT. While data is being shifted out, data on the bus is simultaneously being shifted in. Therefore, SMB0DAT always contains the last data byte present on the bus. Thus, in the event of lost arbitration, the transition from master transmitter to slave receiver is made with the correct data in SMB0DAT.

Figure 14.6. SMB0DAT: SMBus Data Register

| R/W  | Reset Value  |

|------|------|------|------|------|------|------|------|--------------|

|      |      |      |      |      |      |      |      | 00000000     |

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | SFR Address: |

|      |      |      |      |      |      |      |      | 0xC2         |

Bits7-0: SMB0DAT: SMBus Data.

The SMB0DAT register contains a byte of data to be transmitted on the SMBus serial interface or a byte that has just been received on the SMBus serial interface. The CPU can read from or write to this register whenever the SI serial interrupt flag (SMB0CN.3) is set to logic one. The serial data in the register remains stable as long as the SI flag is set. When the SI flag is not set, the system may be in the process of shifting data in/out and the CPU should not attempt to access this register.

#### 14.6.4. Address Register

The SMB0ADR Address register holds the slave address for the SMBus interface. In slave mode, the seven most-significant bits hold the 7-bit slave address. The least significant bit, bit 0, is used to enable the recognition of the general call address (0x00). If bit 0 is set to logic 1, the general call address will be recognized. Otherwise, the general call address is ignored. The contents of this register are ignored when the SMBus hardware is operating in master mode.

Figure 14.7. SMB0ADR: SMBus Address Register

| R/W  | Reset Value  |

|------|------|------|------|------|------|------|------|--------------|

| SLV6 | SLV5 | SLV4 | SLV3 | SLV2 | SLV1 | SLV0 | GC   | 00000000     |

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | SFR Address: |

|      |      |      |      |      |      |      |      | 0xC3         |

Bits7-1: SLV6-SLV0: SMBus Slave Address.

These bits are loaded with the 7-bit slave address to which the SMBus will respond when operating as a slave transmitter or slave receiver. SLV6 is the most significant bit of the address and corresponds to the first bit of the address byte received on the SMBus.

Bit0: GC: General Call Address Enable.

This bit is used to enable general call address (0x00) recognition.

0: General call address is ignored.

1: General call address is recognized.

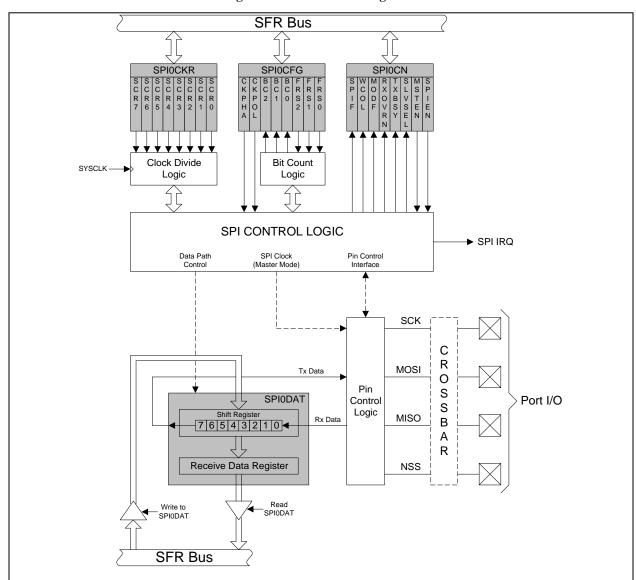

## 15. SERIAL PERIPHERAL INTERFACE BUS

The Serial Peripheral Interface (SPI) provides access to a four-wire, full-duplex, serial bus. SPI supports the connection of multiple slave devices to a master device on the same bus. A separate slave-select signal (NSS) is used to select a slave device and enable a data transfer between the master and the selected slave. Multiple masters on the same bus are also supported. Collision detection is provided when two or more masters attempt a data transfer at the same time. The SPI can operate as either a master or a slave. When the SPI is configured as a master, the maximum data transfer rate (bits/sec) is one-half the system clock frequency.

When the SPI is configured as a slave, the maximum data transfer rate (bits/sec) for full-duplex operation is 1/10 the system clock frequency, provided that the master issues SCK, NSS, and the serial input data synchronously with the system clock. If the master issues SCK, NSS, and the serial input data asynchronously, the maximum data transfer rate (bits/sec) must be less that 1/10 the system clock frequency. In the special case where the master only wants to transmit data to the slave and does not need to receive data from the slave (i.e. half-duplex operation), the SPI slave can receive data at a maximum data transfer rate (bits/sec) of ½ the system clock frequency. This is provided that the master issues SCK, NSS, and the serial input data synchronously with the system clock.

Figure 15.1. SPI Block Diagram

## 15.4. SPI Special Function Registers

The SPI is accessed and controlled through four special function registers in the system controller: SPI0CN Control Register, SPI0DAT Data Register, SPI0CFG Configuration Register, and SPI0CKR Clock Rate Register. The four special function registers related to the operation of the SPI Bus are described in the following section.

Figure 15.5. SPI0CFG: SPI Configuration Register

| R/W   | R/W   | R    | R    | R    | R/W     | R/W     | R/W     | Reset Value  |

|-------|-------|------|------|------|---------|---------|---------|--------------|

| СКРНА | CKPOL | BC2  | BC1  | BC0  | SPIFRS2 | SPIFRS1 | SPIFRS0 | 00000111     |

| Bit7  | Bit6  | Bit5 | Bit4 | Bit3 | Bit2    | Bit1    | Bit0    | SFR Address: |

|       |       |      |      |      |         |         |         | 0x9A         |

Bit7: CKPHA: SPI Clock Phase.

This bit controls the SPI clock phase.

0: Data sampled on first edge of SCK period.1: Data sampled on second edge of SCK period.

Bit6: CKPOL: SPI Clock Polarity.

This bit controls the SPI clock polarity.

0: SCK line low in idle state.1: SCK line high in idle state.

Bits5-3: BC2-BC0: SPI Bit Count.

Indicates which of the up to 8 bits of the SPI word have been transmitted.

| BC2-BC0 |   |   | Bit Transmitted |

|---------|---|---|-----------------|

| 0       | 0 | 0 | Bit 0 (LSB)     |

| 0       | 0 | 1 | Bit 1           |

| 0       | 1 | 0 | Bit 2           |

| 0       | 1 | 1 | Bit 3           |

| 1       | 0 | 0 | Bit 4           |

| 1       | 0 | 1 | Bit 5           |

| 1       | 1 | 0 | Bit 6           |

| 1       | 1 | 1 | Bit 7 (MSB)     |

Bits2-0: SPIFRS2-SPIFRS0: SPI Frame Size.

These three bits determine the number of bits to shift in/out of the SPI shift register during a data transfer in master mode. They are ignored in slave mode.

|   | <b>SPIFRS</b> | Bits Shifted |   |

|---|---------------|--------------|---|

| 0 | 0             | 0            | 1 |

| 0 | 0             | 1            | 2 |

| 0 | 1             | 0            | 3 |

| 0 | 1             | 1            | 4 |

| 1 | 0             | 0            | 5 |

| 1 | 0             | 1            | 6 |

| 1 | 1             | 0            | 7 |

| 1 | 1             | 1            | 8 |

#### Figure 15.7. SPI0CKR: SPI Clock Rate Register

|   | R/W  | Reset Value  |

|---|------|------|------|------|------|------|------|------|--------------|

|   | SCR7 | SCR6 | SCR5 | SCR4 | SCR3 | SCR2 | SCR1 | SCR0 | 00000000     |

| _ | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | SFR Address: |

|   |      |      |      |      |      |      |      |      | 0x9D         |

## Bits7-0: SCR7-SCR0: SPI Clock Rate

These bits determine the frequency of the SCK output when the SPI module is configured for master mode operation. The SCK clock frequency is a divided down version of the system clock, and is given in the following equations:

$f_{SCK} = 0.5 * f_{SYSCLK} / (SPI0CKR + 1), \qquad \qquad \text{for } 0 \leq \text{ SPI0CKR} \leq 255,$

Figure 15.8. SPI0DAT: SPI Data Register

| R/W  | Reset Value  |

|------|------|------|------|------|------|------|------|--------------|

|      |      |      |      |      |      |      |      | 00000000     |

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | SFR Address: |

|      |      |      |      |      |      |      |      | 0x9B         |

Bits7-0: SPI0DAT: SPI0 Transmit and Receive Data.

The SPI0DAT register is used to transmit and receive SPI data. Writing data to SPI0DAT places the data immediately into the shift register and initiates a transfer when in Master Mode. A read of SPI0DAT returns the contents of the receive buffer.

#### 16.1.2. Mode 1: 8-Bit UART, Variable Baud Rate

Mode 1 provides standard asynchronous, full duplex communication using a total of 10 bits per data byte: one start bit, eight data bits (LSB first), and one stop bit (see the timing diagram in Figure 16.4). Data are transmitted from the TX pin and received at the RX pin (see the interconnection diagram in Figure 16.5). On receive, the eight data bits are stored in SBUF and the stop bit goes into RB8 (SCON.2).

Data transmission begins when an instruction writes a data byte to the SBUF register. The TI Transmit Interrupt Flag (SCON.1) is set at the end of the transmission (the beginning of the stop-bit time). Data reception can begin any time after the REN Receive Enable bit (SCON.4) is set to logic 1. After the stop bit is received, the data byte will be loaded into the SBUF receive register if the following conditions are met: RI must be logic 0, and if SM2 is logic 1, the stop bit must be logic 1.

If these conditions are met, the eight bits of data are stored in SBUF, the stop bit is stored in RB8 and the RI flag is set. If these conditions are not met, SBUF and RB8 will not be loaded and the RI flag will not be set. An interrupt will occur if enabled when either TI or RI is set.

Figure 16.4. UART Mode 1 Timing Diagram

The baud rate generated in Mode 1 is a function of timer overflow. The UART can use Timer 1 operating in 8-bit Counter/Timer with Auto-Reload Mode, or Timer 2 operating in Baud Rate Generator Mode to generate the baud rate (note that the TX and RX clock sources are selected separately). On each timer overflow event (a rollover from all ones (0xFF for Timer 1, 0xFFFF for Timer 2) to zero), a clock is sent to the baud rate logic.

When Timer 1 is selected as a baud rate source, the SMOD bit (PCON.7) selects whether or not to divide the Timer 1 overflow rate by two. On reset, the SMOD bit is logic 0, thus selecting the lower speed baud rate by default. The SMOD bit affects the baud rate generated by Timer 1 as follows:

```

Mode 1 Baud Rate = (1/32) * T1_OVERFLOWRATE (when the SMOD bit is set to logic 0). Mode 1 Baud Rate = (1/16) * T1_OVERFLOWRATE (when the SMOD bit is set to logic 1).

```

When Timer 2 is selected as a baud rate source, the baud rate generated by Timer 2 is as follows:

```

Mode 1 Baud Rate = (1/16) * T2 OVERFLOWRATE.

```

The Timer 1 overflow rate is determined by the Timer 1 clock source (T1CLK) and reload value (TH1). The frequency of T1CLK can be selected as SYSCLK, SYSCLK/12, or an external clock source. The Timer 1 overflow rate can be calculated as follows:

$$T1\_OVERFLOWRATE = T1CLK / (256 - TH1).$$

For example, assume TMOD = 0x20.

If T1M (CKCON.4) is logic 1, then the above equation becomes:

$$T1\_OVERFLOWRATE = (SYSCLK)/(256 - TH1).$$

If T1M (CKCON.4) is logic 0, then the above equation becomes:

$$T1\_OVERFLOWRATE = (SYSCLK/12) / (256 - TH1).$$

The Timer 2 overflow rate, when in *Baud Rate Generator Mode* and using an internal clock source, is determined solely by the Timer 2 16-bit reload value (RCAP2H:RCAP2L). The Timer 2 clock source is fixed at SYSCLK/2. The Timer 2 overflow rate can be calculated as follows:

#### $T2\_OVERFLOWRATE = (SYSCLK/2) / (65536 - [RCAP2H:RCAP2L]).$

Timer 2 can be selected as the baud rate generator for RX and/or TX by setting RCLK (T2CON.5) and/or TCLK (T2CON.4), respectively. When either RCLK or TCLK is set to logic 1, Timer 2 interrupts are automatically disabled and the timer is forced into *Baud Rate Generator Mode* with SYSCLK/2 as its clock source. If a different timebase is required, setting the C/T2 bit (T2CON.1) to logic 1 will allow Timer 2 to be clocked from the external input pin T2. See the Timers section for complete timer configuration details.

RS-232

LEVEL

XLTR

TX

C8051Fxxx

OR

MCU

TX

C8051Fxxx

TX

C8051Fxxx

TX

C8051Fxxx

TX

C8051Fxxx

Figure 16.5. UART Modes 1, 2, and 3 Interconnect Diagram

#### 16.1.3. Mode 2: 9-Bit UART, Fixed Baud Rate

Mode 2 provides asynchronous, full-duplex communication using a total of eleven bits per data byte: a start bit, 8 data bits (LSB first), a programmable ninth data bit, and a stop bit (see timing diagram in Figure 16.6). On transmit, the ninth data bit is determined by the value in TB8 (SCON.3). It can be assigned the value of the parity flag P in the PSW or used in multiprocessor communications. On receive, the ninth data bit goes into RB8 (SCON.2) and the stop bit is ignored.

Data transmission begins when an instruction writes a data byte to the SBUF register. The TI Transmit Interrupt Flag (SCON.1) is set at the end of the transmission (the beginning of the stop-bit time). Data reception can begin any time after the REN Receive Enable bit (SCON.4) is set to logic 1. After the stop bit is received, the data byte will be loaded into the SBUF receive register if the following conditions are met: RI must be logic 0, and if SM2 is logic 1, the 9<sup>th</sup> bit must be logic 1.

If these conditions are met, the eight bits of data are stored in SBUF, the ninth bit is stored in RB8 and the RI flag is set. If these conditions are not met, SBUF and RB8 will not be loaded and the RI flag will not be set. An interrupt will occur if enabled when either TI or RI are set.

The baud rate in Mode 2 is a direct function of the system clock frequency as follows:

$$Mode\ 2\ Baud\ Rate = 2^{SMOD}*(SYSCLK/64).$$

The SMOD bit (PCON.7) selects whether to divide SYSCLK by 32 or 64. In the formula, 2 is raised to the power SMOD, resulting in a baud rate of either 1/32 or 1/64 of the system clock frequency. On reset, the SMOD bit is logic 0, thus selecting the lower speed baud rate by default.

MARK

START BIT

D0

D1

D2

D3

D4

D5

D6

D7

D8

STOP BIT

BIT TIMES

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

Figure 16.6. UART Modes 2 and 3 Timing Diagram

#### 16.1.4. Mode 3: 9-Bit UART, Variable Baud Rate

Mode 3 is the same as Mode 2 in all respects except the baud rate is variable. The baud rate is determined in the same manner as for Mode 1. Mode 3 operation transmits 11 bits: a start bit, 8 data bits (LSB first), a programmable ninth data bit, and a stop bit. Timer 1 or Timer 2 overflows generate the baud rate just as with Mode 1. In summary, Mode 3 transmits using the same protocol as Mode 2 but with Mode 1 baud rate generation.

# C8051F018 C8051F019

## 17. TIMERS

Each MCU implements four counter/timers: three are 16-bit counter/timers compatible with those found in the standard 8051, and one is a 16-bit timer for use with the ADC, SMBus, or for general purpose use. These can be used to measure time intervals, count external events and generate periodic interrupt requests. Timer 0 and Timer 1 are nearly identical and have four primary modes of operation. Timer 2 offers additional capabilities not available in Timers 0 and 1. Timer 3 is similar to Timer 2, but without the capture or Baud Rate Generator modes.

| Timer 0 and Timer 1:                    | Timer 2:                              | Timer 3:                      |

|-----------------------------------------|---------------------------------------|-------------------------------|

| 13-bit counter/timer                    | 16-bit counter/timer with auto-reload | 16-bit timer with auto-reload |

| 16-bit counter/timer                    | 16-bit counter/timer with capture     |                               |

| 8-bit counter/timer with auto-reload    | Baud rate generator                   |                               |

| Two 8-bit counter/timers (Timer 0 only) |                                       |                               |

When functioning as a timer, the counter/timer registers are incremented on each clock tick. Clock ticks are derived from the system clock divided by either one or twelve as specified by the Timer Clock Select bits (T2M-T0M) in CKCON. The twelve-clocks-per-tick option provides compatibility with the older generation of the 8051 family. Applications that require a faster timer can use the one-clock-per-tick option.

When functioning as a counter, a counter/timer register is incremented on each high-to-low transition at the selected input pin for T0, T1, or T2. Events with a frequency of up to one-fourth the system clock's frequency can be counted. The input signal need not be periodic, but it should be held at a given level for at least two full system clock cycles to ensure the level is sampled.

#### 17.1. Timer 0 and Timer 1

Timer 0 and Timer 1 are accessed and controlled through SFRs. Each counter/timer is implemented as a 16-bit register accessed as two separate bytes: a low byte (TL0 or TL1) and a high byte (TH0 or TH1). The Counter/Timer Control (TCON) register is used to enable Timer 0 and Timer 1 as well as indicate their status. Both counter/timers operate in one of four primary modes selected by setting the Mode Select bits M1-M0 in the Counter/Timer Mode (TMOD) register. Each timer can be configured independently. Following is a detailed description of each operating mode.

#### 17.1.1. Mode 0: 13-bit Counter/Timer

Timer 0 and Timer 1 operate as a 13-bit counter/timer in Mode 0. The following describes the configuration and operation of Timer 0. However, both timers operate identically and Timer 1 is configured in the same manner as described for Timer 0.

The TH0 register holds the eight MSBs of the 13-bit counter/timer. TL0 holds the five LSBs in bit positions TL0.4-TL0.0. The three upper bits of TL0 (TL0.7-TL0.5) are indeterminate and should be masked out or ignored when reading. As the 13-bit timer register increments and overflows from 0x1FFF (all ones) to 0x0000, the timer overflow flag TF0 (TCON.5) is set and an interrupt will occur if enabled.

The C/T0 bit (TMOD.2) selects the counter/timer's clock source. Clearing C/T selects the system clock as the input for the timer. When C/T0 is set to logic 1, high-to-low transitions at the selected input pin increment the timer register. (Refer to Port I/O Section 13.1 for information on selecting and configuring external I/O pins.)

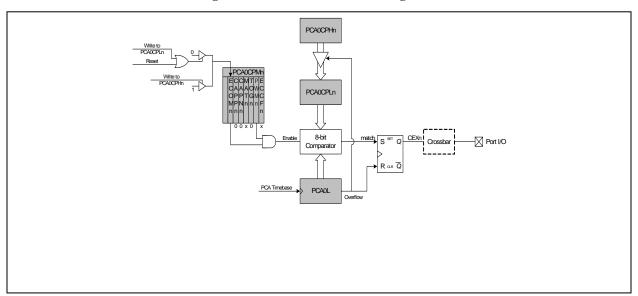

#### 18.1.4. Pulse Width Modulator Mode

All of the modules can be used independently to generate pulse width modulated (PWM) outputs on their respective CEXn pin. The frequency of the output is dependent on the timebase for the PCA counter/timer. The duty cycle of the PWM output signal is varied using the module's PCA0CPLn capture/compare register. When the value in the low byte of the PCA counter/timer (PCA0L) is equal to the value in PCA0CPLn, the output on the CEXn pin will be set. When the count value in PCA0L overflows, the CEXn output will be reset (see Figure 18.6). Also, when the counter/timer low byte (PCA0L) overflows from 0xFF to 0x00, PCA0CPLn is reloaded automatically with the value stored in the PCA0CPHn without software intervention. It is good practice to write to PCA0CPHn instead of PCA0CPLn to avoid glitches in the digital comparator. Setting the ECOMn and PWMn bits in the PCA0CPMn register enables Pulse Width Modulator mode.

Figure 18.6. PCA PWM Mode Diagram

Figure 18.9. PCA0MD: PCA Mode Register

| R/W  | Reset Value  |

|------|------|------|------|------|------|------|------|--------------|

| CIDL | -    | -    | -    | -    | CPS1 | CPS0 | ECF  | 00000000     |

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | SFR Address: |

|      |      |      |      |      |      |      |      | 0xD9         |

Bit7: CIDL: PCA Counter/Timer Idle Control.

Specifies PCA behavior when CPU is in Idle Mode.

0: PCA continues to function normally while the system controller is in Idle Mode.

1: PCA operation is suspended while the system controller is in Idle Mode.

Bits6-3: UNUSED. Read = 0000b, Write = don't care.

Bits2-1: CPS1-CPS0: PCA Counter/Timer Pulse Select.

These bits select the timebase source for the PCA counter.

| CPS1 | CPS0 | Timebase                                                              |

|------|------|-----------------------------------------------------------------------|

| 0    | 0    | System clock divided by 12                                            |

| 0    | 1    | System clock divided by 4                                             |

| 1    | 0    | Timer 0 overflow                                                      |

| 1    | 1    | High-to-low transitions on ECI (max rate = system clock divided by 4) |

Bit0: ECF: PCA Counter/Timer Overflow Interrupt Enable.

This bit sets the masking of the PCA Counter/Timer Overflow (CF) interrupt.

0: Disable the CF interrupt.

1: Enable a PCA Counter/Timer Overflow interrupt request when CF (PCA0CN.7) is set.