#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | 80C51                                                                      |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 60MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | POR, PWM, WDT                                                              |

| Number of I/O              | 34                                                                         |

| Program Memory Size        | 128KB (128K x 8)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 8K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-LQFP                                                                    |

| Supplier Device Package    | 44-VQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at89c51re2-rltum |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Table 3. C51 Core SFRs

| Mnemonic | Add | Name                   | 7  | 6  | 5  | 4   | 3   | 2  | 1  | 0 |

|----------|-----|------------------------|----|----|----|-----|-----|----|----|---|

| ACC      | E0h | Accumulator            |    |    |    |     |     |    |    |   |

| В        | F0h | B Register             |    |    |    |     |     |    |    |   |

| PSW      | D0h | Program Status Word    | CY | AC | F0 | RS1 | RS0 | OV | F1 | Р |

| SP       | 81h | Stack Pointer          |    |    |    |     |     |    |    |   |

| DPL      | 82h | Data Pointer Low byte  |    |    |    |     |     |    |    |   |

| DPH      | 83h | Data Pointer High byte |    |    |    |     |     |    |    |   |

#### Table 4. System Management SFRs

| Mnemonic | Add | Name                     | 7       | 6       | 5     | 4      | 3    | 2    | 1          | 0     |

|----------|-----|--------------------------|---------|---------|-------|--------|------|------|------------|-------|

| PCON     | 87h | Power Control            | SMOD1_0 | SMOD0_0 | -     | POF    | GF1  | GF0  | PD         | IDL   |

| AUXR     | 8Eh | Auxiliary Register 0     | -       | -       | MO    | XRS2   | XRS1 | XRS0 | EXTRA<br>M | AO    |

| AUXR1    | A2h | Auxiliary Register 1     | EES     | SP9     | U2    | -      | GF2  | 0    | -          | DPS   |

| CKRL     | 97h | Clock Reload Register    | -       | -       | -     | -      | -    | -    | -          | -     |

| BMSEL    | 92h | Bank Memory Select       | MBO2    | MBO1    | MBO0  |        | -    | FBS2 | FBS1       | FBS0  |

| CKCON0   | 8Fh | Clock Control Register 0 | TWIX2   | WDX2    | PCAX2 | SIX2_0 | T2X2 | T1X2 | T0X2       | X2    |

| CKCON1   | AFh | Clock Control Register 1 | -       | -       | -     | -      | -    | -    | SIX2_1     | SPIX2 |

#### Table 5. Interrupt SFRs

| Mnemonic | Add | Name                              | 7  | 6    | 5    | 4   | 3     | 2    | 1     | 0    |

|----------|-----|-----------------------------------|----|------|------|-----|-------|------|-------|------|

| IEN0     | A8h | Interrupt Enable Control 0        | EA | EC   | ET2  | ES  | ET1   | EX1  | ET0   | EX0  |

| IEN1     | B1h | Interrupt Enable Control 1        | -  | -    | -    | -   | ES_1  | ESPI | ETWI  | EKBD |

| IPH0     | B7h | Interrupt Priority Control High 0 | -  | PPCH | PT2H | PSH | PT1H  | PX1H | PT0H  | PX0H |

| IPL0     | B8h | Interrupt Priority Control Low 0  | -  | PPCL | PT2L | PSL | PT1L  | PX1L | PT0L  | PX0L |

| IPH1     | B3h | Interrupt Priority Control High 1 | -  | -    | -    | -   | PSH_1 | SPIH | IE2CH | KBDH |

| IPL1     | B2h | Interrupt Priority Control Low 1  | -  | -    | -    | -   | PSL_1 | SPIL | IE2CL | KBDL |

#### Table 6. Port SFRs

| Mnemonic | Add | Name         | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----------|-----|--------------|---|---|---|---|---|---|---|---|

| P0       | 80h | 8-bit Port 0 |   |   |   |   |   |   |   |   |

| P1       | 90h | 8-bit Port 1 |   |   |   |   |   |   |   |   |

| P2       | A0h | 8-bit Port 2 |   |   |   |   |   |   |   |   |

| P3       | B0h | 8-bit Port 3 |   |   |   |   |   |   |   |   |

| P4       | C0h | 8-bit Port 4 |   |   |   |   |   |   |   |   |

| Enhanced    | In comparison to the original 80C52, the AT89C51RE2 implements some new features, which                                                                                                                     |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Features    | are:                                                                                                                                                                                                        |

|             | X2 option                                                                                                                                                                                                   |

|             | Dual Data Pointer                                                                                                                                                                                           |

|             | Extended RAM                                                                                                                                                                                                |

|             | Extended stack                                                                                                                                                                                              |

|             | Programmable Counter Array (PCA)                                                                                                                                                                            |

|             | Hardware Watchdog                                                                                                                                                                                           |

|             | SPI interface                                                                                                                                                                                               |

|             | 4-level interrupt priority system                                                                                                                                                                           |

|             | power-off flag                                                                                                                                                                                              |

|             | ONCE mode                                                                                                                                                                                                   |

|             | ALE disabling                                                                                                                                                                                               |

|             | Enhanced features on the UART and the timer 2                                                                                                                                                               |

| X2 Feature  | The AT89C51RE2 core needs only 6 clock periods per machine cycle. This feature called 'X2' provides the following advantages:                                                                               |

|             | • Divide frequency crystals by 2 (cheaper crystals) while keeping same CPU power.                                                                                                                           |

|             | • Save power consumption while keeping same CPU power (oscillator power saving).                                                                                                                            |

|             | • Save power consumption by dividing dynamically the operating frequency by 2 in operating and idle modes.                                                                                                  |

|             | <ul> <li>Increase CPU power by 2 while keeping same crystal frequency.</li> </ul>                                                                                                                           |

|             | In order to keep the original C51 compatibility, a divider by 2 is inserted between the XTAL1 sig-<br>nal and the main clock input of the core (phase generator). This divider may be disabled by software. |

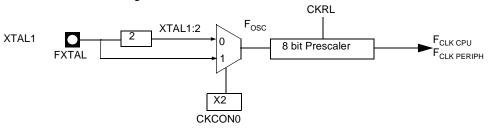

| Description | The clock for the whole circuit and peripherals is first divided by two before being used by the CPU core and the peripherals.                                                                              |

|             | This allows any cyclic ratio to be accepted on XTAL1 input. In X2 mode, as this divider is bypassed, the signals on XTAL1 must have a cyclic ratio between 40 to 60%.                                       |

|             | Figure 2 shows the clock generation block diagram. X2 bit is validated on the rising edge of the                                                                                                            |

Figure 2 shows the clock generation block diagram. X2 bit is validated on the rising edge of the XTAL1÷2 to avoid glitches when switching from X2 to STD mode. Figure 3 shows the switching mode waveforms.

Figure 2. Clock Generation Diagram

0010 70F6JNZ LOOP ; check for 0 terminator 0012 05A2 INC AUXR1 ; (optional) restore DPS

INC is a short (2 bytes) and fast (12 clocks) way to manipulate the DPS bit in the AUXR1 SFR. However, note that the INC instruction does not directly force the DPS bit to a particular state, but simply toggles it. In simple routines, such as the block move example, only the fact that DPS is toggled in the proper sequence matters, not its actual value. In other words, the block move routine works the same whether DPS is '0' or '1' on entry. Observe that without the last instruction (INC AUXR1), the routine will exit with DPS in the opposite state.

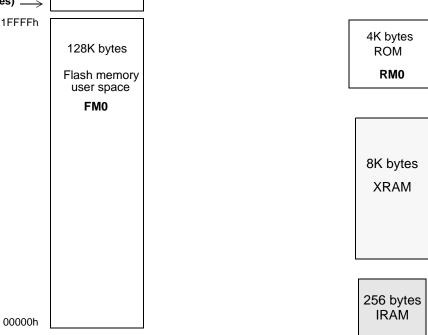

#### **Memory Architecture**

AT89C51RE2 features several on-chip memories:

- Flash memory: • containing 128 Kbytes of program memory (user space) organized into 128 bytes pages.

- Boot ROM: • 4K bytes for boot loader.

- 8K bytes internal XRAM •

#### **Physical memory** organisation

Figure 5. Physical memory organisation

Fuse Configuration Byte(1 byte) FCB Hardware Security (1 byte)  $\longrightarrow$  HSB

Column Latches (128 bytes)  $\longrightarrow$

1FFFFh

#### FCON Register

Table 23. FCON Register

FCON Register (S:D1h) Flash Control Register

| 7          | 6               | 5                                                | 4                                                                                                                               | 3              | 2               | 1            | 0     |  |  |

|------------|-----------------|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------|--------------|-------|--|--|

| FPL3       | FPL2            | FPL1                                             | FPL0                                                                                                                            | FPS            | FMOD2           | FMOD1        | FMOD0 |  |  |

| Bit Number | Bit<br>Mnemonic | Description                                      |                                                                                                                                 |                |                 |              |       |  |  |

| 7-4        | FPL3:0          |                                                  | Programming Launch Command Bits<br>Write 5Xh followed by AXh to launch the programming according to FMOD2:0. (see<br>Fable 26.) |                |                 |              |       |  |  |

| 3          | FPS             | When this bit i<br>The MOVX @<br>When this bit i | DPTR, A instruis cleared:                                                                                                       |                | the columns lat | ·            | pace  |  |  |

| 2-0        | FMOD2:0         | Flash Mode<br>These bits allo<br>See Table 25.   | ow to select the                                                                                                                | e target memor | y area and oper | ation on FM0 |       |  |  |

Reset Value= 0000 0000b

#### Table 29. Write MOVX @DPTR,A

| FPS of<br>FCCON | EA | XRAM<br>ERAM | CL FM0 |

|-----------------|----|--------------|--------|

| 0               | Х  | winner       |        |

| 1               | 1  |              | winner |

|                 | 0  | winner       |        |

Table 30. MOVC A, @A+DPTR executed from External code EA=0

| FMOD2:0 | FBS<br>(Fetch) | MBO<br>(Target) | MOVC A,@A+DPTR     |

|---------|----------------|-----------------|--------------------|

| Х       | Х              | Х               | Read External Code |

Table 31. MOVC A, @A+DPTR executed from External code EA=1, PC>=0x8000, FBS=Bank3

| FMOD2:0 | MBO<br>(Target) | DPTR      | MOVC A,@A+DPTR                                                   |

|---------|-----------------|-----------|------------------------------------------------------------------|

| x       | х               | < 0x8000  | Depends on FLB2:0<br>Can Returns Random value, for secured part. |

|         | Х               | >= 0x8000 | External code read                                               |

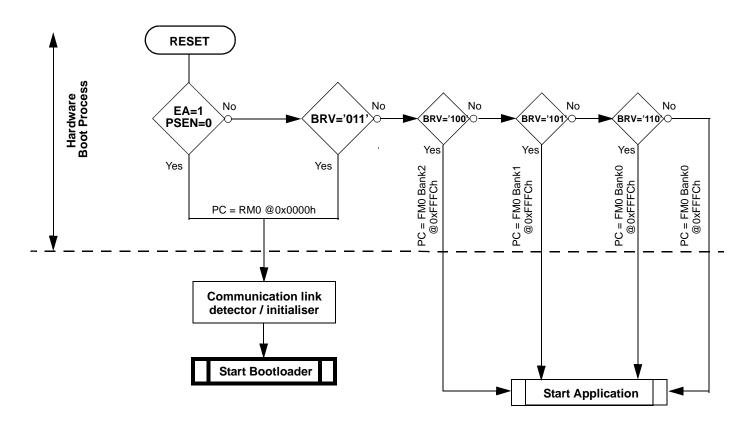

### Bootloader Description

Entry points After reset only one bootloader entry point is possible. This entry point stands at address 0x0000 of the boot ROM memory. This entry point executes the boot process of the bootloader.

The bootloader entry point can be selected through two processes:

At reset, if the hardware conditions are applied, the bootloader entry point is accessed and executed.

At reset, if the hardware conditions are not set and the BRV2-0 is programmed '011', the bootloader entry point is accessed and the bootprocess is started.

#### Boot Process Description

The boot process consists in three main operations:

- The hardware boot process request detection

- The communication link detection (Uart or OCD)

- The start-up of the bootloader

Hardware boot process request detection The hardware boot process request is detected when the hardware conditions (under reset, EA=1 and PSEN=0) are received by the processor or when no hardware condition is applied and the BRV2:0 is configured '011'.

Communication link detection

- Two interfaces are available for ISP:

- UART0

- OCD UART

#### **Erasing commands** The erasing command is supported by the following areas:

#### Table 39. Memory space & Erase

| Memory/Information Family | Comments/Restriction      |

|---------------------------|---------------------------|

| FLASH                     | need security level check |

Nothing is done on the other areas.

FLASH

The erasing command on the Flash memory:

- erases the four physical flash memory banks (from address 0000h to 1FFFFh).

- the HSB (Hardware Security Byte) is set at NO\_PROTECTION:

– FLB2.0 = '111'

## Registers

Table 46. TCON Register

TCON (S:88h) Timer/Counter Control Register

| 7          | 6               | 5               | 4                                                                                                                                                                               | 3                                                  | 2   | 1   | 0                 |  |

|------------|-----------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-----|-----|-------------------|--|

| TF1        | TR1             | TF0             | TR0                                                                                                                                                                             | IE1                                                | IT1 | IE0 | IT0               |  |

| Bit Number | Bit<br>Mnemonic | Description     |                                                                                                                                                                                 |                                                    |     |     |                   |  |

| 7          | TF1             |                 | rdware when p                                                                                                                                                                   | processor vecto<br>ounter overflow                 |     |     | ws.               |  |

| 6          | TR1             |                 | Control Bit<br>ff Timer/Count<br>Timer/Counter                                                                                                                                  |                                                    |     |     |                   |  |

| 5          | TF0             | Cleared by ha   | <b>Timer 0 Overflow Flag</b><br>Cleared by hardware when processor vectors to interrupt routine.<br>Set by hardware on Timer/Counter overflow, when Timer 0 register overflows. |                                                    |     |     |                   |  |

| 4          | TR0             |                 | Control Bit<br>ff Timer/Count<br>Timer/Counter                                                                                                                                  |                                                    |     |     |                   |  |

| 3          | IE1             |                 | rdware when i                                                                                                                                                                   | nterrupt is proce                                  |     |     | 1).               |  |

| 2          | IT1             | Clear to select |                                                                                                                                                                                 | <b>t</b><br>ve (level triggere<br>ive (edge trigge |     |     | <sup>-</sup> 1#). |  |

| 1          | IEO             | Cleared by ha   | Interrupt 0 Edge Flag<br>Cleared by hardware when interrupt is processed if edge-triggered (see IT0).<br>Set by hardware when external interrupt is detected on INT0# pin.      |                                                    |     |     |                   |  |

| 0          | ITO             | Clear to select |                                                                                                                                                                                 | <b>t</b><br>ve (level triggere<br>ive (edge trigge | ,   | • • | <sup>-</sup> 0#). |  |

Reset Value = 0000 0000b

AT89C51RE2

## Baud Rate Selection for UART 1 for Mode 1 and 3

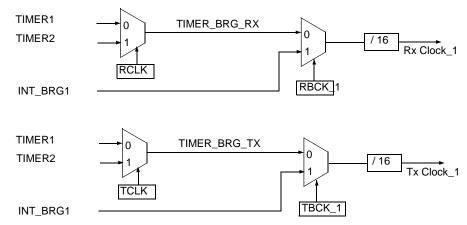

The Baud Rate Generator for transmit and receive clocks can be selected separately via the T2CON and BDRCON\_1 registers.

Figure 41. Baud Rate Selection for UART 1

Table 67. Baud Rate Selection Table UART 1

| TCLK<br>(T2CON) | RCLK<br>(T2CON) | TBCK_1<br>(BDRCON_1) | RBCK_1<br>(BDRCON_1) | Clock Source<br>UART Tx_1 | Clock Source<br>UART Rx_1 |

|-----------------|-----------------|----------------------|----------------------|---------------------------|---------------------------|

| 0               | 0               | 0                    | 0                    | Timer 1                   | Timer 1                   |

| 1               | 0               | 0                    | 0                    | Timer 2                   | Timer 1                   |

| 0               | 1               | 0                    | 0                    | Timer 1                   | Timer 2                   |

| 1               | 1               | 0                    | 0                    | Timer 2                   | Timer 2                   |

| Х               | 0               | 1                    | 0                    | INT_BRG_1                 | Timer 1                   |

| Х               | 1               | 1                    | 0                    | INT_BRG_1                 | Timer 2                   |

| 0               | Х               | 0                    | 1                    | Timer 1                   | INT_BRG_1                 |

| 1               | Х               | 0                    | 1                    | Timer 2                   | INT_BRG_1                 |

| Х               | Х               | 1                    | 1                    | INT_BRG_1                 | INT_BRG_1                 |

#### Table 77. PCON Register

PCON - Power Control Register (87h)

| 7             | 6               | 5                                              | 4                                                                                                                                                    | 3                 | 2          | 1  | 0   |  |  |

|---------------|-----------------|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------|----|-----|--|--|

| SMOD1_0       | SMOD0_0         | -                                              | POF                                                                                                                                                  | GF1               | GF0        | PD | IDL |  |  |

| Bit<br>Number | Bit<br>Mnemonic |                                                | Description                                                                                                                                          |                   |            |    |     |  |  |

| 7             | SMOD1_0         |                                                | erial port Mode bit 1 for UART<br>et to select double baud rate in mode 1, 2 or 3.                                                                   |                   |            |    |     |  |  |

| 6             | SMOD0_0         | Cleared to se                                  | erial port Mode bit 0 for UART<br>leared to select SM0 bit in SCON register.<br>et to select FE bit in SCON register.                                |                   |            |    |     |  |  |

| 5             | -               | Reserved<br>The value rea                      | Reserved the value read from this bit is indeterminate. Do not set this bit.                                                                         |                   |            |    |     |  |  |

| 4             | POF             | Cleared to re                                  | ower-Off Flag<br>leared to recognize next reset type.<br>et by hardware when VCC rises from 0 to its nominal voltage. Can also be set by<br>oftware. |                   |            |    |     |  |  |

| 3             | GF1             | Cleared by u                                   | General purpose Flag<br>Cleared by user for general purpose usage.<br>Set by user for general purpose usage.                                         |                   |            |    |     |  |  |

| 2             | GF0             | Cleared by u                                   | General purpose Flag<br>Cleared by user for general purpose usage.<br>Set by user for general purpose usage.                                         |                   |            |    |     |  |  |

| 1             | PD              | Cleared by h                                   | Power-Down mode bit<br>Cleared by hardware when reset occurs.<br>Set to enter power-down mode.                                                       |                   |            |    |     |  |  |

| 0             | IDL             | Idle mode bi<br>Cleared by h<br>Set to enter i | ardware when                                                                                                                                         | interrupt or rese | et occurs. |    |     |  |  |

Reset Value = 00X1 0000b Not bit addressable

Power-off flag reset value will be 1 only after a power on (cold reset). A warm reset doesn't affect the value of this bit.

# AT89C51RE2

| Table 104. | Status in  | Slave Recei  | ver Mode | (Continued)  |

|------------|------------|--------------|----------|--------------|

|            | oluluo III | 010101100001 | voi mouo | (Contantaoa) |

|                |                                                                                                        | Application S      | oftware | e Respo | nse |    |                                                                                                                                                                                      |  |

|----------------|--------------------------------------------------------------------------------------------------------|--------------------|---------|---------|-----|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Status         |                                                                                                        | To/from SSDAT      |         | To SS   | CON |    |                                                                                                                                                                                      |  |

| Code<br>(SSCS) | Status of the 2-wire bus and 2-wire hardware                                                           |                    | STA     | ѕто     | SI  | АА | Next Action Taken By 2-wire Software                                                                                                                                                 |  |

|                |                                                                                                        | Read data byte or  | 0       | 0       | 0   | 0  | Switched to the not addressed slave mode; no<br>recognition of own SLA or GCA<br>Switched to the not addressed slave mode; own                                                       |  |

|                |                                                                                                        | Read data byte or  | 0       | 0       | 0   | 1  | SLA will be recognised; GCA will be recognised if GC=logic 1                                                                                                                         |  |

| 98h            | 98h Previously addressed with<br>general call; data has been<br>received; NOT ACK has been<br>returned | Read data byte or  | 1       | 0       | 0   | 0  | Switched to the not addressed slave mode; no recognition of own SLA or GCA. A START condition will be transmitted when the bus becomes free                                          |  |

|                |                                                                                                        | Read data byte     | 1       | 0       | 0   | 1  | Switched to the not addressed slave mode; own<br>SLA will be recognised; GCA will be recognised if<br>GC=logic 1. A START condition will be<br>transmitted when the bus becomes free |  |

|                |                                                                                                        | No SSDAT action or | 0       | 0       | 0   | 0  | Switched to the not addressed slave mode; no<br>recognition of own SLA or GCA<br>Switched to the not addressed slave mode; own                                                       |  |

|                |                                                                                                        | No SSDAT action or | 0       | 0       | 0   | 1  | SLA will be recognised; GCA will be recognised if GC=logic 1                                                                                                                         |  |

| A0h            | A STOP condition or repeated<br>START condition has been<br>received while still addressed<br>as slave | No SSDAT action or | 1       | 0       | 0   | 0  | Switched to the not addressed slave mode; no<br>recognition of own SLA or GCA. A START<br>condition will be transmitted when the bus<br>becomes free                                 |  |

|                |                                                                                                        | No SSDAT action    | 1       | 0       | 0   | 1  | Switched to the not addressed slave mode; own<br>SLA will be recognised; GCA will be recognised if<br>GC=logic 1. A START condition will be<br>transmitted when the bus becomes free |  |

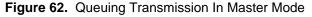

When a transmission is in progress a new data can be queued and sent as soon as transmission has been completed. So it is possible to transmit bytes without latency, useful in some applications.

The SPTE bit in SPSCR is set as long as the transmission buffer is free. It means that the user application can write SPDAT with the data to be transmitted until the SPTE becomes cleared.

Figure 62 shows a queuing transmission in master mode. Once the Byte 1 is ready, it is immediately sent on the bus. Meanwhile an other byte is prepared (and the SPTE is cleared), it will be sent at the end of the current transmission. The next data must be ready before the end of the current transmission.

In slave mode it is almost the same except it is the external master that start the transmission.

Also, in slave mode, if no new data is ready, the last value received will be the next data byte transmitted.

# AT89C51RE2

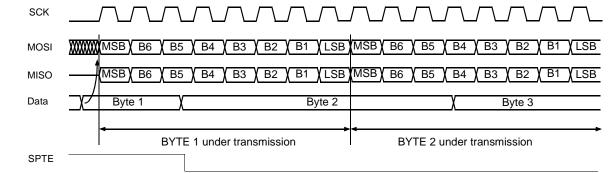

# **Power Monitor** The POR/PFD function monitors the internal power-supply of the CPU core memories and the peripherals, and if needed, suspends their activity when the internal power supply falls below a safety threshold. This is achieved by applying an internal reset to them.

By generating the Reset the Power Monitor insures a correct start up when AT89C51RE2 is powered up.

**Description** In order to startup and maintain the microcontroller in correct operating mode, V<sub>CC</sub> has to be stabilized in the V<sub>CC</sub> operating range and the oscillator has to be stabilized with a nominal amplitude compatible with logic level VIH/VIL.

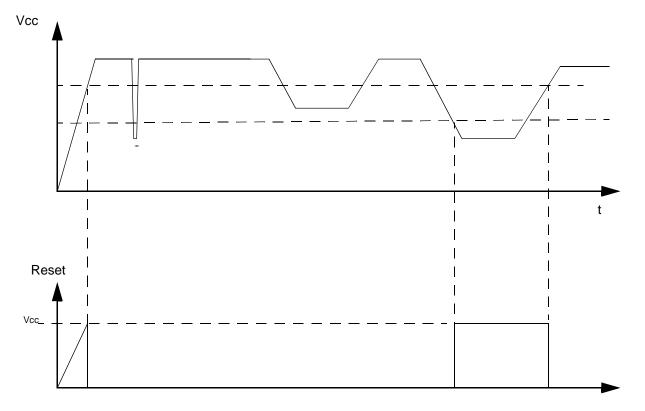

These parameters are controlled during the three phases: power-up, normal operation and power going down. See Figure 66.

Figure 66. Power Monitor Block Diagram

Note: 1. Once XTAL1 High and low levels reach above and below VIH/VIL. a 1024 clock period delay will extend the reset coming from the Power Fail Detect. If the power falls below the Power Fail Detect threshold level, the Reset will be applied immediately.

The Voltage regulator generates a regulated internal supply for the CPU core the memories and the peripherals. Spikes on the external Vcc are smoothed by the voltage regulator.

The Power fail detect monitor the supply generated by the voltage regulator and generate a reset if this supply falls below a safety threshold as illustrated in the Figure 67 below.

Figure 67. Power Fail Detect

When the power is applied, the Power Monitor immediately asserts a reset. Once the internal supply after the voltage regulator reach a safety level, the power monitor then looks at the XTAL clock input. The internal reset will remain asserted until the Xtal1 levels are above and below VIH and VIL. Further more. An internal counter will count 1024 clock periods before the reset is de-asserted.

If the internal power supply falls below a safety level, a reset is immediately asserted.

## **Power-off Flag**

The power-off flag allows the user to distinguish between a "cold start" reset and a "warm start" reset.

A cold start reset is the one induced by  $V_{CC}$  switch-on. A warm start reset occurs while  $V_{CC}$  is still applied to the device and could be generated for example by an exit from power-down.

The power-off flag (POF) is located in PCON register (Table 118). POF is set by hardware when  $V_{CC}$  rises from 0 to its nominal voltage. The POF can be set or cleared by software allowing the user to determine the type of reset.

#### Table 118. PCON Register

PCON - Power Control Register (87h)

| 7             | 6               | 5                                                 | 4                                                                          | 3                            | 2                 | 1               | 0        |  |  |

|---------------|-----------------|---------------------------------------------------|----------------------------------------------------------------------------|------------------------------|-------------------|-----------------|----------|--|--|

| SMOD1         | SMOD0           | -                                                 | POF                                                                        | GF1                          | GF0               | PD              | IDL      |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                       |                                                                            |                              |                   |                 |          |  |  |

| 7             | SMOD1           | •                                                 | erial port Mode bit 1<br>Set to select double baud rate in mode 1, 2 or 3. |                              |                   |                 |          |  |  |

| 6             | SMOD0           |                                                   |                                                                            | SCON register.<br>register.  |                   |                 |          |  |  |

| 5             | -               | <b>Reserved</b><br>The value rea                  | d from this bit i                                                          | s indeterminate              | . Do not set this | s bit.          |          |  |  |

| 4             | POF             |                                                   | ognize next re                                                             |                              | s nominal volta   | ge. Can also be | e set by |  |  |

| 3             | GF1             |                                                   |                                                                            | ourpose usage.<br>ose usage. |                   |                 |          |  |  |

| 2             | GF0             |                                                   |                                                                            | ourpose usage.<br>ose usage. |                   |                 |          |  |  |

| 1             | PD              |                                                   | mode bit<br>rdware when re<br>ower-down mo                                 |                              |                   |                 |          |  |  |

| 0             | IDL             | Idle mode bit<br>Cleared by ha<br>Set to enter id | rdware when ir                                                             | nterrupt or rese             | t occurs.         |                 |          |  |  |

Reset Value = 00X1 0000b Not bit addressable

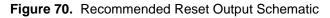

#### **Reset Output**

As detailed in Section "Hardware Watchdog Timer", page 124, the WDT generates a 96-clock period pulse on the RST pin. In order to properly propagate this pulse to the rest of the application in case of external capacitor or power-supply supervisor circuit, a 1 k $\Omega$  resistor must be added as shown Figure 70.

| Table 121. AC Parameters for a Variab | e Clock |

|---------------------------------------|---------|

|---------------------------------------|---------|

| Symbol            | Туре | Standard<br>Clock | X2 Clock  | X parameter for<br>-M <sup>(1)</sup> range | X parameter for<br>-L <sup>(2)</sup> range | Units |

|-------------------|------|-------------------|-----------|--------------------------------------------|--------------------------------------------|-------|

| T <sub>LHLL</sub> | Min  | 2 T - x           | T - x     | 15                                         | 15                                         | ns    |

| T <sub>AVLL</sub> | Min  | Т - х             | 0.5 T - x | 20                                         | 20                                         | ns    |

| T <sub>LLAX</sub> | Min  | Т - х             | 0.5 T - x | 20                                         | 20                                         | ns    |

| T <sub>LLIV</sub> | Max  | 4 T - x           | 2 T - x   | 35                                         | 35                                         | ns    |

| T <sub>LLPL</sub> | Min  | Т - х             | 0.5 T - x | 15                                         | 15                                         | ns    |

| T <sub>PLPH</sub> | Min  | 3 T - x           | 1.5 T - x | 25                                         | 25                                         | ns    |

| T <sub>PLIV</sub> | Max  | 3 T - x           | 1.5 T - x | 45                                         | 45                                         | ns    |

| T <sub>PXIX</sub> | Min  | х                 | х         | 0                                          | 0                                          | ns    |

| T <sub>PXIZ</sub> | Max  | T - x             | 0.5 T - x | 15                                         | 15                                         | ns    |

| T <sub>AVIV</sub> | Max  | 5 T - x           | 2.5 T - x | 45                                         | 45                                         | ns    |

| T <sub>PLAZ</sub> | Max  | х                 | х         | 10                                         | 10                                         | ns    |

Notes: 1. '-L ' refers to 2V - 5.5V version.

2. ' -M ' refers to 4.5V to 5.5V version.

# Document Revision History

| Changes from                   | 1. | Modified ordering information.                      |

|--------------------------------|----|-----------------------------------------------------|

| 7663B to 7663C                 | 2. | Various grammatical corections throughout document. |

| Changes from<br>7663C to 7663D | 1. | TWI interface added.                                |

| Changes from                   | 1. | Removed 64 and 68 pins package product version.     |

| 7663D to 7663E                 | 2. | Minor correction on Table 69 on page 102.           |

# AT89C51RE2

| Ir                                                                                      | terrupt                                        | 71                                                                                                                   |

|-----------------------------------------------------------------------------------------|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| R                                                                                       | egisters                                       | 73                                                                                                                   |

|                                                                                         |                                                |                                                                                                                      |

| Timer                                                                                   | 2                                              | 77                                                                                                                   |

| A                                                                                       | uto-Reload Mode                                | 77                                                                                                                   |

| Р                                                                                       | rogrammable Clock-Output                       | 78                                                                                                                   |

| R                                                                                       | egisters                                       | 80                                                                                                                   |

| _                                                                                       |                                                |                                                                                                                      |

| -                                                                                       | ammable Counter Array PCA                      |                                                                                                                      |

|                                                                                         | CA Capture Mode                                |                                                                                                                      |

|                                                                                         | 6-bit Software Timer/ Compare Mode             |                                                                                                                      |

| Н                                                                                       | igh Speed Output Mode                          | 91                                                                                                                   |

| Р                                                                                       | ulse Width Modulator Mode                      | 92                                                                                                                   |

| Р                                                                                       | CA Watchdog Timer                              | 93                                                                                                                   |

|                                                                                         |                                                |                                                                                                                      |

|                                                                                         | I/O Port                                       |                                                                                                                      |

| F                                                                                       | raming Error Detection                         | 94                                                                                                                   |

| A                                                                                       | utomatic Address Recognition                   | 95                                                                                                                   |

|                                                                                         | egisters                                       |                                                                                                                      |

| В                                                                                       | aud Rate Selection for UART 0 for Mode 1 and 3 | 98                                                                                                                   |

| В                                                                                       | aud Rate Selection for UART 1 for Mode 1 and 3 | 99                                                                                                                   |

| U                                                                                       | ART Registers 1                                | 103                                                                                                                  |

|                                                                                         |                                                |                                                                                                                      |

|                                                                                         |                                                |                                                                                                                      |

|                                                                                         | upt System 1                                   |                                                                                                                      |

| R                                                                                       | egisters 1                                     | 110                                                                                                                  |

| R                                                                                       |                                                | 110                                                                                                                  |

| R<br>Ir                                                                                 | egisters                                       | 110<br>117                                                                                                           |

| R<br>Ir<br><b>Powe</b>                                                                  | egisters                                       | 110<br>117<br>1 <b>18</b>                                                                                            |

| R<br>Ir<br><b>Powe</b> l<br>Ir                                                          | egisters                                       | 110<br>117<br>1 <b>18</b><br>118                                                                                     |

| R<br>Ir<br><b>Powe</b><br>Ir<br>Ic                                                      | egisters                                       | 110<br>117<br>1 <b>18</b><br>118<br>118                                                                              |

| R<br>Ir<br><b>Powe</b><br>Ir<br>Ic<br>P                                                 | egisters                                       | 110<br>117<br>1 <b>18</b><br>118<br>118<br>118                                                                       |

| R<br>Ir<br><b>Powe</b><br>Ir<br>Ic<br>P                                                 | egisters                                       | 110<br>117<br>1 <b>18</b><br>118<br>118<br>118                                                                       |

| R<br>Ir<br><b>Powe</b> l<br>Ir<br>Ic<br>R                                               | egisters                                       | 110<br>117<br>1 <b>18</b><br>118<br>118<br>118<br>121                                                                |

| R<br>Ir<br>Power<br>Ir<br>Ic<br>P<br>R<br><b>Oscill</b>                                 | egisters                                       | 110<br>117<br><b>18</b><br>118<br>118<br>118<br>121                                                                  |

| R<br>Ir<br>Ir<br>Ic<br>P<br>R<br><b>Oscill</b>                                          | egisters                                       | 110<br>117<br><b>18</b><br>118<br>118<br>118<br>121<br><b>22</b><br>122                                              |

| R<br>Ir<br>Ir<br>Ic<br>P<br>R<br><b>Oscill</b>                                          | egisters                                       | 110<br>117<br><b>18</b><br>118<br>118<br>118<br>121<br><b>22</b><br>122                                              |

| R<br>Ir<br>Ir<br>Ic<br>P<br>R<br><b>Oscill</b><br>R<br>F                                | egisters                                       | 110<br>117<br>1 <b>18</b><br>118<br>118<br>118<br>121<br>122<br>122<br>123                                           |

| R<br>Ir<br>Ir<br>Ic<br>P<br>R<br>Oscill<br>R<br>F<br>Hardv                              | egisters                                       | 110<br>117<br>1 <b>18</b><br>118<br>118<br>121<br>122<br>122<br>122                                                  |

| R<br>Ir<br>Powel<br>Ir<br>Ic<br>P<br>R<br><b>Oscill</b><br>R<br>F<br><b>Hardv</b><br>U  | egisters                                       | 110<br>117<br>1 <b>18</b><br>118<br>118<br>118<br>121<br>122<br>122<br>123<br>123                                    |

| R<br>Ir<br>Powel<br>Ir<br>Ic<br>P<br>R<br><b>Oscill</b><br>R<br>F<br><b>Hardv</b><br>U  | egisters                                       | 110<br>117<br>1 <b>18</b><br>118<br>118<br>118<br>121<br>122<br>122<br>123<br>123                                    |

| R<br>Ir<br>Ir<br>Ic<br>P<br>R<br>Oscill<br>R<br>F<br>Hardv<br>U<br>W                    | egisters                                       | 110<br>117<br>1 <b>18</b><br>118<br>118<br>118<br>121<br>122<br>122<br>123<br>124<br>124<br>125                      |

| R<br>Ir<br>Ir<br>Ic<br>P<br>R<br>Oscill<br>R<br>F<br>Hardw<br>U<br>W<br>Reduc           | egisters                                       | 110<br>117<br>1 <b>18</b><br>118<br>118<br>118<br>121<br>122<br>122<br>123<br>124<br>124<br>124<br>124               |

| R<br>Ir<br>Power<br>Ir<br>Ic<br>P<br>R<br>Oscill<br>R<br>F<br>Hardw<br>U<br>W<br>Reduce | egisters                                       | 110<br>117<br>1 <b>18</b><br>118<br>118<br>118<br>121<br>122<br>122<br>122<br>122<br>123<br>124<br>124<br>125<br>126 |