#

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                                   |

|----------------------------|---------------------------------------------------------------------------------------|

| Core Processor             | 78K/0R                                                                                |

| Core Size                  | 16-Bit                                                                                |

| Speed                      | 20MHz                                                                                 |

| Connectivity               | CSI, I <sup>2</sup> C, LINbus, UART/USART                                             |

| Peripherals                | DMA, LCD, LVD, POR, PWM, WDT                                                          |

| Number of I/O              | 60                                                                                    |

| Program Memory Size        | 128KB (128K x 8)                                                                      |

| Program Memory Type        | FLASH                                                                                 |

| EEPROM Size                | -                                                                                     |

| RAM Size                   | 7K x 8                                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                           |

| Data Converters            | A/D 12x12b; D/A 2x12b                                                                 |

| Oscillator Type            | Internal                                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                     |

| Mounting Type              | Surface Mount                                                                         |

| Package / Case             | 100-LQFP                                                                              |

| Supplier Device Package    | 100-LFQFP (14x14)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f1505agc-ueu-ax |

|                            |                                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 19.4.4 Interrupt request hold                               |     |

|-------------------------------------------------------------|-----|

| CHAPTER 20 KEY INTERRUPT FUNCTION                           | 771 |

|                                                             |     |

| 20.1 Functions of Key Interrupt                             |     |

| 20.2 Configuration of Key Interrupt                         |     |

| 20.3 Register Controlling Key Interrupt                     |     |

| CHAPTER 21 STANDBY FUNCTION                                 |     |

| 21.1 Standby Function and Configuration                     |     |

| 21.1.1 Standby function                                     |     |

| 21.1.2 Registers controlling standby function               |     |

| 21.2 Standby Function Operation                             |     |

| 21.2.1 HALT mode                                            |     |

| 21.2.2 STOP mode                                            |     |

| CHAPTER 22 RESET FUNCTION                                   |     |

| 22.1 Register for Confirming Reset Source                   |     |

|                                                             |     |

| CHAPTER 23 POWER-ON-CLEAR CIRCUIT                           |     |

| 23.1 Functions of Power-on-Clear Circuit                    |     |

| 23.2 Configuration of Power-on-Clear Circuit                |     |

| 23.3 Operation of Power-on-Clear Circuit                    |     |

| 23.4 Cautions for Power-on-Clear Circuit                    | 802 |

| CHAPTER 24 LOW-VOLTAGE DETECTOR                             | 804 |

|                                                             |     |

| 24.1 Functions of Low-Voltage Detector                      |     |

| 24.2 Configuration of Low-Voltage Detector                  |     |

| 24.3 Registers Controlling Low-Voltage Detector             |     |

| 24.4 Operation of Low-Voltage Detector                      |     |

| 24.4.1 When used as reset                                   |     |

| 24.4.2 When used as interrupt                               |     |

| 24.5 Cautions for Low-Voltage Detector                      |     |

| CHAPTER 25 REGULATOR                                        |     |

| 25.1 Regulator Overview                                     |     |

| 25.2 Registers Controlling Regulator                        |     |

| CHAPTER 26 OPTION BYTE                                      | 829 |

| 26.1 Functions of Option Bytes                              |     |

| 26.1.1 User option byte (000C0H to 000C2H/010C0H to 010C2H) |     |

| 26.1.2 On-chip debug option byte (000C3H/ 010C3H)           |     |

| 26.2 Format of User Option Byte                             |     |

| 26.3 Format of On-chip Debug Option Byte                    |     |

| 26.4 Setting of Option Byte                                 |     |

|                                                             |     |

| CHAPTER 27 FLASH MEMORY                                     |     |

| 27.1 Writing with Flash Memory Programmer                   | 834 |

| 27.2 Programming Environment                                |     |

| APPENDIX A DEVELOPMENT TOOLS                                               | 940  |

|----------------------------------------------------------------------------|------|

| A.1 Software Package                                                       |      |

| A.2 Language Processing Software                                           |      |

| A.3 Flash Memory Programming Tools                                         |      |

| A.3.1 When using flash memory programmer PG-FP5 and FL-PR5                 |      |

| A.3.2 When using on-chip debug emulator with programming function QB-MINI2 |      |

| A.4 Debugging Tools (Hardware)                                             |      |

| A.4.1 When using in-circuit emulator QB-78K0RLX3                           |      |

| A.4.2 When using on-chip debug emulator with programming function QB-MINI2 |      |

| A.5 Debugging Tools (Software)                                             | 946  |

| APPENDIX B REGISTER INDEX                                                  | 947  |

| B.1 Register Index (In Alphabetical Order with Respect to Register Names)  |      |

| B.2 Register Index (In Alphabetical Order with Respect to Register Symbol) |      |

| APPENDIX C LIST OF CAUTIONS                                                | 957  |

| APPENDIX D REVISION HISTORY                                                | 996  |

| D.1 Major Revisions in This Edition                                        | 996  |

| D.2 Revision History of Preceding Editions                                 | 1000 |

| Pin Name                          | I/O Circuit Type | I/O    | Recommended Connection of Unused Pins                                                                                                                                                                                                                                               |

|-----------------------------------|------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P150/ANI8/AMP2+ <sup>Note 1</sup> | 11-N             | I/O    | Input: Independently connect to AVDDO or AVss via a resistor.                                                                                                                                                                                                                       |

| P151/ANI9 <sup>Note 1</sup>       | 11-G Note 3      |        | Output: Leave open.                                                                                                                                                                                                                                                                 |

| P152/ANI10 <sup>Note 1</sup>      |                  |        |                                                                                                                                                                                                                                                                                     |

| P157/ANI15/AVREFM Note 1, 2       | 11-T             | -      |                                                                                                                                                                                                                                                                                     |

| SEG0/COM4 to SEG3/COM7            | 18-F             | Output | Leave open.                                                                                                                                                                                                                                                                         |

| SEG4 to SEG26                     | 17-T             | -      |                                                                                                                                                                                                                                                                                     |

| COM0 to COM3                      | 18-E             |        |                                                                                                                                                                                                                                                                                     |

| VLC0 to VLC2                      | -                | -      |                                                                                                                                                                                                                                                                                     |

| AVDDO                             | _                | -      | $\label{eq:setup_state} \begin{array}{l} <\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$                                                                                                                                                                 |

| AV <sub>DD1</sub>                 | _                | -      | $\label{eq:when one or more of P110 or P111 are set as a digital port> Make this pin the same potential as EV_{DD} or V_{DD}. \\ < When all of P110 and P111 are set as analog ports> \\ Make this pin to have a potential where 2.3 V \leq AV_{DD1} \leq V_{DD}. \\ \end{aligned}$ |

| AVss                              | _                | -      | Make this pin the same potential as the $EV_{SS}$ or $V_{SS}.$                                                                                                                                                                                                                      |

| VREFOUT/AVREFP                    | -                | -      | Make this pin the same potential as the AV $_{\text{DD0}},$ EV $_{\text{DD}}$ or V $_{\text{DD}}.$                                                                                                                                                                                  |

| FLMD0                             | 2-W              | -      | Leave open or connect to $V_{\text{SS}}$ via a resistor of 100 k $\Omega$ or more.                                                                                                                                                                                                  |

| RESET                             | 2                | Input  | Connect directly to EVDD or via a resistor.                                                                                                                                                                                                                                         |

| REGC                              | _                | -      | Connect to Vss via capacitor (0.47 to 1 $\mu$ F).                                                                                                                                                                                                                                   |

Table 2-4. Connection of Unused Pins (78K0R/LH3) (3/3)

**Notes 1.** P150/ANI8/AMP2+ to P152/ANI10 and P157/ANI15/AVREFM are set in the digital input port mode after release of reset.

**2.** AVREFM applies to  $\mu$  PD78F150xA only.

**3.**  $\mu$  PD78F151xA corresponds to type 11-G.

<R>

## (d) Auxiliary carry flag (AC)

If the operation result has a carry from bit 3 or a borrow at bit 3, this flag is set (1). It is reset (0) in all other cases.

## (e) In-service priority flags (ISP1, ISP0)

This flag manages the priority of acknowledgeable maskable vectored interrupts. Vectored interrupt requests specified lower than the value of ISP0 and ISP1 by a priority specification flag register (PRn0L, PRn0H, PRn1L, PRn1H, PRn2L, PRn2H) (see **19.3 (3)**) can not be acknowledged. Actual request acknowledgment is controlled by the interrupt enable flag (IE).

**Remark** n = 0, 1

## (f) Carry flag (CY)

This flag stores overflow and underflow upon add/subtract instruction execution. It stores the shift-out value upon rotate instruction execution and functions as a bit accumulator during bit operation instruction execution.

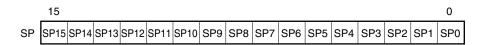

## (3) Stack pointer (SP)

This is a 16-bit register to hold the start address of the memory stack area. Only the internal RAM area can be set as the stack area.

## Figure 3-10. Format of Stack Pointer

The SP is decremented ahead of write (save) to the stack memory and is incremented after read (restored) from the stack memory.

Each stack operation saves data as shown in Figure 3-11.

- Cautions 1. Since reset signal generation makes the SP contents undefined, be sure to initialize the SP before using the stack.

- 2. It is prohibited to use the general-purpose register (FFEE0H to FFEFFH) space as a stack area.

- 3. While using the self-programming function, the area of FFE20H to FFEFFH cannot be used as a stack memory.

## Table 5-4. CPU Clock Transition and SFR Register Setting Examples (2/6)

## (4) CPU operating with 20 MHz internal high-speed oscillation clock (J) after reset release (A)

(The CPU operates with the internal high-speed oscillation clock immediately after a reset release (B).)

| (Set                  | ting sequence of SFR registers) |                      |                         |                 |

|-----------------------|---------------------------------|----------------------|-------------------------|-----------------|

|                       | Setting Flag of SFR Register    | DSCCTL Register Note | Waiting for Oscillation | DSCCTL Register |

| Status Transition     |                                 | DSCON                | Stabilization           | SELDSC          |

| $(A) \to (B) \to (J)$ |                                 | 1                    | Necessary               | 1               |

|                       |                                 |                      | (100 <i>µ</i> s)        |                 |

**Note** Check that  $V_{DD} \ge 2.7$  V and set DSCON = 1.

## (5) CPU clock changing from internal high-speed oscillation clock (B) to high-speed system clock (C)

| (Setting sequence of SFR registers)                                |                                |        |                  |                 |                  |                  |                           |      |

|--------------------------------------------------------------------|--------------------------------|--------|------------------|-----------------|------------------|------------------|---------------------------|------|

| Setting Flag of SFR Register<br>Status Transition                  | CMC Register <sup>Note 1</sup> |        | OSTS<br>Register | CSC<br>Register | OSMC<br>Register | OSTC<br>Register | CKC<br>Regi<br>ster       |      |

|                                                                    | EXCLK                          | OSCSEL | AMPH             |                 | MSTOP            | FSEL             |                           | MCM0 |

| (B) $\rightarrow$ (C)<br>(X1 clock: 2 MHz $\leq$ fX $\leq$ 10 MHz) | 0                              | 1      | 0                | Note 2          | 0                | 0                | Must be<br>checked        | 1    |

| (B) $\rightarrow$ (C)<br>(X1 clock: 10 MHz < fX $\leq$ 20 MHz)     | 0                              | 1      | 1                | Note 2          | 0                | 1 Note 3         | Must be<br>checked        | 1    |

| $(B) \rightarrow (C)$<br>(external main clock)                     | 1                              | 1      | ×                | Note 2          | 0                | 0/1              | Must<br>not be<br>checked | 1    |

(Setting sequence of SEB registers)

Unnecessary if these registers are already set

Unnecessary if the CPU is operating with the high-speed system clock

- Notes 1. The CMC register can be changed only once after reset release. This setting is not necessary if it has already been set.

- 2. Set the oscillation stabilization time as follows.

- Desired OSTC oscillation stabilization time  $\leq$  Oscillation stabilization time set by OSTS

- 3. FSEL = 1 when  $f_{CLK} > 10 \text{ MHz}$ If a divided clock is selected and fcLK  $\leq$  10 MHz, use with FSEL = 0 is possible even if fx > 10 MHz.

## Caution Set the clock after the supply voltage has reached the operable voltage of the clock to be set (see CHAPTER 31 ELECTRICAL SPECIFICATIONS).

- Remarks 1. x: don't care

- 2. (A) to (K) in Table 5-4 correspond to (A) to (K) in Figure 5-15.

| Timer array unit n | Channel m | Input (TIpq) / | Tin                                                                            | ner I/O Pins of Each Proc                | duct              |  |

|--------------------|-----------|----------------|--------------------------------------------------------------------------------|------------------------------------------|-------------------|--|

|                    |           | output (TOpq)  | 78K0R/LF3                                                                      | 78K0R/LG3                                | 78K0R/LH3         |  |

|                    |           |                | (80 pins)                                                                      | (100 pins)                               | (128 pins)        |  |

| 0                  | 0         | Input          | TI00/TO03/P31/RTCD                                                             | TI00/TO03/P31/RTCDIV/RTCCL/PCLBUZ1/INTP2 |                   |  |

|                    |           | Output         | TO00/TI03/P30RTC1H                                                             | HZ/INTP1                                 |                   |  |

|                    | 1         | I/O            | TI01/TO01/P32/PCLB                                                             | UZ0/INTP5                                |                   |  |

|                    | 2         | Input          | TI02/P52/SEGxx                                                                 |                                          |                   |  |

|                    |           |                | (78K0R/LF3: xx = 28,                                                           | 78K0R/LG3: xx = 37, 78                   | K0R/LH3: xx = 51) |  |

|                    |           | Output         | TO02/P12/SO02/TxD2                                                             |                                          |                   |  |

|                    | 3         | Input          | TI03/TO00/P30RTC1HZ/INTP1                                                      |                                          |                   |  |

|                    |           | Output         | TO03/TI00/P31/RTCD                                                             | IV/RTCCL/PCLBUZ1/IN                      | _BUZ1/INTP2       |  |

|                    | 4         | Input          | TI04/P53/SEGxx<br>(78K0R/LF3: xx = 27, 78K0R/LG3: xx = 36, 78K0R/LH3: xx = 50) |                                          |                   |  |

|                    |           |                |                                                                                |                                          |                   |  |

|                    |           | Output         | TO04/P13/SO10/TxD                                                              |                                          |                   |  |

|                    | 5         | I/O            | _                                                                              | TI05/TO05/P16/INTP1                      | 0                 |  |

|                    | 6         | I/O            | TI06/TO06/P34/INTP8                                                            |                                          | 3                 |  |

|                    | 7         | I/O            | TI07/TO07/P33/INTP3                                                            |                                          |                   |  |

| 1                  | 0         | I/O            | _                                                                              |                                          | TI10/TO10/P84     |  |

|                    | 1         | I/O            |                                                                                |                                          | TI11/TO11/P85     |  |

|                    | 2         | I/O            |                                                                                |                                          | TI12/TO12/P86     |  |

|                    | 3         | I/O            |                                                                                |                                          | TI13/TO13/P87     |  |

Whether each channel of the timer array unit is provided with timer I/O pins differs depending on the product.

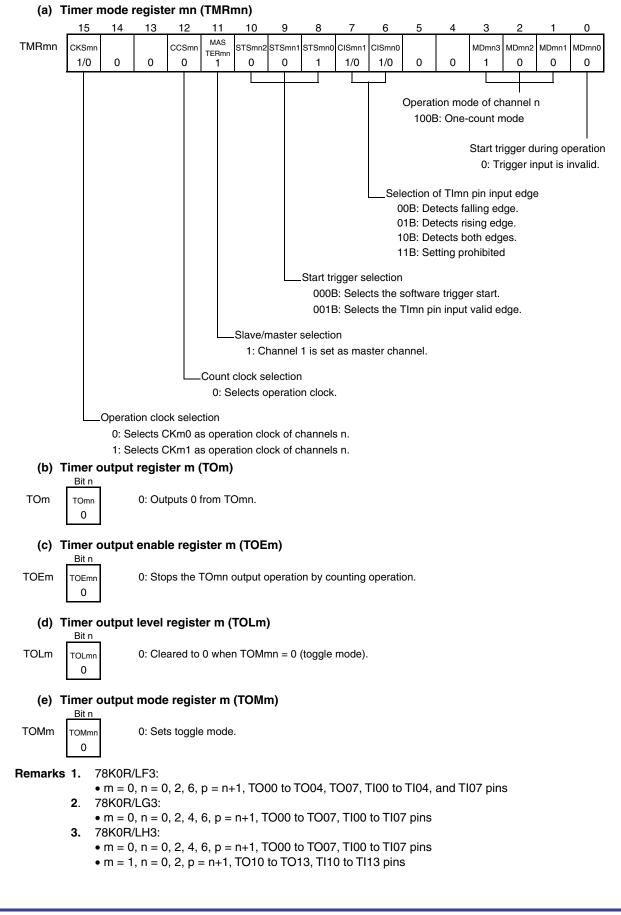

## Figure 6-64. Example of Set Contents of Registers When One-Shot Pulse Output Function Is Used (Master Channel)

|                               | Software Operation                                                                                                                                                                                                                                          | Hardware Status                                                                                                                                                    |

|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TAU<br>default<br>setting     |                                                                                                                                                                                                                                                             | Power-off status<br>(Clock supply is stopped and writing to each register is<br>disabled.)                                                                         |

|                               | Sets the TAU0EN or TAU1EN bits of the PER0 register to 1.                                                                                                                                                                                                   | Power-on status. Each channel stops operating.<br>(Clock supply is started and writing to each register is<br>enabled.)                                            |

|                               | Sets the TPSm register.<br>Determines clock frequencies of CKm0 and CKm1.                                                                                                                                                                                   |                                                                                                                                                                    |

| Channel<br>default<br>setting | Sets the TMRmn and TMRmp registers of two channels<br>to be used (determines operation mode of channels).<br>An output delay is set to the TDRmn register of the<br>master channel, and a pulse width is set to the TDRmp<br>register of the slave channel. | Channel stops operating.<br>(Clock is supplied and some power is consumed.)                                                                                        |

|                               | Sets slave channel.<br>The TOMmp bit of the TOMm register is set to 1<br>(combination operation mode).<br>Sets the TOLmp bit.<br>Sets the TOmp bit and determines default level of the<br>TOmp output.                                                      | The TOmn pin goes into Hi-Z output state.<br>The TOmn default setting level is output when the port<br>mode register is in output mode and the port register is 0. |

|                               |                                                                                                                                                                                                                                                             | TOmp does not change because channel stops operating.<br>The TOmp pin outputs the TOmp set level.                                                                  |

| Figure 6-66. | Operation Procedure of One-Shot Pulse Output Function (1/2) |

|--------------|-------------------------------------------------------------|

|--------------|-------------------------------------------------------------|

## Remarks 1. 78K0R/LF3:

- m = 0, n = 0, 2, 6, p = n+1, TO00 to TO04, and TO07 pins

- Channel 6 of timer array unit 0 can output a one-shot pulse only when software trigger start is selected and it is used as the master channel (because the TI06 pin is not provided).

- 2. 78K0R/LG3:

- m = 0, n = 0, 2, 4, 6, p = n+1, TO00 to TO07 pins

- 3. 78K0R/LH3:

- m = 0, n = 0, 2, 4, 6, p = n+1, TO00 to TO07 pins

- m = 1, n = 0, 2, p = n+1, TO10 to TO13 pins

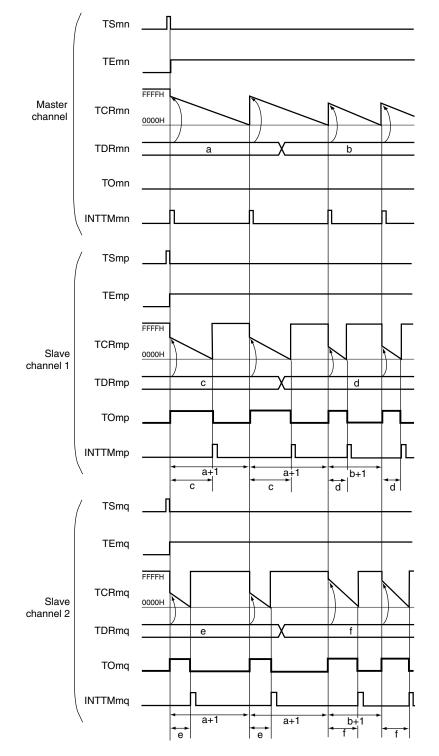

Figure 6-68. Example of Basic Timing of Operation as Multiple PWM Output Function (output two types of PWMs)

Remarks 1. 78K0R/LF3:

- m = 0, n = 0, 2, p = n+1, q = n+2, TO00 to TO04, and TO07 pins

- **2**. 78K0R/LG3:

- m = 0, n = 0, 2, 4, p = n+1, q = n+2, TO00 to TO07 pins **3.** 78K0R/LH3:

- m = 0, n = 0, 2, 4, p = n+1, q = n+2, TO00 to TO07 pins

- m = 1, n = 0, p = 1, q = 2, TO10 to TO13 pins

RENESAS

## 11.4 Operation of D/A Converter

## 11.4.1 Operation in normal mode

D/A conversion is performed using write operation to the DACSn register as the trigger. The setting method is described below.

- <1> Set bit 6 (DACEN) of peripheral enable register 0 (PER0) to 1 to start the supply of the input clock to the D/A converter.

- <2> Set the DAMDn bit of the D/A converter mode register (DAM) to 0 (normal mode).

- <3> Use the bit 6 (DAREF) of the DAM register to select the D/A converter reference voltage supply on the positive side.

- <4> Use the DARESn bit of the DAM register to select the resolution of the D/A converter.

- <5> Set the analog voltage value to be output to the ANOn pin to the D/A conversion value setting register Wn (DACSWn) or D/A conversion value setting register n (DACSn). Steps <1> and <5> above constitute the initial settings.

- <6> Set the DACEn bit of the DAM register to 1 (D/A conversion enable). After the wait time (20 μs or more) elapses, D/A conversion starts, and then, after the settling time (18 μs (max.)) elapses, the D/A converted analog voltage value is output from the ANOn pin.

- <7> To perform subsequent D/A conversions, write to the DACSWn or DACSn register. The previous D/A conversion result is held until the next D/A conversion is performed. When the DACEn bit of the DAM register is set to 0 (D/A conversion operation stop), D/A conversion stops, the ANOn pin goes into a high-impedance state when the PM11n bit of the PM11 register = 1 (input mode), and the ANOn pin outputs the set value of the P11 register when the PM11n bit = 0 (output mode).

## Cautions 1. Even if 1, 0, and then 1 is set to the DACEn bit, there is a wait after 1 is set for the last time.

2. If the DACSWn or DACSn register is rewritten during the settling time, D/A conversion is aborted and reconversion by using the rewritten values starts.

**Remark** n = 0, 1

## 11.4.2 Operation in real-time output mode

D/A conversion is performed using the interrupt request signals (INTTM04 and INTTM05) Note of timer channels 4 and 5

as triggers.

The setting method is described below.

- Note Channel 0 of the D/A converter: INTTM04 Channel 1 of the D/A converter: INTTM05

- <1> Set bit 6 (DACEN) of peripheral enable register 0 (PER0) to 1 to start the supply of the input clock to the D/A converter.

- <2> Set the DAMDn bit of the D/A converter mode register (DAM) to 0 (normal mode).

- <3> Use the bit 6 (DAREF) of the DAM register to select the D/A converter reference voltage supply on the positive side.

- <4> Use the DARESn bit of the DAM register to select the resolution of the D/A converter.

- <5> Set the analog voltage value to be output to the ANOn pin to the D/A conversion value setting register Wn (DACSWn) or D/A conversion value setting register n (DACSn).

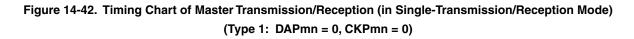

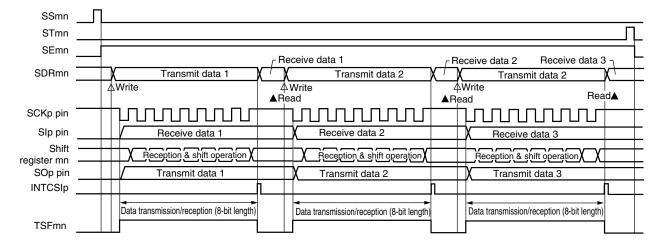

## (3) Processing flow (in single-transmission/reception mode)

**Remark** m: Unit number (m = 0, 1), n: Channel number (n = 0 to 2), p: CSI number (p = 00, 01, 10, 20)

## 14.7 Operation of Simplified I<sup>2</sup>C (IIC10, IIC20) Communication

This is a clocked communication function to communicate with two or more devices by using two lines: serial clock (SCL) and serial data (SDA). This communication function is designed to execute single communication with devices such as EEPROM, flash memory, and A/D converter, and therefore, can be used only by the master and does not have a wait detection function. Make sure by using software, as well as operating the control registers, that the AC specifications of the start and stop conditions are observed.

[Data transmission/reception]

- Master transmission, master reception (only master function with a single master)

- ACK output function<sup>Note</sup> and ACK detection function

- Data length of 8 bits

(When an address is transmitted, the address is specified by the higher 7 bits, and the least significant bit is used for R/W control.)

• Manual generation of start condition and stop condition

[Interrupt function]

• Transfer end interrupt

[Error detection flag]

- Parity error (ACK error)

- \* [Functions not supported by simplified I<sup>2</sup>C]

- Slave transmission, slave reception

- Arbitration loss detection function

- Wait detection function

- **Note** An ACK is not output when the last data is being received by writing 0 to the SOEmn (SOEm register) bit and stopping the output of serial communication data. See **14.7.3 (2)** Processing flow for details.

Remarks 1. To use the full-function I<sup>2</sup>C bus, see CHAPTER 15 SERIAL INTERFACE IICA.

**2.** m: Unit number (m = 0, 1), n: Channel number (n = 0, 2)

The channels supporting simplified I<sup>2</sup>C (IIC10, IIC20) are channel 2 of SAU0 and channel 0 of SAU1.

| Unit | Channel | Used as CSI | Used as UART               | Used as Simplified I <sup>2</sup> C |

|------|---------|-------------|----------------------------|-------------------------------------|

| 0    | 0       | CSI00       | UART0                      | _                                   |

|      | 1       | CSI01       |                            | _                                   |

|      | 2       | CSI10       | UART1                      | IIC10                               |

|      | 3       | _           |                            | _                                   |

| 1    | 0       | CSI20       | UART2                      | IIC20                               |

|      | 1       | -           |                            | _                                   |

|      | 2       | =           | UART3 (supporting LIN-bus) | _                                   |

|      | 3       | _           |                            | _                                   |

## (3) IICA status register (IICS)

This register indicates the status of I<sup>2</sup>C.

IICS is read by a 1-bit or 8-bit memory manipulation instruction only when STT = 1 and during the wait period. Reset signal generation clears this register to 00H.

Caution Reading the IICS register while the address match wakeup function is enabled (WUP = 1) in STOP mode is prohibited. When the WUP bit is changed from 1 to 0 (wakeup operation is stopped), regardless of the INTIICA interrupt request, the change in status is not reflected until the next start condition or stop condition is detected. To use the wakeup function, therefore, enable (SPIE = 1) the interrupt generated by detecting a stop condition and read the IICS register after the interrupt has been detected.

Remark STT: bit 1 of IICA control register 0 (IICCTL0) WUP: bit 7 of IICA control register 1 (IICCTL1)

Address: FFF51H R After reset: 00H Symbol <7> <6> <5> <4> <3> <2> <1> <0> IICS MSTS ALD EXC COI TRC ACKD STD SPD MSTS Master status check flag 0 Slave device status or communication standby status 1 Master device communication status Condition for clearing (MSTS = 0) Condition for setting (MSTS = 1) · When a stop condition is detected · When a start condition is generated • When ALD = 1 (arbitration loss) Cleared by LREL = 1 (exit from communications) When IICE changes from 1 to 0 (operation stop) Reset

| ALD                                                                                                                                                | Detection of arbitration loss                                                                      |                                                              |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|--------------------------------------------------------------|--|

| 0                                                                                                                                                  | This status means either that there was no arbitration or that the arbitration result was a "win". |                                                              |  |

| 1                                                                                                                                                  | This status indicates the arbitration result was a "loss". MSTS is cleared.                        |                                                              |  |

| Condition for clearing (ALD = 0)                                                                                                                   |                                                                                                    | Condition for setting (ALD = 1)                              |  |

| <ul> <li>Automatically cleared after IICS is read<sup>Note</sup></li> <li>When IICE changes from 1 to 0 (operation stop)</li> <li>Reset</li> </ul> |                                                                                                    | <ul> <li>When the arbitration result is a "loss".</li> </ul> |  |

| EXC                                                                                                                                                                                                                              | Detection of extension code reception |                                                                                                                                   |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--|--|

| 0                                                                                                                                                                                                                                | Extension code was not received.      |                                                                                                                                   |  |  |

| 1                                                                                                                                                                                                                                | Extension code was received.          |                                                                                                                                   |  |  |

| Condition for clearing (EXC = 0)                                                                                                                                                                                                 |                                       | Condition for setting (EXC = 1)                                                                                                   |  |  |

| <ul> <li>When a start condition is detected</li> <li>When a stop condition is detected</li> <li>Cleared by LREL = 1 (exit from communications)</li> <li>When IICE changes from 1 to 0 (operation stop)</li> <li>Reset</li> </ul> |                                       | • When the higher four bits of the received address data is either "0000" or "1111" (set at the rising edge of the eighth clock). |  |  |

**Note** This register is also cleared when a 1-bit memory manipulation instruction is executed for bits other than IICS. Therefore, when using the ALD bit, read the data of this bit before the data of the other bits.

Remark

LREL:

Bit 6 of IICA control register 0 (IICCTL0)

IICE:

Bit 7 of IICA control register 0 (IICCTL0)

| Address | : FFF52H  | After re                      | eset: 00H                                                                                                         | R/W <sup>Not</sup> | e              |               |                              |             |                                             |

|---------|-----------|-------------------------------|-------------------------------------------------------------------------------------------------------------------|--------------------|----------------|---------------|------------------------------|-------------|---------------------------------------------|

| Symbol  | <7>       | <6>                           | 5                                                                                                                 | 4                  | 3              | 2             | <1>                          | <0>         | _                                           |

| IICF    | STCF      | IICBSY                        | 0                                                                                                                 | 0                  | 0              | 0             | STCEN                        | IICRSV      | ]                                           |

|         |           |                               |                                                                                                                   |                    |                |               |                              |             | -                                           |

|         | STCF      |                               |                                                                                                                   |                    | 5              | STT clear f   | lag                          |             |                                             |

|         | 0         | Generate                      | start condi                                                                                                       | tion               |                |               |                              |             |                                             |

|         | 1         | Start cond                    | lition gener                                                                                                      | ration unsue       | ccessful: c    | ear STT fl    | ag                           |             |                                             |

|         | Condition | for clearin                   | g (STCF =                                                                                                         | 0)                 |                | Conditio      | on for setting               | g (STCF =   | 1)                                          |

|         |           |                               | d by STT = 1<br>ICE = 0 (operation stop)                                                                          |                    |                |               |                              | n communi   | insuccessful and STT ication reservation is |

|         |           |                               |                                                                                                                   |                    |                |               |                              |             |                                             |

|         | IICBSY    |                               |                                                                                                                   |                    | l²C            | bus status    | s flag                       |             |                                             |

|         | 0         | Bus relea                     | se status (                                                                                                       | communica          | tion initial s | status whe    | n STCEN =                    | : 1)        |                                             |

|         | 1         | Bus comn                      | nunication                                                                                                        | status (com        | nmunicatio     | n initial sta | tus when S                   | TCEN = 0)   | 1                                           |

|         | Condition | n for clearin                 | g (IICBSY                                                                                                         | = 0)               |                | Conditio      | on for setting               | g (IICBSY : | = 1)                                        |

|         |           | ion of stop o<br>IICE = 0 (op |                                                                                                                   | op)                |                |               | tion of start<br>g of IICE w |             | N = 0                                       |

|         | r         | 1                             |                                                                                                                   |                    |                |               |                              |             |                                             |

|         | STCEN     |                               |                                                                                                                   |                    | Initial        | start enab    | le trigger                   |             |                                             |

|         | 0         |                               | After operation is enabled (IICE = 1), enable generation of a start condition upon detection of a stop condition. |                    |                |               |                              |             |                                             |

|         | 1         |                               | After operation is enabled (IICE = 1), enable generation of a start condition without detecting a stop condition. |                    |                |               |                              |             |                                             |

|         | Condition | for clearing                  | g (STCEN                                                                                                          | = 0)               |                | Conditio      | on for setting               | g (STCEN    | = 1)                                        |

|         | Cleared   | d by instruc                  | tion                                                                                                              |                    |                | Set by        | y instructior                | ı           |                                             |

## Figure 15-8. Format of IICA Flag Register (IICF)

Reset

• Detection of start condition

| IICRSV                                                    | Communication reservation function disable bit |                                    |  |  |  |

|-----------------------------------------------------------|------------------------------------------------|------------------------------------|--|--|--|

| 0                                                         | Enable communication reservation               |                                    |  |  |  |

| 1                                                         | Disable communication reservation              |                                    |  |  |  |

| Condition                                                 | for clearing (IICRSV = 0)                      | Condition for setting (IICRSV = 1) |  |  |  |

| <ul> <li>Cleared by instruction</li> <li>Reset</li> </ul> |                                                | Set by instruction                 |  |  |  |

**Note** Bits 6 and 7 are read-only.

Cautions 1. Write to STCEN only when the operation is stopped (IICE = 0).

- As the bus release status (IICBSY = 0) is recognized regardless of the actual bus status when STCEN = 1, when generating the first start condition (STT = 1), it is necessary to verify that no third party communications are in progress in order to prevent such communications from being destroyed.

- 3. Write to IICRSV only when the operation is stopped (IICE = 0).

Remark STT: Bit 1 of IICA control register 0 (IICCTL0) IICE: Bit 7 of IICA control register 0 (IICCTL0)

| Table 16-1. | Maximum | Number o | f Pixels (3/3) |

|-------------|---------|----------|----------------|

|-------------|---------|----------|----------------|

## (b) 78K0R/LG3

| LCD Driver Voltage<br>Generator | Bias<br>Mode | Number of<br>Time Slices | Common Signals Used | Number of<br>Segments | Maximum Number of Pixels                                        |

|---------------------------------|--------------|--------------------------|---------------------|-----------------------|-----------------------------------------------------------------|

| External resistance division    | -            | Static                   | COM0 (COM1 to COM3) | 5                     |                                                                 |

|                                 | 1/2          | 2                        | COM0, COM1          |                       | 108 (54 segment signals,<br>2 common signals) <sup>Note 2</sup> |

|                                 |              | 3                        | COM0 to COM2        |                       | 162 (54 segment signals,                                        |

|                                 | 1/3          | 3                        | COM0 to COM2        |                       | 3 common signals) <sup>№ te 3</sup>                             |

|                                 |              | 4                        | COM0 to COM3        |                       | 216 (54 segment signals, 4 common signals) <sup>Note 4</sup>    |

|                                 | 1/4          | 8                        | COM0 to COM7        | 50                    | 400 (50 segment signals, 8<br>common signals) <sup>№te 5</sup>  |

| Internal voltage<br>boosting    | 1/3          | 3                        | COM0 to COM2        | 54                    | 162 (54 segment signals,<br>3 common signals) <sup>Note3</sup>  |

|                                 |              | 4                        | COM0 to COM3        |                       | 216 (54 segment signals, 4 common signals) <sup>Note 4</sup>    |

|                                 | 1/4          | 8                        | COM0 to COM7        | 50                    | 400 (50 segment signals, 8<br>common signals) <sup>№te 5</sup>  |

| Capacitor Split                 | 1/3          | 3                        | COM0 to COM2        | 54                    | 162 (54 segment signals,<br>3 common signals) <sup>№te</sup>    |

|                                 |              | 4                        | COM0 to COM3        |                       | 216 (54 segment signals, 4 common signals) <sup>Note 4</sup>    |

Notes 1. 6-digit LCD panel, each digit having an 8-segment 且 configuration.

- 2. 13-digit LCD panel, each digit having a 4-segment **B** configuration.

- 3. 20-digit LCD panel, each digit having a 3-segment **B** configuration.

- 4. 27-digit LCD panel, each digit having a 2-segment **B** configuration.

- 5. 50-digit LCD panel, each digit having a 1-segment 且 configuration.

Cautions 1. The VLCD setting is valid only when the voltage boost circuit is operating.

- 2. Bits 5 to 7 must be set to 0.

- 3. Be sure to change the VLCD value after having stopped the operation of the voltage boost circuit (VLCON = 0).

- 4. These values above may change after device evaluation.

- 5. To use the internal voltage boosting method, specify the reference voltage by using the VLCD register (or perform a reset to use the default value of the reference voltage), wait for the reference voltage setup time (2 ms (min.)), and then set VLCON to 1.

## (5) Port function register (PFALL)

This register sets whether to use pins P50 to P57, P90 to P97, P100 to P102, and P140 to P147 as port pins (other than segment output pins) or segment output pins.

PFALL is set using a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation sets PFALL to 00H.

**Remark** The port pins to be used alternatively with the segment output pins vary, depending on the product.

- 78K0R/LF3: P50 to P57, P90 to P92, P100, P140 to P147

- 78K0R/LG3: P50 to P57, P90 to P97, P100, P140 to P147

- 78K0R/LH3: P50 to P57, P90 to P97, P100 to P102, P140 to P147

## Figure 16-6. Format of Port Function Register (PFALL) (1/2)

| Address: F0080H |   | After reset: 00H | R/W   |      |                      |      |      |      |   |

|-----------------|---|------------------|-------|------|----------------------|------|------|------|---|

| Symbol          | 7 | 6                | 5     | 4    | 3                    | 2    | 1    | 0    | _ |

| PFALL           | 0 | PF14H            | PF14L | PF10 | PF9H <sup>Note</sup> | PF9L | PF5H | PF5L | I |

| PF14H | Port/segment outputs specification of the P144 to P147 pins    |

|-------|----------------------------------------------------------------|

| 0     | Used the P144 to P147 pins as port (other than segment output) |

| 1     | Used the P144 to P147 pins as segment output                   |

| PF14L | Port/segment outputs specification of the P140 to P143 pins    |

|-------|----------------------------------------------------------------|

| 0     | Used the P140 to P143 pins as port (other than segment output) |

| 1     | Used the P140 to P143 pins as segment output                   |

| PF10 | Port/segment outputs specification of the P100 to P102 pins    |

|------|----------------------------------------------------------------|

| 0    | Used the P100 to P102 pins as port (other than segment output) |

| 1    | Used the P100 to P102 pins as segment output                   |

| PF9H | Port/segment outputs specification of the P94 to P97 pins    |

|------|--------------------------------------------------------------|

| 0    | Used the P94 to P97 pins as port (other than segment output) |

| 1    | Used the P94 to P97 pins as segment output                   |

| PF9L | Port/segment outputs specification of P90 to P93 pins        |

|------|--------------------------------------------------------------|

| 0    | Used the P90 to P93 pins as port (other than segment output) |

| 1    | Used the P90 to P93 pins as segment output                   |

Note 78K0R/LG3, 78K0R/LH3 only

## Figure 19-9. Format of Priority Specification Flag Registers (PR00L, PR00H, PR01L, PR01H, PR02L, PR02H, PR10L, PR10H, PR11L, PR11H, PR12L, PR12H) (78K0R/LG3) (2/2)

| Address: FFI                         | -EBH After                          | reset: FFH                          | R/W                                 |                                    |                                 |                |                |               |

|--------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|------------------------------------|---------------------------------|----------------|----------------|---------------|

| Symbol                               | <7>                                 | <6>                                 | <5>                                 | <4>                                | 3                               | <2>            | <1>            | <0>           |

| PR01H                                | TMPR004                             | SREPR02                             | SRPR02                              | CSIPR020<br>IICPR020<br>STPR02     | 1                               | RTCIPR0        | RTCPR0         | ADPR0         |

| Address: FFI                         |                                     | reset: FFH                          | R/W                                 |                                    |                                 |                |                |               |

|                                      |                                     |                                     |                                     |                                    | 0                               | 0              |                | 0             |

| Symbol                               | <7>                                 | <6>                                 | <5>                                 | <4>                                | 3                               | <2>            | <1>            | <0>           |

| PR11H                                | TMPR104                             | SREPR12                             | SRPR12                              | CSIPR120<br>IICPR120<br>STPR12     | 1                               | RTCIPR1        | RTCPR1         | ADPR1         |

| Address: FFI                         |                                     | reset: FFH                          | R/W                                 |                                    |                                 |                |                |               |

|                                      | -Don Allei<br><7>                   | <6>                                 | <5>                                 | <4>                                | <3>                             | <2>            | <1>            | <0>           |

| Symbol                               |                                     |                                     |                                     |                                    |                                 |                |                |               |

| PR02L                                | PPR010                              | PPR09                               | PPR08                               | PPR07                              | PPR06                           | TMPR007        | TMPR006        | TMPR005       |

| Address: FFI                         | -DCH After                          | reset: FFH                          | R/W                                 |                                    |                                 |                |                |               |

| Symbol                               | <7>                                 | <6>                                 | <5>                                 | <4>                                | <3>                             | <2>            | <1>            | <0>           |

| PR12L                                | PPR110                              | PPR19                               | PPR18                               | PPR17                              | PPR16                           | TMPR107        | TMPR106        | TMPR105       |

| Address: FFI                         | -D9H After                          | reset: FFH                          | R/W                                 |                                    |                                 |                |                |               |

| Symbol                               | 7                                   | 6                                   | <5>                                 | <4>                                | <3>                             | <2>            | <1>            | <0>           |

| PR02H                                | 1                                   |                                     |                                     |                                    |                                 |                |                |               |

| Address: FFFDDH After reset: FFH R/W |                                     |                                     |                                     |                                    |                                 |                |                |               |

| Address: FFI                         |                                     | 1<br>reset: FFH                     | MDPR0<br>R/W                        | TMPR013                            | TMPR012                         | TMPR011        | TMPR010        | PPR011        |

| Address: FFI<br>Symbol               |                                     |                                     |                                     | TMPR013<br><4>                     | TMPR012<br><3>                  | TMPR011<br><2> | TMPR010<br><1> | PPR011<br><0> |

|                                      | -DDH After                          | reset: FFH                          | R/W                                 | I                                  |                                 |                |                |               |

| Symbol                               | FDDH After<br>7                     | reset: FFH<br>6                     | R/W<br><5>                          | <4>                                | <3>                             | <2>            | <1>            | <0>           |

| Symbol                               | FDDH After<br>7                     | reset: FFH<br>6                     | R/W<br><5>                          | <4>                                | <3>                             | <2><br>TMPR111 | <1>            | <0>           |

| Symbol                               | FDDH After<br>7<br>1                | reset: FFH<br>6<br>1                | R/W<br><5><br>MDPR1                 | <4>                                | <3><br>TMPR112<br>Priority leve | <2><br>TMPR111 | <1>            | <0>           |

| Symbol                               | EDDH After<br>7<br>1<br>XXPR1X      | reset: FFH<br>6<br>1<br>XXPR0X      | R/W<br><5><br>MDPR1                 | <4><br>TMPR113                     | <3><br>TMPR112<br>Priority leve | <2><br>TMPR111 | <1>            | <0>           |

| Symbol                               | FDDH After<br>7<br>1<br>XXPR1X<br>0 | reset: FFH<br>6<br>1<br>XXPR0X<br>0 | R/W<br><5><br>MDPR1<br>Specify leve | <4><br>TMPR113<br>I 0 (high priori | <3><br>TMPR112<br>Priority leve | <2><br>TMPR111 | <1>            | <0>           |

Caution Be sure to set bit 3 of PR01H and PR11H, bits 6, 7 of PR02H and PR12H to 1.

## CHAPTER 25 REGULATOR

## 25.1 Regulator Overview

All 78K0R/Lx3 microcontroller products contain a circuit for operating the device with a constant voltage. At this time, in order to stabilize the regulator output voltage, connect the REGC pin to Vss via a capacitor (0.47 to 1  $\mu$ F).

Also, use a capacitor with good characteristics, since it is used to stabilize internal voltage.

The regulator output voltage is normally 2.4 V (TYP.), and in the low-power consumption mode, 1.8 V (TYP.).

## 25.2 Registers Controlling Regulator

## (1) Regulator mode control register (RMC)

This register sets the output voltage of the regulator. RMC is set with an 8-bit memory manipulation instruction. Reset input sets this register to 00H.

## Figure 25-1. Format of Regulator Mode Control Register (RMC)

| Address: F00F4 | 4H After re | set: 00H R/ | W |   |   |   |   |   |

|----------------|-------------|-------------|---|---|---|---|---|---|

| Symbol         | 7           | 6           | 5 | 4 | 3 | 2 | 1 | 0 |

| RMC            |             |             |   |   |   |   |   |   |

|                |             |             |   |   |   |   |   |   |

| RMC[7:0]         | Control of output voltage of regulator                                                                                             |

|------------------|------------------------------------------------------------------------------------------------------------------------------------|

| 5AH              | Fixed to low-power consumption mode (1.8 V)                                                                                        |

| 00H              | Switches normal power mode (2.4 V) and low-power consumption mode (1.8 V) according to the condition (refer to <b>Table 25-1</b> ) |

| Other than above | Setting prohibited                                                                                                                 |

- Cautions 1. The RMC register can be rewritten only in the low-power consumption mode (refer to Table 25-1). In other words, rewrite this register during CPU operation with the subsystem clock (fxr) while the high-speed system clock (fmx), the high-speed internal oscillation clock, and the 20 MHz internal high-speed oscillation clock (fiH20) are both stopped.

- 2. When using the setting fixed to the low consumption current mode, the RMC register can be used in the following cases.

<When the high-speed internal oscillation clock ( $f_{IH} = 8$  MHz (TYP.) or  $f_{IH} = 1$  MHz (TYP.)) is selected as the CPU clock>

$f_{CLK} \leq 1$  MHz and external oscillator (X1 clock (fx), external main system clock (fex)) stop.

<When the X1 clock (fx) or external main system clock (fex) is selected as the CPU clock>

fclk  $\leq$  1 MHz, fx/fex  $\leq$  5 MHz and the internal high-speed oscillator stop.

<When the subsystem clock (fsub) is selected as the CPU clock>

Both the internal high-speed oscillator and external oscillator (fx/f<sub>Ex</sub>  $\leq$  5 MHz) stop or either one stops.

| Instruction<br>Group       | Mnemonic | Operands           | Bytes | Clocks |        | Operation                         | Flag |       |

|----------------------------|----------|--------------------|-------|--------|--------|-----------------------------------|------|-------|

|                            |          |                    |       | Note 1 | Note 2 |                                   | Z    | AC CY |

| 16-bit<br>data<br>transfer | MOVW     | AX, !addr16        | 3     | 1      | 4      | $AX \leftarrow (addr16)$          |      |       |

|                            |          | !addr16, AX        | 3     | 1      | _      | (addr16) ← AX                     |      |       |

|                            |          | AX, [DE]           | 1     | 1      | 4      | $AX \leftarrow (DE)$              |      |       |

|                            |          | [DE], AX           | 1     | 1      | -      | $(DE) \leftarrow AX$              |      |       |

|                            |          | AX, [DE + byte]    | 2     | 1      | 4      | AX ← (DE + byte)                  |      |       |

|                            |          | [DE + byte], AX    | 2     | 1      | -      | (DE + byte) ← AX                  |      |       |

|                            |          | AX, [HL]           | 1     | 1      | 4      | $AX \leftarrow (HL)$              |      |       |

|                            |          | [HL], AX           | 1     | 1      | -      | $(HL) \leftarrow AX$              |      |       |

|                            |          | AX, [HL + byte]    | 2     | 1      | 4      | $AX \leftarrow (HL + byte)$       |      |       |

|                            |          | [HL + byte], AX    | 2     | 1      | -      | (HL + byte) ← AX                  |      |       |

|                            |          | AX, word[B]        | 3     | 1      | 4      | $AX \leftarrow (B + word)$        |      |       |

|                            |          | word[B], AX        | 3     | 1      | -      | $(B + word) \leftarrow AX$        |      |       |

|                            |          | AX, word[C]        | 3     | 1      | 4      | $AX \leftarrow (C + word)$        |      |       |

|                            |          | word[C], AX        | 3     | 1      | -      | $(C + word) \leftarrow AX$        |      |       |

|                            |          | AX, word[BC]       | 3     | 1      | 4      | $AX \leftarrow (BC + word)$       |      |       |

|                            |          | word[BC], AX       | 3     | 1      | -      | $(BC + word) \leftarrow AX$       |      |       |

|                            |          | AX, [SP + byte]    | 2     | 1      | -      | $AX \leftarrow (SP + byte)$       |      |       |

|                            |          | [SP + byte], AX    | 2     | 1      | _      | $(SP + byte) \leftarrow AX$       |      |       |

|                            |          | BC, saddrp         | 2     | 1      | -      | $BC \leftarrow (saddrp)$          |      |       |

|                            |          | BC, !addr16        | 3     | 1      | 4      | $BC \leftarrow (addr16)$          |      |       |

|                            |          | DE, saddrp         | 2     | 1      | -      | $DE \leftarrow (saddrp)$          |      |       |

|                            |          | DE, !addr16        | 3     | 1      | 4      | $DE \leftarrow (addr16)$          |      |       |

|                            |          | HL, saddrp         | 2     | 1      | -      | $HL \leftarrow (saddrp)$          |      |       |

|                            |          | HL, !addr16        | 3     | 1      | 4      | $HL \leftarrow (addr16)$          |      |       |

|                            |          | AX, ES:!addr16     | 4     | 2      | 5      | $AX \leftarrow (ES, addr16)$      |      |       |

|                            |          | ES:!addr16, AX     | 4     | 2      | -      | (ES, addr16) $\leftarrow$ AX      |      |       |

|                            |          | AX, ES:[DE]        | 2     | 2      | 5      | $AX \leftarrow (ES, DE)$          |      |       |

|                            |          | ES:[DE], AX        | 2     | 2      | -      | $(ES,DE) \leftarrow AX$           |      |       |

|                            |          | AX, ES:[DE + byte] | 3     | 2      | 5      | $AX \leftarrow ((ES, DE) + byte)$ |      |       |

|                            |          | ES:[DE + byte], AX | 3     | 2      | -      | ((ES, DE) + byte) ← AX            |      |       |

|                            |          | AX, ES:[HL]        | 2     | 2      | 5      | $AX \leftarrow (ES, HL)$          |      |       |

|                            |          | ES:[HL], AX        | 2     | 2      | -      | $(ES,HL) \gets AX$                |      |       |

Notes 1. When the internal RAM area or SFR area is accessed, or for an instruction with no data access.

2. When the program memory area is accessed.

**Remarks 1.** One instruction clock cycle is one cycle of the CPU clock (fcPu) selected by the system clock control register (CKC).

2. This number of clocks is for when the program is in the internal ROM (flash memory) area.

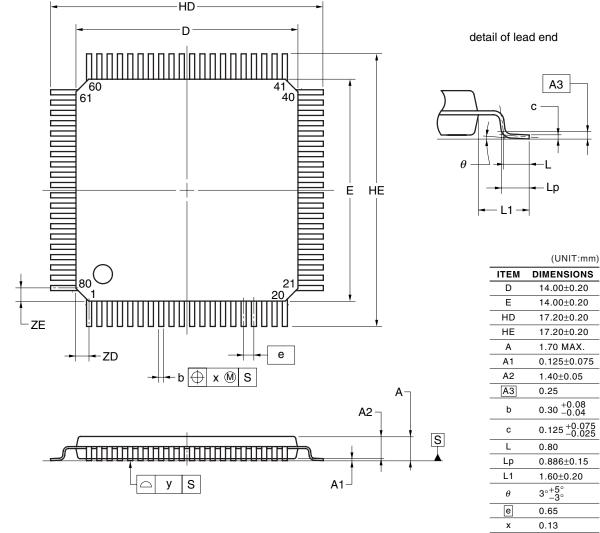

## CHAPTER 32 PACKAGE DRAWINGS

## 32.1 78K0R/LF3

<R> • μ PD78F1500AGC-GAD-AX, 78F1501AGC-GAD-AX, 78F1502AGC-GAD-AX, 78F1510AGC-GAD-AX, 78F1512AGC-GAD-AX

## 80-PIN PLASTIC LQFP (14x14)

#### ΝΟΤΕ

Each lead centerline is located within 0.13 mm of its true position at maximum material condition.

P80GC-65-GAD

0.10

0.825

0.825

у

ZD

ZE