Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Discontinued at Digi-Key                                                                 |

|----------------------------|------------------------------------------------------------------------------------------|

| Core Processor             | ARM926EJ-S                                                                               |

| Core Size                  | 16/32-Bit                                                                                |

| Speed                      | 266MHz                                                                                   |

| Connectivity               | EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, Microwire, SPI, SSI, SSP, UART/USART, USB OTG |

| Peripherals                | DMA, I <sup>2</sup> S, Motor Control PWM, PWM, WDT                                       |

| Number of I/O              | 51                                                                                       |

| Program Memory Size        | -                                                                                        |

| Program Memory Type        | ROMIess                                                                                  |

| EEPROM Size                | -                                                                                        |

| RAM Size                   | 256K x 8                                                                                 |

| Voltage - Supply (Vcc/Vdd) | 0.9V ~ 3.6V                                                                              |

| Data Converters            | A/D 3x10b                                                                                |

| Oscillator Type            | Internal                                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                        |

| Mounting Type              | Surface Mount                                                                            |

| Package / Case             | 296-TFBGA                                                                                |

| Supplier Device Package    | 296-TFBGA (15x15)                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/lpc3240fet296-01-5               |

|                            |                                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Multi-layer AHB system that provides a separate bus for each AHB master, including both an instruction and data bus for the CPU, two data busses for the DMA controller, and another bus for the USB controller, one for the LCD, and a final one for the Ethernet MAC. There are no arbitration delays in the system unless two masters attempt to access the same slave at the same time.

- External memory controller for DDR and SDR SDRAM as well as for static devices.

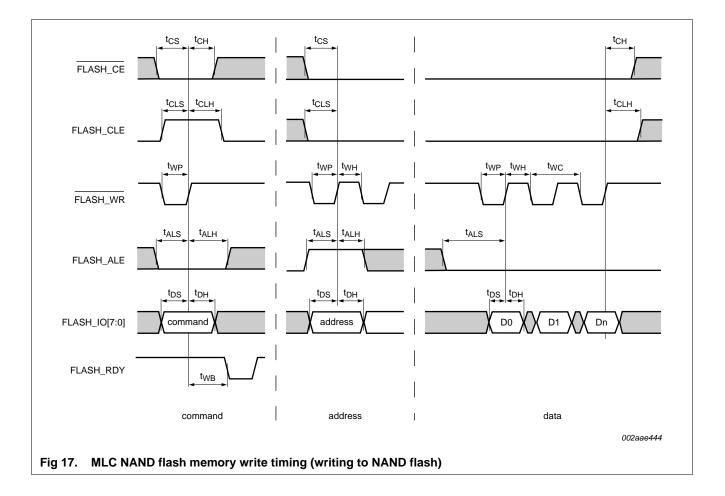

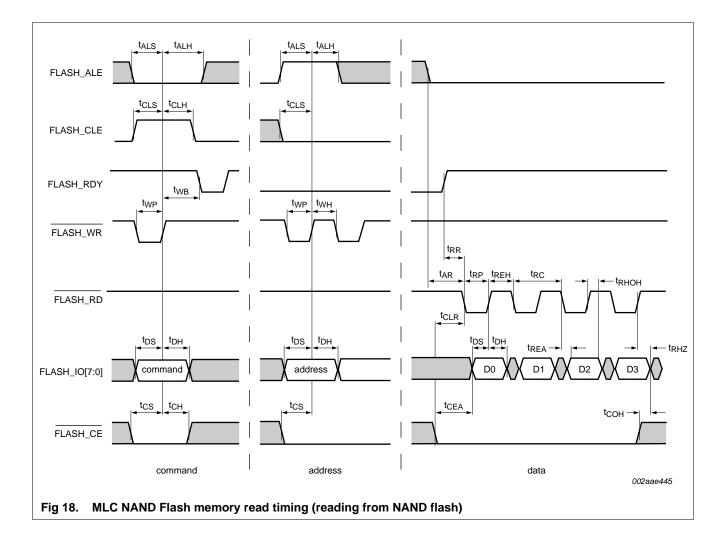

- Two NAND flash controllers: One for single-level NAND flash devices and the other for multi-level NAND flash devices.

- Master Interrupt Controller (MIC) and two Slave Interrupt Controllers (SIC), supporting 74 interrupt sources.

- Eight channel General Purpose DMA (GPDMA) controller on the AHB that can be used with the SD card port, the high-speed UARTs, I<sup>2</sup>S-bus interfaces, and SPI interfaces, as well as memory-to-memory transfers.

- Serial interfaces:

- ◆ 10/100 Ethernet MAC with dedicated DMA Controller.

- USB interface supporting either device, host (OHCI compliant), or On-The-Go (OTG) with an integral DMA controller and dedicated PLL to generate the required 48 MHz USB clock.

- Four standard UARTs with fractional baud rate generation and 64 byte FIFOs. One of the standard UARTs supports IrDA.

- Three additional high-speed UARTs intended for on-board communications that support baud rates up to 921 600 when using a 13 MHz main oscillator. All high-speed UARTs provide 64 byte FIFOs.

- Two SPI controllers.

- Two SSP controllers.

- Two I<sup>2</sup>C-bus interfaces with standard open-drain pins. The I<sup>2</sup>C-bus interfaces support single master, slave, and multi-master I<sup>2</sup>C-bus configurations.

- Two I<sup>2</sup>S-bus interfaces, each with separate input and output channels. Each channel can be operated independently on three pins, or both input and output channels can be used with only four pins and a shared clock.

- Additional peripherals:

- ◆ LCD controller supporting both STN and TFT panels, with dedicated DMA controller. Programmable display resolution up to 1024 × 768.

- Secure Digital (SD) memory card interface, which conforms to the SD Memory Card Specification Version 1.01.

- General Purpose (GP) input, output, and I/O pins. Includes 12 GP input pins, 24 GP output pins, and 51 GP I/O pins.

- ♦ 10-bit, 400 kHz Analog-to-Digital Converter (ADC) with input multiplexing from three pins. Optionally, the ADC can operate as a touch screen controller.

- Real-Time Clock (RTC) with separate power pin and dedicated 32 kHz oscillator. NXP implemented the RTC in an independent on-chip power domain so it can remain active while the rest of the chip is not powered. The RTC also includes a 32-byte scratch pad memory.

- ♦ 32-bit general purpose high-speed timer with a 16-bit pre-scaler. This timer includes one external capture input pin and a capture connection to the RTC clock. Interrupts may be generated using three match registers.

# 4. Ordering information

### Table 1. Ordering information

| Type number <sup>[1]</sup> | Package  | Package                                                    |           |  |  |  |  |

|----------------------------|----------|------------------------------------------------------------|-----------|--|--|--|--|

|                            | Name     | Description                                                | Version   |  |  |  |  |

| LPC3220FET296/01[2]        | TFBGA296 | plastic thin fine-pitch ball grid array package; 296 balls | SOT1048-1 |  |  |  |  |

| LPC3230FET296/01[2]        | TFBGA296 | plastic thin fine-pitch ball grid array package; 296 balls | SOT1048-1 |  |  |  |  |

| LPC3240FET296/01[2]        | TFBGA296 | plastic thin fine-pitch ball grid array package; 296 balls | SOT1048-1 |  |  |  |  |

| LPC3250FET296/01[2]        | TFBGA296 | plastic thin fine-pitch ball grid array package; 296 balls | SOT1048-1 |  |  |  |  |

[1] F = -40 °C to +85 °C temperature range. Note that Revision "A" parts with and without the /01 suffix are identical. For example, LPC3220FET296 Revision "A" is identical to LPC3220FET296/01 Revision "A".

[2] Available starting with Revision "A".

## 4.1 Ordering options

### Table 2. Part options

| Type number      | SRAM (kB) | 10/100 Ethernet | LCD<br>controller | Temperature range (°C) | Package  |

|------------------|-----------|-----------------|-------------------|------------------------|----------|

| LPC3220FET296/01 | 128       | 0               | 0                 | -40 to +85             | TFBGA296 |

| LPC3230FET296/01 | 256       | 0               | 1                 | -40 to +85             | TFBGA296 |

| LPC3240FET296/01 | 256       | 1               | 0                 | -40 to +85             | TFBGA296 |

| LPC3250FET296/01 | 256       | 1               | 1                 | -40 to +85             | TFBGA296 |

16/32-bit ARM microcontrollers

| Symbol      | Pin                                                                 | Power supply domain | Туре  | Description                          |

|-------------|---------------------------------------------------------------------|---------------------|-------|--------------------------------------|

| VDD_IOC     | F7,<br>G6,<br>H6, J5                                                | VDD_IOC             | power | 1.8 V or 3.3 V supply for IOC domain |

| VDD_IOD     | F13,<br>F9                                                          | VDD_IOD             | power | 1.8 V to 3.3 V supply for IOD domain |

| VDD_OSC     | T18                                                                 | VDD_OSC             | power | 1.2 V supply for main oscillator     |

| VDD_PLL397  | T16                                                                 | VDD_PLL397          | power | 1.2 V supply for 397x PLL            |

| VDD_PLLHCLK | R17                                                                 | VDD_PLLHCLK         | power | 1.2 V supply for HCLK PLL            |

| VDD_PLLUSB  | P15                                                                 | VDD_PLLUSB          | power | 1.2 V supply for USB PLL             |

| VDD_FUSE    | N14                                                                 | VDD_FUSE            | power | 1.2 V supply                         |

| VDD_RTC     | K14                                                                 | VDD_RTC             | power | 1.2 V supply for RTC I/O             |

| VDD_RTCCORE | L13                                                                 | VDD_RTCCORE         | power | 1.2 V supply for RTC                 |

| VDD_RTCOSC  | N15                                                                 | VDD_RTCOSC          | power | 1.2 V supply for RTC oscillator      |

| VSS_AD      | P13                                                                 | -                   | power | Ground for ADC/touch screen          |

| VSS_CORE    | G8,<br>G10,<br>G12,<br>H7,<br>K12,<br>L7,<br>M9,<br>M10,<br>M12     | -                   | power | Ground for core                      |

| VSS_EMC     | K5,<br>L5,<br>M5,<br>N6,<br>P6,<br>P7,<br>P8,<br>P9,<br>P10,<br>P11 | -                   | power | Ground for EMC                       |

| VSS_IOA     | K13                                                                 | -                   | power | Ground VDD_IOA domain                |

| VSS_IOB     | F6                                                                  | -                   | power | Ground VDD_IOB domain                |

| VSS_IOC     | F5,<br>G5,<br>H5                                                    | -                   | power | Ground VDD_IOC domain                |

| VSS_IOD     | F10,<br>F11,<br>F12,<br>H12                                         | -                   | power | Ground VDD_IOD domain                |

| VSS_OSC     | P14                                                                 | -                   | power | Ground for main oscillator           |

| VSS_PLL397  | T15                                                                 | -                   | power | Ground for 397x PLL                  |

| VSS_PLLHCLK | R18                                                                 | -                   | power | Ground for HCLK PLL                  |

### Table 4. Pin description ...continued

LPC3220\_30\_40\_50

### 16/32-bit ARM microcontrollers

| Supply domain          | Voltage range                        | Related supply<br>pins | Description        |

|------------------------|--------------------------------------|------------------------|--------------------|

| VDD_IOA[1]             | 1.7 V to 1.95 V or<br>2.7 V to 3.6 V | VDD_IOA                | Peripheral supply. |

| VDD_IOB <sup>[1]</sup> | 1.7 V to 1.95 V or<br>2.7 V to 3.6 V | VDD_IOB                | Peripheral supply. |

| VDD_IOC <sup>[1]</sup> | 1.7 V to 1.95 V or<br>2.3 V to 3.6 V | VDD_IOC                | Peripheral supply. |

| VDD_IOD <sup>[1]</sup> | 1.7 V to 1.95 V or<br>2.7 V to 3.6 V | VDD_IOD                | Peripheral supply. |

#### Table 6.Supply domains

[1] The VDD\_IOA, VDD\_IOB, VDD\_IOC, and VDD\_IOD supply domains can be operated at a voltage independent of the other domains as long as all pins connected to the same peripheral are at the same voltage level. There are two special cases for determining supply domain voltages (for details see application note AN10777):

a) Ethernet configured in MII mode: VDD\_IOD must be the same as VDD\_IOB.

b) UART 3 when used with hardware flow control or when sharing an RS-232 transceiver with another UART: VDD\_IOA must be the same as VDD\_IOD.

### 7.5.1.2 Single-Level Cell (SLC) NAND flash controller

The SLC NAND flash controller interfaces to single-level NAND flash devices. DMA page transfers are supported, including a 20-byte DMA read and write FIFO. Hardware support for ECC (Error Checking and Correction) is included for the main data area. Software can correct a single bit error.

### 7.5.2 SD card controller

The SD interface allows access to external SD memory cards. The SD card interface conforms to the SD Memory Card Specification Version 1.01.

### 7.5.2.1 Features

- 1-bit and 4-bit data line interface support.

- DMA is supported through the system DMA controller.

- Provides all functions specific to the SD memory card. These include the clock generation unit, power management control, command and data transfer.

### 7.5.3 External memory controller

The LPC3220/30/40/50 includes a memory controller that supports data bus SDRAM, DDR SDRAM, and static memory devices. The memory controller provides an interface between the system bus and external (off-chip) memory devices.

The controller supports 16-bit and 32-bit wide SDR SDRAM devices of 64 Mbit, 128 Mbit, 128 Mbit, 256 Mbit, and 512 Mbit sizes, as well as 16-bit wide data bus DDR SDRAM devices of 64 Mbit, 128 Mbit, 128 Mbit, 256 Mbit, and 512 Mbit sizes. Two dynamic memory chip selects are supplied, supporting two groups of SDRAM:

- DYCS0 in the address range 0x8000 0000 to 0x9FFF FFFF

- DYCS1 in the address range 0xA000 0000 to 0xBFFF FFFF

The memory controller also supports 8-bit, 16-bit, and 32-bit wide asynchronous static memory devices, including RAM, ROM, and flash, with or without asynchronous page mode. Four static memory chip selects are supplied for SRAM devices:

- CS0 in the address range 0xE000 0000 to 0xE0FF FFFF

- CS1 in the address range 0xE100 0000 to 0xE1FF FFFF

- CS2 in the address range 0xE200 0000 to 0xE2FF FFFF

- CS3 in the address range 0xE300 0000 to 0xE3FF FFFF

The SDRAM controller uses three data ports to allow simultaneous requests from multiple on-chip AHB bus masters and has the following features.

- Dynamic memory interface supports SDRAM, DDR-SDRAM, and low-power variants.

- Read and write buffers to reduce latency and improve performance.

- Static memory features include

- asynchronous page mode read

- programmable wait states

- bus turnaround cycles

- output enable and write enable delays

- extended wait

- Power-saving modes dynamically control EMC\_CKE[1:0] and EMC\_CLK.

- Dynamic memory self-refresh mode supported by software.

- Controller supports 2 k, 4 k, and 8 k row address synchronous memory parts. That is, typical 512 MB, 256 MB, 128 MB, and 16 MB parts, with 8, 16, or 32 data bits per device.

- Two reset domains enable dynamic memory contents to be preserved over a soft reset.

- This controller does not support synchronous static memory devices (burst mode devices).

### 7.6 AHB master peripherals

The LPC3220/30/40/50 implements four AHB master peripherals, which include a General Purpose Direct Memory Access (GPDMA) controller, a 10/100 Ethernet Media Access Controller (MAC), a Universal Serial Bus (USB) controller, and an LCD controller. Each of these four peripherals contain an integral DMA controller optimized to support the performance demands of the peripheral.

### 7.6.1 General Purpose DMA (GPDMA) controller

The GPDMA controller allows peripheral-to memory, memory-to-peripheral, peripheral-to-peripheral, and memory-to-memory transactions. Each DMA stream provides unidirectional serial DMA transfers for a single source and destination. For example, a bidirectional port requires one stream for transmit and one for receive. The source and destination areas can each be either a memory region or a peripheral, and can be accessed through the same AHB master, or one area by each master. The DMA controller supports the following peripheral device transfers.

- Secure Digital (SD) Memory interface

- High-speed UARTs

- I<sup>2</sup>S0 and I<sup>2</sup>S1 ports

- SPI1 and SPI2 interfaces

- SSP0 and SSP1 interfaces

- Memory

The DMA controls eight DMA channels with hardware prioritization. The DMA controller interfaces to the system via two AHB bus masters, each with a full 32-bit data bus width. DMA operations may be set up for 8-bit, 16-bit, and 32-bit data widths, and can be either big-endian or little-endian. Incrementing or non-incrementing addressing for source and destination are supported, as well as programmable DMA burst size. Scatter or gather DMA is supported through the use of linked lists. This means that the source and destination areas do not have to occupy contiguous areas of memory.

### 7.6.2 Ethernet MAC

The Ethernet block contains a full featured 10 Mbit/s or 100 Mbit/s Ethernet MAC designed to provide optimized performance through the use of DMA hardware acceleration. Features include a generous suite of control registers, half or full duplex operation, flow control, control frames, hardware acceleration for transmit retry, receive

condition is indicated via status registers. An interrupt is also generated if enabled. The DMA controller when enabled transfers data between the endpoint buffer and the USB RAM.

### Features

- Fully compliant with USB 2.0 full-speed specification.

- Supports 32 physical (16 logical) endpoints.

- Supports control, bulk, interrupt and isochronous endpoints.

- Scalable realization of endpoints at run time.

- Endpoint maximum packet size selection (up to USB maximum specification) by software at run time.

- RAM message buffer size based on endpoint realization and maximum packet size.

- Supports bus-powered capability with low suspend current.

- Supports DMA transfer on all non-control endpoints.

- One duplex DMA channel serves all endpoints.

- Allows dynamic switching between CPU controlled and DMA modes.

- Double buffer implementation for bulk and isochronous endpoints.

### 7.6.3.2 USB host controller

The host controller enables data exchange with various USB devices attached to the bus. It consists of register interface, serial interface engine and DMA controller. The register interface complies to the *OHCI specification*.

### Features

- OHCI compliant.

- OHCI specifies the operation and interface of the USB host controller and software driver.

- The host controller has four USB states visible to the software driver:

- USBOperational: Process lists and generate SOF tokens.

- USBReset: Forces reset signaling on the bus, SOF disabled.

- USBSuspend: Monitor USB for wake-up activity.

- USBResume: Forces resume signaling on the bus.

- HCCA register points to interrupt and isochronous descriptors list.

- ControlHeadED and BulkHeadED registers point to control and bulk descriptors list.

### 7.6.3.3 USB OTG controller

USB OTG (On-The-Go) is a supplement to the USB 2.0 specification that augments the capability of existing mobile devices and USB peripherals by adding host functionality for connection to USB peripherals.

### Features

• Fully compliant with On-The-Go supplement to the USB Specification 2.0 Revision 1.0.

LPC3220 30 40 50

### 7.8.1 UARTs

The LPC3220/30/40/50 contains seven UARTs. Four are standard UARTs, and three are high-speed UARTs.

### 7.8.1.1 Standard UARTs

The four standard UARTs are compatible with the INS16Cx50. These UARTs support rates up to 460800 bit/s from a 13 MHz peripheral clock.

### Features

- Each standard UART has 64 byte Receive and Transmit FIFOs.

- Receiver FIFO trigger points at 16, 32, 48, and 60 Bytes.

- Transmitter FIFO trigger points at 0, 4, 8, and 16 Bytes.

- Register locations conform to the "550" industry standard.

- Each standard UART has a fractional rate pre-divider and an internal baud rate generator.

- The standard UARTs support three clocking modes: on, off, and auto-clock. The auto-clock mode shuts off the clock to the UART when it is idle.

- UART 6 includes an IrDA mode to support infrared communication.

- The standard UARTs are designed to support data rates of (2400, 4800, 9600, 19200, 38400, 57600, 115200, 230400, 460800) bit/s.

- Each UART includes an internal loopback mode.

### 7.8.1.2 High-speed UARTs

The three high-speed UARTs are designed to support rates up to 921600 bit/s from a 13 MHz peripheral clock for on-board communication in low noise conditions. This is accomplished by changing the over sampling from  $16 \times$  to  $14 \times$  and altering the rate generation logic.

### Features

- Each high-speed UART has 64-byte Receive and Transmit FIFOs.

- Receiver FIFO trigger points at 1, 4, 8, 16, 32, and 48 B.

- Transmitter FIFO trigger points at 0, 4, and 8 B.

- Each high-speed UART has an internal baud rate generator.

- The high-speed UARTs are designed to support data rates of (2400, 4800, 9600, 19200, 38400, 57600, 115200, 230400, 460800, 921600) bit/s.

- The three high speed UARTs only support (8N1) 8-bit data word length, 1-stop bit, no parity, and no flow control as a the communications protocol.

- Each UART includes an internal loopback mode.

### 7.8.2 SPI serial I/O controller

The LPC3220/30/40/50 has two Serial Peripheral Interfaces (SPI). The SPI is a 3-wire serial interface that is able to interface with a large range of serial peripheral or memory devices (SPI mode 0 to 3 compatible slave devices).

## 9. Limiting values

#### Table 7. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).[1]

| Symbol                 | Parameter                                 | Conditions                                        | Notes | Min  | Max  | Unit |

|------------------------|-------------------------------------------|---------------------------------------------------|-------|------|------|------|

| V <sub>DD(1V2)</sub>   | supply voltage (1.2 V)                    |                                                   | [2]   | -0.5 | +1.4 | V    |

| V <sub>DD(EMC)</sub>   | external memory controller supply voltage |                                                   | [3]   | -0.5 | +4.6 | V    |

| V <sub>DDA(3V3)</sub>  | analog supply voltage (3.3 V)             |                                                   | [4]   | -0.5 | +4.6 | V    |

| V <sub>DD(IO)</sub>    | input/output supply voltage               |                                                   | [5]   | -0.5 | +4.6 | V    |

| VIA                    | analog input voltage                      |                                                   |       | -0.5 | +4.6 | V    |

| VI                     | input voltage                             | 1.8 V pins                                        | [6]   | -0.5 | +2.4 | V    |

|                        |                                           | 3.3 V pins                                        | [6]   | -0.5 | +4.6 | V    |

| I <sub>DD</sub>        | supply current                            | per supply pin                                    |       | -    | 100  | mA   |

| I <sub>SS</sub>        | ground current                            | per ground pin                                    |       | -    | 100  | mA   |

| T <sub>stg</sub>       | storage temperature                       |                                                   |       | -65  | +150 | °C   |

| P <sub>tot(pack)</sub> | total power dissipation<br>(per package)  | max. junction temp 125 °C max. ambient temp 85 °C | [7]   | -    | 1.12 | W    |

| V <sub>ESD</sub>       | electrostatic discharge voltage           | НВМ                                               | [8]   | -    | 2500 | V    |

|                        |                                           | CDM                                               | [9]   | -    | 1000 | V    |

[1] The following applies to <u>Table 7</u>:

a) This product includes circuitry specifically designed for the protection of its internal devices from the damaging effects of excessive static charge. Nonetheless, it is suggested that conventional precautions be taken to avoid applying greater than the rated maximum.

b) Parameters are valid over operating temperature range unless otherwise specified. All voltages are with respect to V<sub>SS</sub> unless otherwise noted.

[2] Core, PLL, oscillator, and RTC supplies; applies to pins VDD\_CORE, VDD\_COREFXD, VDD\_OSC, VDD\_PLL397, VDD\_PLLHCLK, VDD\_PLLUSB, VDD\_RTC, VDD\_RTCCORE, and VDD\_RTCOSC.

[3] I/O pad supply; applies to domains VDD\_EMC.

[4] Applies to VDD\_AD pins.

[5] Applies to pins in the following domains VDD\_IOA, VDD\_IOB, VDD\_IOC, and VDD\_IOD.

[6] Including voltage on outputs in 3-state mode.

[7] Based on package heat transfer, not device power consumption. Calculated package thermal resistance (Theta<sub>JA</sub>): 35.766 °C/W (with JEDEC Test Board and 0 m/s airflow, ±15 % accuracy).

[8] Human body model: equivalent to discharging a 100 pF capacitor through a 1.5 kΩ series resistor.

[9] Charge device model per AEC-Q100-011.

# 10. Static characteristics

### Table 8.Static characteristics

$T_{amb} = -40 \ ^{\circ}C$  to +85  $^{\circ}C$ , unless otherwise specified.

| Symbol                                      | Parameter                                    | Conditions                                                                                                  |     | Min  | Тур <u><sup>[1]</sup></u> | Max  | Unit |

|---------------------------------------------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------|-----|------|---------------------------|------|------|

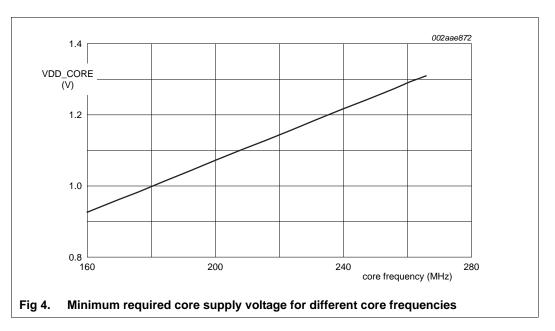

| V <sub>DD(1V2)</sub> supply voltage (1.2 V) |                                              | core supply voltage for<br>full performance;<br>266 MHz (see <u>Figure 4</u> );<br>VDD_CORE supply domain   | [2] | 1.31 | 1.35                      | 1.39 | V    |

|                                             |                                              | core supply voltage for<br>normal performance;<br>208 MHz (see <u>Figure 4</u> );<br>VDD_CORE supply domain | [2] | 1.1  | 1.2                       | 1.39 | V    |

|                                             |                                              | core supply voltage for<br>reduced power;<br>up to 14 MHz CPU;<br>VDD_CORE supply domain                    | [2] | 0.9  | -                         | 1.39 | V    |

|                                             | RTC supply voltage;<br>VDD_RTC supply domain | [3]                                                                                                         | 0.9 | -    | 1.39                      | V    |      |

|                                             | PLL and oscillator supply voltage            | <u>[4]</u>                                                                                                  | 1.1 | 1.2  | 1.39                      | V    |      |

| V <sub>DD(EMC)</sub>                        | external memory                              | in 1.8 V range                                                                                              | [5] | 1.7  | 1.8                       | 1.95 | V    |

|                                             | controller supply voltage                    | in 2.5 V range                                                                                              | [6] | 2.3  | 2.5                       | 2.7  | V    |

|                                             |                                              | in 3.3 V range                                                                                              | [7] | 2.7  | 3.3                       | 3.6  | V    |

| V <sub>DD(IO)</sub>                         | input/output supply<br>voltage               | VDD_IOA, VDD_IOB, and<br>VDD_IOD supply domain<br>in 1.8 V range                                            |     | 1.7  | 1.8                       | 1.95 | V    |

|                                             |                                              | in 3.3 V range                                                                                              |     | 2.7  | 3.3                       | 3.6  | V    |

|                                             |                                              | VDD_IOC supply domain                                                                                       |     | 1.7  | 1.8                       | 1.95 | V    |

|                                             |                                              | in 1.8 V range                                                                                              |     | 1.7  | 1.0                       | 1.95 | V    |

|                                             |                                              | in 3.3 V range                                                                                              |     | 2.3  | 3.3                       | 3.6  | V    |

| V <sub>DDA(3V3)</sub>                       | analog supply voltage<br>(3.3 V)             | applies to pins in VDD_AD power domain                                                                      |     | 2.7  | 3.3                       | 3.6  | V    |

16/32-bit ARM microcontrollers

### 10.1 Minimum core voltage requirements

<u>Figure 4</u> shows the minimum core supply voltage that should be applied for a given core frequency on pin VDD\_CORE to ensure stable operation of the LPC3220/30/40/50.

## 10.2 Power supply sequencing

The LPC32x0 has no power sequencing requirements, that is,  $V_{DD(1V2)}$ ,  $V_{DD(EMC)}$ ,  $V_{DD(IO)}$ , and  $V_{DDA(3V3)}$  can be switched on or off independent of each other. An internal circuit ensures that the system correctly powers up in the absence of core power. During IO power-up this circuit takes care that the system is powered in a defined mode. The same is valid for core power-down.

## 10.3 Power consumption per peripheral

### Table 9. Power consumption per peripheral

$T_{amb} = 25 \text{ °C}$ ; CPU clock = 208 MHz; I-cache/D-cache, MMU disabled; VDD\_CORE = 1.2 V;  $V_{DD(IO)} = 1.8 \text{ V}$ ; USB AHB, IRAM, and IROM clocks always on; all peripherals are at their default state at reset. Peripheral clocks are disabled except for peripheral measured.

| Peripheral                                | I <sub>DD(run)</sub> / mA |

|-------------------------------------------|---------------------------|

| High-speed UART (set to 115 200 Bd (8N1)) | 0.3                       |

| l <sup>2</sup> C-bus                      | 0.3                       |

| SSP                                       | 0.6                       |

| l <sup>2</sup> S                          | 0.5                       |

| DMA                                       | 6.3                       |

| EMC                                       | 7.3                       |

| Multi-level NAND controller               | 1.4                       |

| Single-level NAND controller              | 0.3                       |

| LCD                                       | 5.6                       |

| Ethernet MAC <sup>[1]</sup>               | 2.9                       |

[1] All three Ethernet clocks are in enabled in the MAC\_CLK\_CTRL register (see LPC32x0 User manual).

© NXP Semiconductors N.V. 2014. All rights reserved.

16/32-bit ARM microcontrollers

## **10.5 ADC static characteristics**

#### Table 10. ADC static characteristics

$V_{DDA(3V3)} = 3.3 \text{ V}; T_{amb} = 25 \,^{\circ}\text{C}$  unless otherwise specified; ADC clock frequency 4.5 MHz.

| Symbol              | Parameter                           | Conditions |           | Min | Тур  | Max                   | Unit |

|---------------------|-------------------------------------|------------|-----------|-----|------|-----------------------|------|

| V <sub>IA</sub>     | analog input voltage                |            |           | 0   | -    | V <sub>DDA(3V3)</sub> | V    |

| C <sub>ia</sub>     | analog input capacitance            |            |           | -   | -    | 1                     | pF   |

| E <sub>D</sub>      | differential linearity error        |            | [1][2][3] | -   | ±0.5 | ±1                    | LSB  |

| E <sub>L(adj)</sub> | integral non-linearity              |            | [1][4]    | -   | ±0.6 | ±1                    | LSB  |

| E <sub>O</sub>      | offset error                        |            | [1][5]    | -   | ±1   | ±3                    | LSB  |

| E <sub>G</sub>      | gain error                          |            | [1][6]    | -   | ±0.3 | ±0.6                  | %    |

| ET                  | absolute error                      |            | [1][7]    | -   |      | ±4                    | LSB  |

| R <sub>vsi</sub>    | voltage source interface resistance |            |           | -   | -    | 40                    | kΩ   |

[1] Conditions:  $V_{SSA} = 0 V$  (on pin VSS\_AD);  $V_{DDA(3V3)} = 3.3 V$  (on pin VDD\_AD).

[2] The ADC is monotonic; there are no missing codes.

[3] The differential linearity error (E<sub>D</sub>) is the difference between the actual step width and the ideal step width. See Figure 6.

[4] The integral non-linearity (E<sub>L(adj)</sub>) is the peak difference between the center of the steps of the actual and the ideal transfer curve after appropriate adjustment of gain and offset errors. See <u>Figure 6</u>.

[5] The offset error (E<sub>O</sub>) is the absolute difference between the straight line which fits the actual curve and the straight line which fits the ideal curve. See Figure 6.

[6] The gain error (E<sub>G</sub>) is the relative difference in percent between the straight line fitting the actual transfer curve after removing offset error, and the straight line which fits the ideal transfer curve. See Figure 6.

[7] The absolute error ( $E_T$ ) is the maximum difference between the center of the steps of the actual transfer curve of the non-calibrated ADC and the ideal transfer curve. See Figure 6.

# 11. Dynamic characteristics

## 11.1 Clocking and I/O port pins

### Table 11. Dynamic characteristics

$T_{amb} = -40 \ ^{\circ}C$  to +85  $^{\circ}C$ , unless otherwise specified.<sup>[1]</sup>

| Symbol           | Parameter                  | Conditions |     | Min | Тур | Max | Unit |

|------------------|----------------------------|------------|-----|-----|-----|-----|------|

| Reset            |                            | ·          |     |     |     |     |      |

| tw(RESET)ext     | external RESET pulse width |            | [2] | 10  | -   | -   | ms   |

| External clock   |                            | ·          |     |     |     |     |      |

| f <sub>ext</sub> | external clock frequency   |            | [3] | 1   | 13  | 20  | MHz  |

| Port pins        |                            | ·          |     |     |     |     |      |

| t <sub>r</sub>   | rise time                  |            |     | -   | 5   | -   | ns   |

| t <sub>f</sub>   | fall time                  |            |     | -   | 5   | -   | ns   |

[1] Parameters are valid over operating temperature range unless otherwise specified.

[2] After supply voltages are stable

[3] Supplied by an external crystal.

## 11.2 Static memory controller

#### Table 12. Dynamic characteristics: static external memory interface

$C_L = 25 \text{ pF}, T_{amb} = 20 \text{ °C}, V_{DD(EMC)} = 1.8 \text{ V}, 2.5 \text{ V}, \text{ or } 3.3 \text{ V}.$

| Symbol                | Parameter                        | Notes  | Min | Тур                                               | Max | Unit |

|-----------------------|----------------------------------|--------|-----|---------------------------------------------------|-----|------|

| Common                | to read and write cycles         |        | 1   |                                                   |     |      |

| T <sub>CLCL</sub>     | clock cycle time                 | [1]    | 7.5 | 9.6                                               | -   | ns   |

| t <sub>CSLAV</sub>    | CS LOW to address valid time     |        | -   | 0                                                 | -   | ns   |

| Read cyc              | e parameters                     |        |     |                                                   |     |      |

| t <sub>OELAV</sub>    | OE LOW to address valid time     | [2]    | -   | $0 - WAITOEN \times T_{CLCL}$                     | -   | ns   |

| t <sub>BLSLAV</sub>   | BLS LOW to address valid time    | [2]    | -   | $0 - WAITOEN \times T_{CLCL}$                     | -   | ns   |

| t <sub>CSLOEL</sub>   | CS LOW to OE LOW time            |        | -   | $0 + WAITOEN \times T_{CLCL}$                     | -   | ns   |

| t <sub>CSLBLSL</sub>  | CS LOW to BLS LOW time           | [2]    | -   | $0 + WAITOEN \times T_{CLCL}$                     | -   | ns   |

| t <sub>OELOEH</sub>   | OE LOW to OE HIGH time           | [2][3] | -   | (WAITRD – WAITOEN + 1) $\times$ T <sub>CLCL</sub> | -   | ns   |

| t <sub>BLSLBLSH</sub> | BLS LOW to BLS HIGH time         | [2][3] | -   | (WAITRD – WAITOEN + 1) $\times$ T <sub>CLCL</sub> | -   | ns   |

| t <sub>su(DQ)</sub>   | data input/output set-up time    | [6]    | -   | 8.4                                               | -   | ns   |

| t <sub>h(DQ)</sub>    | data input/output hold time      | [6]    | -   | 0                                                 | -   | ns   |

| t <sub>CSHOEH</sub>   | CS HIGH to OE HIGH time          |        | -   | 0                                                 | -   | ns   |

| t <sub>CSHBLSH</sub>  | CS HIGH to BLS HIGH time         |        | -   | 0                                                 | -   | ns   |

| t <sub>OEHANV</sub>   | OE HIGH to address invalid time  |        | -   | $1 \times T_{CLCL}$                               | -   | ns   |

| t <sub>BLSHANV</sub>  | BLS HIGH to address invalid time |        | -   | $1 \times T_{CLCL}$                               | -   | ns   |

| Write cyc             | e parameters                     |        | 1   |                                                   |     |      |

| t <sub>CSLDV</sub>    | CS LOW to data valid time        |        | -   | 0                                                 | -   | ns   |

| t <sub>CSLWEL</sub>   | CS LOW to WE LOW time            | [4]    | -   | (WAITWEN + 1) $\times$ T <sub>CLCL</sub>          | -   | ns   |

| t <sub>CSLBLSL</sub>  | CS LOW to BLS LOW time           | [4]    | -   | (WAITWEN + 1) $\times$ T <sub>CLCL</sub>          | -   | ns   |

| t <sub>WELDV</sub>    | WE LOW to data valid time        | [4]    | -   | $0 - (WAITWEN + 1) \times T_{CLCL}$               | -   | ns   |

LPC3220\_30\_40\_50 Product data sheet

16/32-bit ARM microcontrollers

| Table 18.       | Dynamic characteristics of SLC NAND flash memory controllercontinued |

|-----------------|----------------------------------------------------------------------|

| $T_{amb} = -40$ | ) ℃ to +85 ℃                                                         |

| Symbol              | Parameter               | Conditions |           | Min | Тур                                                                                    | Max | Unit |

|---------------------|-------------------------|------------|-----------|-----|----------------------------------------------------------------------------------------|-----|------|

| t <sub>WH</sub>     | WE HIGH hold time       | write      | [1][6][7] | -   | T <sub>HCLK</sub> × (Wsu + Wh)                                                         | -   | ns   |

| t <sub>WHR</sub>    | WE HIGH to RE LOW time  | write      | [1][7][9] | -   | $\begin{array}{l} (T_{HCLK} \times Wh) + (2 \times T_{HCLK} \\ \times Wb) \end{array}$ | -   | ns   |

| t <sub>WP</sub>     | WE pulse width          | write      | [1][8]    | -   | $T_{HCLK} \times Ww$                                                                   | -   | ns   |

| t <sub>REHRBL</sub> | RE HIGH to R/B LOW time | write      | [1][3][5] | -   | $(T_{HCLK} \times Rh) + (2 \times T_{HCLK} \times Rb)$                                 | -   | ns   |

[1]  $T_{HCLK} = 1/HCLK$

- [2] Rsu = bit field R\_SETUP[3:0] in register SLC\_TAC[3:0] for reads

- [3] Rh = bit field R\_HOLD[3:0] in register SLC\_TAC[7:4] for reads

- [4] Rw = bit field R\_WIDTH[3:0] in register SLC\_TAC[11:8] for reads

- [5] Rb = bit field R\_RDY[3:0] in register SLC\_TAC[15:12] for reads

- [6] Wsu = bit field W\_SETUP[3:0] in register SLC\_TAC[19:16] for writes

- [7] Wh = bit field W\_HOLD[3:0] in register SLC\_TAC[23:20] for writes

- [8] Ww = bit field W\_WIDTH[3:0] in register SLC\_TAC[27:24] for writes

- [9] Wb = bit field W\_RDY[3:0] in register SLC\_TAC[31:28] for writes

## **NXP Semiconductors**

# LPC3220/30/40/50

16/32-bit ARM microcontrollers

16/32-bit ARM microcontrollers

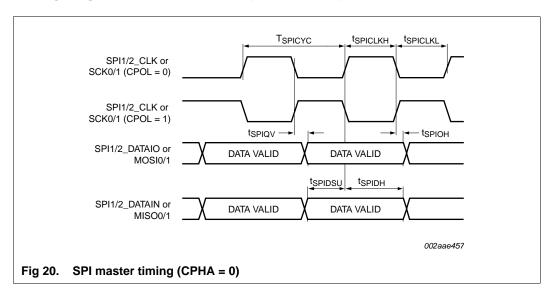

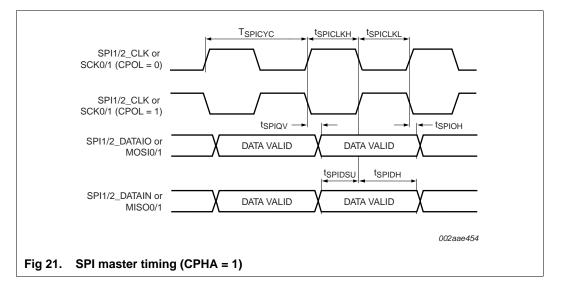

### 11.9.2 Timing diagrams for SPI and SSP (in SPI mode)

16/32-bit ARM microcontrollers

### Table 20. Abbreviations ... continued

| Acronym | Description                                 |

|---------|---------------------------------------------|

| UART    | Universal Asynchronous Receiver/Transmitter |

| USB     | Universal Serial Bus                        |

| VFP     | Vector Floating Point processor             |

# 15. References

- [1] LPC3220/30/40/50 User manual UM10326: http://www.nxp.com/documents/user\_manual/UM10326.pdf

- [2] LPC3220/30/40/50 Errata sheet: http://www.nxp.com/documents/errata\_sheet/ES\_LPC3250.pdf

# 17. Legal information

## 17.1 Data sheet status

| Document status[1][2]          | Product status[3] | Definition                                                                            |

|--------------------------------|-------------------|---------------------------------------------------------------------------------------|

| Objective [short] data sheet   | Development       | This document contains data from the objective specification for product development. |

| Preliminary [short] data sheet | Qualification     | This document contains data from the preliminary specification.                       |

| Product [short] data sheet     | Production        | This document contains the product specification.                                     |

[1] Please consult the most recently issued document before initiating or completing a design.

[2] The term 'short data sheet' is explained in section "Definitions".

[3] The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL <a href="http://www.nxp.com">http://www.nxp.com</a>.

## 17.2 Definitions

**Draft** — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.

**Product specification** — The information and data provided in a Product data sheet shall define the specification of the product as agreed between NXP Semiconductors and its customer, unless NXP Semiconductors and customer have explicitly agreed otherwise in writing. In no event however, shall an agreement be valid in which the NXP Semiconductors product is deemed to offer functions and qualities beyond those described in the Product data sheet.

## 17.3 Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the *Terms and conditions of commercial sale* of NXP Semiconductors.

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) will cause permanent damage to the device. Limiting values are stress ratings only and (proper) operation of the device at these or any other conditions above those given in the Recommended operating conditions section (if present) or the Characteristics sections of this document is not warranted. Constant or repeated exposure to limiting values will permanently and irreversibly affect the quality and reliability of the device.

Terms and conditions of commercial sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at <a href="http://www.nxp.com/profile/terms">http://www.nxp.com/profile/terms</a>, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

**No offer to sell or license** — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

© NXP Semiconductors N.V. 2014. All rights reserved.

LPC3220 30 40 50

### 16/32-bit ARM microcontrollers

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

Non-automotive qualified products — Unless this data sheet expressly states that this specific NXP Semiconductors product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. NXP Semiconductors accepts no liability for inclusion and/or use of non-automotive qualified products in automotive equipment or applications.

In the event that customer uses the product for design-in and use in automotive applications to automotive specifications and standards, customer (a) shall use the product without NXP Semiconductors' warranty of the product for such automotive applications, use and specifications, and (b)

# 18. Contact information

whenever customer uses the product for automotive applications beyond NXP Semiconductors' specifications such use shall be solely at customer's own risk, and (c) customer fully indemnifies NXP Semiconductors for any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond NXP Semiconductors' standard warranty and NXP Semiconductors' product specifications.

## 17.4 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

I<sup>2</sup>C-bus — logo is a trademark of NXP Semiconductors N.V.

For more information, please visit: <u>http://www.nxp.com</u>

For sales office addresses, please send an email to: salesaddresses@nxp.com

LPC3220\_30\_40\_50