Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PSMC, PWM, WDT                               |

| Number of I/O              | 24                                                                        |

| Program Memory Size        | 28KB (16K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 2K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 11x12b; D/A 1x8b, 3x5b                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 28-QFN (6x6)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1788-e-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## PIC16(L)F1788/9

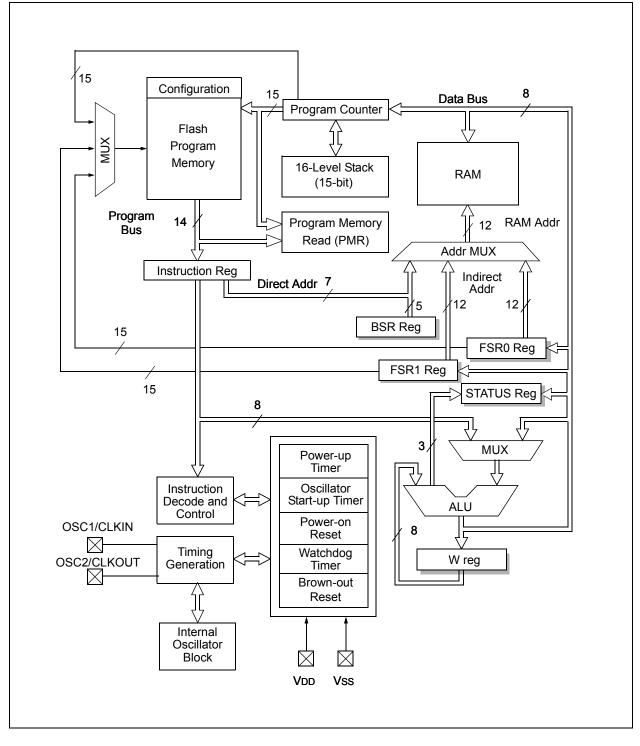

## Pin Diagram – 44-Pin QFN

#### **TABLE 1-3:** PIC16(L)F1789 PINOUT DESCRIPTION (CONTINUED)

| Name                    | Function       | Input<br>Type    | Output<br>Type | Description                                  |

|-------------------------|----------------|------------------|----------------|----------------------------------------------|

| RC4/PSMC1E/SDI/SDA      | RC4            | TTL/ST           | CMOS           | General purpose I/O.                         |

|                         | PSMC1E         | —                | CMOS           | PSMC1 output E.                              |

|                         | SDI            | ST               | _              | SPI data input.                              |

|                         | SDA            | l <sup>2</sup> C | OD             | I <sup>2</sup> C data input/output.          |

| RC5/PSMC1F/SDO          | RC5            | TTL/ST           | CMOS           | General purpose I/O.                         |

|                         | PSMC1F         | _                | CMOS           | PSMC1 output F.                              |

|                         | SDO            |                  | CMOS           | SPI data output.                             |

| RC6/PSMC2A/TX/CK        | RC6            | TTL/ST           | CMOS           | General purpose I/O.                         |

|                         | PSMC2A         |                  | CMOS           | PSMC2 output A.                              |

|                         | ТХ             | _                | CMOS           | EUSART asynchronous transmit.                |

|                         | СК             | ST               | CMOS           | EUSART synchronous clock.                    |

| RC7/PSMC2B/RX/DT        | RC7            | TTL/ST           | CMOS           | General purpose I/O.                         |

|                         | PSMC2B         | —                | CMOS           | PSMC2 output B.                              |

|                         | RX             | ST               | —              | EUSART asynchronous input.                   |

|                         | DT             | ST               | CMOS           | EUSART synchronous data.                     |

| RD0/OPA3IN+             | RD0            | TTL/ST           | CMOS           | General purpose I/O.                         |

|                         | OPA3IN+        | AN               | _              | Operational Amplifier 3 non-inverting input. |

| RD1/AN21/C1IN4-/C2IN4-/ | RD1            | TTL/ST           | CMOS           | General purpose I/O.                         |

| C3IN4-/C4IN4-/OPA3OUT   | AN21           | AN               | _              | ADC Channel 21 input.                        |

|                         | C1IN4-         | AN               | _              | Comparator C4 negative input.                |

|                         | C2IN4-         | AN               | _              | Comparator C4 negative input.                |

|                         | C3IN4-         | AN               |                | Comparator C4 negative input.                |

|                         | C4IN4-         | AN               |                | Comparator C4 negative input.                |

|                         | <b>OPA3OUT</b> |                  | AN             | Operational Amplifier 3 output.              |

| RD2/OPA3IN-/DAC4OUT1    | RD2            | TTL/ST           | CMOS           | General purpose I/O.                         |

|                         | OPA3IN-        | AN               |                | Operational Amplifier 3 inverting input.     |

|                         | DAC4OUT1       |                  | AN             | Digital-to-Analog Converter output.          |

| RD3/PSMC4A              | RD3            | TTL/ST           | CMOS           | General purpose I/O.                         |

|                         | PSMC4A         |                  | CMOS           | PSMC4 output A.                              |

| RD4/PSMC3F              | RD4            | TTL/ST           | CMOS           | General purpose I/O.                         |

|                         | PSMC3F         | _                | CMOS           | PSMC3 output F.                              |

| RD5/PSMC3E              | RD5            | TTL/ST           | CMOS           | General purpose I/O.                         |

|                         | PSMC3E         | _                | CMOS           | PSMC3 output E.                              |

| RD6/C3OUT/PSMC3D        | RD6            | TTL/ST           | CMOS           | General purpose I/O.                         |

|                         | C3OUT          | _                | CMOS           | Comparator C3 output.                        |

|                         | PSMC3D         | _                | CMOS           | PSMC3 output D.                              |

| RD7/C4OUT/PSMC3C        | RD7            | TTL/ST           | CMOS           | General purpose I/O.                         |

|                         | C4OUT          |                  | CMOS           | Comparator C4 output.                        |

|                         | PSMC3C         |                  | CMOS           | PSMC3 output C.                              |

| RE0/AN5/CCP3/PSMC4B     | RE0            | TTL/ST           | _              | General purpose input.                       |

|                         | AN5            | AN               | _              | ADC Channel 5 input.                         |

|                         | CCP3           | ST               | CMOS           | Capture/Compare/PWM3.                        |

|                         | PSMC4B         |                  | CMOS           | PSMC4 output B.                              |

TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels  $I^2C$  = Schmitt Trigger input with  $I^2C$

HV = High Voltage XTAL = Crystal

levels Note 1: Pin functions can be assigned to one of two locations via software. See Register 13-1.

2: All pins have interrupt-on-change functionality.

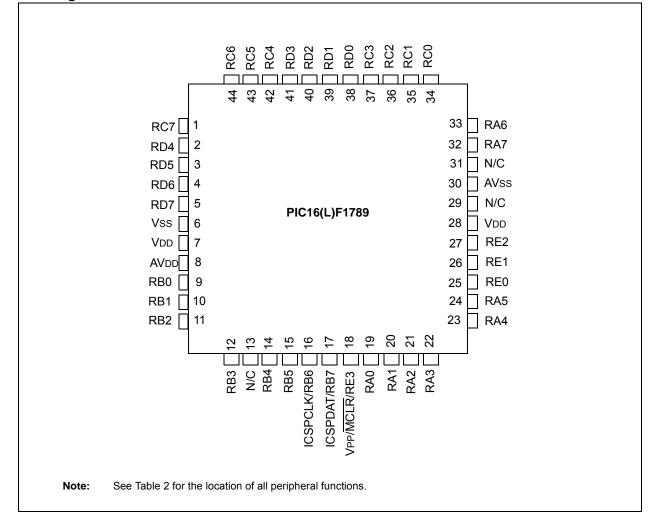

## 2.0 ENHANCED MID-RANGE CPU

This family of devices contain an enhanced mid-range 8-bit CPU core. The CPU has 49 instructions. Interrupt capability includes automatic context saving. The hardware stack is 16 levels deep and has Overflow and Underflow Reset capability. Direct, Indirect, and

FIGURE 2-1: CORE BLOCK DIAGRAM

Relative addressing modes are available. Two File Select Registers (FSRs) provide the ability to read program and data memory.

- · Automatic Interrupt Context Saving

- 16-level Stack with Overflow and Underflow

- File Select Registers

- Instruction Set

## EXAMPLE 3-2: ACCESSING PROGRAM MEMORY VIA FSR

| constants    |                             |

|--------------|-----------------------------|

| DW           | DATA0 ;First constant       |

| DW           | DATA1 ;Second constant      |

| DW           | DATA2                       |

| DW           | DATA3                       |

| my_function  | 1                           |

| ; LOTS       | OF CODE                     |

| MOVLW        | DATA_INDEX                  |

| ADDLW        | LOW constants               |

| MOVWF        | FSR1L                       |

| MOVLW        | HIGH constants ;MSb is set  |

| automatical  | ly                          |

| MOVWF        | FSR1H                       |

| BTFSC        | STATUS,C ;carry from ADDLW? |

| INCF         | FSR1H,f ;yes                |

| MOVIW        | 0[FSR1]                     |

| ; THE PROGRA | AM MEMORY IS IN W           |

| 1            |                             |

# PIC16(L)F1788/9

| IADI             | LE 3-12:               | SPECIAL                              | FUNCTIO                                          | IN REGIS         | IER SUMI        |       | INTINUEL             | り                    | 1                    |                      | 1                               |

|------------------|------------------------|--------------------------------------|--------------------------------------------------|------------------|-----------------|-------|----------------------|----------------------|----------------------|----------------------|---------------------------------|

| Addr             | Name                   | Bit 7                                | Bit 6                                            | Bit 5            | Bit 4           | Bit 3 | Bit 2                | Bit 1                | Bit 0                | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

| Ban              | k 4                    |                                      |                                                  |                  |                 |       |                      |                      |                      |                      |                                 |

| 20Ch             | WPUA                   | WPUA7                                | WPUA6                                            | WPUA5            | WPUA4           | WPUA3 | WPUA2                | WPUA1                | WPUA0                | 1111 1111            | 1111 1111                       |

| 20Dh             | WPUB                   | WPUB7                                | WPUB6                                            | WPUB5            | WPUB4           | WPUB3 | WPUB2                | WPUB1                | WPUB0                | 1111 1111            | 1111 1111                       |

| 20Eh             | WPUC                   | WPUC7                                | WPUC6                                            | WPUC5            | WPUC4           | WPUC3 | WPUC2                | WPUC1                | WPUC0                | 1111 1111            | 1111 1111                       |

| 20Fh             | WPUD <sup>(3)</sup>    | WPUD7                                | WPUD6                                            | WPUD5            | WPUD4           | WPUD3 | WPUD2                | WPUD1                | WPUD0                | 1111 1111            | 1111 1111                       |

| 210h             | WPUE                   | —                                    | —                                                | -                | -               | WPUE3 | WPUE2 <sup>(3)</sup> | WPUE1 <sup>(3)</sup> | WPUE0 <sup>(3)</sup> | 1111                 | 1111                            |

| 211h             | SSP1BUF                | Synchronous                          | Serial Port Re                                   | ceive Buffer/Tra | ansmit Register |       |                      |                      |                      | XXXX XXXX            | uuuu uuuu                       |

| 212h             | SSP1ADD                |                                      |                                                  |                  | ADD<            | 7:0>  |                      |                      |                      | 0000 0000            | 0000 0000                       |

| 213h             | SSP1MSK                |                                      |                                                  |                  | MSK<            | 7:0>  |                      |                      |                      | 1111 1111            | 1111 1111                       |

| 214h             | SSP1STAT               | SMP                                  | CKE                                              | D/A              | Р               | S     | R/W                  | UA                   | BF                   | 0000 0000            | 0000 0000                       |

| 215h             | SSP1CON1               | WCOL                                 | SSPOV                                            | SSPEN            | СКР             |       | SSPN                 | 1<3:0>               |                      | 0000 0000            | 0000 0000                       |

| 216h             | SSP1CON2               | GCEN                                 | ACKSTAT                                          | ACKDT            | ACKEN           | RCEN  | PEN                  | RSEN                 | SEN                  | 0000 0000            | 0000 0000                       |

| 217h             | SSP1CON3               | ACKTIM                               | PCIE                                             | SCIE             | BOEN            | SDAHT | SBCDE                | AHEN                 | DHEN                 | 0000 0000            | 0000 0000                       |

| 218h             |                        |                                      |                                                  | •                | •               |       | •                    |                      | •                    |                      |                                 |

| <br>21Fh         | -                      | Unimplemente                         | d                                                |                  |                 |       |                      |                      |                      | _                    | _                               |

| Ban              | k 5                    |                                      |                                                  |                  |                 |       |                      |                      |                      |                      |                                 |

| 28Ch             | ODCONA                 | Open-Drain Co                        | Dpen-Drain Control for PORTA 0000 0000 0000 0000 |                  |                 |       |                      |                      |                      | 0000 0000            |                                 |

| 28Dh             | ODCONB                 | Open-Drain Control for PORTB         |                                                  |                  |                 |       |                      |                      |                      | 0000 0000            | 0000 0000                       |

| 28Eh             | ODCONC                 | Open-Drain Control for PORTC         |                                                  |                  |                 |       |                      |                      |                      | 0000 0000            | 0000 0000                       |

| 28Fh             | ODCOND <sup>(3)</sup>  | Open-Drain Control for PORTD         |                                                  |                  |                 |       |                      |                      |                      | 0000 0000            | 0000 0000                       |

| 290h             | ODCONE <sup>(3)</sup>  | —                                    | —                                                | —                | —               | —     | ODE2                 | ODE1                 | ODE0                 | 000                  | uuu                             |

| 291h             | CCPR1L                 | Capture/Comp                         | oare/PWM Re                                      | gister 1 (LSB)   |                 |       |                      |                      |                      | xxxx xxxx            | uuuu uuuu                       |

| 292h             | CCPR1H                 | Capture/Comp                         | oare/PWM Re                                      | gister 1 (MSB)   |                 |       |                      |                      |                      | xxxx xxxx            | uuuu uuuu                       |

| 293h             | CCP1CON                | —                                    | —                                                | DC1E             | 8<1:0>          |       | CCP1I                | V<3:0>               |                      | 00 0000              | 00 0000                         |

| 294h             |                        |                                      | ad                                               |                  |                 |       |                      |                      |                      | _                    | _                               |

| 297h             |                        | ommpiemente                          | Jnimplemented — — —                              |                  |                 |       |                      |                      |                      |                      |                                 |

| 298h             | CCPR2L                 | Capture/Compare/PWM Register 2 (LSB) |                                                  |                  |                 |       |                      |                      | xxxx xxxx            | uuuu uuuu            |                                 |

| 299h             | CCPR2H                 | Capture/Comp                         | oare/PWM Re                                      | gister 2 (MSB)   |                 |       |                      |                      |                      | xxxx xxxx            | uuuu uuuu                       |

| 29Ah             | CCP2CON                | —                                    | —                                                | DC2E             | 8<1:0>          |       | CCP2I                | V<3:0>               |                      | 00 0000              | 00 0000                         |

| 29Bh<br><br>29Fh | _                      | Unimplemente                         | Unimplemented                                    |                  |                 |       |                      |                      |                      | -                    | -                               |

| Ban              | k 6                    |                                      |                                                  |                  |                 |       |                      |                      |                      |                      |                                 |

| 30Ch             | SLRCONA                | Slew Rate Cor                        | ntrol for PORT                                   | Ā                |                 |       |                      |                      |                      | 0000 0000            | 0000 0000                       |

| 30Dh             | SLRCONB                | Slew Rate Cor                        | Slew Rate Control for PORTB                      |                  |                 |       |                      |                      |                      | 0000 0000            | 0000 0000                       |

| 30Eh             | SLRCONC                | Slew Rate Control for PORTC          |                                                  |                  |                 |       |                      |                      | 1                    | 0000 0000            |                                 |

| 30Fh             | SLRCOND(3)             | Slew Rate Cor                        | ntrol for PORT                                   | D                |                 |       |                      |                      |                      | 0000 0000            | 0000 0000                       |

| 310h             | SLRCONE <sup>(3)</sup> | —                                    | —                                                | —                | —               | —     | SLRE2                | SLRE1                | SLRE0                | 111                  | 111                             |

| 311h             | CCPR3L                 | Capture/Comp                         | are/PWM Re                                       | gister 3 (LSB)   |                 |       |                      |                      |                      | xxxx xxxx            | uuuu uuuu                       |

| 312h             | CCPR3H                 | Capture/Comp                         | are/PWM Re                                       | gister 3 (MSB)   |                 |       |                      |                      |                      | xxxx xxxx            | uuuu uuuu                       |

| 313h             | CCP3CON                | —                                    | —                                                | DC3B             | 8<1:0>          |       | CCP3I                | M<3:0>               |                      | 00 0000              | 00 0000                         |

| 314h<br><br>31Fh | _                      | Unimplemente                         | ed                                               | -                |                 |       |                      |                      |                      | -                    | _                               |

x = unknown, u = unchanged, g = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'. These registers can be addressed from any bank. Unimplemented, read as '1'. PIC16(L)F1789 only. Legend:

Note

1: 2:

3:

PIC16F1788/9 only. 4:

## 4.3 Code Protection

Code protection allows the device to be protected from unauthorized access. Program memory protection and data EEPROM protection are controlled independently. Internal access to the program memory and data EEPROM are unaffected by any code protection setting.

#### 4.3.1 PROGRAM MEMORY PROTECTION

The entire program memory space is protected from external reads and writes by the  $\overline{CP}$  bit in Configuration Words. When  $\overline{CP} = 0$ , external reads and writes of program memory are inhibited and a read will return all '0's. The CPU can continue to read program memory, regardless of the protection bit settings. Writing the program memory is dependent upon the write protection setting. See **Section 4.4** "Write **Protection**" for more information.

## 4.3.2 DATA EEPROM PROTECTION

The entire data EEPROM is protected from external reads and writes by the CPD bit. When CPD = 0, external reads and writes of data EEPROM are inhibited. The CPU can continue to read and write data EEPROM regardless of the protection bit settings.

## 4.4 Write Protection

Write protection allows the device to be protected from unintended self-writes. Applications, such as bootloader software, can be protected while allowing other regions of the program memory to be modified.

The WRT<1:0> bits in Configuration Words define the size of the program memory block that is protected.

## 4.5 User ID

Four memory locations (8000h-8003h) are designated as ID locations where the user can store checksum or other code identification numbers. These locations are readable and writable during normal execution. See **Section 12.5 "User ID, Device ID and Configuration Word Access**" for more information on accessing these memory locations. For more information on checksum calculation, see the *"PIC16(L)F178X Memory Programming Specification"* (DS41457).

## 6.4 Two-Speed Clock Start-up Mode

Two-Speed Start-up mode provides additional power savings by minimizing the latency between external oscillator start-up and code execution. In applications that make heavy use of the Sleep mode, Two-Speed Start-up will remove the external oscillator start-up time from the time spent awake and can reduce the overall power consumption of the device. This mode allows the application to wake-up from Sleep, perform a few instructions using the INTOSC internal oscillator block as the clock source and go back to Sleep without waiting for the external oscillator to become stable.

Two-Speed Start-up provides benefits when the oscillator module is configured for LP, XT or HS modes. The Oscillator Start-up Timer (OST) is enabled for these modes and must count 1024 oscillations before the oscillator can be used as the system clock source.

If the oscillator module is configured for any mode other than LP, XT or HS mode, then Two-Speed Start-up is disabled. This is because the external clock oscillator does not require any stabilization time after POR or an exit from Sleep.

If the OST count reaches 1024 before the device enters Sleep mode, the OSTS bit of the OSCSTAT register is set and program execution switches to the external oscillator. However, the system may never operate from the external oscillator if the time spent awake is very short.

| Note: | Executing a SLEEP instruction will abort    |

|-------|---------------------------------------------|

|       | the oscillator start-up time and will cause |

|       | the OSTS bit of the OSCSTAT register to     |

|       | remain clear.                               |

## TABLE 6-1: OSCILLATOR SWITCHING DELAYS

#### Switch From Switch To Frequency **Oscillator Delav** LFINTOSC<sup>(1)</sup> 31 kHz MFINTOSC<sup>(1)</sup> Oscillator Warm-up Delay Twarm<sup>(2)</sup> 31.25 kHz-500 kHz Sleep HFINTOSC<sup>(1)</sup> 31.25 kHz-16 MHz EC, RC<sup>(1)</sup> Sleep/POR DC - 32 MHz 2 cycles EC. RC<sup>(1)</sup> LFINTOSC DC - 32 MHz 1 cycle of each Timer1 Oscillator Sleep/POR 32 kHz-20 MHz 1024 Clock Cycles (OST) LP, XT, HS<sup>(1)</sup> MFINTOSC<sup>(1)</sup> 31.25 kHz-500 kHz Any clock source 2 µs (approx.) HFINTOSC<sup>(1)</sup> 31.25 kHz-16 MHz LFINTOSC<sup>(1)</sup> Any clock source 31 kHz 1 cycle of each Any clock source Timer1 Oscillator 32 kHz 1024 Clock Cycles (OST) PLL inactive PLL active 16-32 MHz 2 ms (approx.)

Note 1: PLL inactive.

2: See Section 31.0 "Electrical Specifications".

### 6.4.1 TWO-SPEED START-UP MODE CONFIGURATION

Two-Speed Start-up mode is configured by the following settings:

- IESO (of the Configuration Words) = 1; Internal/External Switchover bit (Two-Speed Start-up mode enabled).

- SCS (of the OSCCON register) = 00.

- FOSC<2:0> bits in the Configuration Words configured for LP, XT or HS mode.

Two-Speed Start-up mode is entered after:

- Power-on Reset (POR) and, if enabled, after Power-up Timer (PWRT) has expired, or

- Wake-up from Sleep.

| R-1/q                                                                                                              | R-0/q                                                                                                                                                                                                   | R-q/q                                                     | R-0/q          | R-0/q          | R-q/q                    | R-0/0            | R-0/q        |

|--------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|----------------|----------------|--------------------------|------------------|--------------|

| T1OSCR                                                                                                             | PLLR                                                                                                                                                                                                    | OSTS                                                      | HFIOFR         | HFIOFL         | MFIOFR                   | LFIOFR           | HFIOFS       |

| bit 7                                                                                                              |                                                                                                                                                                                                         |                                                           |                |                |                          |                  | bit 0        |

|                                                                                                                    |                                                                                                                                                                                                         |                                                           |                |                |                          |                  |              |

| Legend:                                                                                                            |                                                                                                                                                                                                         |                                                           |                |                |                          |                  |              |

| R = Readable                                                                                                       | bit                                                                                                                                                                                                     | W = Writable                                              | bit            | U = Unimpler   | mented bit, read         | l as '0'         |              |

| u = Bit is unch                                                                                                    | anged                                                                                                                                                                                                   | x = Bit is unkr                                           | nown           | -n/n = Value a | at POR and BO            | R/Value at all o | other Resets |

| '1' = Bit is set                                                                                                   |                                                                                                                                                                                                         | '0' = Bit is cle                                          | ared           | q = Condition  | al                       |                  |              |

| bit 7                                                                                                              | <u>If T1OSCEN</u><br>1 = Timer1<br>0 = Timer1<br><u>If T1OSCEN</u>                                                                                                                                      | oscillator is rea                                         | dy<br>ready    |                |                          |                  |              |

| bit 6                                                                                                              | <b>PLLR</b> 4x PLI<br>1 = 4x PLL<br>0 = 4x PLL                                                                                                                                                          | is ready                                                  |                |                |                          |                  |              |

| bit 5                                                                                                              | 1 = Running                                                                                                                                                                                             | lator Start-up Ti<br>g from the clock<br>g from an intern | defined by the | e FOSC<2:0> I  | oits of the Confi<br>00) | guration Word    | S            |

| bit 4                                                                                                              |                                                                                                                                                                                                         |                                                           |                |                |                          |                  |              |

| bit 3                                                                                                              |                                                                                                                                                                                                         |                                                           |                |                |                          |                  |              |

| bit 2 MFIOFR: Medium-Frequency Internal Oscillator Ready bit<br>1 = MFINTOSC is ready<br>0 = MFINTOSC is not ready |                                                                                                                                                                                                         |                                                           |                |                |                          |                  |              |

| bit 1                                                                                                              |                                                                                                                                                                                                         |                                                           |                |                |                          |                  |              |

| bit 0                                                                                                              | <ul> <li>0 = LFINTOSC is not ready</li> <li>HFIOFS: High-Frequency Internal Oscillator Stable bit</li> <li>1 = HFINTOSC is at least 0.5% accurate</li> <li>0 = HFINTOSC is not 0.5% accurate</li> </ul> |                                                           |                |                |                          |                  |              |

## REGISTER 6-2: OSCSTAT: OSCILLATOR STATUS REGISTER

## PIC16(L)F1788/9

## 13.10 Register Definitions: PORTD

### REGISTER 13-26: PORTD: PORTD REGISTER

| R/W-x/u                                 | R/W-x/u           | R/W-x/u                                                              | R/W-x/u                            | R/W-x/u                                                                        | R/W-x/u                                                                                                       | R/W-x/u                                                                                                                                 |  |

|-----------------------------------------|-------------------|----------------------------------------------------------------------|------------------------------------|--------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--|

| RD6                                     | RD5               | RD4                                                                  | RD3                                | RD2                                                                            | RD1                                                                                                           | RD0                                                                                                                                     |  |

|                                         |                   |                                                                      |                                    |                                                                                |                                                                                                               | bit 0                                                                                                                                   |  |

|                                         |                   |                                                                      |                                    |                                                                                |                                                                                                               |                                                                                                                                         |  |

|                                         |                   |                                                                      |                                    |                                                                                |                                                                                                               |                                                                                                                                         |  |

| R = Readable bit W = Writable bit       |                   |                                                                      | U = Unimplemented bit, read as '0' |                                                                                |                                                                                                               |                                                                                                                                         |  |

| I = Bit is unchanged x = Bit is unknown |                   | -n/n = Value at POR and BOR/Value at all other Resets                |                                    |                                                                                |                                                                                                               |                                                                                                                                         |  |

|                                         | '0' = Bit is clea | ared                                                                 |                                    |                                                                                |                                                                                                               |                                                                                                                                         |  |

|                                         | RD6               | RD6     RD5       it     W = Writable       nged     x = Bit is unkr | RD6 RD5 RD4                        | RD6RD5RD4RD3itW = Writable bitU = Unimplerngedx = Bit is unknown-n/n = Value a | RD6RD5RD4RD3RD2itW = Writable bitU = Unimplemented bit, readngedx = Bit is unknown-n/n = Value at POR and BOI | RD6RD5RD4RD3RD2RD1itW = Writable bitU = Unimplemented bit, read as '0'ngedx = Bit is unknown-n/n = Value at POR and BOR/Value at all or |  |

bit 7-0 **RD<7:0>**: PORTD General Purpose I/O Pin bits<sup>(1)</sup> 1 = Port pin is ≥ VIH 0 = Port pin is ≤ VIL

### REGISTER 13-27: TRISD: PORTD TRI-STATE REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TRISD7  | TRISD6  | TRISD5  | TRISD4  | TRISD3  | TRISD2  | TRISD1  | TRISD0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

**TRISD<7:0>:** PORTD Tri-State Control bits 1 = PORTD pin configured as an input (tri-stated)

0 = PORTD pin configured as an output

## REGISTER 13-28: LATD: PORTD DATA LATCH REGISTER

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| LATD7   | LATD6   | LATD5   | LATD4   | LATD3   | LATD2   | LATD1   | LATD0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-0 LATD<7:0>: PORTD Output Latch Value bits<sup>(1)</sup>

**Note 1:** Writes to PORTD are actually written to corresponding LATD register. Reads from PORTD register is return of actual I/O pin values.

**Note 1:** Writes to PORTD are actually written to corresponding LATD register. Reads from PORTD register is return of actual I/O pin values.

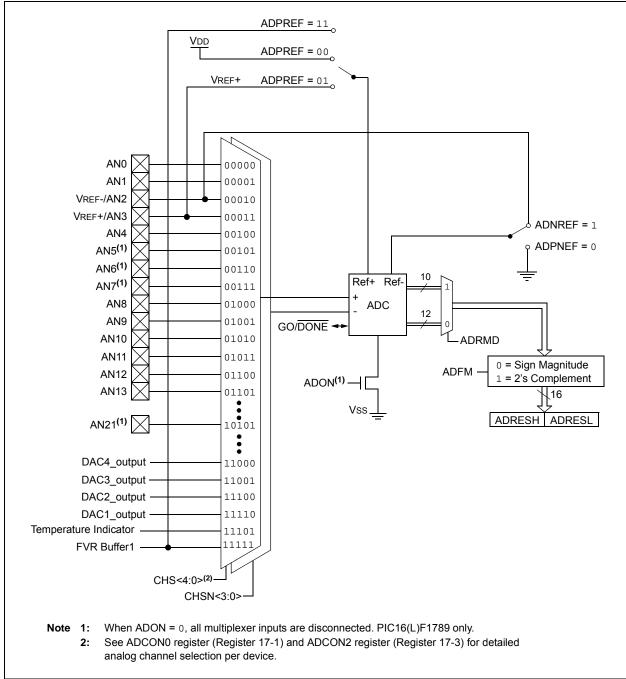

## 17.0 ANALOG-TO-DIGITAL CONVERTER (ADC) MODULE

The Analog-to-Digital Converter (ADC) allows conversion of a single-ended and differential analog input signals to a 12-bit binary representation of that signal. This device uses analog inputs, which are multiplexed into a single sample and hold circuit. The output of the sample and hold is connected to the input of the converter. The converter generates a 12-bit binary result via successive approximation and stores

## FIGURE 17-1: ADC BLOCK DIAGRAM

the conversion result into the ADC result registers (ADRESH:ADRESL register pair). Figure 17-1 shows the block diagram of the ADC.

The ADC voltage reference is software selectable to be either internally generated or externally supplied.

The ADC can generate an interrupt upon completion of a conversion. This interrupt can be used to wake-up the device from Sleep.

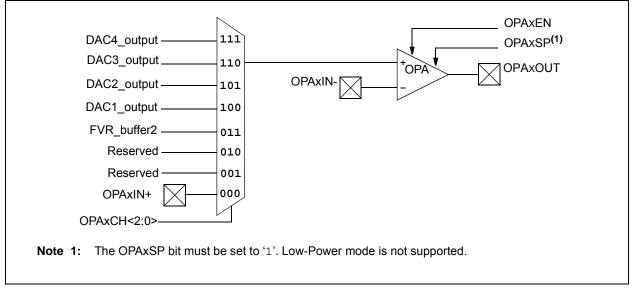

## 18.0 OPERATIONAL AMPLIFIER (OPA) MODULES

The Operational Amplifier (OPA) is a standard three-terminal device requiring external feedback to operate. The OPA module has the following features:

- External connections to I/O ports

- Low leakage inputs

- · Factory Calibrated Input Offset Voltage

## 21.0 COMPARATOR MODULE

Comparators are used to interface analog circuits to a digital circuit by comparing two analog voltages and providing a digital indication of their relative magnitudes. Comparators are very useful mixed signal building blocks because they provide analog functionality independent of program execution. The analog comparator module includes the following features:

- · Independent comparator control

- Programmable input selection

- · Comparator output is available internally/externally

- Programmable output polarity

- Interrupt-on-change

- · Wake-up from Sleep

- Programmable Speed/Power optimization

- · PWM shutdown

- Programmable and fixed voltage reference

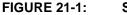

## 21.1 Comparator Overview

A single comparator is shown in Figure 21-1 along with the relationship between the analog input levels and the digital output. When the analog voltage at VIN+ is less than the analog voltage at VIN-, the output of the comparator is a digital low level. When the analog voltage at VIN+ is greater than the analog voltage at VIN-, the output of the comparator is a digital high level.

The comparators available for this device are located in Table 21-1.

#### TABLE 21-1: COMPARATOR AVAILABILITY PER DEVICE

| Device          | C1 | C2 | C3 | C4 |

|-----------------|----|----|----|----|

| PIC16(L)F1788/9 | •  | ٠  | ٠  | ٠  |

#### SINGLE COMPARATOR

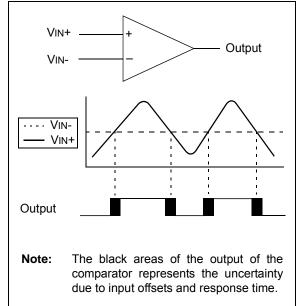

## 25.3 PWM Overview

Pulse-Width Modulation (PWM) is a scheme that provides power to a load by switching quickly between fully on and fully off states. The PWM signal resembles a square wave where the high portion of the signal is considered the on state and the low portion of the signal is considered the off state. The high portion, also known as the pulse width, can vary in time and is defined in steps. A larger number of steps applied, which lengthens the pulse width, also supplies more power to the load. Lowering the number of steps applied, which shortens the pulse width, supplies less power. The PWM period is defined as the duration of one complete cycle or the total amount of on and off time combined.

PWM resolution defines the maximum number of steps that can be present in a single PWM period. A higher resolution allows for more precise control of the pulse width time and in turn the power that is applied to the load.

The term duty cycle describes the proportion of the on time to the off time and is expressed in percentages, where 0% is fully off and 100% is fully on. A lower duty cycle corresponds to less power applied and a higher duty cycle corresponds to more power applied.

Figure 25-3 shows a typical waveform of the PWM signal.

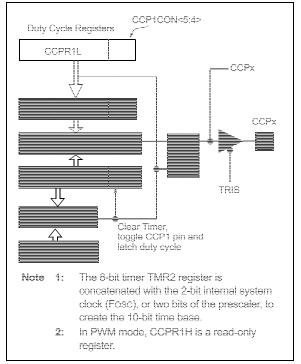

#### 25.3.1 STANDARD PWM OPERATION

The standard PWM function described in this section is available and identical for all CCP modules.

The standard PWM mode generates a Pulse-Width Modulation (PWM) signal on the CCPx pin with up to ten bits of resolution. The period, duty cycle, and resolution are controlled by the following registers:

- PR2 registers

- · T2CON registers

- · CCPRxL registers

- · CCPxCON registers

Figure 25-4 shows a simplified block diagram of PWM operation.

- Note 1: The corresponding TRIS bit must be cleared to enable the PWM output on the CCPx pin.

- 2: Clearing the CCPxCON register will relinquish control of the CCPx pin.

#### FIGURE 25-3: CCP PWM OUTPUT SIGNAL

SIMPLIFIED PWM BLOCK DIAGRAM

|          | ••••••       | •••••         |                                 |        |        |        |        |         |                     |

|----------|--------------|---------------|---------------------------------|--------|--------|--------|--------|---------|---------------------|

| Name     | Bit 7        | Bit 6         | Bit 5                           | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0   | Register<br>on Page |

| APFCON1  | C2OUTSEL     | CC1PSEL       | SDOSEL                          | SCKSEL | SDISEL | TXSEL  | RXSEL  | CCP2SEL | 132                 |

| APFCON2  | —            | _             | _                               | _      | _      | SSSE   | L<1:0> | CCP3SEL | 231                 |

| CCP1CON  | —            | _             | DC1B                            | <1:0>  |        | CCP1   | V<3:0> |         | 231                 |

| CCP2CON  | —            | _             | DC2B                            | <1:0>  |        | CCP2   | √<3:0> |         | 231                 |

| CCP33CON | —            | _             | DC3B                            | <1:0>  |        | CCP3   | V<3:0> |         | 231                 |

| INTCON   | GIE          | PEIE          | TMR0IE                          | INTE   | IOCIE  | TMR0IF | INTF   | IOCIF   | 97                  |

| PIE1     | TMR1GIE      | ADIE          | RCIE                            | TXIE   | SSP1IE | CCP1IE | TMR2IE | TMR1IE  | 97                  |

| PIE2     | OSFIE        | C2IE          | C1IE                            | EEIE   | BCL1IE | C4IE   | C3IE   | CCP2IE  | 99                  |

| PIE3     | —            | _             | _                               | CCP3IE | -      | —      | —      | —       | 100                 |

| PIR1     | TMR1GIF      | ADIF          | RCIF                            | TXIF   | SSP1IF | CCP1IF | TMR2IF | TMR1IF  | 102                 |

| PIR2     | OSFIF        | C2IF          | C1IF                            | EEIF   | BCL1IF | C4IF   | C3IF   | CCP2IF  | 103                 |

| PIR3     | —            | _             | _                               | CCP3IF | -      | —      | —      | —       | 104                 |

| PR2      | Timer2 Perio | d Register    |                                 |        |        |        |        |         | 220*                |

| T2CON    | —            |               | T2OUTPS<3:0> TMR2ON T2CKPS<1:0> |        |        |        |        |         |                     |

| TMR2     | Timer2 Modu  | lule Register |                                 |        |        |        |        |         | 220                 |

| TRISA    | TRISA7       | TRISA6        | TRISA5                          | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0  | 136                 |

|          |              |               |                                 |        |        |        |        |         |                     |

## TABLE 25-3: SUMMARY OF REGISTERS ASSOCIATED WITH STANDARD PWM

Legend: — = Unimplemented location, read as '0'. Shaded cells are not used by the PWM. \* Page provides register information.

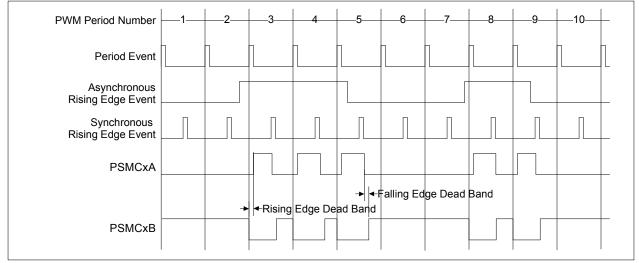

## 26.3.8 PULSE-SKIPPING PWM WITH COMPLEMENTARY OUTPUTS

The pulse-skipping PWM is used to generate a series of fixed-length pulses that may or not be triggered at each period event. If any of the sources enabled to generate a rising edge event are high when a period event occurs, a pulse will be generated. If the rising edge sources are low at the period event, no pulse will be generated.

The rising edge occurs based upon the value in the PSMCxPH register pair.

The falling edge event always occurs according to the enabled event inputs without qualification between any two inputs.

#### 26.3.8.1 Mode Features

- · Dead-band control is available

- · No steering control available

- Primary PWM is output on only PSMCxA.

- · Complementary PWM is output on only PSMCxB.

### 26.3.8.2 Waveform Generation

#### Rising Edge Event

If any enabled asynchronous rising edge event = 1 when there is a period event, then upon the next synchronous rising edge event:

- · Complementary output is set inactive

- Dead-band rising is activated (if enabled)

- · Primary output is set active

#### Falling Edge Event

- · Primary output is set inactive

- Dead-band falling is activated (if enabled)

- · Complementary output is set active

Note: To use this mode, an external source must be used for the determination of whether or not to generate the set pulse. If the phase time base is used, it will either always generate a pulse or never generate a pulse based on the PSMCxPH value.

### FIGURE 26-11: PULSE-SKIPPING WITH COMPLEMENTARY OUTPUT PWM WAVEFORM

## 28.4 EUSART Baud Rate Generator (BRG)

The Baud Rate Generator (BRG) is an 8-bit or 16-bit timer that is dedicated to the support of both the asynchronous and synchronous EUSART operation. By default, the BRG operates in 8-bit mode. Setting the BRG16 bit of the BAUDCON register selects 16-bit mode.

The SPBRGH, SPBRGL register pair determines the period of the free running baud rate timer. In Asynchronous mode the multiplier of the baud rate period is determined by both the BRGH bit of the TXSTA register and the BRG16 bit of the BAUDCON register. In Synchronous mode, the BRGH bit is ignored.

Table 28-3 contains the formulas for determining the baud rate. Example 28-1 provides a sample calculation for determining the baud rate and baud rate error.

Typical baud rates and error values for various asynchronous modes have been computed for your convenience and are shown in Table 28-3. It may be advantageous to use the high baud rate (BRGH = 1), or the 16-bit BRG (BRG16 = 1) to reduce the baud rate error. The 16-bit BRG mode is used to achieve slow baud rates for fast oscillator frequencies.

Writing a new value to the SPBRGH, SPBRGL register pair causes the BRG timer to be reset (or cleared). This ensures that the BRG does not wait for a timer overflow before outputting the new baud rate.

If the system clock is changed during an active receive operation, a receive error or data loss may result. To avoid this problem, check the status of the RCIDL bit to make sure that the receive operation is idle before changing the system clock.

## EXAMPLE 28-1: CALCULATING BAUD RATE ERROR

For a device with Fosc of 16 MHz, desired baud rate of 9600, Asynchronous mode, 8-bit BRG: Fosc Desired Baud Rate =  $\frac{1000}{64([SPBRGH:SPBRGL] + 1)}$ Solving for SPBRGH:SPBRGL: Fosc  $X = \frac{Desired Baud Rate}{-1}$ 64 16000000  $\frac{9600}{64} - 1$ = [25.042] = 25 Calculated Baud Rate =  $\frac{16000000}{64(25+1)}$ = 9615Error = Calc. Baud Rate – Desired Baud Rate Desired Baud Rate  $= \frac{(9615 - 9600)}{9600} = 0.16\%$

## 31.3 DC Characteristics

## TABLE 31-1:SUPPLY VOLTAGE

| PIC16LF1788/9  |        |                                                        |            | Standard Operating Conditions (unless otherwise stated) |            |        |                                                     |  |  |  |  |

|----------------|--------|--------------------------------------------------------|------------|---------------------------------------------------------|------------|--------|-----------------------------------------------------|--|--|--|--|

| PIC16F         | 1788/9 |                                                        |            |                                                         |            |        |                                                     |  |  |  |  |

| Param<br>. No. | Sym.   | Characteristic Min. Typ† Max. Units                    |            | Conditions                                              |            |        |                                                     |  |  |  |  |

| D001           | Vdd    | Supply Voltage (VDDMIN, VDDMAX)                        |            |                                                         |            |        |                                                     |  |  |  |  |

|                |        |                                                        | 1.8<br>2.5 | -                                                       | 3.6<br>3.6 | V<br>V | Fosc ≤ 16 MHz:<br>Fosc ≤ 32 MHz ( <b>Note 2</b> )   |  |  |  |  |

| D001           |        |                                                        | 2.3<br>2.5 | _                                                       | 5.5<br>5.5 | V<br>V | Fosc ≤ 16 MHz:<br>Fosc ≤ 32 MHz ( <b>Note 2</b> )   |  |  |  |  |

| D002*          | Vdr    | RAM Data Retention Voltage <sup>(1)</sup>              |            |                                                         |            |        |                                                     |  |  |  |  |

|                |        |                                                        | 1.5        | _                                                       | _          | V      | Device in Sleep mode                                |  |  |  |  |

| D002*          |        |                                                        | 1.7        | _                                                       | —          | V      | Device in Sleep mode                                |  |  |  |  |

|                | VPOR*  | Power-on Reset Release Voltage                         | _          | 1.6                                                     | _          | V      |                                                     |  |  |  |  |

|                | VPORR* | Power-on Reset Rearm Voltage                           |            |                                                         |            |        |                                                     |  |  |  |  |

|                |        |                                                        | _          | 0.8                                                     | _          | V      | Device in Sleep mode                                |  |  |  |  |

|                |        |                                                        | _          | 1.5                                                     | _          | V      | Device in Sleep mode                                |  |  |  |  |

| D003           | VFVR   | Fixed Voltage Reference                                | -4         | —                                                       | 4          | %      | 1.024V, VDD $\geq 2.5V$                             |  |  |  |  |

|                |        | Voltage <sup>(3)</sup>                                 | -4         | _                                                       | 4          | %      | $2.048V, VDD \geq 2.5V$                             |  |  |  |  |

|                |        |                                                        | -5         | _                                                       | 5          | %      | $4.096V, VDD \ge 4.75V$                             |  |  |  |  |

| D004*          | SVDD   | VDD Rise Rate to ensure internal Power-on Reset signal | 0.05       | —                                                       | -          | V/ms   | See Section 5.1 "Power-On Reset (POR)" for details. |  |  |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.3V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

2: PLL required for 32 MHz operation.

3: Industrial temperature range only.

| PIC16LF1788/9 |                         | Operating Conditions: (unless otherwise stated)<br>Low-Power Sleep Mode |          |               |                |       |            |                                 |  |  |

|---------------|-------------------------|-------------------------------------------------------------------------|----------|---------------|----------------|-------|------------|---------------------------------|--|--|

| PIC16F17      | Low-Po                  | Low-Power Sleep Mode, VREGPM = 1                                        |          |               |                |       |            |                                 |  |  |

| Param         | Device Characteristics  | Min                                                                     | <b>T</b> | Max.<br>+85°C | Max.<br>+125°C | Units | Conditions |                                 |  |  |

| No.           |                         | Min.                                                                    | Тур†     |               |                |       | Vdd        | Note                            |  |  |

|               | Power-down Base Current | (IPD) <sup>(2)</sup>                                                    |          |               |                |       |            |                                 |  |  |

| D029          |                         | _                                                                       | 0.05     | 2             | 9              | μA    | 1.8        | ADC Current (Note 3),           |  |  |

|               |                         | _                                                                       | 0.08     | 3             | 10             | μA    | 3.0        | no conversion in progress       |  |  |

| D029          |                         | —                                                                       | 0.3      | 4             | 12             | μA    | 2.3        | ADC Current (Note 3),           |  |  |

|               |                         | _                                                                       | 0.4      | 5             | 13             | μA    | 3.0        | no conversion in progress       |  |  |

|               |                         | —                                                                       | 0.5      | 7             | 16             | μA    | 5.0        |                                 |  |  |

| D030          |                         | _                                                                       | 250      | —             | —              | μA    | 1.8        | ADC Current (Note 3),           |  |  |

|               |                         | —                                                                       | 280      | —             | —              | μA    | 3.0        | conversion in progress          |  |  |

| D030          |                         | —                                                                       | 230      | —             | —              | μA    | 2.3        | ADC Current (Note 3, Note 4,    |  |  |

|               |                         | —                                                                       | 250      | —             | —              | μA    | 3.0        | Note 5), conversion in progress |  |  |

|               |                         |                                                                         | 350      | —             | —              | μA    | 5.0        |                                 |  |  |

| D031          |                         | —                                                                       | 250      | 650           | —              | μA    | 3.0        | Op Amp (High power)             |  |  |

| D031          |                         |                                                                         | 250      | 650           | —              | μA    | 3.0        | Op Amp (High power) (Note 5)    |  |  |

|               |                         | —                                                                       | 350      | 850           |                | μA    | 5.0        |                                 |  |  |

| D032          |                         | —                                                                       | 250      | 650           | —              | μA    | 1.8        | Comparator, Normal-Power mode   |  |  |

|               |                         | —                                                                       | 300      | 700           | _              | μA    | 3.0        |                                 |  |  |

| D032          |                         |                                                                         | 280      | 650           | _              | μA    | 2.3        | Comparator, Normal-Power mode   |  |  |

|               |                         |                                                                         | 300      | 700           | _              | μA    | 3.0        | (Note 5)                        |  |  |

|               |                         | —                                                                       | 310      | 700           | -              | μA    | 5.0        |                                 |  |  |

## TABLE 31-3: POWER-DOWN CURRENTS (IPD)<sup>(1,2,4)</sup> (CONTINUED)

These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The peripheral current is the sum of the base IPD and the additional current consumed when this peripheral is enabled. The peripheral △ current can be determined by subtracting the base IDD or IPD current from this limit. Max values should be used when calculating total current consumption.

2: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to Vss.

**3:** ADC oscillator source is FRC.

4: 0.1  $\mu$ F capacitor on VCAP.

5: VREGPM = 0.

# PIC16(L)F1788/9

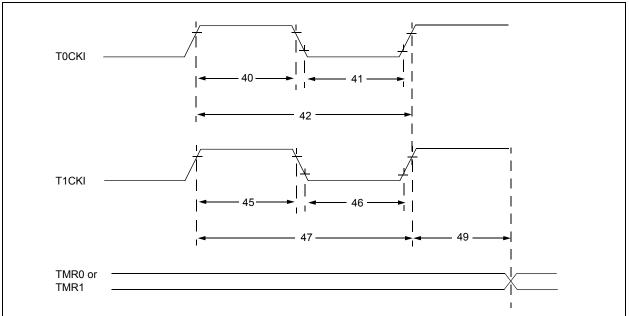

#### FIGURE 31-10: TIMER0 AND TIMER1 EXTERNAL CLOCK TIMINGS

| TABLE 31-11: | TIMER0 AND TIMER1 EXTERNAL CLOCK REQUIREMENTS |

|--------------|-----------------------------------------------|

|--------------|-----------------------------------------------|

| Standa       | rd Operating | Conditions (u                       | Inless otherwis                        | e stated)      |                                           |                                           |        |       |                                    |                                    |

|--------------|--------------|-------------------------------------|----------------------------------------|----------------|-------------------------------------------|-------------------------------------------|--------|-------|------------------------------------|------------------------------------|

| Param<br>No. | Sym.         |                                     | Characteristi                          | c              | Min.                                      | Тур†                                      | Max.   | Units | Conditions                         |                                    |

| 40*          | TT0H         | T0CKI High Pulse Width No Prescaler |                                        |                | 0.5 Tcy + 20                              | _                                         | -      | ns    |                                    |                                    |

|              |              | With                                |                                        | With Prescaler | 10                                        | _                                         | _      | ns    |                                    |                                    |

| 41*          | T⊤0L         | T0CKI Low Pulse Width No Prescaler  |                                        | 0.5 Tcy + 20   | _                                         | _                                         | ns     |       |                                    |                                    |

|              |              |                                     |                                        | With Prescaler | 10                                        | _                                         | _      | ns    |                                    |                                    |

| 42*          | Тт0Р         | T0CKI Period                        | t                                      |                | Greater of:<br>20 or <u>Tcy + 40</u><br>N | —                                         | _      | ns    | N = prescale value<br>(2, 4,, 256) |                                    |

| 45*          | T⊤1H         | T1CKI High<br>Time                  | Synchronous, No Prescaler              |                | 0.5 Tcy + 20                              | _                                         |        | ns    |                                    |                                    |

|              |              |                                     | Synchronous,<br>with Prescaler         |                | 15                                        | _                                         |        | ns    |                                    |                                    |

|              |              |                                     | Asynchronous                           |                | 30                                        | _                                         | _      | ns    |                                    |                                    |

| 46*          | TT1L         | T1CKI Low<br>Time                   | Synchronous, No Prescaler              |                | 0.5 Tcy + 20                              | —                                         |        | ns    |                                    |                                    |

|              |              |                                     | Synchronous, with Prescaler            |                | 15                                        | —                                         |        | ns    |                                    |                                    |

|              |              |                                     | Asynchronous                           |                | 30                                        | —                                         |        | ns    |                                    |                                    |

| 47*          | T⊤1P         | TT1P                                | T1CKI Input<br>Period                  | Synchronous    |                                           | Greater of:<br>30 or <u>Tcy + 40</u><br>N | _      | _     | ns                                 | N = prescale value<br>(1, 2, 4, 8) |

|              |              |                                     | Asynchronous                           |                | 60                                        | _                                         | _      | ns    |                                    |                                    |

| 48           | F⊤1          |                                     | lator Input Freque<br>abled by setting |                | 32.4                                      | 32.768                                    | 33.1   | kHz   |                                    |                                    |

| 49*          | TCKEZTMR1    | Delay from E<br>Increment           | External Clock Ed                      | lge to Timer   | 2 Tosc                                    | —                                         | 7 Tosc | —     | Timers in Sync<br>mode             |                                    |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

## **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

Dallas Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Novi, MI Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

New York, NY Tel: 631-435-6000

San Jose, CA Tel: 408-735-9110

Canada - Toronto Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon

Hong Kong Tel: 852-2943-5100 Fax: 852-2401-3431

Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

China - Chengdu Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

China - Dongguan Tel: 86-769-8702-9880

**China - Hangzhou** Tel: 86-571-8792-8115 Fax: 86-571-8792-8116

**China - Hong Kong SAR** Tel: 852-2943-5100 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

China - Qingdao Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

China - Shanghai Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

**China - Shenyang** Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

#### ASIA/PACIFIC

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-3019-1500

Japan - Osaka Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

Singapore Tel: 65-6334-8870 Fax: 65-6334-8850

Taiwan - Hsin Chu Tel: 886-3-5778-366 Fax: 886-3-5770-955

Taiwan - Kaohsiung Tel: 886-7-213-7828

Taiwan - Taipei Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

Thailand - Bangkok Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

**Denmark - Copenhagen** Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Dusseldorf Tel: 49-2129-3766400

Germany - Karlsruhe Tel: 49-721-625370

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Venice Tel: 39-049-7625286

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

Poland - Warsaw Tel: 48-22-3325737

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

Sweden - Stockholm Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820